Page 1

General Description

The MAX3460–MAX3464 are high-speed differential

bus transceivers for RS-485 and RS-422 communications. They are designed to meet TIA/EIA-422-B,

TIA/EIA-485-A, V.11, and X.27 standards. The transceiver complies with the Profibus specification providing +2.1V output level with a 54Ω load, 20Mbps data

rate, and output skew less than 2ns. Each part contains

one three-state differential line driver and one differential input line receiver. The devices operate from a +5V

supply and feature true fail-safe circuitry, which guarantees a logic-high receiver output when the receiver

inputs are open or shorted. This enables all receiver

outputs on a terminated bus to output logic highs when

all transmitters are disabled.

All devices feature a 1/4 standard unit load receiver

input impedance that allows 128 transceivers on the

bus. Driver and receiver propagation delays are guaranteed under 20ns for multidrop, clock distribution

applications. Drivers are short-circuit current limited

and are protected against excessive power dissipation

by thermal shutdown circuitry. The driver and receiver

feature active-high and active-low enables, respectively, that can be connected together externally to serve

as a direction control.

Applications

High-Speed RS-485 Communications

High-Speed RS-422 Communications

Level Translators

Industrial-Control Local Area Networks

Profibus Applications

Features

♦ Recommended for Profibus Applications

♦ Guaranteed 20Mbps Data Rate

♦ 20ns Transmitter and Receiver Propagation Delay

♦ 2ns Transmitter and Receiver Skew

♦ High Differential Driver Output Level (2.1V on 54Ω)

♦ Hot-Swap Versions

♦ 1µA Shutdown Supply Current

♦ Low Supply Current Requirements (2.5mA typ)

♦ Allow Up to 128 Transceivers on the Bus

♦ True Fail-Safe Receiver while Maintaining EIA/TIA-

485 Compatibility

♦ Designed for Multipoint Transmissions on Long

or Noisy Bus Lines

♦ Full Duplex and Half Duplex Versions Available

♦ Phase Controls to Correct for Twisted-Pair

Reversal for 14-Pin Versions

♦ Current-Limiting and Thermal Shutdown for

Driver Overload Protection

MAX3460–MAX3464

+5V, Fail-Safe, 20Mbps, Profibus RS-485/

RS-422 Transceivers

________________________________________________________________ Maxim Integrated Products 1

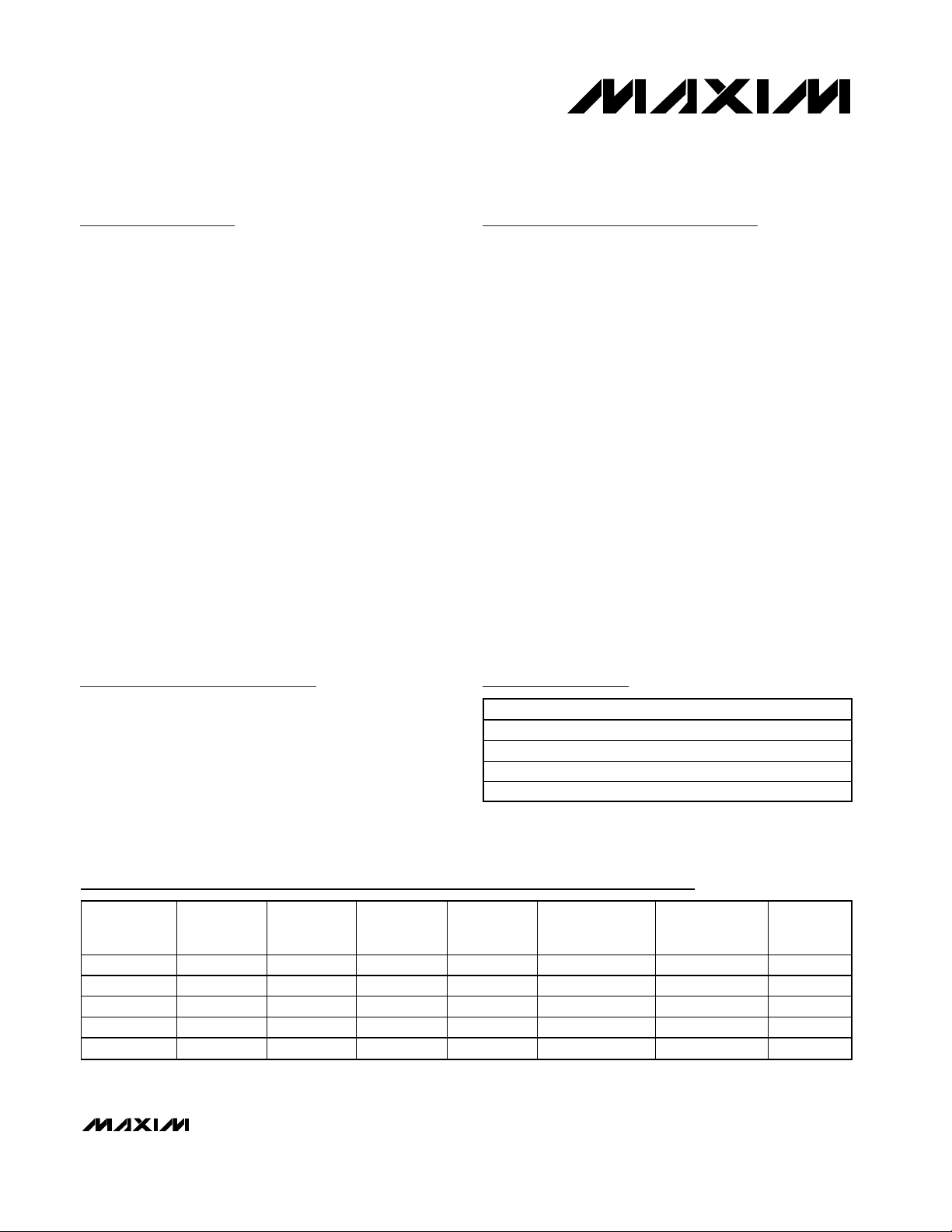

Ordering Information

PART

NUMBER

HALF/FULL

DUPLEX

RECEIVER/

DRIVER

ENABLE

LOW-

POWER

RECEIVER/

DRIVER PHASE

SELECT

INDEPENDENT

SHDN PIN

PIN COUNT

MAX3460 Full Yes Yes Yes Yes Yes 14

MAX3461 Full Yes Yes No Yes Yes 14

MAX3462 Full No No No No No 8

MAX3463 Half Yes Yes Yes No No 8

MAX3464 Half Yes Yes No No No 8

Selector Guide

19-2217; Rev 1; 2/03

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.

Ordering Information continued at end of data sheet.

Pin Configurations appear at end of data sheet.

PART TEMP RANGE PIN-PACKAGE

MAX3460CSD 0°C to +70°C 14 SO

MAX3460CPD 0°C to +70°C 14 Plastic DIP

MAX3460ESD -40°C to +85°C 14 SO

MAX3460EPD -40°C to +85°C 14 Plastic DIP

HOT SWAP

SHUTDOWN

Page 2

MAX3460–MAX3464

+5V, Fail-Safe, 20Mbps, Profibus RS-485/

RS-422 Transceivers

2 _______________________________________________________________________________________

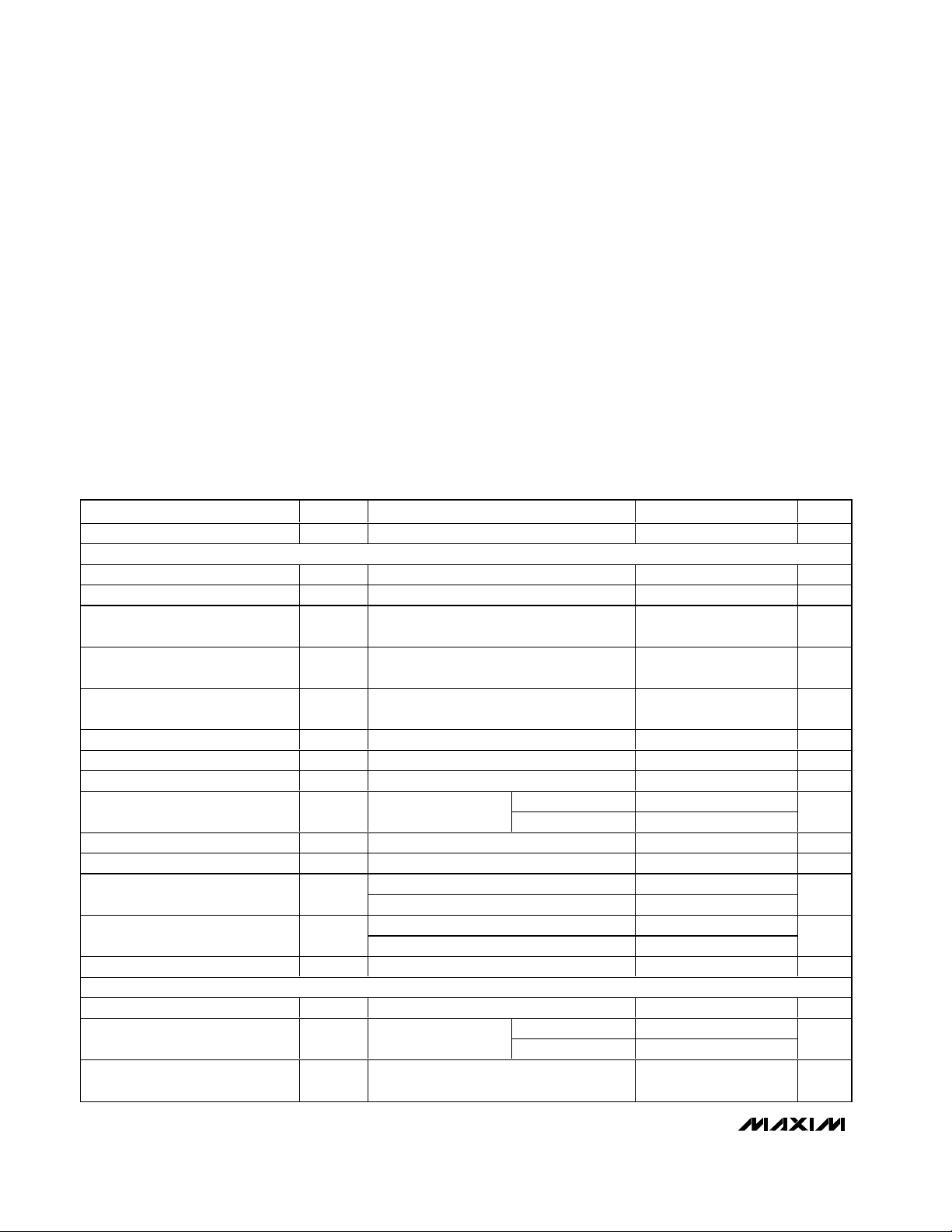

ABSOLUTE MAXIMUM RATINGS

ELECTRICAL CHARACTERISTICS

(VCC= +5V ±5%, TA= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at VCC= +5V and TA= +25°C.) (Note 1)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

Supply Voltage (VCC) to GND ..................................-0.3V to +6V

Control Input Voltage (RE, DE, DI, SHDN, TXP, RXP)

to GND....................................................-0.3V to (V

CC

+ 0.3V)

Driver Output Voltage (Y, Z) to GND .........................-8V to +13V

Receiver Input Voltage (A, B) to GND.......................-8V to +13V

Differential Driver Output Voltage (Y - Z) ...............................±8V

Differential Receiver Input (A - B) ..........................................±8V

Receiver Output Voltage (RO) to GND.......-0.3V to (V

CC

+ 0.3V)

Output Driver Current (Y, Z) ...........................................±250mA

Continuous Power Dissipation (T

A

= +70°C)

8-Pin SO (derate 5.88mW/°C above +70°C)................471mW

8-Pin DIP (derate 9.09mW/°C above +70°C)...............727mW

14-Pin SO (derate 8.33mW/°C above +70°C)..............667mW

14-Pin DIP (derate 10mW/°C above +70°C)................800mW

Operating Temperature Range

MAX346_C__ ......................................................0°C to +70°C

MAX346_E__....................................................-40°C to +85°C

Junction Temperature......................................................+150°C

Storage Temperature Range .............................-65°C to +150°C

Lead Temperature (soldering, 10s) .................................+300°C

Power-Supply Range V

DRIVER

Differential Driver Output (no load) V

Differential Driver Output V

Change in Magnitude of

Differential Output Voltage

Driver Common-Mode Output

Voltage

Change in Magnitude of

Common-Mode Voltage

Input High Voltage V

Input Low Voltage V

Input Hysteresis V

Output Leakage (Y and Z) Full

Duplex

Input Current I

Pulldown Current RXP = TXP = V

Driver Short-Circuit Output

Current (Note 3)

Driver Short-Circuit Foldback

Output Current (Note 3)

Thermal Shutdown Threshold 140 °C

RECEIVER

Differential Input Capacitance C

Input Current (A and B) Full

Duplex

Receiver Differential Threshold

Voltage

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

CC

OD

OD

∆V

V

OC

∆V

HYS

I

IN

I

OSD

I

OSFD

A, B

I

A, B

V

TH

Figure 5, R = ∞ V

Figure 5, R = 27Ω 2.1 V

Figure 5, R = 50Ω or 27Ω

OD

(Note 2)

Figure 5, R = 50Ω or 27Ω 3V

Figure 5, R = 50Ω or 27Ω

OC

(Note 2)

DE, DI, RE, SHDN 2.0 V

IH

DE, DI, RE, SHDN 0.8 V

IL

DE, DI, RE, SHDN 50 mV

V

= +12V +125

DE = GND, VCC =

O

GND or +5.25V

DI, RE, DE, SHDN ±1µA

CC

0 ≤ V

-7V ≤ V

(VCC - 1V) ≤ V

-7V ≤ V

DE = GND,

V

-7V ≤ VCM ≤ 12V -200 -125 -50 mV

≤ 12V, output low +250

OUT

≤ V

OUT

OUT

= GND or 5.25V

CC

, output high -250

CC

≤ 12V, output low +25

OUT

≤ 1V, output high -25

IN

V

= -7V -100

IN

VIN = +12V 250

V

= -7V -200

IN

4.75 5.25 V

CC

0.2 V

0.2 V

51530µA

8pF

V

µA

mA

mA

µA

Page 3

MAX3460–MAX3464

+5V, Fail-Safe, 20Mbps, Profibus RS-485/

RS-422 Transceivers

_______________________________________________________________________________________ 3

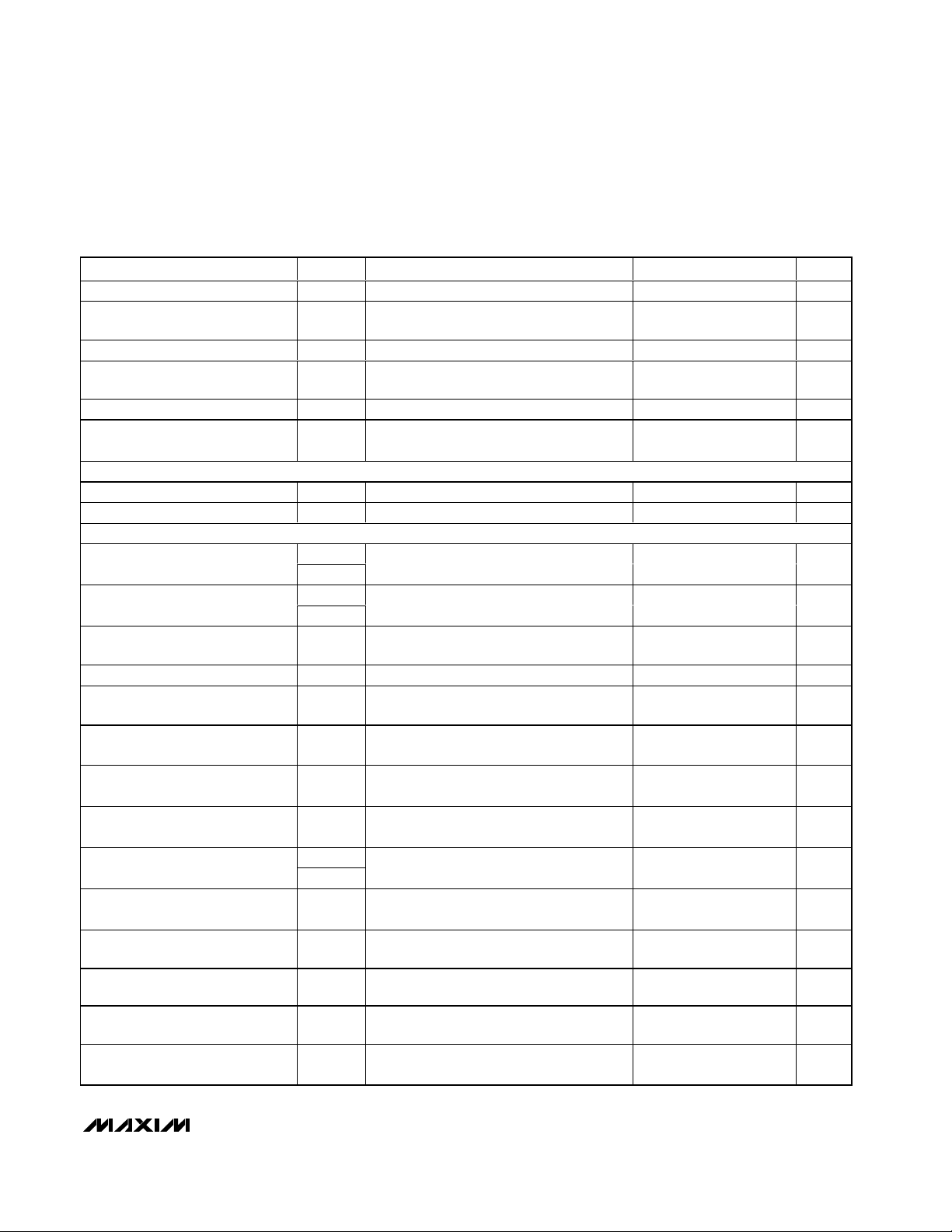

ELECTRICAL CHARACTERISTICS (continued)

(VCC= +5V ±5%, TA= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at VCC= +5V and TA= +25°C.) (Note 1)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Receiver Input Hysteresis ∆V

Receiver Output High Voltage V

Receiver Output Low Voltage V

Three-State Output Current at

Receiver

Receiver Input Resistance R

Receiver Output Short-Circuit

Current

SUPPLY CURRENT

N or m al O p er ati on ( stati c cond i ti on) I

Supply Current in SHDN I

SWITCHING CHARACTERISTICS

Driver Propagation Delay

Driver Differential Output Rise or

Fall Time

Driver Output Skew |t

Maximum Data Rate 20 Mbps

Driver Enable to Output High t

Driver Enable to Output Low t

Driver Disable Time from Low t

Driver Disable Time from High t

Receiver Propagation Delay

Recei ver O utp ut S kew |t

Receiver Enable to Output Low t

Receiver Enable to Output High t

Receiver Disable Time from Low t

Receiver Disable Time from High t

PLH

PLH

- t

PHL

- t

P H L

VA + VB = 0 20 mV

TH

OH

OL

I

OZR

IN

I

OSR

Q

SHDN

t

PLH

t

PHL

t

R

t

F

|t

| t

SKEW

ZH

ZL

LZ

HZ

t

PLH

t

PHL

SKEW

ZL

ZH

LZ

HZ

IO = -4mA, VA - VB = V

IO = 4mA, VB - VA = V

0 ≤ VO ≤ V

CC

TH

TH

-7V ≤ VCM ≤ 12V 48 kΩ

0 ≤ VRO ≤ V

CC

No load, DI = VCC or DI = GND 2.5 4 mA

DE = GND and RE = VCC, or SHDN = V

Figures 6 and 7, R

= 50pF

C

L

Figures 6 and 7, R

= 50pF

C

L

Figures 6 and 7, R

C

= 50pF, TXP = GND or floating

L

DIFF

DIFF

DIFF

= 54Ω,

= 54Ω,

= 54Ω,

Figures 8 and 9, S2 closed, RL = 500Ω,

C

= 50pF

L

Figures 8 and 9, S1 closed, RL = 500Ω,

C

= 50pF

L

Figures 8 and 9, S1 closed, RL = 500Ω,

= 50pF

C

L

Figures 8 and 9, S2 closed, RL = 500Ω,

C

= 50pF

L

Figure 10, CL = 15pF (Note 4) 20 ns

Figure 10, CL = 15pF, RXP = GND or

floating (Note 4)

Figures 8 and 11, RL = 1kΩ, CL = 15pF,

S1 closed (Note 4)

Figures 8 and 11, RL = 1kΩ, CL = 15pF,

S2 closed (Note 4)

Figures 8 and 11, RL = 1kΩ, CL = 15pF,

S1 closed (Note 4)

Figures 8 and 11, RL = 1kΩ, CL = 15pF,

S2 closed (Note 4)

VCC - 1.5 V

±7 ±95 mA

CC

110µA

0.4 V

±1µA

20 ns

20 ns

2ns

100 ns

100 ns

100 ns

100 ns

2ns

100 ns

100 ns

100 ns

100 ns

Page 4

Note 1: All currents into the device are positive; all currents out of the device are negative. All voltages are referenced to device

ground, unless otherwise noted.

Note 2: ∆V

OD

and ∆VOCare the changes in VODand VOC, respectively, when the DI input changes state.

Note 3: The short-circuit output current applies to peak current just prior to foldback-current limiting; the short-circuit foldback output

current applies during current limiting to allow a recovery from bus contention.

Note 4: Capacitive load includes test probe and fixture capacitance.

Note 5: Shutdown is enabled by bringing RE high and DE low or by bringing SHDN high. If the enable inputs are in this state for less

than 50ns, the device is guaranteed not to enter shutdown. If the enable inputs are in this state for at least 800ns, the device

is guaranteed to have entered shutdown.

MAX3460–MAX3464

+5V, Fail-Safe, 20Mbps, Profibus RS-485/

RS-422 Transceivers

4 _______________________________________________________________________________________

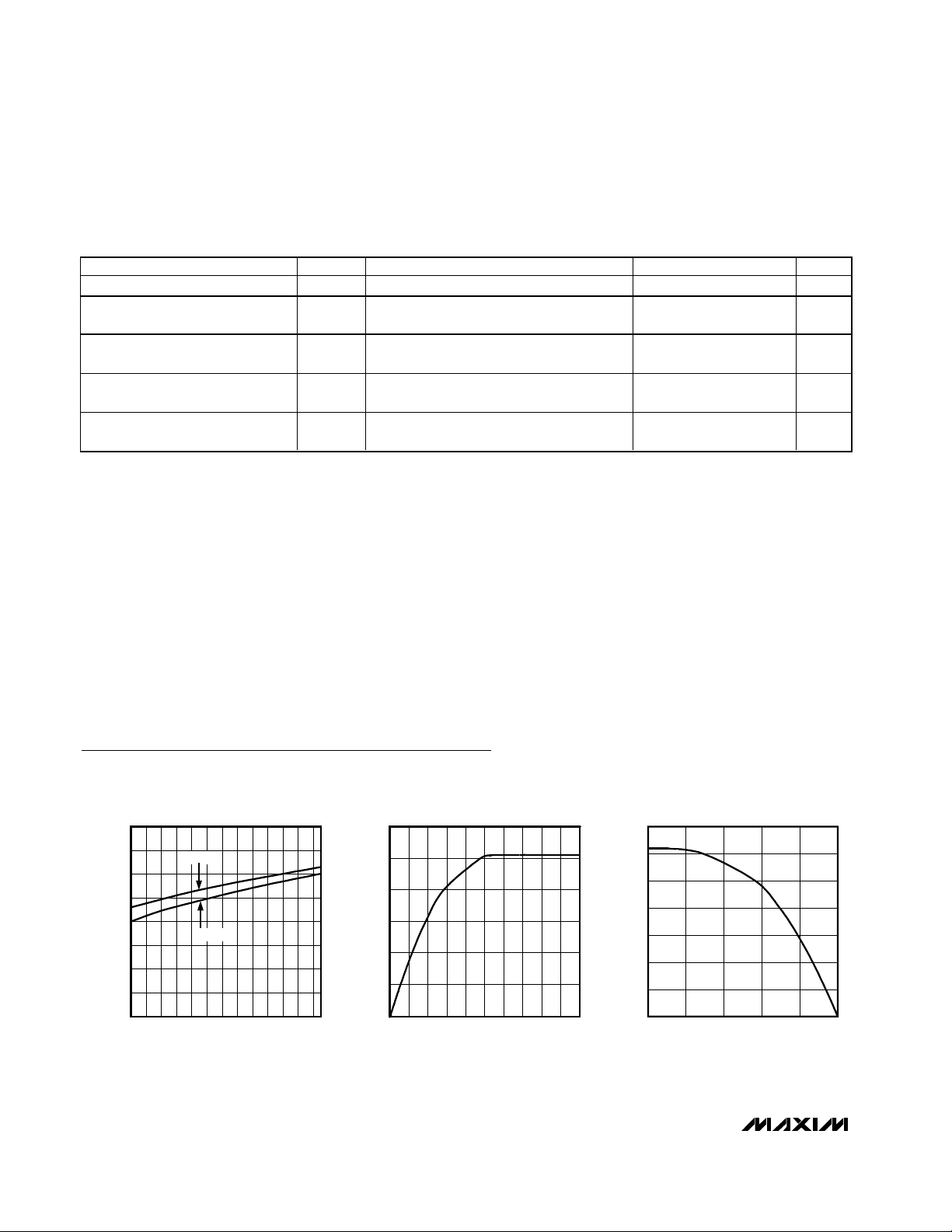

ELECTRICAL CHARACTERISTICS (continued)

(VCC= +5V ±5%, TA= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at VCC= +5V and TA= +25°C.) (Note 1)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Time to Shutdown t

SHDN

(Note 5) 50

ns

Driver Enable from Shutdown to

Output High

)

Figures 8 and 9, RL = 500Ω, CL = 50pF,

S2 closed (Note 5)

4µs

Driver Enable from Shutdown to

Output Low

)

Figures 8 and 9, RL = 500Ω, CL = 50pF,

S1 closed (Note 5)

4µs

Receiver Enable from Shutdown to

Output High

)

Figures 8 and 11, RL = 1kΩ, CL = 15pF,

S2 closed (Notes 4, 5)

4µs

Receiver Enable from Shutdown to

Output Low

)

Figures 8 and 11, RL = 1kΩ, CL = 15pF,

S1 closed (Notes 4, 5)

4µs

NO LOAD SUPPLY CURRENT

vs. TEMPERATURE

MAX3460-64 toc01

2.00

2.05

2.15

2.10

2.30

2.35

2.25

2.20

2.40

NO LOAD SUPPLY CURRENT (mA)

-40 0 20-20

40

60 80

TEMPERATURE (°C)

DE = V

CC

DE = GND

0

30

20

10

40

50

60

0 2.01.50.5 1.0 2.5 3.0 3.5 4.0 4.5 5.0

OUTPUT CURRENT

vs. RECEIVER OUTPUT LOW VOLTAGE

MAX3460-64 toc02

OUTPUT LOW VOLTAGE (V)

OUTPUT CURRENT (mA)

0

10

5

20

15

30

25

35

021345

OUTPUT CURRENT

vs. RECEIVER OUTPUT HIGH VOLTAGE

MAX3460-64 toc03

OUTPUT HIGH VOLTAGE (V)

OUTPUT CURRENT (mA)

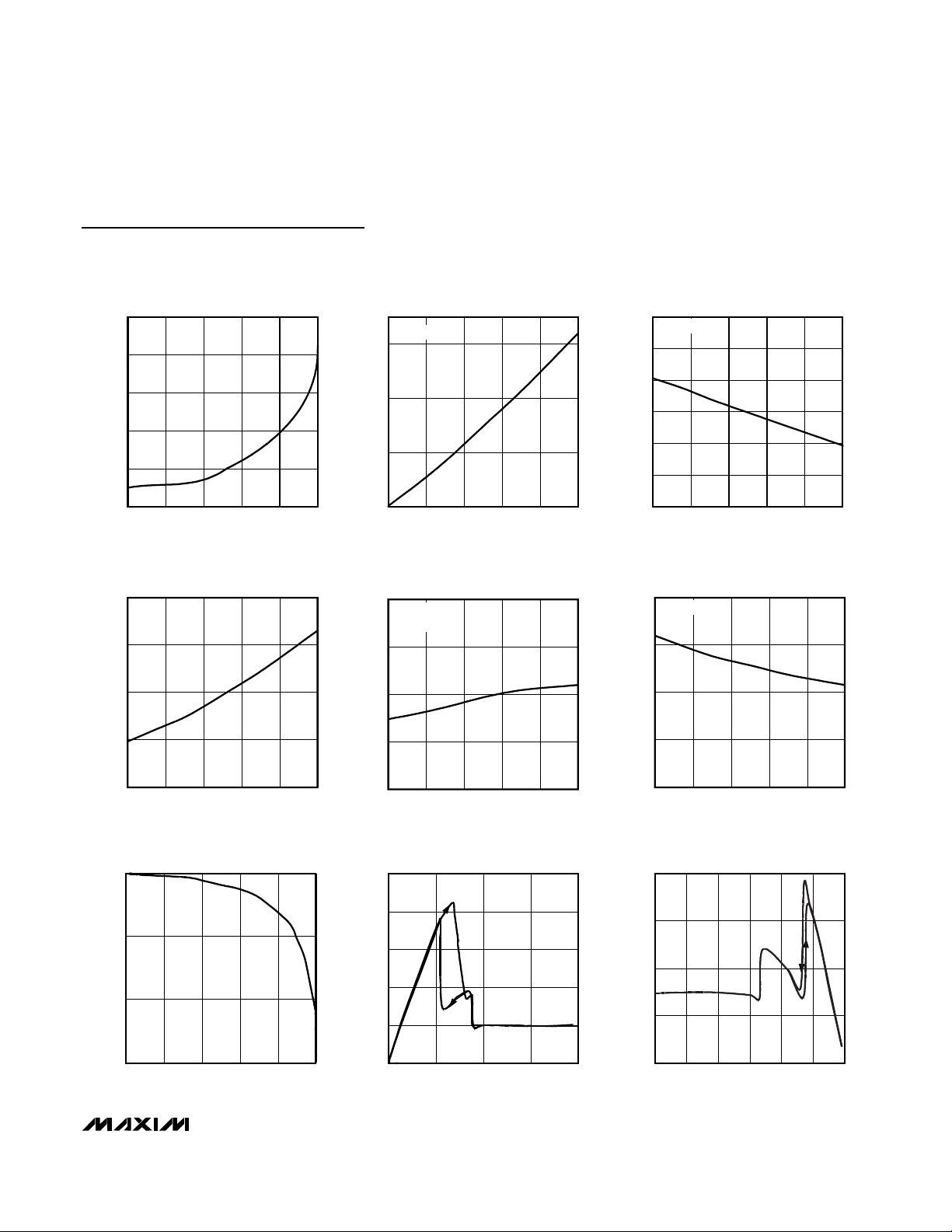

Typical Operating Characteristics

(VCC= +5V, TA = +25°C, unless otherwise noted.)

t

ZH (SHDN

t

ZL (SHDN

t

ZH (SHDN

t

ZL (SHDN

800

Page 5

MAX3460–MAX3464

+5V, Fail-Safe, 20Mbps, Profibus RS-485/

RS-422 Transceivers

_______________________________________________________________________________________ 5

Typical Operating Characteristics (continued)

(VCC= +5V, TA = +25°C, unless otherwise noted.)

SHUTDOWN SUPPLY CURRENT

vs. TEMPERATURE

50

40

30

20

10

SHUTDOWN SUPPLY CURRENT (nA)

0

-40 10-15 35 60 85

TEMPERATURE (°C)

MAX3460-64 toc04

RECEIVER OUTPUT LOW VOLTAGE (mV)

RECEIVER PROPAGATION DELAY

vs. TEMPERATURE

11

10

MAX3460-64 toc07

RECEIVER OUTPUT LOW VOLTAGE

vs. TEMPERATURE

IO = 4mA

140

120

100

80

-40 10-15 35 60 85

TEMPERATURE (°C)

DRIVER PROPAGATION DELAY

vs. TEMPERATURE

12

R

= 54Ω

DIFF

= 50pF

C

L

10

MAX3460-64 toc05

MAX3460-64 toc08

RECEIVER OUTPUT HIGH VOLTAGE

vs. TEMPERATURE

4.90

IO = -4mA

4.85

4.80

4.75

4.70

OUTPUT HIGH VOLTAGE (V)

4.65

4.60

-40 85

10-15 35 60

TEMPERATURE (°C)

DRIVER DIFFERENTIAL OUTPUT VOLTAGE

vs. TEMPERATURE

4.0

R

= 54Ω

DIFF

3.5

MAX3460-64 toc06

MAX3460-64 toc09

9

PROPAGATION DELAY (ns)

8

7

-40 10-15 35 60 85

TEMPERATURE (°C)

DRIVER OUTPUT CURRENT

vs. DIFFERENTIAL OUTPUT VOLTAGE

100

10

1

OUTPUT CURRENT (mA)

0.1

021345

DIFFERENTIAL OUTPUT VOLTAGE (V)

8

PROPAGATION DELAY (ns)

6

4

200

160

MAX3460-64 toc10

120

80

OUTPUT CURRENT (mA)

40

0

3.0

OUTPUT VOLTAGE (V)

2.5

2.0

-40 10-15 35 60 85

TEMPERATURE (°C)

-40 10-15 35 60 85

OUTPUT CURRENT

vs. DRIVER OUTPUT LOW VOLTAGE

-160

MAX3460-64 toc11

-120

-80

OUTPUT CURRENT (mA)

-40

063912

OUTPUT LOW VOLTAGE (V)

0

TEMPERATURE (°C)

OUTPUT CURRENT

vs. DRIVER OUTPUT HIGH VOLTAGE

MAX3460-64 toc12

-7 -3-5 -1 1 3 5

OUTPUT HIGH VOLTAGE (V)

Page 6

MAX3460–MAX3464

+5V, Fail-Safe, 20Mbps, Profibus RS-485/

RS-422 Transceivers

6 _______________________________________________________________________________________

Pin Description

Typical Operating Characteristics (continued)

(VCC= +5V, TA = +25°C, unless otherwise noted.)

0

5V/div

2V/div

5V/div

0

0

DRIVER AND RECEIVER

PROPAGATION DELAYS

MAX3460-64 toc13

DI

Y, Z

RO

10ns/div

0

0

ENABLE RESPONSE TIME

MAX3460-64 toc14

DE

Y, Z

20ns/div

1V/div

5V/div

EYE DIAGRAM

MAX3460-64 toc15

10ns/div

MAX3460/

MAX3461

FULL DUPLEX

PIN

MAX3462

MAX3463/

MAX3464

HALF

DUPLEX

1 ——SHDN Shutdown. Drive SHDN high to enter low-power shutdown mode.

221RO

3 — 2 RE

4 — 3DE

534DI

6, 7 4 5 GND Ground

8 ——TXP

95— Y Noninverting Driver Output

10 6 — Z Inverting Driver Output

11 7 — B Inverting Receiver Input

12 8 — A Noninverting Receiver Input

13 ——RXP

14 1 8 V

—— 7 B Inverting Receiver Input and Inverting Driver Output

—— 6 A Noninverting Receiver Input and Noninverting Driver Output

NAME FUNCTION

Receiver Output. When RE is low and (A - B) ≥ -50mV, RO is high; if (A - B) ≤

-200mV, RO is low.

Receiver Output Enable. Drive RE low to enable RO; RO is high impedance

when RE is high. Drive RE high and DE low to enter low-power shutdown mode.

Driver Output Enable. Drive DE high to enable driver output. These outputs

are high impedance when DE is low. Drive RE high and DE low to enter lowpower shutdown mode.

Driver Input. With DE high, a low on DI forces the noninverting output low and

the inverting output high. Similarly, a high on DI forces the noninverting output

high and the inverting output low.

Transmitter Phase. Connect TXP to GND, or leave unconnected for normal

transmitter phase/polarity. Connect TXP to V

phase/polarity. TXP has an internal 15µA pulldown.

Receiver Phase. Connect RXP to GND, or leave unconnected for normal

receiver phase/polarity. Connect RXP to V

CC

phase/polarity. RXP has an internal 15µA pulldown.

Positive Supply: +4.75V ≤ VCC ≤ +5.25V. Bypass VCC to GND with a 0.1µF

CC

capacitor.

to invert the transmitter

CC

to invert the receiver

Page 7

MAX3460–MAX3464

+5V, Fail-Safe, 20Mbps, Profibus RS-485/

RS-422 Transceivers

_______________________________________________________________________________________ 7

MAX3460/MAX3461

Function Tables

MAX3462

MAX3463/MAX3464

RE DE DI SHDN Z Y

X11001

X10010

0 0 X 0 High-Z High-Z

1 0 X X Shutdown

X X X 1 Shutdown

RE DE A–B SHDN RO

0X≥ -0.05V 0 1

0X≤ -0.2V 0 0

0 X Open/Shorted 0 1

1 1 X 0 High-Z

1 0 X X Shutdown

X X X 1 Shutdown

TRANSMITTING

INPUTS OUTPUTS

RECEIVING

INPUTS OUTPUT

TRANSMITTING

INPUT OUTPUTS

DI Z Y

101

010

RECEIVING

INPUTS OUTPUT

A–BRO

≥ -0.05V 1

≤ -0.2V 0

Open/Shorted 1

INPUTS OUTPUTS

RE DE DI B A

X11 0 1

X10 1 0

0 0 X High-Z High-Z

1 0 X Shutdown

TRANSMITTING

RECEIVING

INPUTS OUTPUT

RE DE A–BRO

0X ≥ -0.05V 1

0X ≤ -0.2V 0

0 X Open/Shorted 1

1 1 X High-Z

1 0 X Shutdown

Page 8

MAX3460–MAX3464

+5V, Fail-Safe, 20Mbps, Profibus RS-485/

RS-422 Transceivers

8 _______________________________________________________________________________________

Pin Configurations and Typical Operating Circuit

Figure 1. MAX3460/MAX3461 Pin Configuration and Typical Full-Duplex Operating Circuit

Figure 2. MAX3462 Pin Configuration and Typical Full-Duplex Operating Circuit

Figure 3. MAX3463/MAX3464 Pin Configuration and Typical Full-Duplex Operating Circuit

TOP VIEW

SHDN

GND

GND

DE

1

RO

2

R

RE

3

4

DI

5

D

6

7

14

V

CC

RXP

13

A

12

BDE

11

Z

10

9

Y

TXP

8

TXP

RXP

5

DI

2

RO

8

13

DIP/SO

CC

414

9ZY

D

R

3 GND

6, 7

RE

10

12

11

A

B

0.1µF

R

t

V

TOP VIEW

V

GND

V

1

CC

3

D

1

CC

RO

DI

R

2

3

D

4

8

A

7

B

6

Z

5

Y

DI

2

RO

DIP/SO

4 GND

0.1µF

5ZY

6

8

A

R

R

7

t

B

MAX3460

MAX3461

MAX3462

V

RE

CC

R

t

R

t

GND

R

V

GND

R

CC

D

RO

D

DI

DE

RO

DI

TOP VIEW

0.1µF

R

1

RO

2

RE

3

DE

D

4

DI

8

RO

V

CC

7

B

RE

6

A

DE

5

GND

DI

R

1

2

3

D

4

V

8

CC

B

7

6

5

A

GND

R

t

MAX3463

MAX3464

B

R

t

A

DIP/SO

NOTE: PIN LABELS Y AND Z ON TIMING, TEST, AND WAVEFORM DIAGRAMS REFER TO PINS A AND B WHEN DE IS HIGH.

DE

R

D

RE

DI

RO

Page 9

MAX3460–MAX3464

+5V, Fail-Safe, 20Mbps, Profibus RS-485/

RS-422 Transceivers

_______________________________________________________________________________________ 9

Detailed Description

The MAX3460–MAX3464 high-speed transceivers for

RS-485/RS-422 communication contain one driver and

one receiver. These devices feature true fail-safe circuitry, which guarantees a logic-high receiver output

when the receiver inputs are open or shorted, or when

they are connected to a terminated transmission line

with all drivers disabled (see the True Fail-Safe section). The MAX3460–MAX3464’s driver slew rates allow

transmit speeds up to 20Mbps.

The MAX3463 and MAX3464 are half-duplex transceivers, while the MAX3460, MAX3461, and MAX3462

are full-duplex transceivers. All of these parts operate

from a single +5V supply. Drivers are output short-circuit current limited. Thermal shutdown circuitry protects

drivers against excessive power dissipation. When activated, the thermal shutdown circuitry places the driver

outputs into a high-impedance state. The MAX3460

and MAX3463 devices have a hot-swap input structure

that prevents disturbances on the differential signal

lines when a circuit board is plugged into a “hot” backplane (see Hot Swap section). All devices have output

levels that are compatible with Profibus standards.

True Fail-Safe

The MAX3460–MAX3464 guarantee a logic-high receiver output when the receiver inputs are shorted or open,

or when they are connected to a terminated transmission line with all drivers disabled. This is done by setting the receiver threshold between -50mV and

-200mV. If the differential receiver input voltage (A - B)

is greater than or equal to -50mV, RO is logic high. If A

- B is less than or equal to -200mV, RO is logic low. In

the case of a terminated bus with all transmitters disabled, the receiver’s differential input voltage is pulled

to 0V by the termination. With the receiver thresholds of

the MAX3460–MAX3464, this results in a logic high with

a 50mV minimum noise margin. Unlike previous true

fail-safe devices, the -50mV to -200mV threshold complies with the ±200mV EIA/TIA-485 standard.

Hot-Swap Capability

Hot-Swap Inputs

When circuit boards are inserted into a “hot” or powered backplane, disturbances to the enable and differential receiver inputs can lead to data errors. Upon

initial circuit board insertion, the processor undergoes

its power-up sequence. During this period, the output

drivers are high impedance and are unable to drive the

DE input of the MAX3460/MAX3463 to a defined logic

level. Leakage currents up to 10µA from the highimpedance output could cause DE to drift to an incorrect logic state. Additionally, parasitic circuit board

capacitance could cause coupling of V

CC

or GND to

DE. These factors could improperly enable the driver.

When VCCrises, an internal pulldown circuit holds DE

low for around 15µs. After the initial power-up

sequence, the pulldown circuit becomes transparent,

resetting the hot-swap tolerable input.

Hot-Swap Input Circuitry

The MAX3460/MAX3463 enable inputs feature hot-swap

capability. At the input there are two NMOS devices, M1

and M2 (Figure 4). When VCCramps from 0, an internal

15µs timer turns on M2 and sets the SR latch, which

also turns on M1. Transistors M2, a 2mA current sink,

and M1, a 100µA current sink, pull DE to GND through a

5.6kΩ resistor. M2 is designed to pull DE to the disabled

state against an external parasitic capacitance up to

100pF that can drive DE high. After 15µs, the timer

deactivates M2 while M1 remains on, holding DE low

against three-state leakages that can drive DE high. M1

remains on until an external source overcomes the

required input current. At this time, the SR latch resets

and M1 turns off. When M1 turns off, DE reverts to a

standard, high-impedance CMOS input. Whenever V

CC

drops below 1V, the hot-swap input is reset.

For RE there is a complimentary circuit employing two

PMOS devices pulling RE to VCC.

Figure 4. Simplified Structure of the Driver Enable Pin (DE)

V

CC

TIMER

15µs

TIMER

EN

5.6kΩ

M1 M2

100µA

(HOT SWAP)

2mA

DE

Page 10

MAX3460–MAX3464

+5V, Fail-Safe, 20Mbps, Profibus RS-485/

10 ______________________________________________________________________________________

Figure 5. Driver DC Test Load

Figure 6. Driver Timing Test Circuit

Figure 7. Driver Propagation Delays

Figure 8. Enable/Disable Timing Test Load

Figure 9. Driver Enable and Disable Times

Figure 10. Receiver Propagation Delays

Figure 11. Receiver Enable and Disable Times

Y

R

V

OD

R

V

OC

Z

3V

DE

Y

DI

R

DIFF

V

ID

C

L

Z

S1

OUTPUT

R

L

UNDER TEST

C

L

S2

3V

DE

Y, Z

V

OL

Y, Z

1.5V

0

, t

t

ZL(SHDN)

ZL

2.3V

OUTPUT NORMALLY LOW

OUTPUT NORMALLY HIGH

0

2.3V

t

ZH(SHDN)

, t

ZH

ƒ = 1MHz, tR ≤ 3ns, tF ≤ 3ns

V

OH

RO

V

OL

A

1V

B

-1V

1.5V 1.5V

t

PHL

INPUT

OUTPUT

t

PLH

V

CC

1.5V

t

LZ

V

+ 0.5V

OL

V

- 0.5V

OH

t

HZ

3V

DI

V

DIFF

1.5V

0

Z

V

O

Y

1/2 V

V

O

0

-V

10%

O

t

R

ƒ = 1MHz, tR ≤ 3ns, tF ≤ 3ns

O

90%

1.5V

t

PLH

V

= V (Y) - V (Z)

DIFF

t

SKEW

= | t

t

PHL

90%

t

F

- t

|

PLH

PHL

10%

1/2 V

O

3V

RE

V

CC

RO

RO

1.5V

0

t

, t

ZL(SHDN)

ZL

1.5V

OUTPUT NORMALLY LOW

OUTPUT NORMALLY HIGH

0

1.5V

t

ZH(SHDN)

, t

ZH

1.5V

t

LZ

V

+ 0.5V

OL

- 0.5V

V

OH

t

HZ

Page 11

MAX3460–MAX3464

+5V, Fail-Safe, 20Mbps, Profibus RS-485/

RS-422 Transceivers

______________________________________________________________________________________ 11

Applications Information

128 Transceivers on the Bus

The standard RS-485 receiver input impedance is 12kΩ

(one-unit load), and the standard driver can drive up to

32 unit loads. The MAX3460–MAX3464 family of transceivers has a 1/4-unit-load receiver input impedance

(48kΩ), allowing up to 128 transceivers to be connected in parallel on one communication line. Any combination of these devices and/or other RS-485 transceivers

with a total of 32 unit loads or less can be connected to

the line.

Low-Power Shutdown Mode

(except MAX3462)

Low-power shutdown mode is initiated by bringing

SHDN high (MAX3460/MAX3461), or both RE high and

DE low. In shutdown, the devices typically draw only

1µA of supply current. RE and DE can be driven simultaneously; the parts are guaranteed not to enter shutdown if RE is high and DE is low for less than 50ns. If

the inputs are in this state for at least 800ns, the parts

are guaranteed to enter shutdown.

Driver Output Protection

Two mechanisms prevent excessive output current and

power dissipation caused by faults or by bus contention. The first, a foldback current limit on the output

stage, provides immediate protection against short circuits over the whole common-mode voltage range (see

Typical Operating Characteristics). The second, a thermal shutdown circuit, forces the driver outputs into a

high-impedance state if the die temperature exceeds

+140°C.

Propagation Delay

Many digital encoding schemes depend on the difference

between the driver and receiver propagation delay times.

Typical propagation delays are shown in the Typical

Operating Characteristics. The difference in receiver delay

times, |t

PLH

- t

PHL

|, is a maximum of 2ns. The driver skew

time |t

PLH

- t

PHL

| is also a maximum of 2ns.

Typical Applications

The MAX3460–MAX3464 transceivers are designed for

bidirectional data communications on multipoint bus

transmission lines. Figures 13 and 14 show typical network applications circuits. To minimize reflections, the

line should be terminated at both ends in its characteristic impedance, and stub lengths off the main line

should be kept as short as possible.

Profibus Termination

The MAX3460–MAX3464 are designed for driving

Profibus termination networks. With a worst-case loading of two termination networks with 220Ω termination

impedance and 390Ω pullups and pulldowns, the drivers can drive V

A-B

> 2.1V output.

Chip Information

TRANSISTOR COUNT: 610

PROCESS: BiCMOS

Figure 12. Receiver Propagation Delay Test Circuit

Ordering Information (continued)

B

RECEIVER

ATE

V

ID

R

OUTPUT

A

PART TEMP RANGE PIN-PACKAGE

MAX3461CSD 0°C to +70°C 14 SO

MAX3461CPD 0°C to +70°C 14 Plastic DIP

MAX3461ESD -40°C to +85°C 14 SO

MAX3461EPD -40°C to +85°C 14 Plastic DIP

MAX3462CSA 0°C to +70°C 8 SO

MAX3462CPA 0°C to +70°C 8 Plastic DIP

MAX3462ESA -40°C to +85°C 8 SO

MAX3462EPA -40°C to +85°C 8 Plastic DIP

MAX3463CSA 0°C to +70°C 8 SO

MAX3463CPA 0°C to +70°C 8 Plastic DIP

MAX3463ESA -40°C to +85°C 8 SO

MAX3463EPA -40°C to +85°C 8 Plastic DIP

MAX3464CSA 0°C to +70°C 8 SO

MAX3464CPA 0°C to +70°C 8 Plastic DIP

MAX3464ESA -40°C to +85°C 8 SO

MAX3464EPA -40°C to +85°C 8 Plastic DIP

Page 12

MAX3460–MAX3464

+5V, Fail-Safe, 20Mbps, Profibus RS-485/

RS-422 Transceivers

12 ______________________________________________________________________________________

Figure 13. Typical Half-Duplex RS-485 Network

Figure 14. Typical Full-Duplex RS-485 Network

120Ω 120Ω

DI

D

B

B

D

DE

DE

RO

RE

R

MAX3463

A

D

MAX3464

(HALF-DUPLEX)

DI DE RO

A

RO

RE

DE

DI

R

D

120Ω

B

Z

120Ω

Y

YZB A B

AABAB

R

R

RE

YZ

D

DI DE RO

R

RE

120Ω

120Ω

Y

D

Z

B

R

A

DI

RO

RE

DI

DE

RE

RO

D

R

D

R

(FULL-DUPLEX)

DI DE RORE

NOTE: RE AND DE ON MAX3460/MAX3461/MAX3462 ONLY

DI DE RORE

MAX3460

MAX3461

MAX3462

Page 13

MAX3460–MAX3464

+5V, Fail-Safe, 20Mbps, Profibus RS-485/

RS-422 Transceivers

______________________________________________________________________________________ 13

Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,

go to www.maxim-ic.com/packages

.)

N

1

TOP VIEW

D

e

FRONT VIEW

INCHES

DIM

MIN

0.053A

0.004

A1

0.014

B

0.007

C

e 0.050 BSC 1.27 BSC

0.150

HE

A

B

A1

C

L

E

H 0.2440.228 5.80 6.20

0.016L

VARIATIONS:

INCHES

MINDIM

D

0.189 0.197 AA5.004.80 8

0.337 0.344 AB8.758.55 14

D

0-8

SIDE VIEW

MAX

0.069

0.010

0.019

0.010

0.157

0.050

MAX

0.3940.386D

MILLIMETERS

MAX

MIN

1.35

1.75

0.10

0.25

0.35

0.49

0.19

0.25

3.80 4.00

0.40 1.27

MILLIMETERS

MAX

MIN

9.80 10.00

N MS012

16

AC

SOICN .EPS

PROPRIETARY INFORMATION

TITLE:

PACKAGE OUTLINE, .150" SOIC

REV.DOCUMENT CONTROL NO.APPROVAL

21-0041

1

B

1

Page 14

MAX3460–MAX3464

+5V, Fail-Safe, 20Mbps, Profibus RS-485/

RS-422 Transceivers

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are

implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

14 ____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2003 Maxim Integrated Products Printed USA is a registered trademark of Maxim Integrated Products.

Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,

go to www.maxim-ic.com/packages

.)

PDIPN.EPS

Loading...

Loading...