Page 1

查询MAX1132EVKIT供应商

19-3488; Rev 1; 1/05

提供评估板

_________________________________

低功耗、14位、多通道、模数转换器

MAX1149

MAX1146/MAX1148

MAX1147/MAX1149

有模拟输入均可通过软件设置为单极性/双极性和单端/差

分模式。

其4线串口可直接连接

件,无需外部逻辑接口。利用串行触发输出

方便实现与数字信号处理器的连接。

采用内部时钟或外部串行时钟实现逐次逼近型模数转换。

MAX1146/MAX1148

MAX1149

1.5V到V

MAX1146–MAX1149

式。采用软关断模式可以使器件在转换之间关断。关断

后,访问串口将自动启动器件。快速的启动时间允许在

所有转换之间关断。采用快速启动,电源电流可降至低

于

120µA

MAX1146–MAX1149

,内置采样/保持

采用

采用

内部含一个

内部含一个

的外部基准。

DD

。

提供20引脚的

(T/H)

+4.75V至+5.25V

+2.7V至+3.6V

SPI™/QSPI™/MICROWIRE

+2.500V

提供一个硬关断和两个软关断模

(ADC) MAX1146–

、电压基准和时钟。

单电源供电。所

MAX1146–MAX1149

+4.096V

基准,而

基准。所有器件均可使用

TSSOP

封装。

概述

单电源供电,

™ 器

(SSTRB)

MAX1147/

可

多通道、真差分、串行、

位

14

_________________________________

路单端或4路差分输入

♦

8

路单端或2路差分输入

♦

4

内部复用器和

♦

单电源供电

♦

4.75V至5.25V

2.7V至3.6V (MAX1147/MAX1149)

内部基准

♦

+4.096V (MAX1146/MAX1148)

+2.500V (MAX1147/MAX1149)

♦

116ksps

低功耗

♦

1.1mA (116ksps)

120µA (10ksps)

12µA (1ksps)

300nA (

♦

SPI/QSPI/MICROWIRE

引脚

♦

20

T/H

电源供电

采样速率

关断模式

TSSOP

(MAX1148/MAX1149)

(MAX1146/MAX1147)

(MAX1146/MAX1148)

)

兼容

ADC

MAX1146–MAX1149

特性

_________________________________

便携式数据记录仪

数据采集

医疗仪器

电池供电仪表

过程控制

_______________________________________________________________

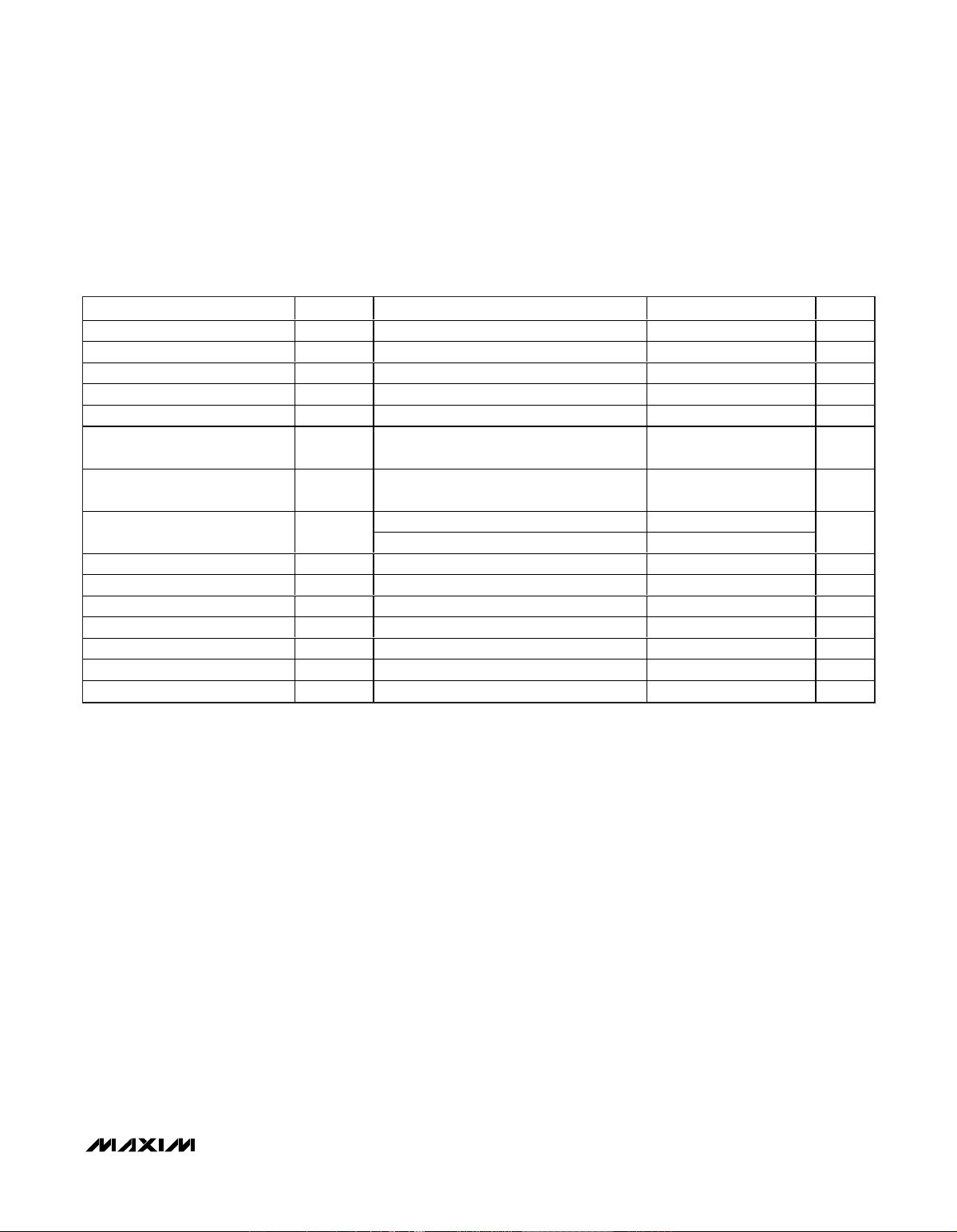

PART

MAX1146BCUP 0°C to +70°C 20 TSSOP ±2 4 +4.096

MAX1146BEUP -40°C to +85°C 20 TSSOP ±2 4 +4.096

MAX1147BCUP 0°C to +70°C 20 TSSOP ±2 4 +2.500

MAX1147BEUP -40°C to +85°C 20 TSSOP ±2 4 +2.500

MAX1148BCUP 0°C to +70°C 20 TSSOP ±2 8 +4.096

MAX1148BEUP -40°C to +85°C 20 TSSOP ±2 8 +4.096

MAX1149BCUP 0°C to +70°C 20 TSSOP ±2 8 +2.500

MAX1149BEUP -40°C to +85°C 20 TSSOP ±2 8 +2.500

TEMP

RANGE

应用

PINPACKAGE

引脚配置位于数据资料末尾。

SPI/QSPI是Motorola, Inc.

MICROWIRE是National Semiconductor Corp.

的商标。

定购信息/选购指南

INL

(LSB)

INPUT

CHANNELS

的商标。

INTERNAL

REFERENCE (V)

________________________________________________________________ Maxim Integrated Products 1

本文是

翻译错误,如需确认任何词语的准确性,请参考

索取免费样品和最新版的数据资料,请访问

正式英文资料的译文,

Maxim

不对翻译中存在的差异或由此产生的错误负责。请注意译文中可能存在文字组织或

Maxim

Maxim

Maxim

提供的英文版资料。

的主页:

www.maxim-ic.com.cn

。

Page 2

多通道、真差分、串行、

位

14

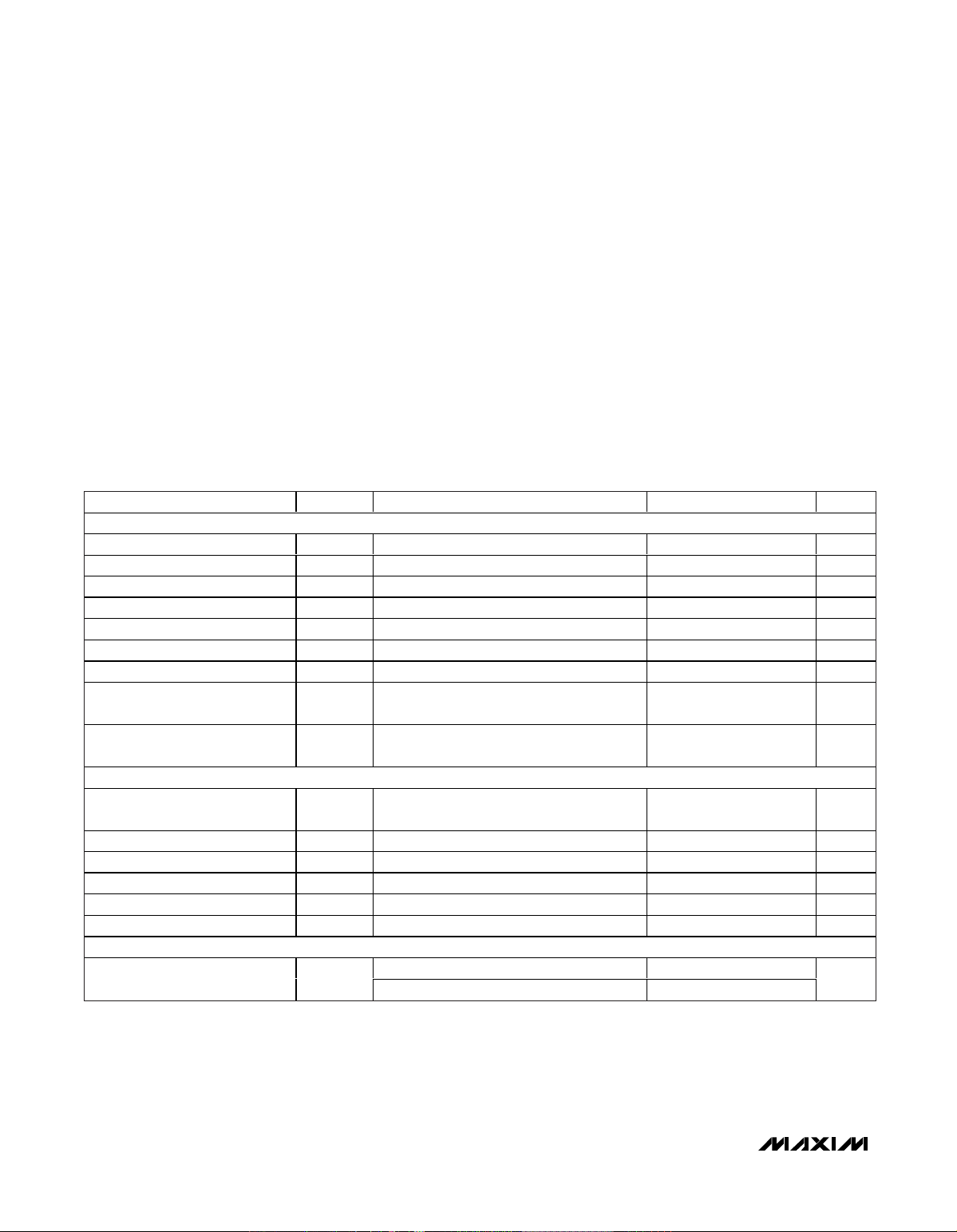

ABSOLUTE MAXIMUM RATINGS

VDDto AGND, DGND............................................-0.3V to +6.0V

AGND to DGND.....................................................-0.3V to +0.3V

CH0–CH7, COM to AGND..........................-0.3V to (V

REF, REFADJ to AGND ..............................-0.3V to (V

Digital Inputs to DGND...............................-0.3V to (V

Digital Outputs to DGND............................-0.3V to (V

Digital Output Sink Current .................................................25mA

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

ELECTRICAL CHARACTERISTICS

(VDD= 5V (MAX1146/MAX1148), VDD= 3.3V (MAX1147/MAX1149), SHDN = VDD, V

duty cycle), 18 clocks/conversion (116ksps), V

MAX1148), external 2.500V reference at REF (MAX1147/MAX1149), T

= +25°C.)

T

A

MAX1146–MAX1149

DC ACCURACY (Note 1)

Resolution 14 Bits

Relative Accuracy (Note 2) INL ±0.7 ±2 LSB

Differential Nonlinearity DNL -1.0 ±0.5 +1.5 LSB

Offset Error ±10 LSB

Offset Temperature Coefficient 0.3 ppm/°C

Gain Error (Note 3) ±20 LSB

Gain Temperature Coefficient ±0.8 ppm/°C

Channel-to-Channel Offset

Matching

Channel-to-Channel Gain

Matching

DYNAMIC SPECIFICATIONS (1kHz sine-wave input, 2.5V

Signal-to-Noise Plus Distortion

Ratio

Total Harmonic Distortion THD Up to the 5th harmonic -96 -88 dB

Spurious-Free Dynamic Range SFDR 84 98 dB

Channel-to-Channel Crosstalk (Note 4) -85 dB

Small-Signal Bandwidth SSBW -3dB point 3.0 MHz

Full-Power Bandwidth FPBW SINAD > 68dB 2.0 MHz

CONVERSION RATE

Conversion Time (Note 5) t

ADC

Continuous Power Dissipation (T

+ 0.3V)

DD

+ 0.3V)

DD

+ 0.3V)

DD

+ 0.3V)

DD

REFADJ

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

SINAD 77 81 dB

CONV

External clock, 2.1MHz 15 SCLK cycles 7.2

Internal clock 6 8

= VDD, C

P-P

20 TSSOP (derate 10.9mW/°C above +70°C) .............879mW

Operating Temperature Ranges

MAX114_ BC_ _ ..................................................0°C to +70°C

MAX114_ BE_ _ ...............................................-40°C to +85°C

Storage Temperature Range .............................-60°C to +150°C

Lead Temperature (soldering, 10s) .................................+300°C

= 0, f

= 2.2µF, external +4.096V reference at REF (MAX1146/

REF

= T

A

MIN

, full-scale analog input, 116ksps, 2.1MHz external clock)

COM

to T

, unless otherwise noted. Typical values are at

MAX

= +70°C)

A

= 2.1MHz, external clock (50%

SCLK

±1 LSB

±1 LSB

µs

2 _______________________________________________________________________________________

Page 3

多通道、真差分、串行、

位

14

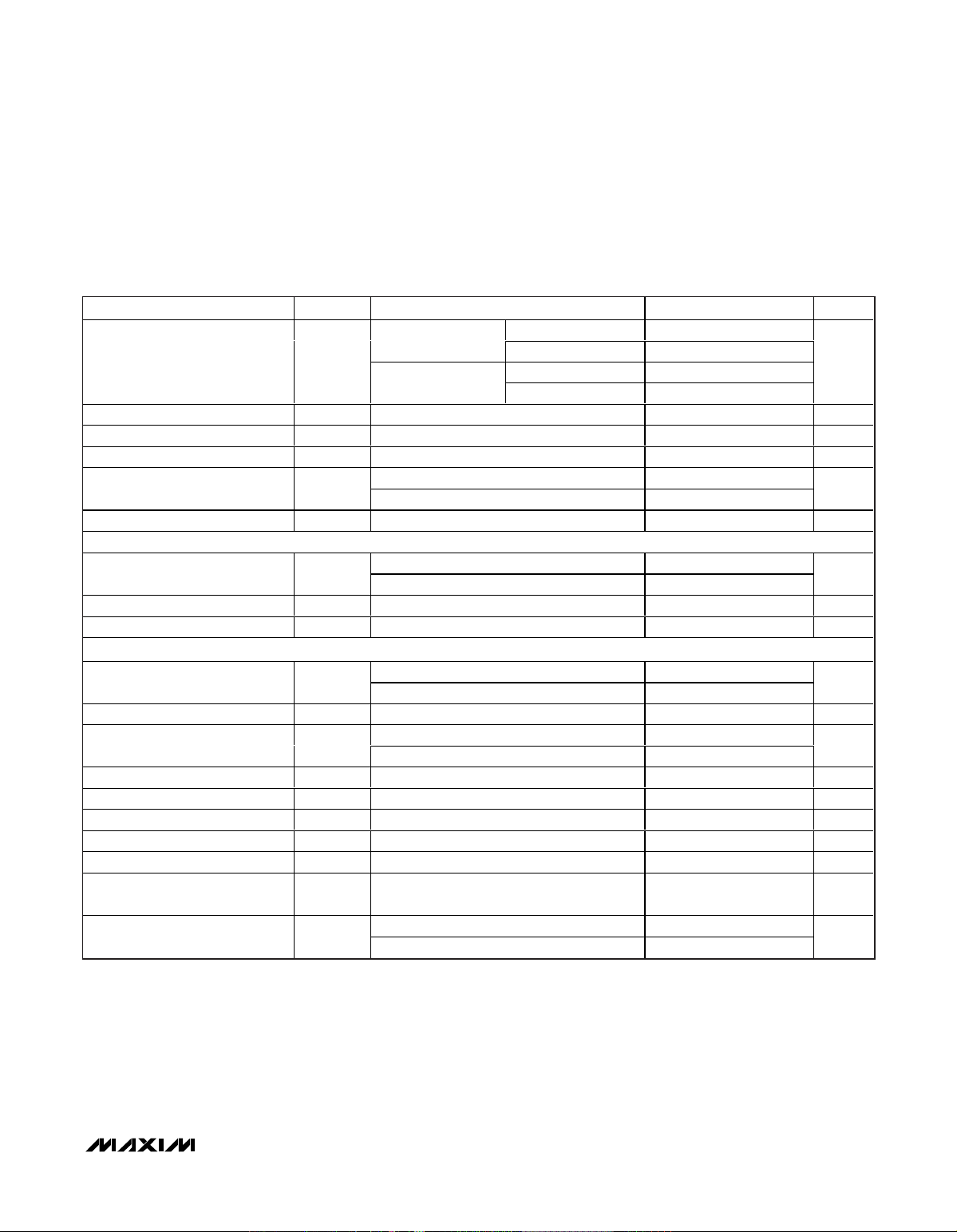

ELECTRICAL CHARACTERISTICS (continued)

(VDD= 5V (MAX1146/MAX1148), VDD= 3.3V (MAX1147/MAX1149), SHDN = VDD, V

duty cycle), 18 clocks/conversion (116ksps), V

MAX1148), external 2.500V reference at REF (MAX1147/MAX1149), T

= +25°C.)

T

A

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Throughput Rate f

T/H Acquisition Time t

Aperture Delay t

Aperture Jitter t

Serial Clock Frequency f

Internal Clock Frequency 2.1 MHz

ANALOG INPUTS (CH0—CH7, COM)

Input Voltage Range, SingleEnded and Differential (Note 6)

Multiplexer Leakage Current On/off-leakage current, VCH_ = 0 to V

Input Capacitance 18 pF

INTERNAL REFERENCE (C

REF Output Voltage V

REF Short-Circuit Current I

V

Tempco (Note 7)

REF

Load Regulation 0 to 0.2mA output load (Note 8) 2.0 mV

Capacitive Bypass at REF 2

Capacitive Bypass at REFADJ 0.01 µF

REFADJ Output Voltage 1.250 V

REFADJ Input Range ±18 mV

REFADJ Logic High

Reference Buffer Voltage Gain

REF

SAMPLE

ACQ

AD

AJ

SCLK

= 2.2 F, C

REF

REFSC

REFADJ

Internal clock mode,

f

SCLK

External clock mode,

f

SCLK

External clock mode 0.1 2.1

Internal clock mode 0 2.1

Unipolar, COM = 0 V

Bipolar, COM = V

REFADJ

MAX1147/MAX1149, TA = +25°C 2.480 2.500 2.520

MAX1146/MAX1148, TA = +25°C 4.076 4.096 4.116

REF = DGND 20 mA

MAX114_ BC _ _ ±30 ±50

MAX114_ BE _ _ ±40 ±60

Pull REFADJ high to disable the internal

bandgap reference and reference buffer

MAX1147/MAX1149 2.000

MAX1146/MAX1148 3.277

= VDD, C

= 2.1MHz

= 2.1MHz

= 0.01 F)

= 2.2µF, external +4.096V reference at REF (MAX1146/

REF

= T

A

REF

to T

MIN

18 clocks/conversion 60.3

24 clocks/conversion 51.5

18 clocks/conversion 116.66

24 clocks/conversion 87.50

/ 2, single-ended ±V

= 0, f

COM

, unless otherwise noted. Typical values are at

MAX

DD

= 2.1MHz, external clock (50%

SCLK

1.4 µs

20 ns

<50 ps

0

±0.01 ±1 µA

-

V

DD

0.25V

REF

REF

ADC

ksps

MHz

/ 2

ppm/°C

MAX1146–MAX1149

V

V

µF

V

V/V

_______________________________________________________________________________________ 3

Page 4

多通道、真差分、串行、

位

14

ELECTRICAL CHARACTERISTICS (continued)

(VDD= 5V (MAX1146/MAX1148), VDD= 3.3V (MAX1147/MAX1149), SHDN = VDD, V

duty cycle), 18 clocks/conversion (116ksps), V

MAX1148), external 2.500V reference at REF (MAX1147/MAX1149), T

= +25°C.)

T

A

EXTERNAL REFERENCE AT REF

REF Input Voltage Range V

REF Input Current I

REF Input Resistance 68 k

DIGITAL INPUTS (DIN, SCLK, CS, SHDN)

Input High Voltage V

MAX1146–MAX1149

Input Low Voltage V

Input Hysteresis V

Input Leakage I

Input Capacitance C

DIGITAL OUTPUT (DOUT, SSTRB)

Output-Voltage Low V

Output-Voltage High V

Tri-State Leakage Current I

Tri-State Output Capacitance C

POWER REQUIREMENTS

Positive Supply Voltage V

Supply Current (Note 8) I

Shutdown Supply Current

(Note 8)

Power-Supply Rejection (Note 9) PSR External reference ±0.2 mV

ADC

= 0, f

REFADJ

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

REF

REF

HYST

IN

OL

OH

OUT

DD

DD

Shutdown 0.01 10

V

IH

V

IL

IN

I

SINK

I

SOURCE

CS = V

L

CS = V

MAX1147/MAX1149 2.7 3.6

MAX1146/MAX1148 4.75 5.25

Normal

operation, fullscale input

Fast power-down 230

Full power-down 0.3

SHDN = DGND 0.3 10

= VDD, C

< 3.6V 2.0

DD

> 3.6V 3.0

DD

= 2mA 0.4 V

= 2mA VDD - 0.5 V

DD

DD

= 2.2µF, external +4.096V reference at REF (MAX1146/

REF

= T

A

MIN

External

reference

Internal reference at

116ksps

COM

to T

, unless otherwise noted. Typical values are at

MAX

116ksps 1.1 1.5

10ksps 0.12

1ksps 0.012

= 2.1MHz, external clock (50%

SCLK

V

1.5

325

325 450

0.2 V

10 pF

10 pF

1.9 2.4 mA

230

DD

50mV

0.8 V

±1 µA

±10 µA

+

V

µA

V

V

mA

µA

4 _______________________________________________________________________________________

Page 5

多通道、真差分、串行、

位

14

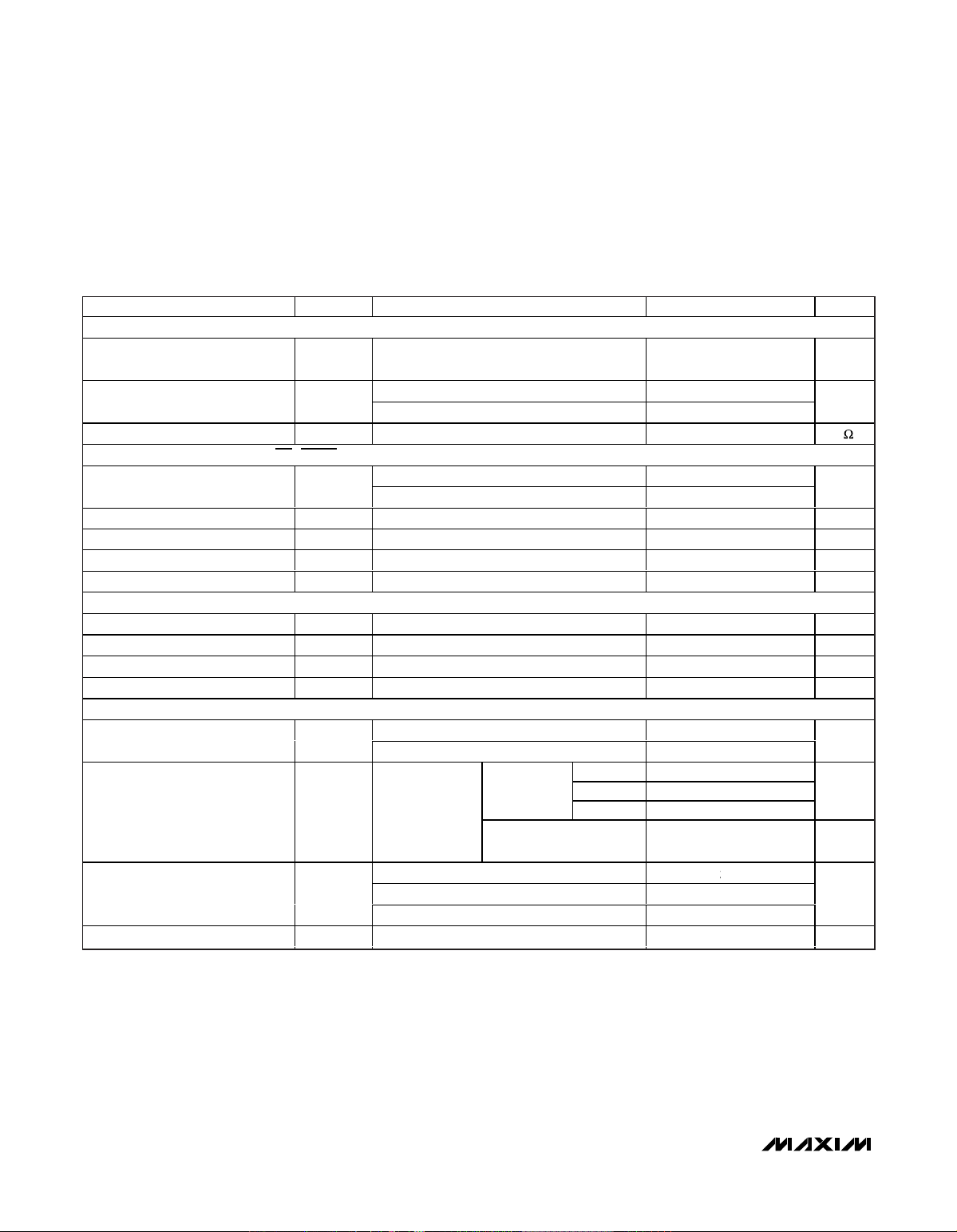

TIMING CHARACTERISTICS

(VDD= 4.75V to 5.25V (MAX1146/MAX1148), VDD= 2.7V to 3.6V (MAX1147/MAX1149), SHDN = VDD, V

external clock (50% duty cycle), 18 clocks/conversion (116ksps), V

for the MAX1146/MAX1148, external 2.500V reference at REF for the MAX1147/MAX1149, T

Typical values are at T

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

DIN to SCLK Setup Time t

DIN to SCLK Hold Time t

SCLK Fall to Output Data Valid t

CS Fall to DOUT Enable t

CS Rise to DOUT Disable t

SHDN Rise CS Fall to SCLK Rise

Time

SHDN Rise CS Fall to SCLK Rise

Hold Time

SCLK Clock Frequency f

SCLK Pulse-Width High t

SCLK Pulse-Width Low t

CS Fall to SSTRB Output Enable t

CS Rise to SSTRB Output Disable t

SSTRB Rise to SCLK Rise t

SCLK Fall to SSTRB Edge t

CS Pulse Width t

Note 1: Tested at VDD= 3.0V (MAX1147/MAX1149) or 5.0V(MAX1146/MAX1148); V

Note 2: Relative accuracy is the deviation of the analog value at any code from its theoretical value after the full-scale range has

been calibrated.

Note 3: Offset nulled. Measured with external reference.

Note 4: “On” channel grounded; full-scale 1kHz sine wave applied to all “off” channels.

Note 5: Conversion time defined as the number of clock cycles multiplied by the clock period; clock has 50% duty cycle. (See

Figures 8–11.)

Note 6: The common-mode range for the analog inputs is from AGND to V

Note 7: Digital inputs equal V

Note 8: External load should not change during conversion for specified accuracy.

Note 9: Measured as (V

MAX1146/MAX1148. V

= +25°C.) (Figures 1, 2, and 3)

A

DS

DH

DOV

DOE

DOD

t

CSS

t

CSH

SCLK

CH

CL

STE

STD

SCK

SCST

CSW

or DGND.

DD

x 3.6V) - (V

FS

DD

x 2.7V) for the MAX1147/MAX1149 and (V

FS

= 3.6V to 2.7V for MAX1147/MAX1149 and VDD= 5.25V to 4.75V for the MAX1146/MAX1148.

C

= 50pF 10 80 ns

LOAD

C

= 50pF 120 ns

LOAD

C

= 50pF 120 ns

LOAD

External clock mode 0.1 2.1

Internal clock mode 0 2.1

Internal clock mode 100 ns

Internal clock mode 100 ns

External clock mode only 120 ns

External clock mode only 120 ns

Internal clock mode only 0 ns

REFADJ

= VDD, C

.

DD

= 2.2µF, external +4.096V reference at REF

REF

COM

FS

= T

A

= 0; unipolar single-ended input mode.

x 5.25V) - (V

to T

MIN

50 ns

0ns

50 ns

50 ns

100 ns

x 4.75V) for the

FS

= 0, f

COM

, unless otherwise noted.

MAX

ADC

= 2.1MHz,

SCLK

MHz

80 ns

MAX1146–MAX1149

_______________________________________________________________________________________ 5

Page 6

多通道、真差分、串行、

位

14

ADC

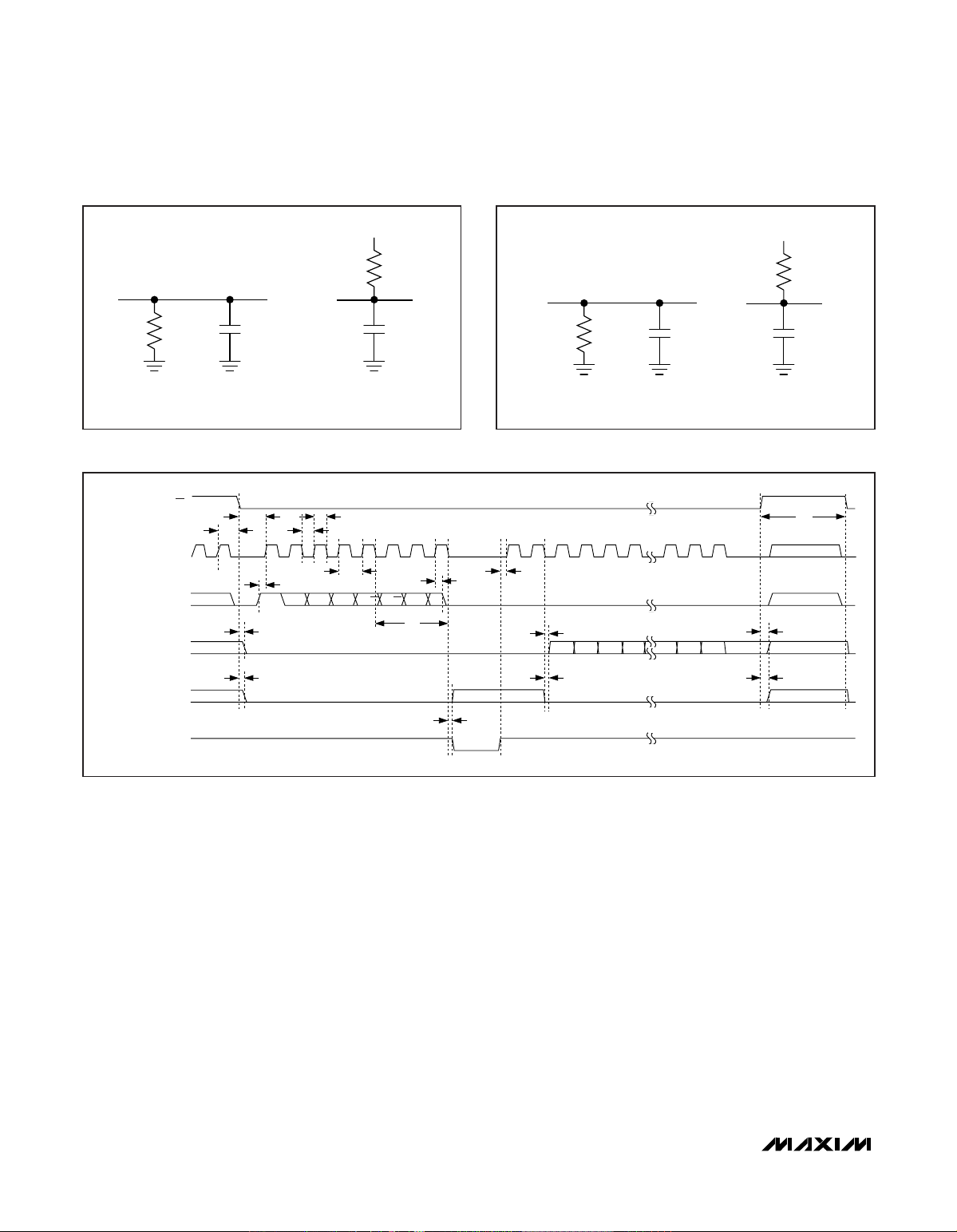

V

DD

V

DD

DOUT

a) HIGH-Z TO V

图

测试使能时间的负载电路

1.

MAX1146–MAX1149

(EXTERNAL CLOCK MODE)

(INTERNAL CLOCK MODE)

6kΩ

DGND

OH

CS

SCLK

DIN

DOUT

SSTRB

SSTRB

AND VOL TO V

t

CSH

t

DOE

HIGH-Z

t

STE

HIGH-Z

6kΩ

DOUT

t

CH

SGL/DIF UNI/BIP

C

LOAD

50pF

DGND

OL

t

t

DH

t

ACQ

t

SCST

SCK

C

LOAD

50pF

DGND

OH

b) HIGH-Z TO VOL AND VOH TO V

t

CSS

t

CL

189

1

f

SCLK

t

DS

START SEL2 SEL1 SEL0 PD1 PD0

DOUT

6kΩ

DGND

a) V

OH

图

测试禁止时间的负载电路

2.

t

DOV

D13 D12 D11 D10

t

SCST

6kΩ

DOUT

C

LOAD

50pF

DGND

C

50pF

DGND

TO HIGH-Z b) VOL TO HIGH-Z

t

CSW

24

t

t

DOD

HIGH-Z

STD

HIGH-Z

D2 D1 D0

LOAD

图

详细工作时序

3.

6 _______________________________________________________________________________________

Page 7

多通道、真差分、串行、

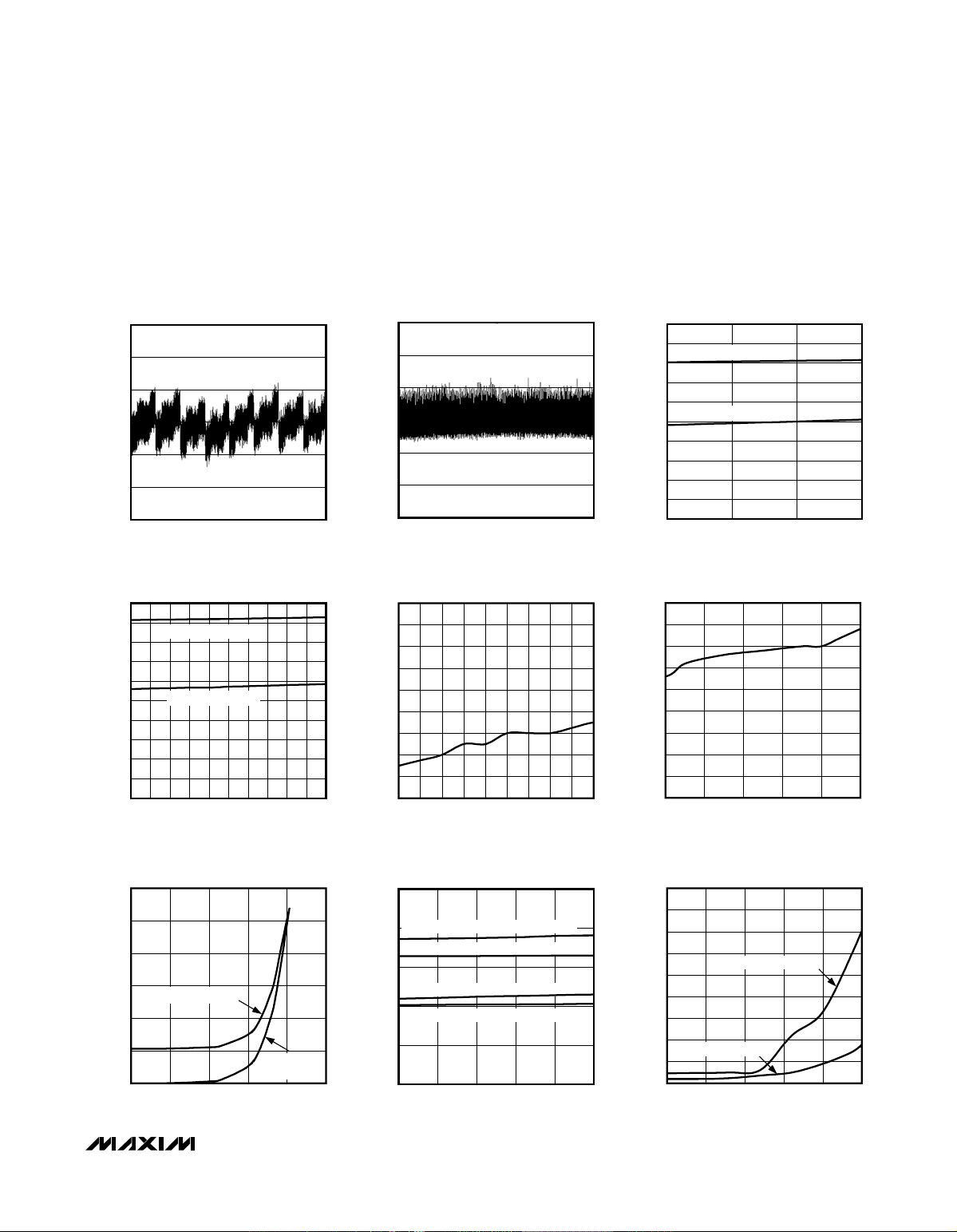

SHUTDOWN SUPPLY CURRENT

vs. SUPPLY VOLTAGE (MAX1146/MAX1148)

MAX1146 toc06

SUPPLY VOLTAGE (V)

SHUTDOWN SUPPLY CURRENT (µA)

5.155.054.954.85

0.05

0.10

0.15

0.20

0.25

0.30

0.35

0.40

0.45

0

4.75 5.25

14

___________________________________________________________________

(VDD= +5.0V (MAX1146/MAX1148), VDD= +3.3V (MAX1147/MAX1149), SHDN = VDD, V

(50% duty cycle), 18 clocks/conversion (116ksps), V

nal +2.500V reference at REF (MAX1147/MAX1149), C

INL vs. OUTPUT CODE

MAX1146 toc01

1.5

1.0

0.5

0

DNL (LSB)

-0.5

-1.0

-1.5

1.5

1.0

0.5

0

INL (LSB)

-0.5

-1.0

-1.5

0 16384

OUTPUT CODE

1228881924096

SUPPLY CURRENT vs. SUPPLY VOLTAGE

2.0

(MAX1146/MAX1148)

1.8

1.6

1.4

1.2

1.0

0.8

0.6

SUPPLY CURRENT (mA)

0.4

0.2

0

INTERNAL REFERENCE

EXTERNAL REFERENCE

4.75 5.25

SUPPLY VOLTAGE (V)

MAX1146 toc04

5.205.155.05 5.104.85 4.90 4.95 5.004.80

vs. SUPPLY VOLTAGE (MAX1147/MAX1149)

1.8

1.6

1.4

1.2

1.0

0.8

0.6

0.4

SHUTDOWN SUPPLY CURRENT (µA)

0.2

0

2.7 3.6

= VDD, external +4.096V reference at REF (MAX1146/MAX1148), exter-

REFADJ

REF

= 2.2µF, C

= 50pF, TA= +25°C, unless otherwise noted.)

LOAD

DNL vs. OUTPUT CODE

0 16384

OUTPUT CODE

1228881924096

SHUTDOWN SUPPLY CURRENT

3.53.43.2 3.32.9 3.0 3.12.8

SUPPLY VOLTAGE (V)

= 0, f

COM

2.0

1.8

MAX1146 toc02

1.6

1.4

1.2

1.0

0.8

0.6

SUPPLY CURRENT (mA)

0.4

0.2

MAX1146 toc05

= 2.1MHz, external clock

SCLK

SUPPLY CURRENT vs. SUPPLY VOLTAGE

(MAX1147/MAX1149)

INTERNAL REFERENCE

EXTERNAL REFERENCE

0

2.7 3.6

SUPPLY VOLTAGE (V)

位

ADC

典型工作特性

3.33.0

MAX1146–MAX1149

MAX1146 toc03

SUPPLY CURRENT

vs. CONVERSION RATE

1200

1000

800

600

400

SUPPLY CURRENT (µA)

200

FAST POWER-DOWN

0

0.01 1000

CONVERSION RATE (ksps)

SHUTDOWN SUPPLY CURRENT

vs. TEMPERATURE

MAX1146/MAX1148

MAX1147/MAX1149

603510-15

TEMPERATURE (°C)

FULL

POWER-DOWN

1001010.1

2.5

MAX1146 toc07

2.0

1.5

1.0

SUPPLY CURRENT (mA)

0.5

0

SUPPLY CURRENT vs. TEMPERATURE

MAX1146/MAX1148 INTERNAL REFERENCE

MAX1147/MAX1149 INTERNAL REFERENCE

MAX1146/MAX1148 EXTERNAL REFERENCE

MAX1147/MAX1149 EXTERNAL REFERENCE

-40 85

TEMPERATURE (°C)

603510-15

MAX1146 toc08

4.5

4.0

3.5

3.0

2.5

2.0

1.5

1.0

SHUTDOWN SUPPLY CURRENT (µA)

0.5

0

-40 85

_______________________________________________________________________________________ 7

MAX1146 toc09

Page 8

多通道、真差分、串行、

E

位

14

ADC

_______________________________________________________________

(VDD= +5.0V (MAX1146/MAX1148), VDD= +3.3V (MAX1147/MAX1149), SHDN = VDD, V

(50% duty cycle), 18 clocks/conversion (116ksps), V

nal +2.500V reference at REF (MAX1147/MAX1149), C

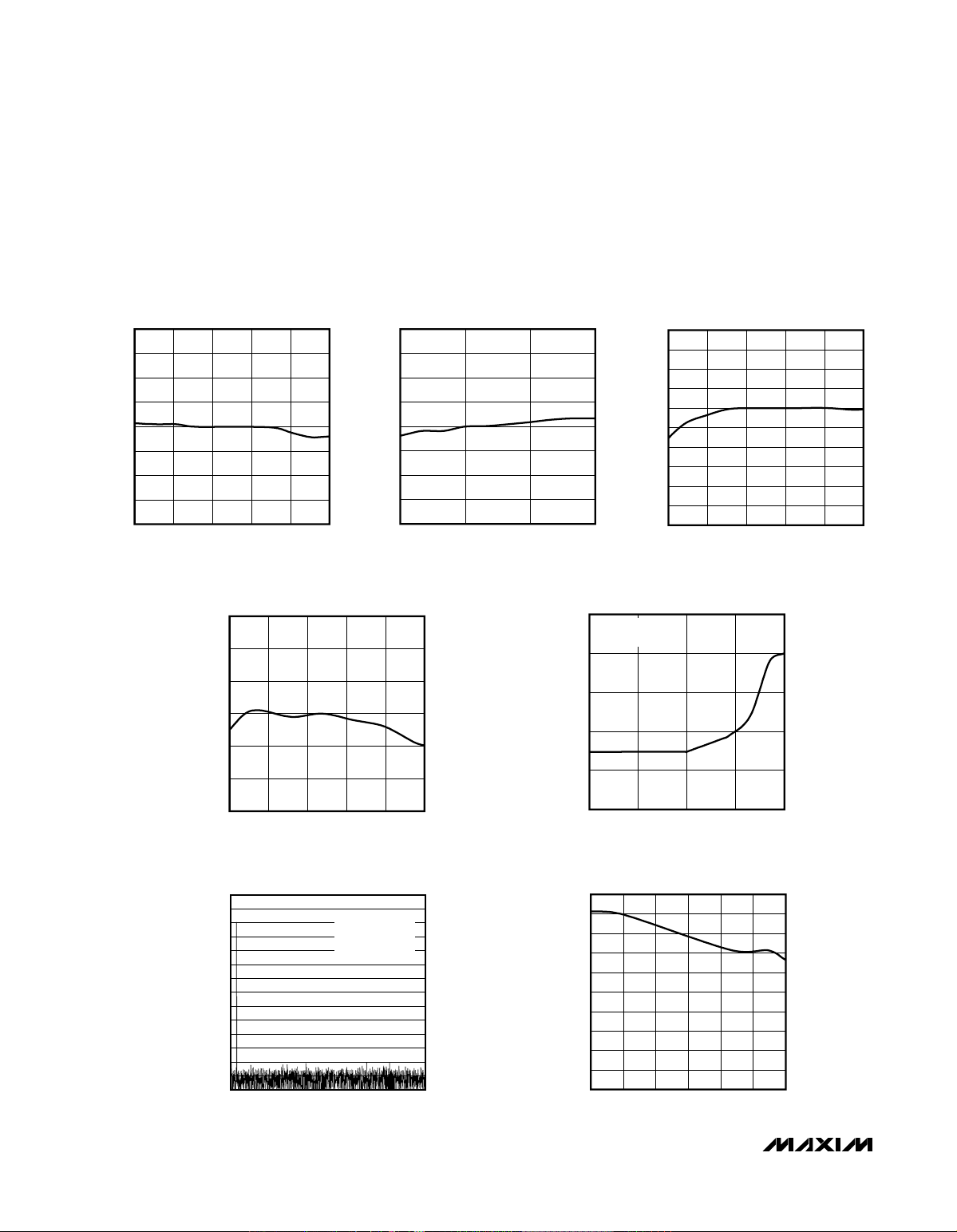

REFERENCE VOLTAGE vs. SUPPLY VOLTAG

(MAX1146/MAX1148)

4.0980

4.0975

4.0970

4.0965

4.0960

4.0955

REFERENCE VOLTAGE (V)

4.0950

MAX1146–MAX1149

4.0945

4.0940

4.75 5.25

5.155.054.85 4.95

SUPPLY VOLTAGE (V)

MAX1146 toc10

REFERENCE VOLTAGE vs. SUPPLY VOLTAGE

2.5020

2.5015

2.5010

2.5005

2.5000

2.4995

REFERENCE VOLTAGE (V)

2.4990

2.4985

2.4980

2.7 3.6

= VDD, external +4.096V reference at REF (MAX1146/MAX1148), exter-

REFADJ

= 2.2µF, C

REF

= 50pF, TA= +25°C, unless otherwise noted.)

LOAD

(MAX1147/MAX1149)

3.33.0

SUPPLY VOLTAGE (V)

REFERENCE VOLTAGE vs. TEMPERATURE

(MAX1147/MAX1149)

2.503

2.502

2.501

2.500

2.499

REFERENCE VOLTAGE (V)

2.498

MAX1146 toc13

REFERENCE BUFFER POWER-UP DELAY

2500

2000

1500

DELAY (µs)

1000

500

= 0, f

COM

4.100

4.099

MAX1146 toc11

4.098

4.097

4.096

4.095

4.094

4.093

REFERENCE VOLTAGE (V)

4.092

4.091

4.090

vs. TIME IN SHUTDOWN

C

= 4.7µF

REF

= 0.01µF

C

REFADJ

典型工作特性(续

= 2.1MHz, external clock

SCLK

REFERENCE VOLTAGE vs. TEMPERATURE

-40 85

(MAX1146/MAX1148)

603510-15

TEMPERATURE (°C)

MAX1146 toc14

)

MAX1146 toc12

2.497

-40 85

TEMPERATURE (°C)

603510-15

0

0.001 10

TIME IN SHUTDOWN (s)

10.10.01

EFFECTIVE NUMBER OF BITS

20

10

0

-10

-20

-30

-40

-50

-60

AMPLITUDE (dB)

-70

-80

-90

-100

-110

-120

0

FFT PLOT

fIN = 1kHz

f

SAMPLE

V

DD

FREQUENCY (Hz)

= 116ksps

= 5V/3V

13.0

12.9

MAX1146 toc15

50004000300020001000

12.8

12.7

12.6

12.5

12.4

12.3

EFFECTIVE NUMBER OF BITS

12.2

12.1

12.0

155

vs. FREQUENCY

FREQUENCY (kHz)

8 _______________________________________________________________________________________

MAX1146 toc16

4637281910

Page 9

多通道、真差分、串行、

OFFSET ERROR vs. SUPPLY VOLTAGE

(MAX1147/MAX1149)

MAX1146 toc17

SUPPLY VOLTAGE (V)

OFFSET ERROR (LSB)

3.33.0

-4

-2

0

2

4

6

-6

2.7 3.6

OFFSET ERROR vs. SUPPLY VOLTAGE

(MAX1146/MAX1148)

MAX1146 toc18

SUPPLY VOLTAGE (V)

OFFSET ERROR (LSB)

5.155.054.954.85

-7

-4

-5

-6

-2

-3

-1

0

-8

4.75 5.25

_______________________________________________________________

(VDD= +5.0V (MAX1146/MAX1148), VDD= +3.3V (MAX1147/MAX1149), SHDN = VDD, V

(50% duty cycle), 18 clocks/conversion (116ksps), V

nal +2.500V reference at REF (MAX1147/MAX1149), C

= VDD, external +4.096V reference at REF (MAX1146/MAX1148), exter-

REFADJ

= 2.2µF, C

REF

= 50pF, TA= +25°C, unless otherwise noted.)

LOAD

COM

= 0, f

SCLK

位

14

ADC

典型工作特性(续

= 2.1MHz, external clock

MAX1146–MAX1149

)

GAIN ERROR vs. SUPPLY VOLTAGE

(MAX1147/MAX1149)

6

4

2

0

GAIN ERROR (LSB)

-2

-4

-6

2.7 3.6

SUPPLY VOLTAGE (V)

3.33.0

CHANNEL-TO-CHANNEL GAIN MATCHING

vs. SUPPLY VOLTAGE (MAX1147/MAX1149)

6

4

2

0

-2

GAIN MATCHING (LSB)

-4

-6

2.7 3.6

SUPPLY VOLTAGE (V)

3.33.0

MAX1146 toc19

MAX1146 toc21

GAIN ERROR vs. SUPPLY VOLTAGE

(MAX1146/MAX1148)

6

4

2

0

GAIN ERROR (LSB)

-2

-4

-6

4.75 5.25

SUPPLY VOLTAGE (V)

5.155.054.85 4.95

CHANNEL-TO-CHANNEL GAIN MATCHING

vs. SUPPLY VOLTAGE (MAX1146/MAX1148)

6

4

2

0

-2

GAIN MATCHING (LSB)

-4

-6

4.75 5.25

SUPPLY VOLTAGE (V)

5.155.054.954.85

MAX1146 toc20

XMAX1146 toc22

_______________________________________________________________________________________ 9

Page 10

多通道、真差分、串行、

CHANNEL-TO-CHANNEL OFFSET MATCHING

vs. TEMPERATURE

MAX1146 toc26

TEMPERATURE (°C)

OFFSET MATCHING (LSB)

6035-15 10

-4

-2

0

2

4

6

-6

-40 85

GAIN ERROR vs. TEMPERATURE

MAX1146 toc27

TEMPERATURE (°C)

GAIN ERROR (LSB)

6035-15 10

-4

-2

0

2

4

6

-6

-40 85

CHANNEL-TO-CHANNEL OFFSET MATCHING

vs. SUPPLY VOLTAGE (MAX1147/MAX1149)

MAX1146 toc24

SUPPLY VOLTAGE (V)

OFFSET MATCHING (LSB)

3.33.0

-4

-2

0

2

4

6

-6

2.7 3.6

CHANNEL-TO-CHANNEL OFFSET MATCHING

vs. SUPPLY VOLTAGE (MAX1146/MAX1148)

MAX1146 toc25

SUPPLY VOLTAGE (V)

OFFSET MATCHING (LSB)

5.155.054.85 4.95

-4

-2

0

2

4

6

-6

4.75 5.25

CHANNEL-TO-CHANNEL GAIN MATCHING

vs. TEMPERATURE

MAX1146 toc23

TEMPERATURE (°C)

GAIN MATCHING (LSB)

6035-15 10

-4

-2

0

2

4

6

-6

-40 85

位

14

ADC

_______________________________________________________________

(VDD= +5.0V (MAX1146/MAX1148), VDD= +3.3V (MAX1147/MAX1149), SHDN = VDD, V

(50% duty cycle), 18 clocks/conversion (116ksps), V

nal +2.500V reference at REF (MAX1147/MAX1149), C

= VDD, external +4.096V reference at REF (MAX1146/MAX1148), exter-

REFADJ

= 2.2µF, C

REF

= 50pF, TA= +25°C, unless otherwise noted.)

LOAD

COM

= 0, f

MAX1146–MAX1149

典型工作特性(续

= 2.1MHz, external clock

SCLK

)

10 ______________________________________________________________________________________

OFFSET ERROR vs. TEMPERATURE

6

4

2

0

-2

OFFSET ERROR (LSB)

-4

-6

-40 85

TEMPERATURE (°C)

6035-15 10

MAX1146 toc28

Page 11

多通道、真差分、串行、

位

14

_______________________________________________________________________

PIN

引脚

名称

MAX1148

MAX1149

10 10 SHDN

11 11 REF

12 12 REFADJ

13 13 AGND Analog Ground

14 14 DGND Digital Ground

15 15 DOUT

16 16 SSTRB

17 17 DIN

18 18 CS

19 19 SCLK

20 20 V

— 5–8 N.C. No Connection. Not internally connected.

MAX1146

MAX1147

1 1 CH0

2 2 CH1

3 3 CH2

4 4 CH3

5 — CH4

6 — CH5

7 — CH6

8 — CH7

9 9 COM

NAME FUNCTION

模拟输入

Analog Inputs

Common Input. Negative analog input in single-ended mode. COM sets zero-code voltage in

公共输入端。单端模式下为模拟负输入。单极性和双极性模式下,

unipolar and bipolar mode.

Active-Low Shutdown Input. Pulling SHDN low shuts down the device reducing supply current

低电平有效关断输入。

to 0.2µA. Driving shutdown high enables the devices.

Reference-Buffer Output/ADC Reference Input. Reference voltage for analog-to-digital

基准缓冲输出

conversion. In internal reference mode, the MAX1146/MAX1148 V

为

V

MAX1147/MAX1149 V

Bandgap Reference Output and Reference Buffer Input. Bypass to AGND with a 0.01µF

带隙基准输出和基准缓冲输入。采用

capacitor. Connect REFADJ to V

基准和基准缓冲放大器。

buffer amplifier.

模拟地

数字地

Serial Data Output. Data is clocked out at the falling edge of SCLK when CS is low. DOUT is

串行数据输出。CS置低时,数据在

high impedance when CS is high.

Serial Strobe Output. In internal clock mode, SSTRB goes low when the ADC conversion

串行触发输出。在内部时钟模式下,

begins, and goes high when the conversion is finished. In external clock mode, SSTRB pulses

在外部时钟模式下,

high for two clock periods before the MSB decision. SSTRB is high impedance when CS is high

(外部时钟模式)。

(external clock mode).

Serial Data Input. Data is clocked in at the rising edge of SCLK when CS is low. DIN is high

串行数据输入。CS置低时,数据在

impedance when CS is high.

Active-Low Chip Select. Data is not clocked into DIN unless CS is low. When CS is high, DOUT

低电平有效片选。只有CS置低时,数据才可同步输入

is high impedance.

Serial Clock Input. Clocks data in and out of the serial interface and sets the conversion speed

串行时钟输入。将数据同步输入或输出串口,在外部时钟模式下决定转换速率 (占空比必须在

至

in external clock mode. (Duty cycle must be 40% to 60%.)

正电源。用

Positive Supply Voltage. Bypass to AGND with a 0.1µF capacitor.

DD

无连接。内部未连接。

+4.096V,MAX1147/MAX1149的V

REF

之间)。

60%

基准输入。模数转换的基准电压。内部基准模式下,

/ADC

SSTRB在MSB

电容旁路至

0.1µF

置低,器件关断,电源电流降至

SHDN

is +2.500V.

REF

AGND

0.01µF

to disable the internal bandgap reference and reference-

DD

SCLK

ADC

输出前保持两个时钟周期的高电平。CS置高时,

SCLK

。

功能

COM

。置高,使能器件。

0.2µA

is +4.096V, and the

为

+2.500V

REF

电容旁路至

下降沿同步输出。CS置高时,

转换开始后,

上升沿同步输入。CS置高时,

AGND。REFADJ连至V

SSTRB

DIN。CS

REF

。

置低,转换完成后,

置高时,

设置零编码输出的电压。

MAX1146/MAX1148

DD

为高阻。

DOUT

为高阻。

DIN

为高阻。

DOUT

ADC

引脚说明

的

禁止内部带隙

置高。

SSTRB

为高阻

SSTRB

40%

MAX1146–MAX1149

______________________________________________________________________________________ 11

Page 12

多通道、真差分、串行、

位

14

ADC

______________________________

MAX1146–MAX1149 ADC

采用逐次逼近技术和输入

详细说明

电路将模拟信号转换成14位数字输出。灵活的串口提供

了与微处理器

图5为

MAX1148/MAX1149

的方便连接。图4为典型应用电路,

(µP)

的原理图。

真差分模拟输入和采样/保持

MAX1146–MAX1149

用器

(MUX)

、两个

两个开关电容数模转换器

CH0

MAX1146–MAX1149

ANALOG

INPUTS

2.2µF

图

典型应用电路

4.

CS

SCLK

DIN

SHDN

CH0

CH1

CH2

CH3

CH4

CH5

CH6

CH7

COM

REFADJ

REF

CH1

CH2

CH3

CH4

CH5

CH6

CH7

REF

COM

INPUT

SHIFT

REGISTER

ANALOG

INPUT

MUX

+1.250V

BANDGAP

REFERENCE

模拟输入结构包括一个模拟输入复

T/H

MAX1148

MAX1149

AGND DGND

电容、

(DAC) (图6)

V

DD

SHDN

SCLK

CS

DIN

SSTRB

DOUT

REFADJ

CONTROL

LOGIC

T/H

20kΩ

开关、一个比较器和

T/H

。

10Ω

0.1µF 4.7µF

0.01µF

INTERNAL

CLOCK

OUTPUT

SHIFT

REGISTER

CLOCK

SAR

IN

A

= 2.0V/V

V

ADC

REF

OUT

MAX1149

V

DD

V

DD

I/O

SCK

I/O

MOSI

I/O

MISO

T/H

在单端模式下,模拟输入

IN-

连至

。在差分模式下,

COM

MUX将IN+

IN+和IN-

等被选择的模拟输入对。根据表1–5选择模拟输入通道。

在控制字节第五个

选通道。此时,

T/H

下降沿,模拟输入复用器接通所

SCLK

开关处于采样位置,

样模拟输入信号。 在控制字节第八个

断开,

MUX

上的电荷作为输入信号的采样。输入

C

T/H-

开关位置参见图

在转换期间,开关电容

开关切换到保持位置,维持

T/H

。

8–11

进行调整,在14位精度内将

DAC

连至所选通道,

连接

CH0/CH1

C

T/H+

SCLK

和

采

C

T/H-

下降沿,

和

C

T/H+

MUX和T/H

比较器输入电压恢复为0。此操作需要15个转换时钟周

期,相当于将

转移至二进制加权电容

C

T/H+

和

上

C

18pF x (V

T/H-

,形成模拟输入信号的数字

DAC

IN+

- V

IN-

的电荷

)

输出。

转换完成后,

开关由保持位置切回采样位置,

T/H

MUX

切换到最近指定的位置。在内部时钟模式下,转换在

µP

SSTRB

八个

采样输入信号所需的

V

SS

如果输入信号源阻抗高,则采样时间延长。

MAX1149

的上升沿完成。在外部时钟模式下,转换在第十

下降沿完成。

SCLK

时间是模拟输入源阻抗的函数。

T/H

MAX1146–

提供三个

SCLK

周期

(t

ACQ

,期间

)

T/H

电容必

须获取表征输入信号的电荷,一般是控制字节的最后三

DOUT

SSTRB

个

T/H

式中,

输入

C

T/H-

为减小源阻抗较高时的采样误差,可在模拟输入和

之间连

但是与源阻抗一起构成了一个RC滤波器,限制了模拟输

入带宽。对于较大的源阻抗,可采用

。 应尽量减小输入源阻抗

SCLK

电容在分配时间内完成充电。

t

= 11.5 × (R

ACQ

R

SOURCE

MUX和T/H

为模拟输入源阻抗,

开关电阻之和),

SOURCE

和输入寄生电容之和)。

的电容。该输入电容可减小输入AC阻抗,

100pF

(R

SOURCE

+ RIN) × C

等于

R

IN

等于

C

IN

MAX4430

,以保证

)

IN

2.6kΩ

18pF (C

等缓冲放

(模拟

T/H+

AGND

,

大器,以保证模拟输入信号的完整性。

V

DD

DGND

AGND

图

原理图

5.

12 ______________________________________________________________________________________

Page 13

ANALOG INPUT MUX

多通道、真差分、串行、

位

14

ADC

MAX1146–MAX1149

图

等效输入电路

6.

CH0

CH1

CH2

CH3

CH4

CH5

CH6

CH7

COM

IN+

IN-

HOLD

HOLD

HOLD

C

T/H+

TRACK

C

T/H-

TRACK

TRACK

REF

REF

MAX1148

MAX1149

14-BIT

CAPACITIVE

DAC

14-BIT

CAPACITIVE

DAC

输入带宽

MAX1146–MAX1149

输入采样电路具有

3.0MHz

带宽。 可实现高速瞬变信号数字采样, 采用欠采样

技术,可测量带宽超过

采样速率的周期信号。为避

ADC

免其它高频信号与被采样信号混叠,建议采用抗混叠

滤波。

小信号

模拟输入保护

内部保护二极管将模拟输入钳位在

这些二极管仅允许模拟输入在

之间变化,以免对器件造成损坏。对于高精度转

0.3V)

换,输入不能比

AGND低50mV

注意:模拟输入高于电源

______________________________________________________________________________________ 13

(AGND - 0.3V) 至(VDD+

,也不能比

时,将电流限制在

50mV

和

V

DD

AGND

V

DD

高

之间。

50mV

2mA

。

。

快速查看

图7所示电路可用于快速评估

MAX1148/MAX1149

每次转换前,需要使用

输入一个控制字节。连接

输入控制字节

$FF HEX (

钟模式下的单端单极性转换,转换之间不关断。在外

部时钟模式下,14位转换结果的

SSTRB

入, 可改变

钟周期(图

SCLK

输出两个时钟周期的高脉冲。改变

DOUT

10)

输出位的顺序。每次转换需18个时

。所有

SSTRB和DOUT

下降沿。

MAX1148/MAX1149

DIN至V

参见表

,可通过时钟

DD

,即触发

1)

MSB

的改变均出现在

SCLK向DIN

CH7

移出

DOUT

的模拟输

CH7

SCLK

外部时

前,

。

Page 14

多通道、真差分、串行、

位

14

ADC

10Ω

A

IN

0.01µF

0.01µF

CH7

REFADJ

MAX1148

MAX1149

V

DIN

SHDN

SCLK

DOUT

SSTRB

DD

0.1µF 4.7µF

EXTERNAL CLOCK

10Ω

V

DD

OSCILLOSCOPE

SCLK

DOUT*

V

REF

2.2µF

REF

COM

CS

DGND

AGND

CH1 CH2 CH3 CH4

MAX1146–MAX1149

MAX1149 V

MAX1148 V

图

快速查看电路

7.

表

控制字节格式

1.

BIT NAME DESCRIPTION

7 (MSB) START Start bit. The first logic 1 bit after CS goes low defines the beginning of the control byte.

6 SEL2

5 SEL1

4 SEL0

3 SGL/DIF

2 UNI/BIP

1 PD1

0 (LSB) PD0

= +2.500V

REF

= +4.096V

REF

Channel-select bits. The channel-select bits select which of the eight channels are used for the conversion

(Tables 2, 3, 4, and 5).

1 = single ended, 0 = differential. Selects single-ended or differential conversions. In single-ended mode,

input signal voltages are referred to COM. In differential mode, the voltage difference between two channels

is measured.

1 = unipolar, 0 = bipolar. Selects unipolar or bipolar conversion mode. In unipolar mode, connect COM to

AGND to perform conversion from 0 to V

from 0 to V

Selects clock and power-down modes.

PD1 = 0 and PD0 = 0 selects full power-down mode*.

PD1 = 0 and PD0 = 1 selects fast power-down mode*.

PD1 = 1 and PD0 = 0 selects internal clock mode.

PD1 = 1 and PD0 = 1 selects external clock mode.

V

≤ AIN ≤ V

COM

. See Table 7.

REF

REF

*FULL-SCALE ANALOG INPUT, CONVERSION RESULT = $FFF HEX

. In bipolar mode, connect COM to V

REF

SSTRB

/2 to perform conversion

REF

起始位自动复位关断模式。

*

14 ______________________________________________________________________________________

Page 15

多通道、真差分、串行、

位

14

ADC

MAX1146–MAX1149

表

2. MAX1148/MAX1149

SEL2 SEL1 SEL0 CH0 CH1 CH2 CH3 CH4 CH5 CH6 CH7 COM

000+ -

100 + -

001 + -

101 + -

010 + -

110 + -

011 +-

111 +-

在单端模式下的通道选择

(SGL/ DIF = 1)

表

3. MAX1148/MAX1149

SEL2 SEL1 SEL0 CH0 CH1 CH2 CH3 CH4 CH5 CH6 CH7

000+ -

001 +-

010 +-

011 +-

100 - +

101 -+

110 - +

111 -+

表

4. MAX1146/MAX1147

通道选择

SEL2 SEL1 SEL0 CH0 CH1 CH2 CH3 COM

000+ -

100 + -

001 + -

101 +-

初次上电时,内部上电复位电路使能

的内部时钟模式,

时

SSTRB

低后,

始之前,

向

DIN

SCLK

(SGL/DIF = 1)

MAX1146–MAX1149

置高。不能在电源电压稳定前启动转换。CS置

上出现第一个逻辑1被认为是起始位。转换开

DIN

输出为零。

DOUT

同步输入一个控制字节启动一次转换。CS置低时,

的每个上升沿将来自

在差分模式下的通道选择

在单端模式下的

上电复位

MAX1146–MAX1149

准备好进行转换

启动转换

的一位移入

DIN

MAX1146–

(SGL/DIF = 0)

表

5. MAX1146/MAX1147

通道选择

SEL2 SEL1 SEL0 CH0 CH1 CH2 CH3

000+-

001 +-

100-+

101 -+

MAX1149

认为是控制字节的

任何逻辑0均无效。表1为控制字节的格式。

MAX1146–MAX1149

件。对于

和采样沿。设置

SPI和QSPI

节。采用

次8位传输实现一次转换(第一个8位配置

个8位同步输出14位转换结果)。

(SGL/DIF = 0)

内部移位寄存器。CS置低后的第一个逻辑1被

。该起始位之前同步进入

MSB

兼容

,在

SPI

总线可在发送一个字节的同时接收一个字

典型应用电路

控制寄存器中选择正确的时钟极性

SPI

CPOL = 0和CPHA = 0。MICROWIRE

(图4)

在差分模式下的

DIN

SPI/QSPI和MICROWIRE

,最简单的软件接口仅需三

,其余两

ADC

的

器

、

______________________________________________________________________________________ 15

Page 16

多通道、真差分、串行、

位

14

ADC

数字输出

在单极性输入模式下,数字输出为标准二进制格式(图

在双极性输入模式下,数字输出为二的补码格式(图

数据在

下降沿同步输出,

SCLK

MSB

先出。

时钟模式

MAX1146–MAX1149

以使用内部时钟来驱动逐次逼近转换。数据移入移出

MAX1146–MAX1149

外部时钟模式可实现最快吞吐率

频率范围为

0.1MHz至2.1MHz

佳噪声性能,这是因为数字接口在转换期间可以为空闲

状态,其串行时钟频率范围为0至

式允许

MAX1146–MAX1149

控制字节的

请求一次转换,然后同步返回结果。

CPU

PD1和PD0

MAX1146– MAX1149

均被使能。图8-图11是可用时钟模式。

既可以使用外部串行时钟也可

使用外部时钟。

(116ksps)

,其串行时钟

。内部时钟模式可提供最

2.1MHz

。内部时钟模

位用来设置时钟和关断模式。

上电时为内部时钟模式,所有电路

外部时钟

在外部时钟模式下,外部时钟移入移出数据,同时还驱

动模数转换。在控制字节的最后一位移入后,

SSTRB

出两个时钟周期的高脉冲。逐次逼近转换结果每一位在

随后14个

为高电平时,

CS

下降沿出现在

SCLK

SSTRB和DOUT

DOUT上(图8和10)

为高阻。

14)

15)

输

。当

如果外部串行时钟频率低于

。

。

转换时间超过

在

140µs

内完成,否则

,则需采用内部时钟模式。转换必须

140µs

配置为内部时钟模式时,

生转换所需时钟,µP不再产生驱动

可在方便时以最大

SSTRB

在转换开始时置低,当转换完成后置高。

置低最长时间为

2.1MHz

8.0µs

100kHz

电容的压降会影响转换结果。

T/H

MAX1146–MAX1149

,期间,

或串行时钟中断导致

转换的时钟,并

SAR

的时钟速率读取转换结果。

应保持低电平以实

SCLK

现最佳噪声性能。

一个内部寄存器用来在转换过程中存储数据。在转换完

成后的任何时刻,可由

出 。 在

DOUT

SSTRB

输出转换结果的

余位(图9和

置高后的第二个

。

11)

为达到最高转换精度,

在内部时钟转换期间

(t

CONV

将数据由此寄存器同步输

SCLK

SCLK

,然后是

MSB

MSB

MAX1146–MAX1149

应保持静止。在转换中不要

)

将CS置高。CS置高将退出当前转换。在

个零以确保下一个起始位被识别。当选择内部时钟模

18

式时,CS置高,

升沿表明

MAX1146– MAX1149

SSTRB

并不进入高阻状态。

已经完成转换。之后

可在方便时读取转换结果。

内部时钟

在内部产

SSTRB

时钟下降沿,

先出格式的其

的数字

DIN

SSTRB

I/O

同步输入

的上

µP

CS

SCLK

DIN

SSTRB

HIGH-Z

DOUT

HIGH-Z

INPUT MUX

SET ACCORDING TO PREVIOUS CONTROL BYTE SET TO CB1

INPUT T/H

图

外部时钟模式

8.

16 ______________________________________________________________________________________

18916 24

CB1

SEL2

START

—— 24时钟/

SEL1

TRACK

SEL0

SGL/DIF

UNI/BIP

转换时序

PD1

PD0

t

ACQ

D13 D12 D11 D10 D9 D8 D6 D5 D4 D3 D2 D1 D0D7

OPEN

t

CONV

HIGH-Z

HIGH-Z

RESET TO CB1

TRACKHOLD

Page 17

多通道、真差分、串行、

位

14

ADC

MAX1146–MAX1149

CS

SCLK

DIN

SSTRB

DOUT

INPUT MUX

SET ACCORDING TO PREVIOUS CONTROL BYTE SET TO CB1

INPUT T/H

START

HIGH-Z

图9.内部时钟模式

CS

SCLK

DIN

SSTRB

DOUT

INPUT MUX

START

HIGH-Z

SET ACCORDING TO PREVIOUS

CONTROL BYTE

18916 24

CB1

SEL1 SEL0

SEL2

TRACK

时钟/转换时序

——

24

18

CB1 CB2

SEL1

SEL2

SEL0

SGL/DIF

PD1

SGL/DIF

PD0

UNI/BIP

t

PD1

UNI/BIP UNI/BIP

t

ACQ

t

ACQ

CONV

OPEN

14

PD0

D13 D12 D11 D10 D9 D8 D6 D5 D4 D3 D2 D1 D0D7

RESET TO CB1

10 1811

SEL2

SEL1

START

t

CONV

D13 D12 D5 D4 D3 D2 D1 D0 D3 D2 D1 D0

SET TO CB1

SEL0

SGL/DIF

HIGH-Z

TRACKHOLD

14

PD0

PD1

t

ACQ

D13 D1210D5 D4

SET TO CB2

START

11

SEL2

SEL1

SEL0

SGL/DIF

15

UNI/BIP

图

INPUT T/H

10.

外部时钟模式

HOLD

——

18

时钟/转换时序

______________________________

TRACK

HOLD

应用信息

空闲模式

当转换结果的所有位被同步输出或在

零后,器件进入空闲状态。

同步输入18个

DIN

起始位

仅CS下降沿并不能启动一次转换。CS置低后同步输入

的第一个逻辑1为起始位,并作为控制字节的第一位。识

别出起始位后,器件在

的第八个下降沿,控制字节最后一位同步输入后开

SCLK

第五个下降沿开始采样。在

SCLK

始转换。起始位定义如下:

______________________________________________________________________________________ 17

DIN

TRACK

转换器空闲的任何时间,CS置低,第一个同步输入

1)

的逻辑1。

DIN

HOLD

或

2) DOUT

DIN

同步输出当前转换结果第5位后,同步输入

的第一个逻辑

1 (图10和11)

。

在当前转换完成之前触发CS,将退出转换,清空输出寄

存器。

如果转换期间CS保持低电平,则

的最快转换速度为每次18个时钟周期。图10和11为

个

周期进行一次转换的串口时序。

SCLK

MAX1146–MAX1149

18

Page 18

多通道、真差分、串行、

位

14

ADC

CS

SCLK

SSTRB

DOUT

INPUT MUX

INPUT T/H

MAX1146–MAX1149

图

内部时钟模式

11.

DIN

18

CB1 CB2

SEL0

SEL2 SEL1

START

HIGH-Z

SET ACCORDING TO PREVIOUS

CONTROL BYTE

——

18

TRACK HOLD

时钟/转换时序

SGL/DIF

UNI/BIP

PD1

PD0

t

t

ACQ

CONV

OPEN RESET TO CB2OPEN

14

RESET TO CB1

硬关断和软关断模式

MAX1146–MAX1149

模式。

置低转换器进入硬关断模式。转换立即中止,电

SHDN

源电流减至

0.01µF,C

C

REFADJ

和

300nA

REF

C

REF

= 2.2µF

准时,器件由快速关断模式启动无需唤醒时间。

通过控制字节的

转换过程完成后,进入软关断模式。此时串口保持有

效,最后的转换结果可同步输出。在完全关断模式,只

有串口工作,电源电流减小到

只有带隙基准和串口工作,电源电流减小到

用外部基准时,快速关断模式下的电源电流降至

表

*

内部基准缓冲启动时间和旁路电容

6.

C

启动时间由

*C

REFADJ

0.01µF 4.7µF 2ms

0.1µF 10µF 25ms

C

REFADJ

可提供一个硬关断和两个软关断

。当使用内部基准缓冲,且

时,器件启动时间为

C

2ms

REFADJ

。较大的

容值会增加启动时间(表6)。采用外部基

PD1和PD0

位选择软关断模式(表1)。当

。在快速关断模式,

300nA

230µA

120µA

REF

控制。

POWER-UP TIMES FROM AN

EXTENDED POWER-DOWN

10 18

11

SEL2 SEL1

START

D13 D12

D5 D4 D3 D2 D1 D0

TRACK

MAX1146–MAX1149

从软关断模式中唤醒(表1)。当采用内部基准缓冲, 且

C

REFADJ

2ms

(表6)

=

唤醒时间。

MAX1146–MAX1149

决定

ADC

MAX1146–MAX1149

;采

。

基准通过一个

容旁路

缓冲具有

压。

MAX1147/MAX1149

益, 在

用最小

MAX1146–MAX1149

1)将REFADJ

外部基准(图

将外部基准连至

2)

SEL0

SGL/DIF

UNI/BIP

14

PD1

PD0

t

SET TO CB2SET TO CB1

t

ACQ

CONV

HOLD

TRACK

D13 D12

10

11

SEL2

START

D5 D4

收到控制字节的起始位后,自动

= 0.01µF,C

。 较大的

C

REFADJ

REF

= 2.2µF

和

C

时,器件启动时间为

容值会增加启动时间

REF

。采用外部基准时,器件由快速关断模式启动无需

基准电压

可采用内部或外部基准。基准电压

输入范围,还决定满量程输出值(表7)。

内部基准

20kΩ

含有一个内部

电阻连接至

1.250V

REFADJ

REFADJ至AGND。MAX1146/MAX1148

3.277V/V

增益,在

REF

提供

的基准缓冲具有

REF

2.2µF

提供

+2.500V

的电容将

基准电压。使用内部基准时,

旁路至

REF

AGND

带隙基准。该

。采用

0.01µF

+4.096V

2.000V/V

。

的基准

基准电

外部基准

以两种方式使用外部基准:

连接至

12)

REFADJ

,禁止内部基准缓冲,

V

DD

。

,使用内部基准缓冲(图

REF

13)

电

增

接

。

18 ______________________________________________________________________________________

Page 19

SAR

REF

ADC

REFERENCE

BUFFER

MAX1146–

MAX1149

图

12.

外部基准连至

DISABLED

20kΩ

1.250V

BANDGAP

REFERENCE

REF

方式1允许直接应用

输入阻抗典型值为

REF

部基准必须能提供最大

小于

10Ω

。用

0.1µF

电容旁路

REF

V

DD

DGND

AGND

1.5V至V

。进行转换时,接

10kΩ

210µA

3.000V

0.1µF

REFADJ

0.1µF

+ 50mV

DD

电流,并且其输出阻抗应

REF至AGND

MAX6163

OUT

+5V

的外部基准。

可改善输出

阻抗。

方式2利用内部基准缓冲来减小外部基准负载。

输入阻抗典型值为

基准必须提供最小

100Ω。MAX1146/MAX1148

MAX1147/MAX1149

外部基准电压乘以基准缓冲增益即为

压,在

测得的基准电压值必须在

REF

。在转换时,接

20kΩ

100µA

电流,并且输出阻抗应小于

具有

2.000V/V

基准缓冲具有

增益。接

SAR ADC

1.5V至V

REFADJ

3.277V/V

REFADJ

DD

+5V

IN

GND

的外

REF

REFADJ

的外部

增益,

的基准电

+ 50mV

的

多通道、真差分、串行、

位

14

+3.3V

24kΩ

MAX1146–

100kΩ

图

基准调整电路

13.

之间。用

旁路

REF至AGND

0.01µF

510kΩ

电容旁路

。

0.047µF

REFADJ至AGND,2.2µF

表7为单极性和双极性模式的满量程电压范围。

MAX1146–MAX1149

输出数据编码在单极性模式时为

二进制格式,双极性模式时为二的补码格式,

(V

REF

邻整数倍

和双极性输入/输出

MAX1146–MAX1149

,其中N为位数

/2N)

值之间的中点。图14和图15分别为单极性

LSB

(I/O)

的串口与

完全兼容。如串口可用,将

CPU

产生

串行时钟。最大可选时钟频率为

ADC

。量化电平分界点位于相

(14)

的传输函数。

SPI、QSPI和MICROWIRE

CPU

SPI和MICROWIRE

使用

SPI (图16a) 或MICROWIRE

CPOL = CPHA = 0

。需要读两个8位来获取

MAX1149

REFADJ

的串口设为主机,并由

接口(图

16b)

ADC

ADC

电容

传输函数

1 LSB =

串口

2.1MHz

。

接口

时,设置

的全部

MAX1146–MAX1149

表

注意:模拟输入的共模范围为

满度和零度

7.

INPUT AND OUTPUT

MODES

Single-Ended Mode V

Differential Mode V

______________________________________________________________________________________ 19

UNIPOLAR MODE BIPOLAR MODE

ZERO SCALE FULL SCALE

V

REF

V

REF

AGND至V

COM

IN-

DD

。

+ V

+ V

COM

IN-

NEGATIVE FULL

SCALE

−

REF

+VV

COM

2

−

V

REF

V

+ −

IN

2

ZERO SCALE

V

COM

V

IN-

POSITIVE FULL

SCALE

++V

REF

V

COM

2

+

V

REF

+

V

−

IN

2

Page 20

多通道、真差分、串行、

位

14

1...111

1...110

1...101

1...100

ADC

1 LSB =

16384

V

REF

V

V

REF

V

1...111

1...110

1...101

1...100

REF

1 LSB =

REF

16384

BINARY OUTPUT CODE (LSB)

0...011

MAX1146–MAX1149

0...010

0...001

0...000

图

单极性传输函数

14.

位结果。

14

0123 16383

DOUT

INPUT VOLTAGE (LSB)

数据在串行时钟下降沿转换,在

16381

上升沿同步进入µP。第一个8位数据流为转换结果前

位,以

开始。第二个8位数据流含其余6位。

MSB

QSPI

采用高速

MAX1146–MAX1149

位来获取

16

钟的下降沿转换,在

QSPI

接口(图

17)

支持最大

的全部14位结果。

ADC

SCLK

时设置

CPOL = 0,CPHA = 0

2.1MHz的f

DOUT

SCLK

数据在串行时

上升沿同步进入µP。前14位

为所需数据。

PIC16/PIC17 SSP

MAX1146– MAX1149

PIC16/PIC17

微控制器

兼容于使用同步串口

。如需建立

(µC)

SPI

(SSP)

通信,可按照

REF

V

SCLK

接口

。需要读

模块接口

模块的

0...001

0...000

0...111

0...011

0...010

TWO'S COMPLEMENT BINARY OUTPUT CODE (LSB)

0...001

0...000

0123 8191

图

双极性传输函数

15.

图18所示连接控制器,并将

按表8和表9所示初始化同步串口控制寄存器

8

和同步串口状态寄存器

PIC16/PIC17 µC

允许同时进行8位数据的同步收和发。

需要连续读两个8位获取

,

据在串行时钟下降沿转换,在

。第一个8位数据流为转换结果前8位, 以

µC

8193 16383

8192

INPUT VOLTAGE (LSB)

PIC16/PIC17

(SSPSTAT)

全部14位结果。

ADC

始。第二个数据流含其余各位,即D5至D0。

16381

。在

上升沿同步进入

SCLK

REF

V

配置为主机。

(SSPCON)

模式中,

SPI

数

DOUT

开

MSB

I/O

SCK

MISO

SPI

图

16a. SPI

20 ______________________________________________________________________________________

连接

V

DD

SS

CS

SCLK

DOUT

MAX1146–

MAX1149

MICROWIRE

图

16b. MICROWIRE

I/O

SK

SI

连接

CS

SCLK

DOUT

MAX1146–

MAX1149

Page 21

QSPI

SCK

MISO

多通道、真差分、串行、

位

14

ADC

MAX1146–MAX1149

SCK

SDI

I/O

PIC16/PIC17

V

DD

V

DD

CS

V

DD

SS

CS

SCLK

DOUT

MAX1146–

MAX1149

SCLK

DOUT

CS

MAX1146–

MAX1149

图

17. QSPI

表

8. SSPCON

WCOL Bit 7 X Write collision detection bit.

SSPOV Bit 6 X Receive overflow detect bit.

SSPEN Bit 5 1

CKP Bit 4 0 Clock polarity select bit. CKP = 0 for SPI master mode selection.

SSPM3 Bit 3 0

SSPM2 Bit 2 0

SSPM1 Bit 1 0

SSPM0 Bit 0 1

表

9. SSPSTAT

SMP Bit 7 0

CKE Bit 6 1

连接

图

18. PIC16/ PIC17

寄存器详细内容

CONTROL BIT

PICI6/PICI7

SETTINGS

SYNCHRONOUS SERIAL-PORT CONTROL REGISTER (SSPCON)

Synchronous serial port enable bit:

0: Disables serial port and configures these pins as I/O port pins.

1: E nab l es ser i al p or t and confi g ur es S C K, S D O, and S C I p i ns as ser i al - p or t p i ns.

Synchronous serial port mode select bit. Sets SPI master mode and selects

= f

F

CLK

OSC

/ 16.

寄存器详细内容

CONTROL BIT

D/A Bit 5 X Data address bit.

P Bit 4 X Stop bit.

S Bit 3 X Start bit.

R/W Bit 2 X Read/write bit information.

UA Bit 1 X Update address.

BF Bit 0 X Buffer full status bit.

MAX1146–MAX1149

SETTINGS

SYNCHRONOUS SERIAL-PORT STATUS REGISTER (SSPSTAT)

SPI data input sample phase. Input data is sampled at the middle of the data

output time.

SPI clock edge select bit. Data is transmitted on the rising edge of the serial

clock.

GND GND

微控制器的

SPI

接口连接

______________________________________________________________________________________ 21

Page 22

多通道、真差分、串行、

位

14

ADC

TMS32OLC3x

图19是外部时钟模式下,

MAX1146–MAX1149与TMS320

接口的应用电路。图20是该接口电路的时序图。采用以

下步骤启动

1) TMS320将CLKX (

出时钟,

MAX1146–MAX1149

发送时钟) 配置为高电平有效的输

CLKR (TMS320

平有效的输入时钟。

MAX1146–MAX1149的SCLK

通过

2)

TMS320的XF_I/O

的CS置低,将数据同步输入

。

DIN

TMS320的CLKX和CLKR

转换,并读取结果:

接收时钟) 配置为高电

输入连在一起。

端口将

MAX1146–MAX1149

MAX1146 –MAX1149

3)向MAX1146–MAX1149写8位(1XXXXX11)

化转换,将其设为外部时钟模式。根据具体应用参考

MAX1146–MAX1149

表1选择合适的

4) TMS320的FSR

SSTRB

TMS320

5) TMS320

XXXXX

输入监视

输出。

SSTRB

可以接收来自

在随后

16

值。

MAX1146–MAX1149

的下降沿表明正在进行转换,

MAX1146–MAX1149

个

的上升沿读入每一位数

SCLK

的数据。

据。这16位数据包括14位转换结果,其余两位可以

忽略。

6) CS

置高, 在启动下一次转换前, 禁止

MAX1149

操作。

MAX1146–

接口

与

的

,初始

的

布板、接地和旁路

为实现最佳系统性能,必须进行仔细的PC板布板。应具

有独立的模拟地和数字地。并确保模拟信号和数字信号

互相远离。不要将模拟和数字(特别是时钟) 走线平行放

置,或者将数字走线紧靠在器件下面。

图4是推荐的系统地线连接方式。在

拟接地点,在

DGND

建立一个数字接地点。连接所有的

模拟地至星形模拟地。连接数字地至星形数字地。直接

在器件处连接数字接地点和模拟接地点。为实现最佳

噪声性能,返回星形电源地的走线应为低阻并尽可能

的短。

TMS320LC3x

XF

CLKX

CLKR

DX

DR

FSR

CS

SCLK

DIN

DOUT

SSTRB

AGND

MAX1146–

MAX1149

建立一个模

图

19. MAX1146–MAX1149与TMS320

CS

SCLK

DIN

SSTRB

DOUT

图

20. TMS320

22 ______________________________________________________________________________________

START SEL2 SEL1 SEL0 PD1 PD0

串口时序图

SGL/DIF

UNI/BIP

MSB B12 B1 LSB

的串口

HIGH-Z

HIGH-Z

Page 23

电源的高频噪声会降低器件高速性能。采用

V

DD

电容将电源旁路至数字地。尽量缩短电容引线长度

4.7µF

以实现最佳电源噪声抑制。

形成的低通滤波器可抑制较强的电源噪声。

0.1µF

电容串一个

______________________________

10Ω

参数定义

0.1µF

电阻,

和

积分非线性

积分非线性

可以是最佳线性拟合的直线,也可以是传输函数端点间的

直线,但要消除失调和增益误差影响。

的静态线性参数测量采用的是端点法。

是实际传输函数与直线的偏差。该直线

(INL)

MAX1146–MAX1149

微分非线性

微分非线性

异。小于

且不会丢码。

1 LSB的DNL

(DNL)

是实际步长和

误差可以保证传输函数单调,并

理想值之间的差

1 LSB

孔径定义

孔径抖动

延迟

(tAD)

的时间差。

是相邻采样点之间时间间隔的变化。孔径

(tAJ)

是指采样时钟上升沿和实际采样发生时刻之间

信噪比

对于由数字采样完全恢复的波形,信噪比

程模拟输入

值。 理想的,理论最小模数转换噪声仅源于量化误差,

直接由

实际上,除量化噪声外,还存在其它噪声, 如 : 热噪

声、基准噪声、时钟抖动等。

声的比值,此噪声包括所有频谱分量减去基频、前5次谐

波和直流失调。

(RMS值) 和RMS

分辨率(N位) 决定:

ADC

SNR = (6.02 x N + 1.76)dB

量化误差(残留误差) 的比

SNR为RMS

信号和

(SNR)

是满量

RMS

噪

多通道、真差分、串行、

位

14

信号与噪声和失真比

信号与噪声和失真比

其它所有输出等效

ADC

SINAD(dB) = 20 x log (SignalRMS / NoiseRMS)

有效位数

的整体精度。理想的

范围与

总谐波失真

频幅度的比值。可以表示为:

其中,

无杂散动态范围

值与下一个最大失真分量

(ENOB)

的满量程范围一致时,可由下式计算

ADC

THD

log

=×

20

是基频幅度,

V

1

ENOB = (SINAD - 1.76) / 6.02

(THD)

(SINAD)

RMS

代表

ADC

ADC

是输入信号前5次谐波

⎛

VVVV

⎜

⎜

⎝

V

2

(SFDR)

是指基频(最大的信号分量

______________________________

TRANSISTOR COUNT: 5589

PROCESS: BiCMOS

是输入基频

值之比。

在指定输入频率和采样率下

误差仅由量化噪声构成。输入

RMS

2

2

+++

2

3

至

是2至5次谐波的幅度。

V

5

2

4

V

1

无杂散动态范围

值之比。

RMS

ADC

幅度与

RMS

有效位数

:

ENOB

总谐波失真

之和与基

⎞

2

5

⎟

⎟

⎠

) RMS

芯片信息

MAX1146–MAX1149

______________________________________________________________________________________ 23

Page 24

多通道、真差分、串行、

位

14

ADC

_______________________________________________________________________

TOP VIEW

MAX1146–MAX1149

CH0

CH1

CH2

N.C.

N.C.

N.C.

COM

SHDN

1

2

3

4

MAX1146

5

MAX1147

6

7

8

9

10

TSSOP

20

19

18

17

16

15

14

13

12

11

V

DD

SCLK

CS

DINCH3

SSTRB

DOUT

DGND

AGNDN.C.

REFADJ

REF

CH0

CH1

CH2

CH4

CH5

CH6

COM

SHDN

1

2

3

4

MAX1148

5

MAX1149

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

V

DD

SCLK

CS

DINCH3

SSTRB

DOUT

DGND

AGNDCH7

REFADJ

REF

TSSOP

引脚配置

24 ______________________________________________________________________________________

Page 25

多通道、真差分、串行、

位

14

_______________________________________________________________________

(本数据资料提供的封装图可能不是最近的规格,如需最近的封装外型信息,请查询 www.maxim-ic.com.cn/packages。)

ADC

MAX1146–MAX1149

封装信息

TSSOP4.40mm.EPS

MAXIM

北京

8328

免费电话:

电话:

010-6201 0598

传真:

010-6201 0298

Maxim不对Maxim

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 ____________________ 25

© 2005 Maxim Integrated Products Printed USA

北京办事处

信箱 邮政编码

800 810 0310

产品以外的任何电路使用负责,也不提供其专利许可。

100083

保留在任何时间、没有任何通报的前提下修改产品资料和规格的权利。

Maxim

是

Maxim Integrated Products, Inc.

的注册商标。

Loading...

Loading...