Datasheet MAS9264T95LD, MAS9264T95LC, MAS9264T95LB, MAS9264T95FS, MAS9264T95FE Datasheet (DYNEX)

...Page 1

MA9264

1/15

The MA9264 64k Static RAM is configured as 8192x8 bits and

manufactured using CMOS-SOS high performance, radiation hard,

1.5µm technology.

The design uses a 6 transistor cell and has full static operation with

no clock or timing strobe required. Address input buffers are deselected

when chip select is in the HIGH state.

See Application Note “Overview of the Dynex Semiconductor

Radiation Hard 1.5µm CMOS/SOS SRAM Range”.

FEATURES

■ 1.5µm CMOS-SOS Technology

■ Latch-up Free

■ Fast Access Time 70ns Typical

■ Total Dose 10

6

Rad(Si)

■ Transient Upset >10

11

Rad(Si)/sec

■ SEU 4.3 x 10

-11

Errors/bitday

■ Single 5V Supply

■ Three State Output

■ Low Standby Current 100µA Typical

■ -55°C to +125°C Operation

■ All Inputs and Outputs Fully TTL or CMOS

Compatible

■ Fully Static Operation

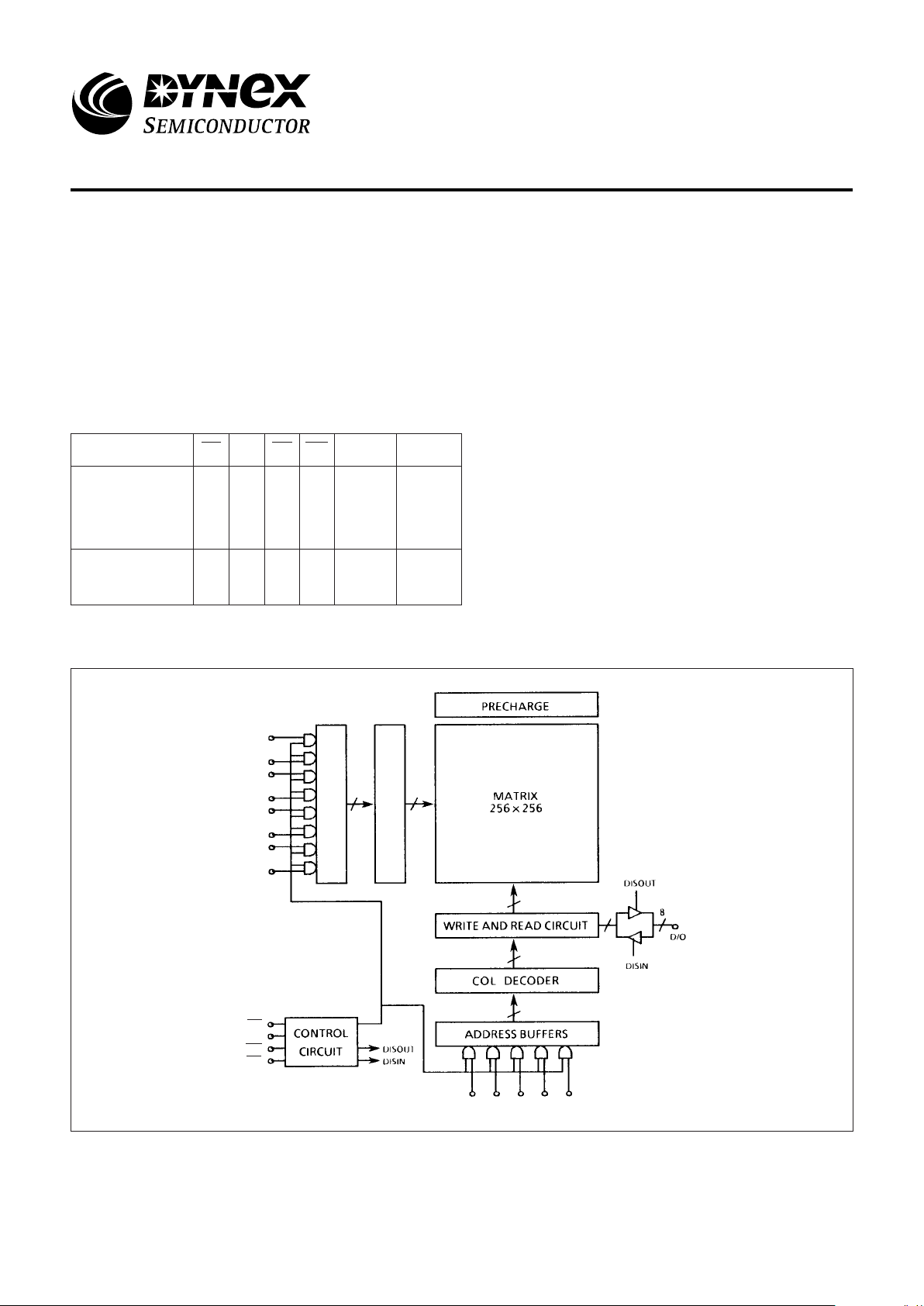

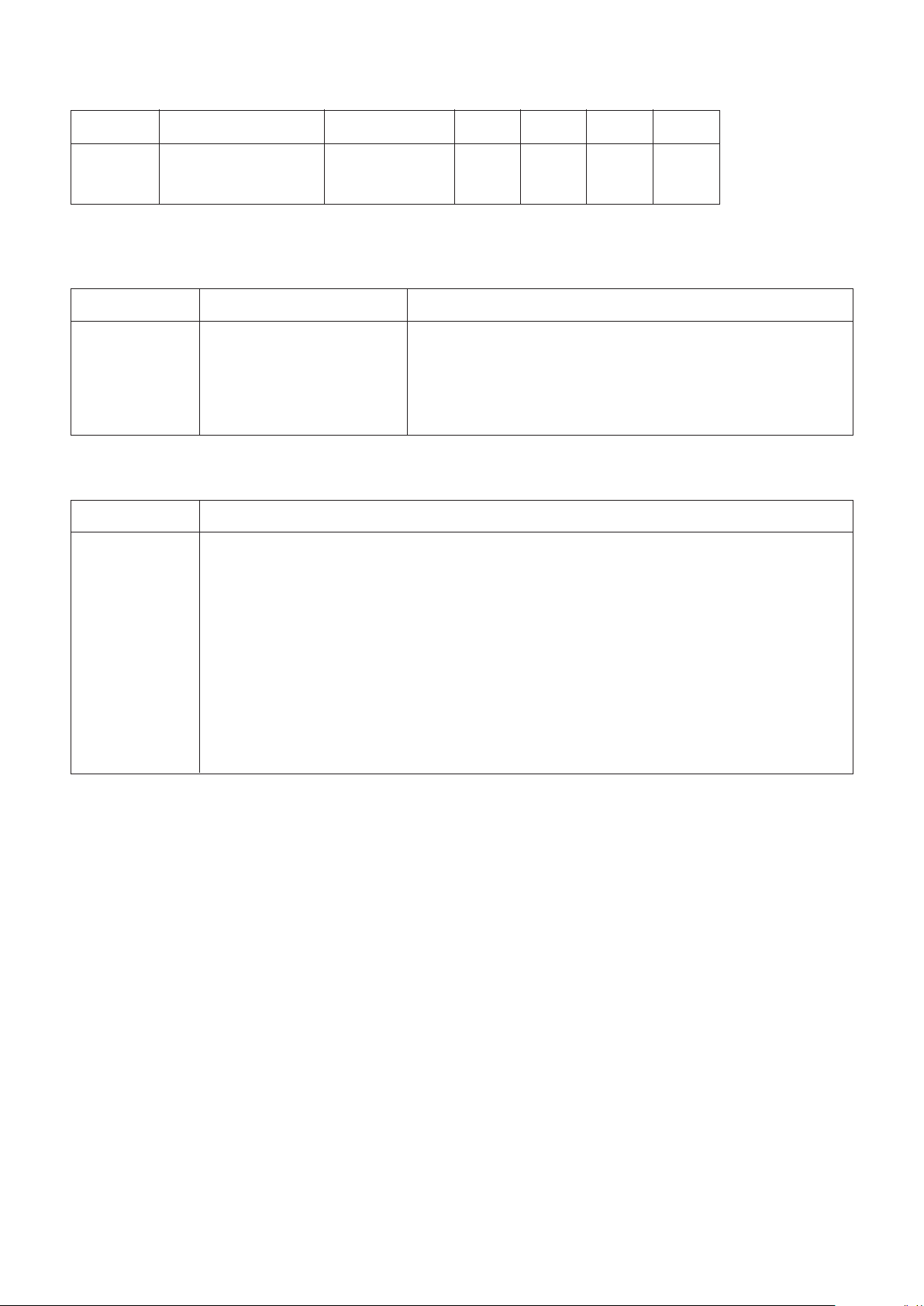

Operation Mode CS CE OE WE I/O Power

Read L H L H D OUT

Write L H X L D IN ISB1

Output Disable L H H H High Z

Standby H X X X High Z ISB2

XLXX X

Figure 1: Truth Table

Figure 2: Block Diagram

A12

A9

A8

A4

A3

A6

A5

A7

A

D

D

R

E

S

S

B

U

F

F

E

R

R

O

W

D

E

C

O

D

E

R

A10 A0 A1 A2 A11

CS

CE

WE

OE

MA9264

Radiation Hard 8192x8 Bit Static RAM

Replaces June 1999 version, DS3692-6.0 DS3692-7.0 January 2000

Page 2

MA9264

2/15

SIGNAL DEFINITIONS

A0-12

Address input pins which select a particular eight bit word within

the memory array.

D0-7

Bidirectional data pins which serve as data outputs during a read

operation and as data inputs during a write operation.

CS

Chip Select, which, at low level, activates a read or write

operation. When at a high level it defaults the SRAM to a

prechargencondition and holds the data output drivers in a high

impedance state.

WE

Write Enable which when at a low level enables a write and holds

data output drivers in a high impedance state. When at a high

level, it enables a read.

OE

Output Enable which when at a high level holds the data output

drivers in a high impedance state. When at a low level, data

output driver state is defined by CS, WE and CE. If this signal is

not used it must be connected to VSS.

CE

Chip Enable which when at a high level allows normal operation.

When at a low level it defaults the SRAM to a precharge

condition, disables the input circuits on all input pins and holds

the data output drivers in a high impedance state. If this signal

is not used it must be connected to VDD.

Page 3

MA9264

3/15

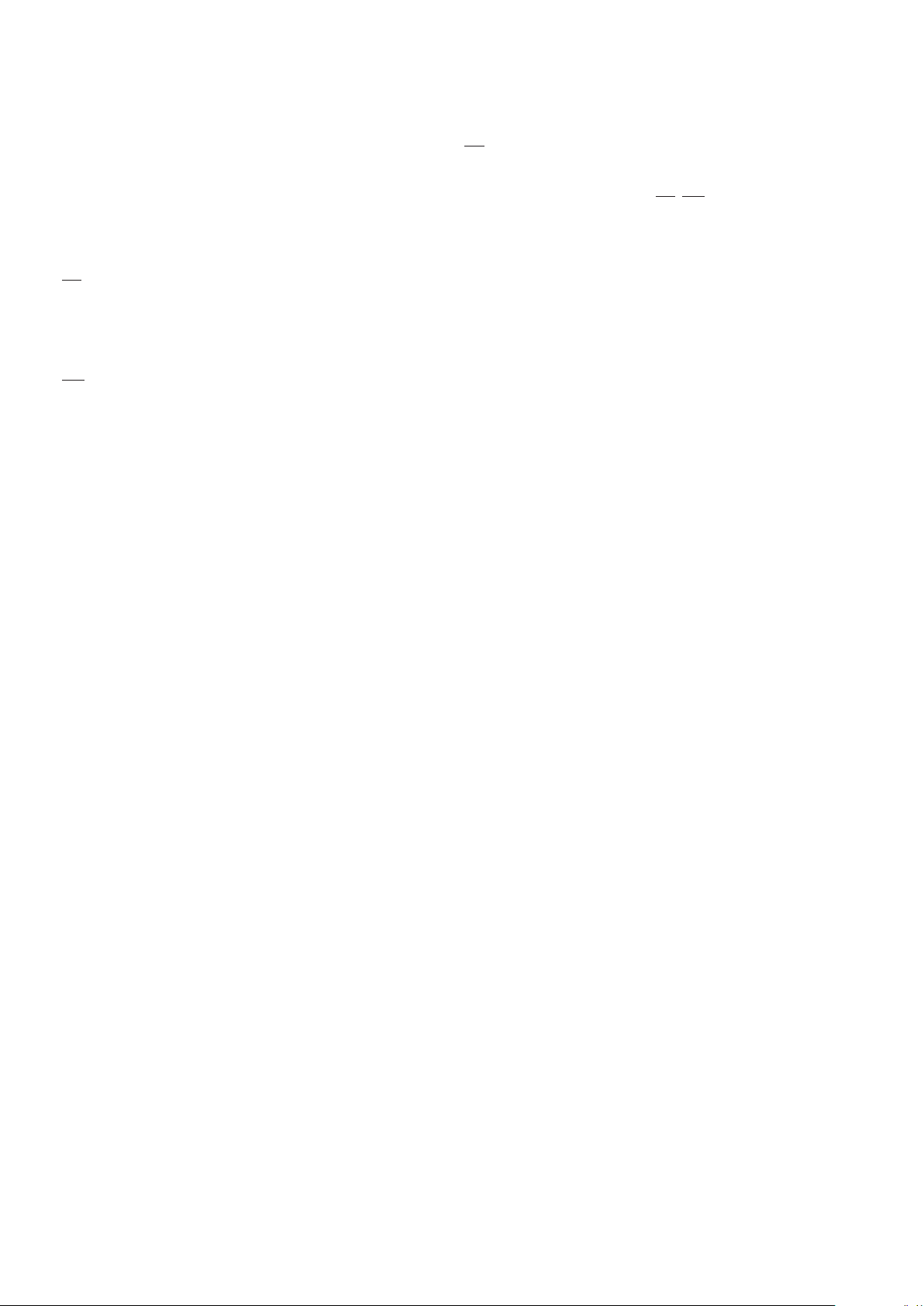

CHARACTERISTICS AND RATINGS

Symbol Parameter Min. Max. Units

V

CC

Supply Voltage -0.5 7.0 V

V

I

Input Voltage -0.3 VDD+0.3 V

T

A

Operating Temperature -55 125 °C

T

S

Storage Temperature -65 150 °C

Figure 3: Absolute Maximum Ratings

Stresses above those listed may cause permanent

damage to the device. This is a stress rating only and

functlonal operation of the device at these condltions,

or at any other condition above those indicated in the

operations section of this specification, is not Implied

Exposure to absolute maxlmum rating conditions for

extended perlods may affect device reliability.

Notes for Tables 4 and 5:

Characteristics apply to pre radiation at T

A

= -55°C to +125°C with VDD = 5V ±10% and to post 100k Rad(Si) total dose

radiation at TA = 25°C with VDD = 5V ±10% (characteristics at higher radiation levels available on request). GROUP A

SUBGROUPS 1, 2, 3.

Symbol Parameter Conditions (Option) Min. Typ. Max. Units

V

DD

Supply voltage - 4.5 5.0 5.5 V

V

lH

Logical ‘1’ Input Voltage - (TTL) VDD/2 - V

DD

V

(CMOS) 0.8 V

DD

-VDDV

V

lL

Logical ‘0’ Input Voltage - (TTL) V

SS

- 0.8 V

(CMOS) V

SS

- 0.2 V

DD

V

V

OH1

Logical ‘1’ Output Voltage I

OH1

= -2mA 2.4 - - V

V

OH2

Logical ‘1’ Output Voltage I

OH2

= -1mA V

DD

-0.5 - - V

V

OL

Logical ‘0’ Output Voltage IOL = 4mA - - 0.4 V

I

LI

Input Leakage Current VIN = VDD or VSS All inputs - - ±10 µA

I

LO

Output Leakage Current Chip disabled, V

OUT

= VDD or V

SS

--±10 µA

I

SB1

Selected Static Current (CMOS) All inputs = V

DD

-0.2V - 0.1 10 mA

except CS = V

SS

+0.2V

I

DD

Dynamic Operating Current fRC = 1MHz, all inputs - 6 18 mA

(CMOS) switching, VIH = V

DD

-0.2V

I

SB2

Standby Supply Current CS = V

DD

-0.2V - 0.1 10 mA

CE = V

SS

+0.2V

Figure 4: Electrical Characteristics

Symbol Parameter Conditions (Option) Min. Typ. Max. Units

V

DR

VCC for Data Retention CS = V

DR,

CE = V

SS

2.0 - - V

I

DDR

Data Retention Current CS = VDR, VDR = 2.0V - 0.05 4 mA

CE = V

SS

Figure 5: Data Retention Characteristics

Page 4

MA9264

4/15

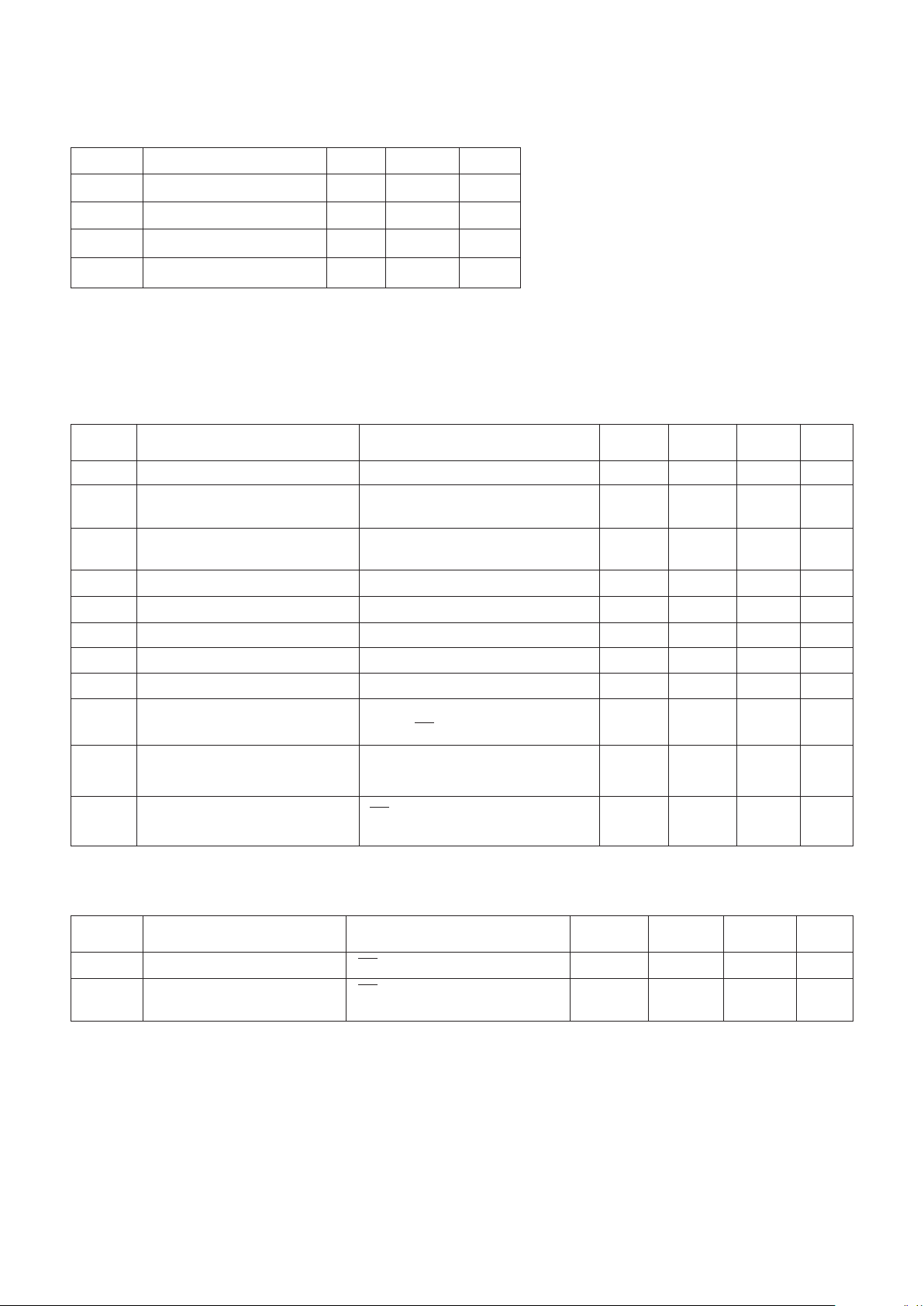

AC CHARACTERISTICS

Conditions of Test for Tables 5 and 6:

1. Input pulse = VSS to 3.0V (TTL) and VSS to 4.0V (CMOS).

2. Times measurement reference level = 1.5V.

3. Input Rise and Fall times ≤5ns.

4. Output load 1TTL gate and CL = 60pF.

5. Transition is measured at ±500mV from steady state.

6. This parameter is sampled and not 100% tested.

Notes for Tables 6 and 7:

Characteristics apply to pre-radiation at TA = -55°C to +125°C with V

DD

= 5V±10% and to post 100k Rad(Si) total dose radiation

at TA = 25°C with VDD = 5V ±10%. GROUP A SUBGROUPS 9, 10, 11.

MAX9264X70 MAX9264X95

Symbol Parameter Min Max Min Max Units

T

AVAVR

Read Cycle Time 70 - 95 - ns

T

AVQV

Address Access Time - 65 - 90 ns

T

EHQV

Chip Select Access Time - 70 - 95 ns

T

SLQV

Chip Enable Access Time - 70 - 95 ns

T

EHQX

(5,6) Chip Selection to Output in Low Z 15 - 15 - ns

T

SLQX

(5,6) Chip Enable to Output in Low Z 15 - 15 - ns

T

ELQZ

(5,6) Chip Deselection to Output in High Z 0 20 0 20 ns

T

SHQZ

(5,6) Chip Disable to Output in High Z 0 20 0 20 ns

T

AXQX

Output Hold from Address Change 30 - 40 - ns

T

GLQV

Output Enable Access Time - 25 - 30 ns

T

GLQX

(5,6) Output Enable to Output in Low Z 15 - 15 - ns

T

GHQZ

(5,6) Output Enable to Output in High Z 0 20 0 20 ns

Figure 6: Read Cycle AC Electrical Characteristics

MAX9264X70 MAX9264X95

Symbol Parameter Min Max Min Max Units

T

AVAVW

Write Cycle Tlme 55 - 60 - ns

T

EHWH

Chip Selection to End of Write 50 - 60 - ns

T

SLWH

Chip Enable to End of Write 50 - 60 - ns

T

AVWH

Address Valid to End of Write 50 - 55 - ns

T

AVWL

Address Set Up Time 0 - 0 - ns

T

WLWH

Write Pulse Width 40 - 45 - ns

T

WHAV

Write Recovery Time 0 - 0 - ns

T

WLQZ

(5,6) Wnte to Output in High Z 0 20 0 20 ns

T

DVWH

Data to Write Time Overlap 25 - 30 - ns

T

WHDX

Data Hold from Write 0 - 0 - ns

T

WHQX

(5,6) Output Active from End to Write 0 20 0 20 ns

Figure 7: Write Cycle AC Electrical Characteristics

Page 5

MA9264

5/15

Symbol Parameter Conditions Min. Typ. Max. Units

C

IN

Input Capacitance Vl = 0V - 3 5 pF

C

OUT

Output Capacitance V

I/O

= 0V - 5 7 pF

Note: T

A

= 25°C and f = 1MHz. Data obtained by characterisation or analysis; not routinely measured.

Figure 8: Capacitance

Symbol Parameter Conditions

F

T

Basic Functionality VDD = 4.5V - 5.5V, FREQ = 1MHz

VIL = VSS, VIH = VDD, VOL ≤ 1.5V, VOH ≥ 1.5V

TEMP = -55°C to +125°C, GPS PATTERN SET

GROUP A SUBGROUPS 7, 8A, 8B

Figure 9: Functionality

Subgroup Definition

1 Static characteristics specified in Tables 4 and 5 at +25°C

2 Static characteristics specified in Tables 4 and 5 at +125°C

3 Static characteristics specified in Tables 4 and 5 at -55°C

7 Functional characteristics specified in Table 9 at +25°C

8A Functional characteristics specified in Table 9 at +125°C

8B Functional characteristics specified in Table 9 at -55°C

9 Switching characteristics specified in Tables 6 and 7 at +25°C

10 Switching characteristics specified in Tables 6 and 7 at +125°C

11 Switching characteristics specified in Tables 6 and 7 at -55°C

Figure 10: Definition of Subgroups

Page 6

MA9264

6/15

TIMING DIAGRAMS

Figure 11b: Read Cycle 2

Figure 11a: Read Cycle 1

1. WE is high for Read Cycle.

2. Device is continually selected. CS, OE low, CE high.

1.

WE is high for Read Cycle.

2. Address Vaild prior to or coincident with CS transition low or CE transition high.

T

AVAVR

T

AVQV

T

AXQX

T

SLQV

T

SLQX

T

SHQZ

ADDRESS

CS

DATA OUT

HIGH

IMPEDANCE

DATA VALID

T

EHQX

T

EHQV

T

ELQZ

CE

T

GLQX

T

GLQV

T

GHQZ

OE

T

AVAVR

T

AVQV

T

AXQX

ADDRESS

DATA OUT

DATA VALID

Page 7

MA9264

7/15

Figure 12: Write Cycle

ADDRESS

T

AVAVW

T

AVWH

T

AVWL

T

WLWH (2)

T

WHAV (3)

(4)

T

WLQZ

WE

T

AXQX

T

WLQX

DATA OUT

(6) (7)

HIGH

IMPEDANCE

DATA VALIDDATA IN

T

DVWH

T

WHDX

T

SLWH

T

EHWH

CS

CE

(5)

(8)

1. WE must be high during all address transitions.

2. A write occurs during the overlap (T

WLWH

) of a low CS, a high CE and a low WE.

3. T

WHAV

is measured from either CS or WE going high or CE going low, whichever is the earlier, to the end

of the write cycle.

4. If the CS low or CE high transition occurs simultaneously with, or after, the WE low transition, the output

remains in the high impedance state.

5. DATA OUT is in the active state, so DATA IN must not be in the opposing state.

6. DATA OUT is the write data of the current cycle, if selected.

7. DATA OUT is the read data of the next address,if selected.

8. OE is low. (If OE is high then DATA OUT remains in the high impedance state throughout the cycle).

Page 8

MA9264

8/15

TYPICAL PERFORMANCE CHARACTERISTICS MAx9264x70

55

53

51

49

47

45

Page 9

MA9264

9/15

72

68

64

60

56

52

48

44

40

64

62

60

58

56

54

52

50

Page 10

MA9264

10/15

25

20

15

10

5

16

14

12

10

8

6

4

2

58

57

56

55

54

53

52

51

50

49

48

Page 11

MA9264

11/15

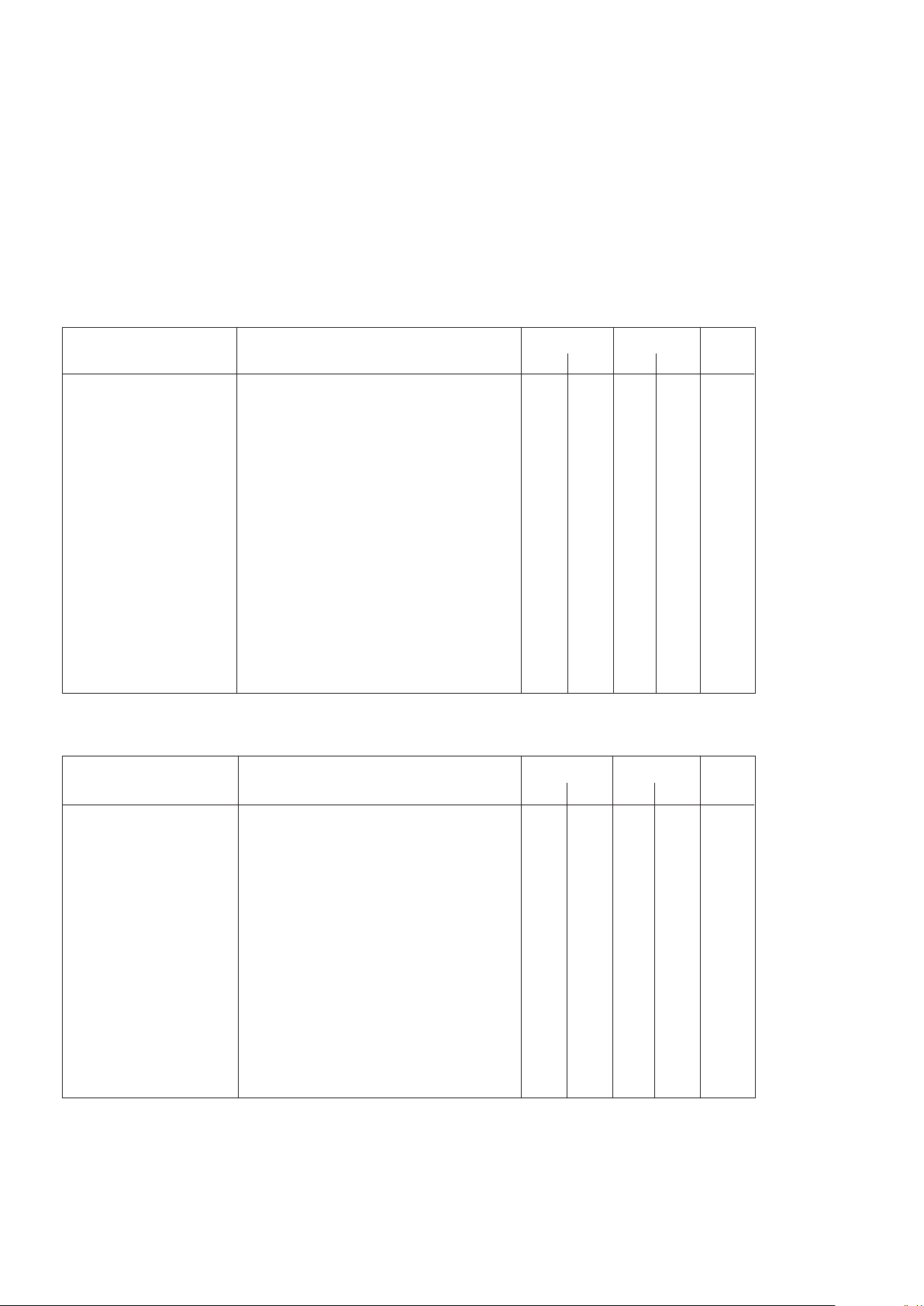

OUTLINES AND PIN ASSIGNMENTS

Figure 13: 28-Lead Ceramic DIL (Solder Seal) - Package Style C

D

W

A

e b Z

H

A

1

15°

M

E

C

e

1

Seating Plane

114

2815

28

VCC

27

W

26

CE

25

A8

24

A9

23

A11

22

OE

21

A10

20

CS

19

D/Q7

18

D/Q6

17

D/Q5

16

D/Q4

15

D/Q3

1

NC

2

A12

3

A7

4

A6

5

A5

6

A4

7

A3

8

A2

9

A1

10

A0

11

D/Q0

12

D/Q1

13

D/Q2

14

GND

Top

View

Ref

Millimetres Inches

Min. Nom. Max. Min. Nom. Max.

A - - 5.715 - - 0.225

A1 0.38 - 1.53 0.015 - 0.060

b 0.35 - 0.59 0.014 - 0.023

c 0.20 - 0.36 0.008 - 0.014

D - - 36.02 - - 1.418

e - 2.54 Typ. - - 0.100 Typ. -

e1 - 15.24 Typ. - - 0.600 Typ. -

H 4.71 - 5.38 0.185 - 0.212

Me - - 15.90 - - 0.626

Z - - 1.27 - - 0.050

W - - 1.53 - - 0.060

XG404

Page 12

MA9264

12/15

Figure 14: 28-Lead Ceramic Flatpack (Solder Seal) - Package Style F

Ref

Millimetres Inches

Min. Nom. Max. Min. Nom. Max.

A - - 3.18 - - 0.125

Q 0.66 - - 0.026 - -

b 0.38 - 0.48 0.015 - 0.019

c 0.10 - 0.18 0.004 - 0.007

D 18.08 - 18.49 0.712 - 0.728

e - 1.27 - - 0.050 L 7.62 - 9.91 0.300 - 0.390

M 12.50 - 12.09 0.492 - 0.508

XG530

M

b

e

D

L

A

Q

c

Pin 1

Z

M

E

1NC

2 A12

3A7

4A6

5A5

6A4

7A3

8A2

9A1

10 A0

11 D/Q0

12 D/Q1

13 D/Q2

14 GND

28

VCC

27

W

26

CE

25

A8

24

A9

23

A11

22

OE

21

A10

20

CS

19

D/Q7

18

D/Q6

17

D/Q5

16

D/Q4

15

D/Q3

Bottom

View

Page 13

MA9264

13/15

Function Pin N umber

Option D and F

Via Static1Static2Dynamic Radiation

A12 2 R 5V 0V F14 5V

A7 3 R 5V 0V F7 5V

A6 4 R 5V 0V F9 5V

A5 5 R 5V 0V F8 5V

A4 6 R 5V 0V F11 5V

A3 7 R 5V 0V F10 5V

A2 8 R 5V 0V F5 5V

A1 9 R 5V 0V F4 5V

A0 10 R 5V 0V F3 5V

D/Q0 11 R 5V 0V F1 5V

D/Q1 12 R 5V 0V F1 5V

D/Q2 13 R 5V 0V F1 5V

GND(VSS ) 14 Direct 0V 0V 0V 0V

D/Q3 15 R 5V 0V F1 5V

D/Q4 16 R 5V 0V F1 5V

D/Q5 17 R 5V 0V F1 5V

D/Q6 18 R 5V 0V F1 5V

D/Q7 19 R 5V 0V F1 5V

CSB 20 R 5V 0V F15 5V

A10 21 R 5V 0V F2 5V

OEB 22 R 5V 0V F15 5V

A11 23 R 5V 0V F6 5V

A9 24 R 5V 0V F13 5V

A8 25 R 5V 0V F12 5V

CE 26 R 5V 0V F15B 5V

WB 27 R 5V 0V F0 5V

VDD 28 Direct 5V 5V 5V 5V

1. F0=150KHz, F1=F0/2, F2=F0/4, F3=F0/8 etc.

2. Static 1, Static 2 and Dynamic: R=4k7.

3. Radiation: R=10k.

Figure 15: Burnin and Radiation Configuration

Page 14

MA9264

14/15

RADIATION TOLERANCE

Total Dose Radiation Testing

For product procured to guaranteed total dose radiation

levels, each wafer lot will be approved when all sample

devices from each lot pass the total dose radiation test.

The sample devices will be subjected to the total dose

radiation level (Cobalt-60 Source), defined by the ordering

code, and must continue to meet the electrical parameters

specified in the data sheet. Electrical tests, pre and post

irradiation, will be read and recorded.

Dynex Semiconductor can provide radiation testing

compliant with MIL-STD-883 test method 1019, Ionizing

Radiation (Total Dose).

Ion LET (MeV.cm2/mg)

UPSET BIT

CROSS-SECTION

(cm2/bit)

Figure 17: Typical Per-Bit Upset Cross-Section vs Ion LET

SINGLE EVENT UPSET CHARACTERISTICS

Total Dose (Function to specification)* 1x105 Rad(Si)

Transient Upset (Stored data loss) 5x10

10

Rad(Si)/sec

Transient Upset (Survivability) >1x1012 Rad(Si)/sec

Neutron Hardness (Function to specification) >1x1015 n/cm

2

Single Event Upset** 4.3x10

-11

Errors/bit day

Latch Up Not possible

* Other total dose radiation levels available on request

** Worst case galactic cosmic ray upset - interplanetary/high altitude orbit

Figure 16: Radiation Hardness Parameters

Page 15

MA9264

15/15

ORDERING INFORMATION

For details of reliability, QA/QC, test and assembly

options, see ‘Manufacturing Capability and Quality

Assurance Standards’ Section 9.

Unique Circuit Designator

S

R

Q

Radiation Hard Processing

100 kRads (Si) Guaranteed

300 kRads (Si) Guaranteed

For radiation levels above thos

e

stated please contact Marketing

Radiation Tolerance

C

F

L

N

Ceramic DIL (Solder Seal)

Flatpack (Solder Seal)

Leadless Chip Carrier

Naked Die

Package Type

QA/QCI Process

(See Section 9 Part 4)

Test Process

(See Section 9 Part 3)

Assembly Process

(See Section 9 Part 2)

L

C

D

E

B

S

Rel 0

Rel 1

Rel 2

Rel 3/4/5/STACK

Class B

Class S

Reliability Level

MAx9264xxxxxxxx

TCTTL

CMOS

709570ns Speed

95ns Speed

CUSTOMER SERVICE CENTRES

France, Benelux, Italy and Spain Tel: +33 (0)1 69 18 90 00. Fax: +33 (0)1 64 46 54 50

North America Tel: 011-800-5554-5554. Fax: 011-800-5444-5444

UK, Germany, Scandinavia & Rest Of World Tel: +44 (0)1522 500500. Fax: +44 (0)1522 500020

SALES OFFICES

France, Benelux, Italy and Spain Tel: +33 (0)1 69 18 90 00. Fax: +33 (0)1 64 46 54 50

Germany Tel: 07351 827723

North America Tel: (613) 723-7035. Fax: (613) 723-1518. Toll Free: 1.888.33.DYNEX (39639) /

Tel: (831) 440-1988. Fax: (831) 440-1989 / Tel: (949) 733-3005. Fax: (949) 733-2986.

UK, Germany, Scandinavia & Rest Of W orld Tel: +44 (0)1522 500500. Fax: +44 (0)1522 500020

These offices are supported by Representatives and Distributors in many countries world-wide.

© Dynex Semiconductor 2000 Publication No. DS3692-7 Issue No. 7.0 January 2000

TECHNICAL DOCUMENTATION – NOT FOR RESALE. PRINTED IN UNITED KINGDOM

HEADQUARTERS OPERATIONS

DYNEX SEMICONDUCTOR LTD

Doddington Road, Lincoln.

Lincolnshire. LN6 3LF. United Kingdom.

Tel: 00-44-(0)1522-500500

Fax: 00-44-(0)1522-500550

DYNEX POWER INC.

Unit 7 - 58 Antares Drive,

Nepean, Ontario, Canada K2E 7W6.

Tel: 613.723.7035

Fax: 613.723.1518

Toll Free: 1.888.33.DYNEX (39639)

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded

as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company

reserves the right to alter without prior notice the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any

guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and

to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury

or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.

All brand names and product names used in this publication are trademarks, registered trademarks or trade names of their respective owners.

http://www.dynexsemi.com

e-mail: power_solutions@dynexsemi.com

Datasheet Annotations:

Dynex Semiconductor annotate datasheets in the top right hard corner of the front page, to indicate product status. The annotations are as follows:Target Information: This is the most tentative form of information and represents a very preliminary specification. No actual design work on the product has been

started.

Preliminary Information: The product is in design and development. The datasheet represents the product as it is understood but details may change.

Advance Information: The product design is complete and final characterisation for volume production is well in hand.

Loading...

Loading...