Page 1

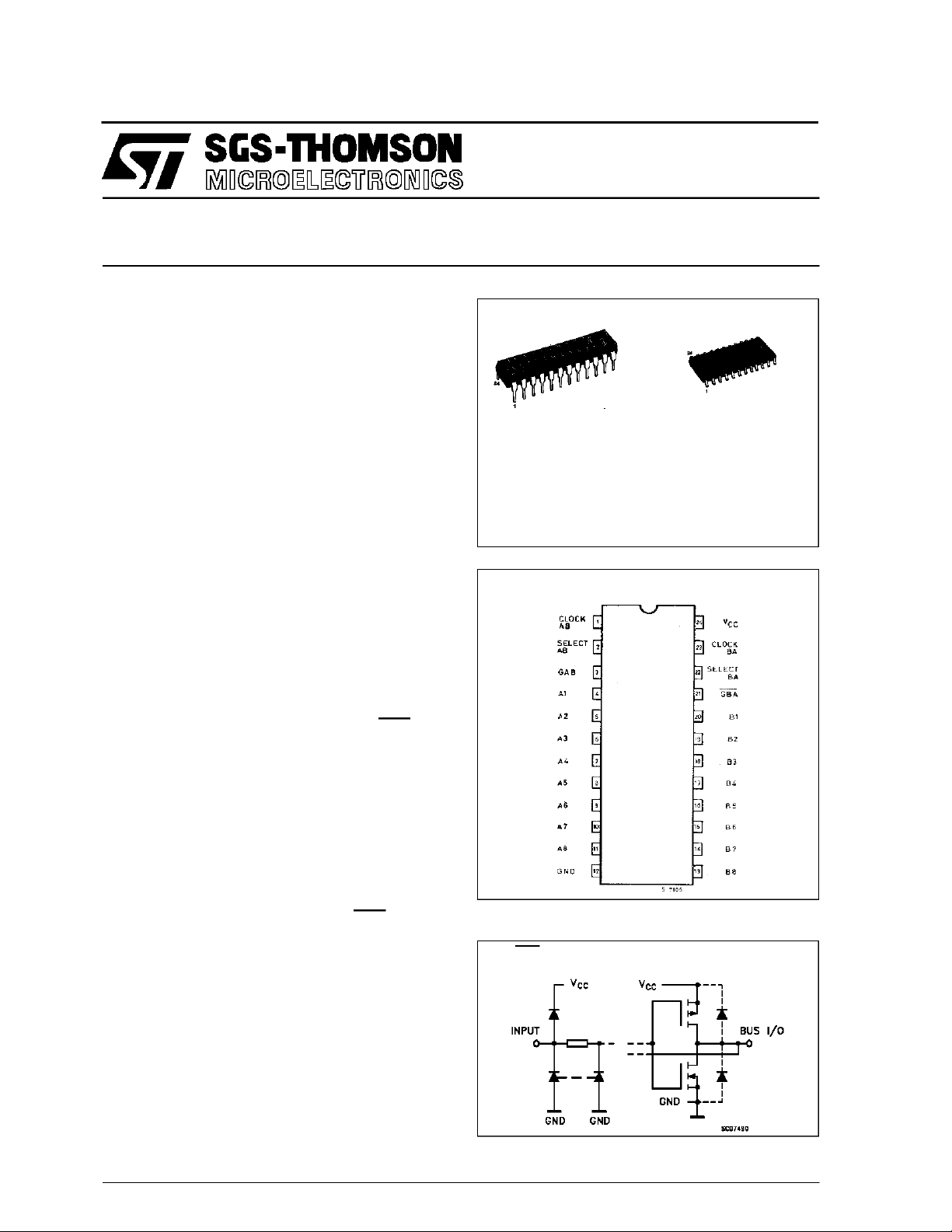

M74HCT651

M74HCT652

HCT651 OCTAL BUS TRANSCEIVER/REGISTER (3-STATE, INV.)

HCT652 OCTAL BUS TRANSCEIVER/REGISTER (3-STATE)

.HIGH SPEED

f

= 60 MHz (TYP.)AT VCC=5V

MAX

.COMPATIBLE WITHTTL OUTPUTS

VIH= 2 V (MIN.) AT VIL= 0.8V (MAX)

.LOWPOWER DISSIPATION

ICC=4µA(MAX) AT TA=25oC

.OUTPUTDRIVE CAPABILITY

15 LSTTL LOADS

.SYMMETRICAL OUTPUT IMPEDANCE

IOH =IOL= 6 mA (mIN.)

B1R

(PlasticPackage)

M1R

(MicroPackage)

.BALANCEDPROPAGATIONDELAYS

t

PLH=tPHL

.PIN ANDFUNCTION COMPATIBLE

WITH 54/74LS651/652

DESCRIPTION

M74HCT651/652 are high speed CMOS OCTAL

BUS TRANSCEIVERS AND REGISTERS

(3-STATE), fabricated in silicon gate C2MOS

technology. They have the same high speed

performance of LSTTL combined with true CMOS

low power consumption. These devices consist of

bustransceiver circuits, D-typeflip-flops, andcontrol

circuitry arranged for multiplexed transmission of

data directly from the input bus or from the internal

storage registers. Enable GAB and GBA are

provided to control the transceiverfunctions. Select

AB andSelect BA control pins are provided to select

whether real-time orstored dataistransfered. A low

input levelselectsreal-time data, anda high selects

stored data. Data onthe A or B bus, or both,can be

stored in the internal D flip-flops by low-to-high

transitionsattheappropriate clock pins(CLOCKAB

or CLOCK BA) regardless of the select or enable

controlpins.When select ABand selectBAareinthe

real-time transfer mode, it is also possible to store

data without using the internal D-type flip-flops by

simultaneously enabling GAB and GBA. In this

configuration each outputreinforces its input. Thus,

when all other data sources to the two sets of bus

linesareat highimpedance, eachset ofbuslineswill

remain at its last state. All inputs are equipped with

protection circuits against static discharge and

transient excess voltage.This integrated circuit has

input and output characteristics that are fully

compatible with 54/74 LSTTL logic families.

M54/74HCT devices are designed to directly

interface HSCMOS systems with TTL and NMOS

components. Theyare also plugin replacements for

LSTTL devices giving a reduction of power

consumption.

M74HC X XXM1R M74HC XXXB1R

PIN CONNECTIONS (top view)

INPUT AND OUTPUT EQUIVALENT CIRCUIT

GAB,GAB, CAB, A, B

SAB,SBA, CBA

ORDER CODES :

October 1993

1/12

Page 2

M74HCT651/652

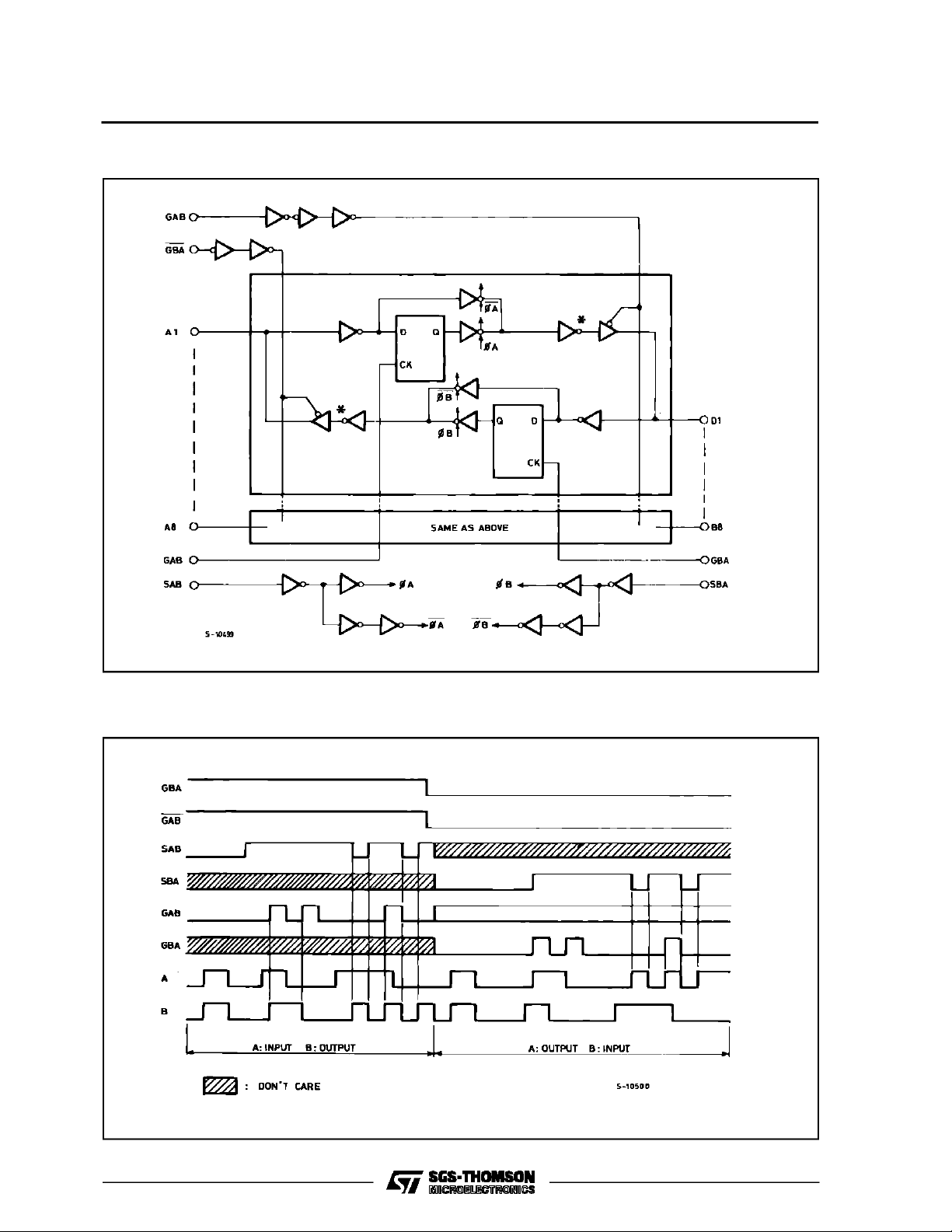

LOGIC DIAGRAM (HCT651)

Note: Incase of 74HCT652 outputinvertermarked *at A busand B bus are eliminated.

TIMING CHART

2/12

Page 3

M74HCT651/652

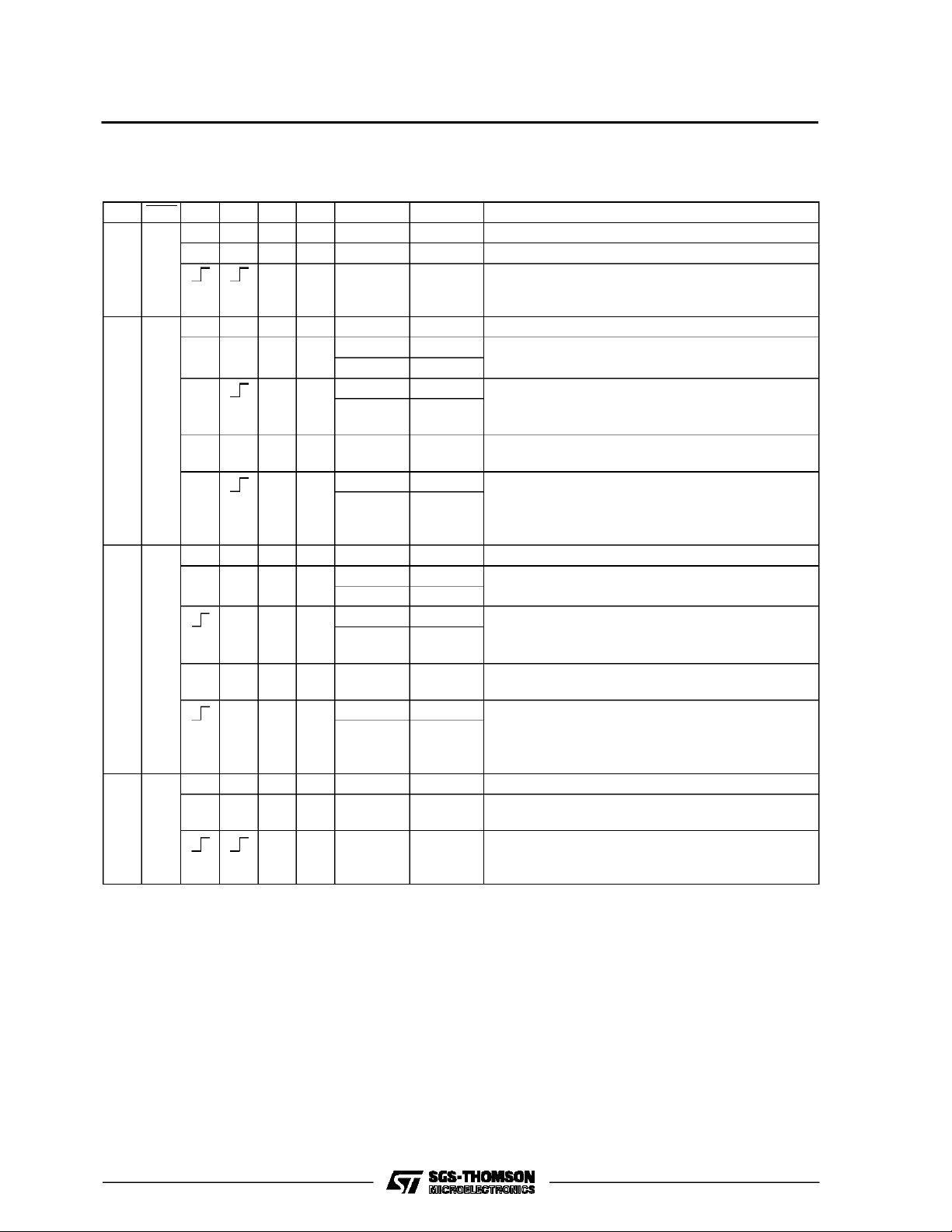

TRUTH TABLE

HCT652 (The tru th table for HC T651 is the same as this, but with th e o utputs invert ed)

GAB GBA CAB CBA SAB SBA A B FUNCTION

INPUTS INPUTS Both the A bus and the B bus are inputs

LH

LL

HH

HL

X : DON’TCARE

Z :HIGHIMPEDANCE

Qn :THE DATA STOREDTO THE INTERNALFLIP-FLOPSBY MOST RECENTLOWTO HIGH TRANSITIONOF THECLOCK INPUTS

* : THE DATAAT THE A AND B BUS WILLBE STORED TOTHE INTERNALFLIP-FLOPSON EVERY LOWTO HIGH TRANSITIONOF

THECLOCK INPUTS

X X X X Z Z The output functions of the A and B bus are disabled

X X INPUTS INPUTS Both the A and B bus are used for inputs to the

internal flip-flops. Data at the bus will be stored on

low to high transition of the clock inputs

OUTPUTS INPUTS The A bus are outputs and the B bus are inputs

X* X X L L L The data at the B bus are displayed at the A bus

HH

X* X L L L The data at the B bus ar displayed at the A bus.

HH

The data of the B bus are stored to the internal

flip-flop on low to high transition of th clock pulse

X* X X H Qn X The data stored to the internal flip-flop are dispayed

at the A bus

X* X H L L The data at the B bus are stored to the internal flip-

HH

flop on low to high transition of the clock pulse. The

states of the internal flip-flops output directly to the

A bus

INPUTS OUTPUTS The A bus are inputs and the B bus are outputs

XX*L X

L L The data at the A bus are displayed at the B bus

HH

X* L X L L The data at the A bus are displayed at the B bus.

HH

The data of the A bus are stored to the internal flipflop on low to high transition of the clock pulse

X X* H X X Qn The data stored to the internal flip-flops are

displayed at the B bus

X* H X L L the data at the A bus are stored to the internal flip-

HH

flop on low to high transition of the clock pulse. The

states of the internal flip-flops output directly to the

B bus

OUTPUTS OUTPUTS Both the A bus and the B bus are outputs

X X H H Qn Qn The data stored to the internal flip-flops are

displayed at the A and B bus respactively

H H Qn Qn The output at the A bus are displayed at the B bus,

the output at the B bus are displayed at the A bus

respectively

3/12

Page 4

M74HCT651/652

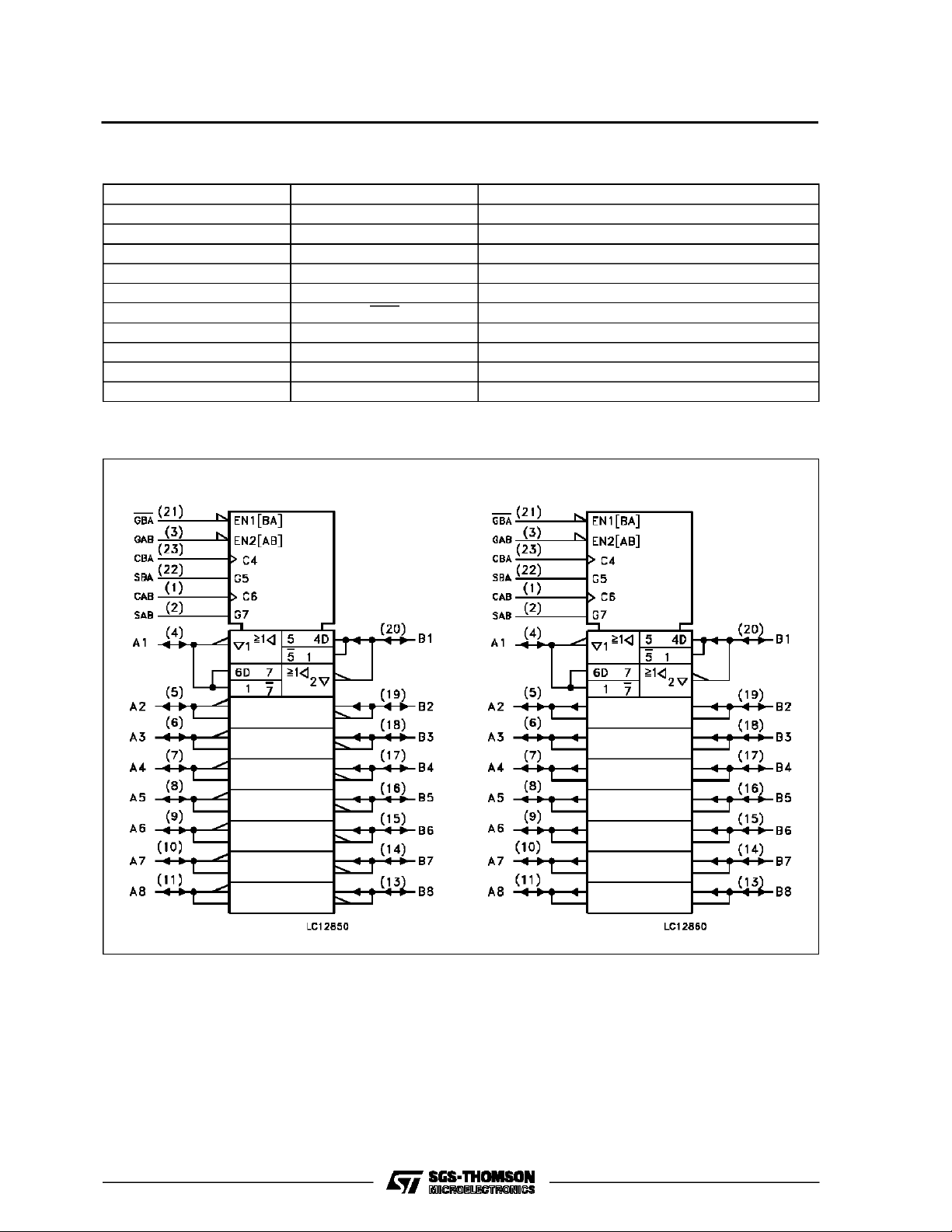

PIN DESCRIPTION

PIN No SYMBOL NAME AND FUNCTION

1 CLOCK AB A to B Clock Input (LOW to HIGH, Edge-Trigged)

2 SELECT AB Select A to B Source Input

3 GAB Direction Control Input

4, 5, 6, 7, 8, 9, 10, 11 A1 to A8 A data Inputs/Outputs

20, 19, 18, 17, 16, 15, 14, 13 B1 to B8 B Data Inputs/Outputs

21 GBA Output Enable Input (Active LOW)

22 SELECT BA Select B to A Source Input

23 CLOCK BA B to A Clock Input (LOW to HIGH, Edge-Triggered)

12 GND Ground (0V)

24 V

IEC LOGIC SYMBOLS

HCT651 HCT652

CC

Positive Supply Voltage

4/12

Page 5

M74HCT651/652

ABSOLU TE M AXIMU M R AT INGS

Symbol Parameter Value Unit

V

CC

V

V

O

I

IK

I

OK

I

O

I

or I

CC

P

D

T

stg

T

AbsoluteMaximumRatingsarethosevalues beyondwhichdamage tothedevicemayoccur.Functional operationunder theseconditionisnotimplied.

RECO MM ENDED OPERAT IN G CO NDITIO NS

Symbol Parameter Value Unit

V

CC

V

I

V

O

T

op

t

r,tf

Supply Voltage -0.5 to +7 V

DC Input Voltage -0.5 to VCC+ 0.5 V

I

DC Output Voltage -0.5 to VCC+ 0.5 V

DC Input Diode Current ± 20 mA

DC Output Diode Current ± 20 mA

DC Output Source Sink Current Per Output Pin ± 35 mA

DC VCCor Ground Current ± 70 mA

GND

Power Dissipation 500 (*) mW

Storage Temperature -65 to +150

Lead Temperature (10 sec) 300

L

Supply Voltage 4.5 to 5.5 V

Input Voltage 0 to V

Output Voltage 0 to V

CC

CC

Operating Temperature: -40 to +85

Input Rise and Fall Time (VCC= 4.5 to 5.5V) 0 to 500 ns

o

C

o

C

V

V

o

C

5/12

Page 6

M74HCT651/652

DC SPECIFICATIONS

Symbol Parameter

V

V

High Level Input Voltage 4.5

IH

Low Level Input

IL

Voltage

V

V

I

I

∆I

High Level Output Voltage

OH

Low Level Output Voltage

OL

Input Leakage Current (*) 5.5 VI=VCCor GND ±0.1 ±1 µA

I

I

3 State Output Off State Current 5.5 VI=VCCor GND ±0.5 ±5.0 µA

OZ

Quiescent Supply Current 5.5 VI=VCCor GND 1 10 µA

CC

Additional worst case supply

CC

current

(*):Applicableonlyto GAB,GBA,CAB,CBA,SAB, SBAinput

V

Test Conditions Value

CC

(V)

TA=25oC -40 to 85oC

Min. Typ. Max. Min. Max.

2.0 2.0 V

to

5.5

4.5

to

5.5

VI=

IO=-20 µA 4.4 4.5 4.4

V

IH

I

=-6.0 mA 4.18 4.31 4.13

4.5

4.5

O

or

V

IL

VI=

IO=20µA 0.0 0.1 0.1

V

IH

I

= 6.0 mA 0.17 0.26 0.33

O

or

V

IL

5.5 Per Input pin

V

= 0.5V or

I

VI= 2.4V

Other Inputs at

VCCor GND

Unit

0.8 0.8 V

V

V

2.0 2.9 mA

6/12

Page 7

M74HCT651/652

AC ELECTRICAL CHARACTERISTICS (Inp ut tr=tf=6ns)

Test Conditions Value

Symbol Parameter

t

TLH

t

THL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PZL

t

PZH

t

PLZ

t

PHZ

f

MAX

t

W(H)

t

W(L)

C

C

C

PD

(*) CPDisdefined as the valueof the IC’s internal equivalent capacitance whichis calculated fromthe operatingcurrent consumption withoutload.

(RefertoTest Circuit).Average operting currentcan be obtained by the followingequation. ICC(opr) = CPD•VCC•fIN+ICC/8(per Channel)

Output Transition Time 4.5 50 7 12 15 ns

Propagation Delay Time

(BUS - BUS)

Propagation Delay Time

(CLOCK - BUS)

Propagation Delay Time

(SELECT - BUS)

3-State Output Enable Time

(GAB,GBA - BUS)

Output Disable Time

(GAB,GBA - BUS)

Maximum Clock Frequency 4.5 50 31 55 25 MHz

Minimum Clock Pulse Width 4.5 50 8 15 19 ns

Minimum Set-up Time 4.5 50 3 10 13 ns

t

s

t

Minimum Hold Time 4.5 50 5 5 ns

h

Input Capacitance 5 10 10 pF

IN

Bus Terminal Capacitance 13 pF

I/O

(*) Power Dissipation Capacitance for HCT651

V

(V)

CC

C

(pF)

L

TA=25oC -40 to 85oC

Min. Typ. Max. Min. Max.

4.5 50 20 30 38 ns

4.5 150 25 38 48 ns

4.5 50 29 44 55 ns

4.5 150 34 52 65 ns

4.5 50 24 34 43 ns

4.5 150 29 42 53 ns

4.5 50 RL=1KΩ 22 33 41 ns

4.5 150 R

=1KΩ 27 41 51 ns

L

4.5 50 RL=1KΩ 24 35 44 ns

38

for HCT652

39

Unit

pF

7/12

Page 8

M74HCT651/652

SWITCHING CHARACTERISTICS TEST CIRCUIT AND WAVEFORM

WAVEFORM 1 WAVEFORM 2

WAVEFORM3

GBA =”H”

WAVEFORM5

WAVEFORM 4

GAB= ”L”

8/12

Page 9

TEST WAVEFORM ICC(Opr.)

INPUT TRANSITIONTIME IS THE SAME AS THAT INCASE OF SWITCHINGCHARACTERISTICSTEST.

M74HCT651/652

9/12

Page 10

M74HCT651/652

Plastic DIP24 (0.25) MECHANICAL DATA

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

a1 0.63 0.025

b 0.45 0.018

b1 0.23 0.31 0.009 0.012

b2 1.27 0.050

D 32.2 1.268

E 15.2 16.68 0.598 0.657

e 2.54 0.100

e3 27.94 1.100

F 14.1 0.555

I 4.445 0.175

L 3.3 0.130

mm inch

10/12

P043A

Page 11

SO24 MECHANICAL DATA

M74HCT651/652

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

A 2.65 0.104

a1 0.10 0.20 0.004 0.007

a2 2.45 0.096

b 0.35 0.49 0.013 0.019

b1 0.23 0.32 0.009 0.012

C 0.50 0.020

c1 45° (typ.)

D 15.20 15.60 0.598 0.614

E 10.00 10.65 0.393 0.420

e 1.27 0.05

e3 13.97 0.55

F 7.40 7.60 0.291 0.299

L 0.50 1.27 0.19 0.050

S8°(max.)

mm inch

L

A

a2

b

e3

D

24 13

112

e

F

s

a1

c1

b1

C

E

11/12

Page 12

M74HCT651/652

Information furnished is believed tobe accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsability for the

consequences of use of such information nor for any infringementof patents or other rights of third partieswhich mayresults from its use. No

license isgranted by implicationor otherwise underany patent or patentrights of SGS-THOMSON Microelectronics. Specificationsmentioned

in this publication are subject to changewithout notice. This publication supersedes and replaces all information previously supplied.

SGS-THOMSON Microelectronicsproducts are not authorizedforuse ascritical componentsinlife supportdevices orsystems withoutexpress

written approval of SGS-THOMSON Microelectonics.

1994 SGS-THOMSON Microelectronics - All RightsReserved

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands-

Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - UnitedKingdom - U.S.A

SGS-THOMSON Microelectronics GROUP OF COMPANIES

12/12

Loading...

Loading...