Page 1

MITSUBISHI<Dig.Ana.INTERFACE>

control in combination with a microcomputer.

resistor)

-

LATCH X 4

D15 D14 D13 D12 D11 D10 D9 D8

D5 D4 D3 D2 D1 D0

M62370GP

3V TYPE 8-BIT 36CH SELECTOR SW BUILT-IN D-A CONVERTER WITH BUFFER AMPLIFIERS

DESCRIPTION

The M62370GP is a CMOS semiconductor IC,containing 36

channels of 8-bit D-A converters.It is operable with a low

supply voltage between 2.7~3.6V,and is easy to use due to

serial data input,and 3-pin(DI,CLK,LD)connection with

microcomputer.The IC also contains Do pin terminal,enabling

cascade connection,and therefore is suitable for automatic

FEATURES

•Operable with a low voltage between 2.7~3.6V

•16-bit serial data input(connected via 3 pins:DI,CLK,LD)

•36 channels built-in of 8-bit D-A converter

•6 channels of D-A converters capable of selecting and

outputting 4 data stored in each converter,through

2 control terminals

APPLICATION

Digital-analog conversion in industrial or home-use

electronic equipment.

Automatic control in combination with EEPROM and

microcomputer(Substitute for conventional semi-fixed

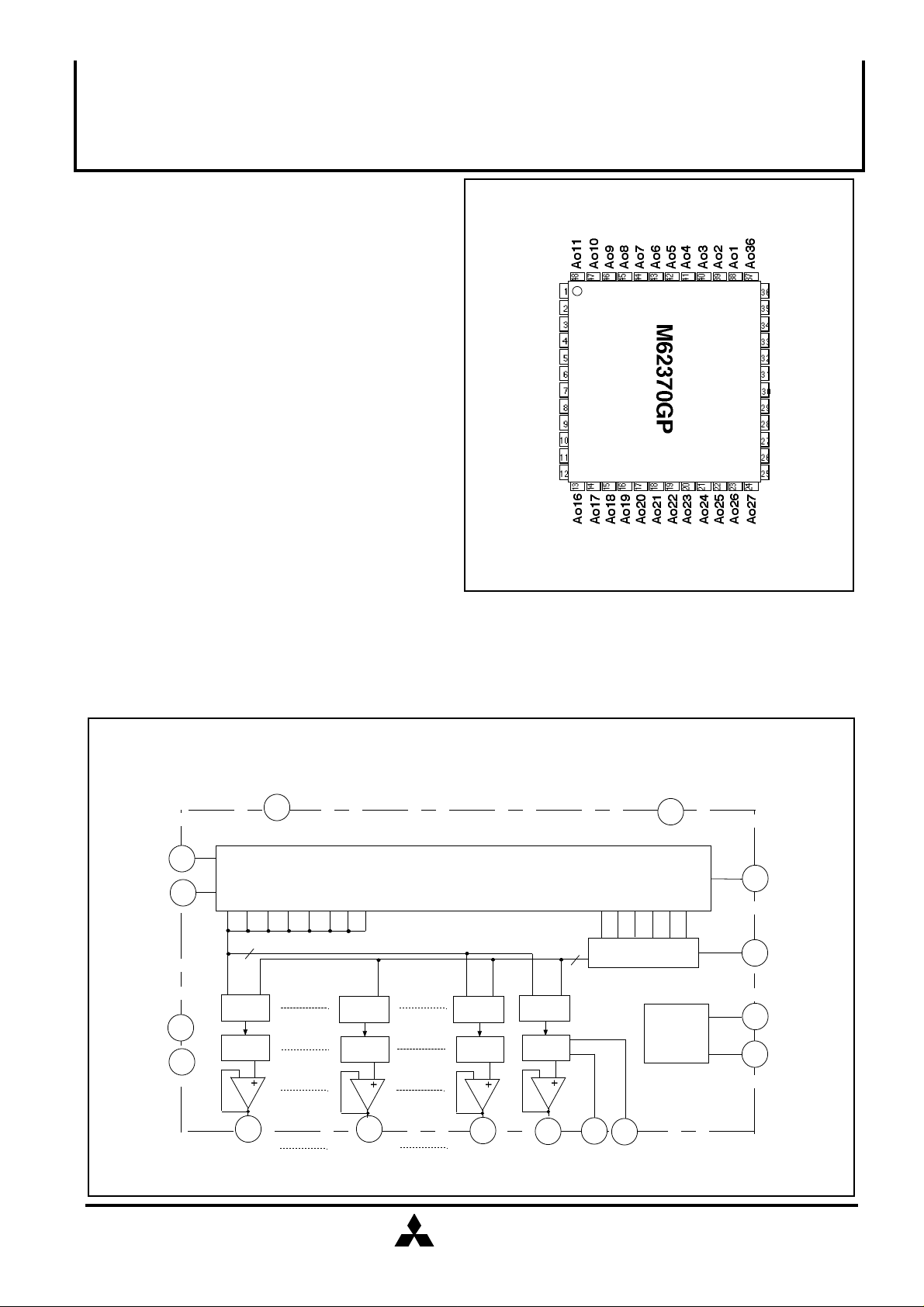

PIN CONFIGURATION (TOP VIEW)

DI

CLK

LD

Do

GND

C0

Vss1

VDD1

Ao12

Ao13

Ao14

Ao15

Outline 48P6D-A

Ao35

Ao34

Ao33

Ao32

Vss2

VDD2

C1

Vcc

Ao31

Ao30

Ao29

Ao28

BLOCK DIAGRAM

CLK

2

DI

1

8-BIT

VDD1

Vss1

8

7

LATCH

D-A

-

38 21

Ao1

8

VCC

29

16-BIT SHIFT REGISTER

8-BIT

D-A

Ao24 Ao35 Ao36

8-BIT

LATCH X 4

D-A

-

36 37

8-BIT

LATCH X 4

D-A

-

DECODER

31

VDD232Vss2

GND

5

DATA

CONTROL

30

Do

4

LD

3

Co

6

C1

MITSUBISHI

ELECTRIC

( / 5 )

1

Page 2

3V TYPE 8-BIT 36CH SELECTOR SW BUILT-IN D-A CONVERTER WITH BUFFER AMPLIFIERS

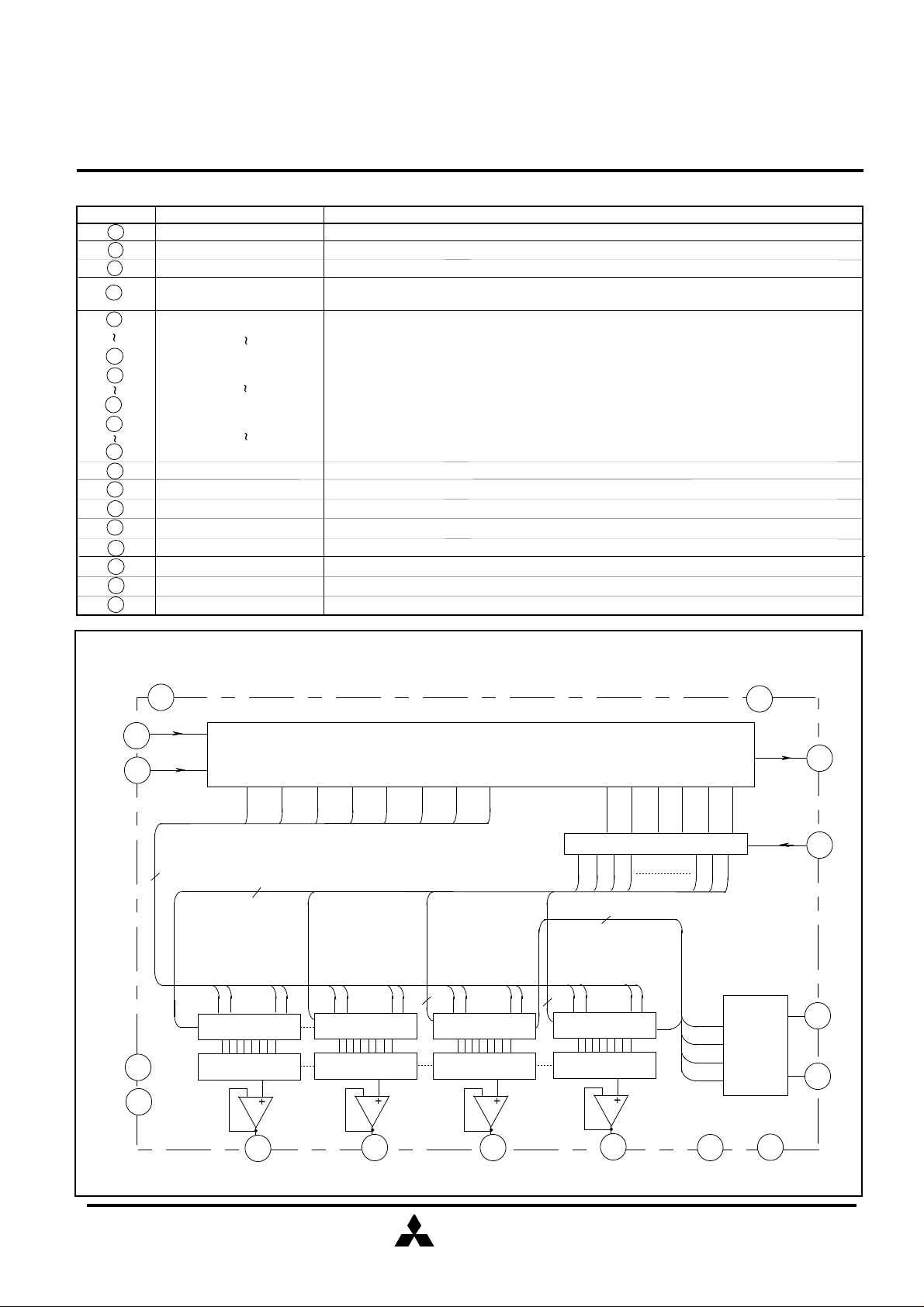

EXPLANATION OF TERMINALS

Pin No. Symbol

1

4

2

3

38

DI

Do

CLK

LD

Ao1

MITSUBISHI<Dig.Ana.INTERFACE>

M62370GP

Function

Serial data input terminal to input 16-bit long ssrial data

Terminal to output MSB data of 16-bit shift register

Shift clock input terminal.Input signal at DI pin is input to 16-bit shift register at rise of shift clock pulse

When H-level signal is input to this terminal,the value stored in 16-bit shift register is loaded

in decoder and D-A converter output register

48

9

28

33

37

29

5

6

30

8

7

31

32

Ao11

Ao12

Ao31

Ao32

Ao36

VCC

GND

C0

C1

VDD1

VSS1

VDD2

VSS2

8-bit D-A converter output terminal

Power supply terminal

GND terminal

Data sslect signal input terminal 1 for channel No.31 through 36

Data select signal input terminal 2 for channel No.31 through 36

Upper reference voltage input terminal and power supply to operational amplifier for channel No.1 through 24

Lower reference voltage input terminal for channel No.1 through 24

Upper reference voltage input terminal and power supply to operational amplifier for channel No.25 through 36

Lower reference voltage input terminal for channel No.25 through 36

BLOCK DIAGRAM FOR EXPLANATION OF TERMINALS

Vcc

29

2

CLK

1DI

D15

D14

D13

D12

16-BIT SHIFT REGISTER

D11

D10

D9 D8

D7

D6

D5

D4

D3 D2

GND

5

43Do

D1 D0

VDD1

ADDRESS DECODER

(8)

............

8-BIT

LATCH

1

8

7Vss1

8-BIT

D-A CONVERTER

-

38

Ao1

............

8-BIT

LATCH

DAC

-

27

Ao30

(4)

............

8-BIT LATCH X 4

3130

DAC

SEL

-

28

Ao31

36

MITSUBISHI

ELECTRIC

3

21

4

(4)

............

(4)

8-BIT LATCH X 4

SEL

8-BIT

D-A CONVERTER

-

37

Ao36

CONTROL

31

VDD2

DATA

32

Vss2

( / 5 )

2

LD

630C0

C1

Page 3

3V TYPE 8-BIT 36CH SELECTOR SW BUILT-IN D-A CONVERTER WITH BUFFER AMPLIFIERS

DIGITAL DATA FORMAT

FIRST

LSB

MITSUBISHI<Dig.Ana.INTERFACE>

M62370GP

LAST

MSB

DAC DATA

D8

0

1

0

1

0

1

D5 D4 D3 D2

0

0

0

0

0

1

1

1

1

1

D9 D10 D11 D12

0

0

1

1

1

1 1 1 1 1 1 1

0

0

0

1

1

0

0

0

0

0

0

0

0

0

1

0

0

0

1

1

0

0

0

1

1

DAC SELECT DATA

D13

0

0

0

0

1

0

0

0

1

1

0

1

1

0

0

0

0

0

0

1

D1 D0

0

0

1

1

1

0

0

0

1

1

0

0

0

0

1

0

1

0

0

1

0

0

1

0

1

D14

0

0

0

0

1

DAC selection

Don‘t care

Ao1 selection

Ao2 selection

Ao30 selection

Ao31(0) selection

Ao32(0) selection

Ao36(0) selection

Ao31(1) selection

Ao36(1) selection

Ao31(2) selection

D15

0

0

0

0

1

(VrefU-VrefL) / 256 X 1 +VrefL

(VrefU-VrefL) / 256 X 2 +VrefL

(VrefU-VrefL) / 256 X 3 +VrefL

(VrefU-VrefL) / 256 X 4 +VrefL

(VrefU-VrefL) / 256 X 255 +VrefL

VrefU

VrefU=VDD1,VDD2

*

VrefL=Vss1,Vss2

D-A output

C0 C1

0

0

1

1

1

1

Address 0 selected

0

Address 1 selected

0

Address 2 selected

Address 3 selected

Ao31 through Ao36

data selected

1

1

1

1

1

1

1

1

1

1

0

0

0

0

1

TIMING CHART (MODEL)

DI

CLK

LD

D-A

OUTPUT

0

0

1

1

1

LSB

D0 D1

0

0

1

1

1

D2

0

Ao36(2) selection

1

Ao31(3) selection

0

Ao36(3) selection

1

Don‘t care

1

Don‘t care

D3

MITSUBISHI

ELECTRIC

D13

D14

MSB

D15

( / 5 )

3

Page 4

MITSUBISHI<Dig.Ana.INTERFACE>

M62370GP

3V TYPE 8-BIT 36CH SELECTOR SW BUILT-IN D-A CONVERTER WITH BUFFER AMPLIFIERS

ABSOLUTE MAXIMUM RATINGS(Ta=25°C,unless otherwise noted)

Symbol Ratings

Vcc

Vo

Pd

K

Topr

Tstg Storage temperature

Supply voltage

Output voltage

Power dissipation

Terminal derating

Operating temperature

Parameter

Ta≤25°C

ELECTRICAL CHARACTERISTICS

Digital part(VCC=+3V±10%, VCC=VDD,Ta=-20 ~ +85°C,unless otherwise noted)

Symbol

VCC

Icc

IILK

VIL

VIH

VOL

VOH

Note.Standard value is at Ta=25°C

Supply voltage

Circuit current

Input leak current

Input low voltage

Input high voltage

Output low voltage

Output high voltage

Parameter

CLK=1MHz operation,Vcc=3V,IAO=0µA

IOL=2.5mA

IOH=-400µA

Conditions

Test conditions

-0.3~+7.0

-0.3~Vcc+0.3

-20~+85

-40~+125

Min.

2.7

-10

2.4

VCC-0.4

400

4

Limits

Typ.

3.0

1.0

Max.

5.5

10

0.6

0.4

Unit

V

V

mW

mW/°C

°C

°C

Unit

V

mA

µA

V

V

V

V

Analog part(VCC=+3V±10%, VCC=VDD,Ta=-20 ~ +85°C,unless otherwise noted)

Symbol

IDD Current dissipation

VDD

Vss

VAO

IAO

SDL

SL

SZERO

SFULL

Co

Ro

D-A converter upper reference

voltage range

D-A converter lower reference

voltage range

Buffer amplifier output voltage range

Buffer amplifier output driving

range

Differential nonlinearity error

Nonlinearity error

Zero code error

Full scale error

Output capacitative load

Buffer amplifier output impedance

Parameter

IAO=±100µA

IAO=+300µA

-200µA

Upper saturation voltage=0.4V

Lower saturation voltage=0.3V

Vcc=2.700V

VDD=2.700V

Vss=0.050V

No load(IAO=±0)

Test conditions

Limits

Min.

2.7

GND

0.1 VDD-0.1

-300

-1.0

-1.5

-2

-2

Typ.

5.0

3.0

50

Max.

5.5 V

VDD-2

VDD-0.20.2

500

1.0

1.5

2

2

0.1

Unit

mA

V

V

µA

LSB

LSB

LSB

LSB

µF

Ω

MITSUBISHI

ELECTRIC

( / 5 )

4

Page 5

3V TYPE 8-BIT 36CH SELECTOR SW BUILT-IN D-A CONVERTER WITH BUFFER AMPLIFIERS

AC CHARACTERISTICS(VCC=VDD,Ta=-20 ~ +85°C,unless otherwise noted)

Symbol

tCKL

tCKH

tCR

tCF

tDCH

tCHD

tCHL

tLDC

tLDH

tDo

tLDD

Parameter

Clock "L"pulse width

Clock "H"pulse width

Clock rise time

Clock fall time

Data set up time

Data hold time

LD set up time

LD hold time

LD "H" pulse duration

Data output delay time

D-A converter output setting time

CL=100pF

CL≤100pF,VAO:0.3 2.7V

The time until the output becomes

the final value of ±2 LSB

Test conditions

MITSUBISHI<Dig.Ana.INTERFACE>

M62370GP

Min Typ

200

200

30

60

200

100

100

70 350

Limits

Max

200

100

200

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

µs

TIMING CHART

CLK

DI

LD

D-A

OUTPUT

Do

OUTPUT

tCR tCF

tCKL

tDCH

tCKH

tCHD

tDo

tLDC

tLDH

tCHL

tLDD

MITSUBISHI

ELECTRIC

( / 5 )

5

Loading...

Loading...