Page 1

M I T S U B I S H I

- 9

MITSUBISHI ICs (AV COMMON)

M52797SP/FP

AV SWITCH with I2C BUS CONTROL

PRELIMINARY

Some parametric limits are subject to change.

FEATURES

APPLICATION

Video equipment

RECOMMENDED OPERATING CONDITION

(Lead pitch :1.778mm)

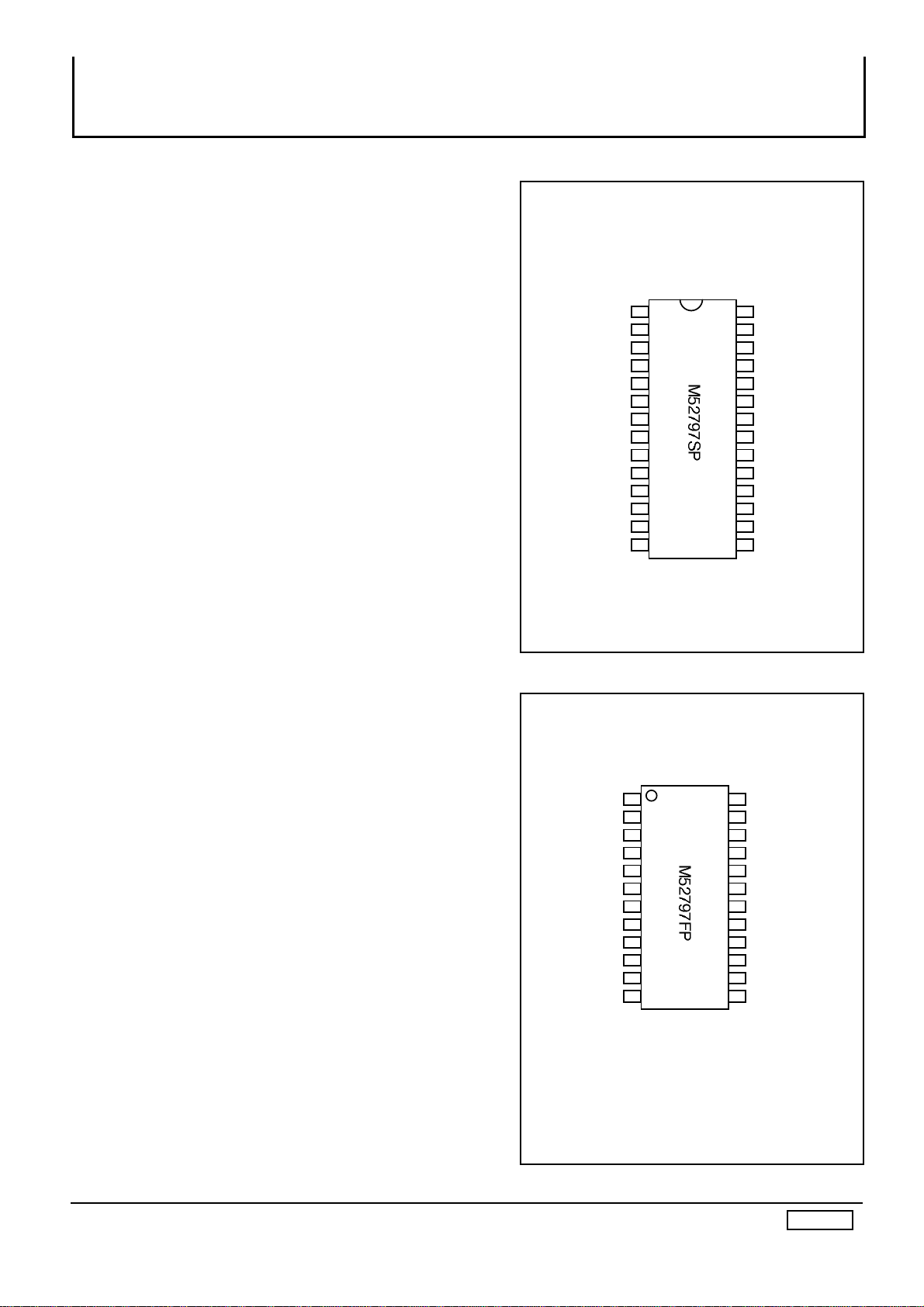

PIN CONFIGURATION ( TOP VIEW )

(Lead pitch :1.27mm)

of

output 0dB or 6dB .

123456714131211109

Lch T IN

Rch 1 OUT

TUNER IN

8

Lch 3 IN

Lch 2 IN

Rch 3 IN

Lch 4 IN

V 1 OUT

28272625242322151617181920

21

BIAS

D5

GND

GND

12345671211109

Rch T IN

V 2 OUT

Lch 1 OUT

8

Lch 3 IN

Lch 2 IN

Rch 3 IN

Lch 4 IN

2423222120191813141516

17

BIAS

D5

GND

Notice. This is not a final specification.

DESCRIPTION

The M52797 is AV switch semiconductor integrated circuit with

I2C bus control .

This IC contains 1-channel of 4-input audio switches and 1channel of 4-input video switches. Each audio switches and

video switches can be controled independently .

The video switches contain amplifiers can be controled a gain

•Video and stereo sound switches in one package

•Wide frequency range ( video switch )...........DC~20MHz

•High separation ( video switch )

.........................Crosstalk -60dB ( typ. ) at 1MHz

•Two types of packages are provided : SDIP with a lead pitch of

1.778mm ( M52797SP ) ; and SOP with a lead pitch of 1.27mm

( M52797FP ) .

PIN CONFIGURATION ( TOP VIEW )

VCC

VCC

VIDEO 2 IN

Rch 2 IN

VIDEO 3 IN

VIDEO 4 IN

Rch 4 IN

SCL

SDA

NC

Outline 28P4B

NC

Rch T IN

Lch 1 OUT

V 2 OUT

D4

CHIP SELECT

NC: No connection

Supply voltage 4.7V~9.3V

Rated supply voltage 5V,9V

Maximum output current 24mA(at 9V)

VCC

VIDEO 2 IN

Rch 2 IN

VIDEO 3 IN

VIDEO 4 IN

Rch 4 IN

SCL

SDA

Outline 24P2N-B

Lch T IN

TUNER IN

V 1 OUT

Rch 1 OUT

D4

CHIP SELECT

1

AUG.'98

Page 2

M I T S U B I S H I

- 9

MITSUBISHI ICs (AV COMMON)

M52797SP/FP

AV SWITCH with I2C BUS CONTROL

PRELIMINARY

Some parametric limits are subject to change.

Lch 3 IN

Rch 2 IN

Rch 3 IN

Rch 4 IN

Lch 4 IN

Lch 2 IN

Lch T IN

V 1 OUT

V 2 OUT

I C Control

BIAS

R

MRL

M

D5

D4

0dB

0dB

0dB

345678910111213161718192021222324252627

15128NC14

V-SW

R-MODE

R-SW

L-SW

L-MODE

SCL

Rch 1 OUT

Lch 1 OUT

VCC

VIDEO 2 IN

TUNER IN

VIDEO 3 IN

VIDEO 4 IN

Notice. This is not a final specification.

BLOCK DIAGRAM

2

0/6dB

Rch T IN

BIAS

L

2

SDA

GND

CHIP SELECT

(at 28P4B)

2

AUG.'98

Page 3

M I T S U B I S H I

- 9

MITSUBISHI ICs (AV COMMON)

M52797SP/FP

AV SWITCH with I2C BUS CONTROL

PRELIMINARY

Some parametric limits are subject to change.

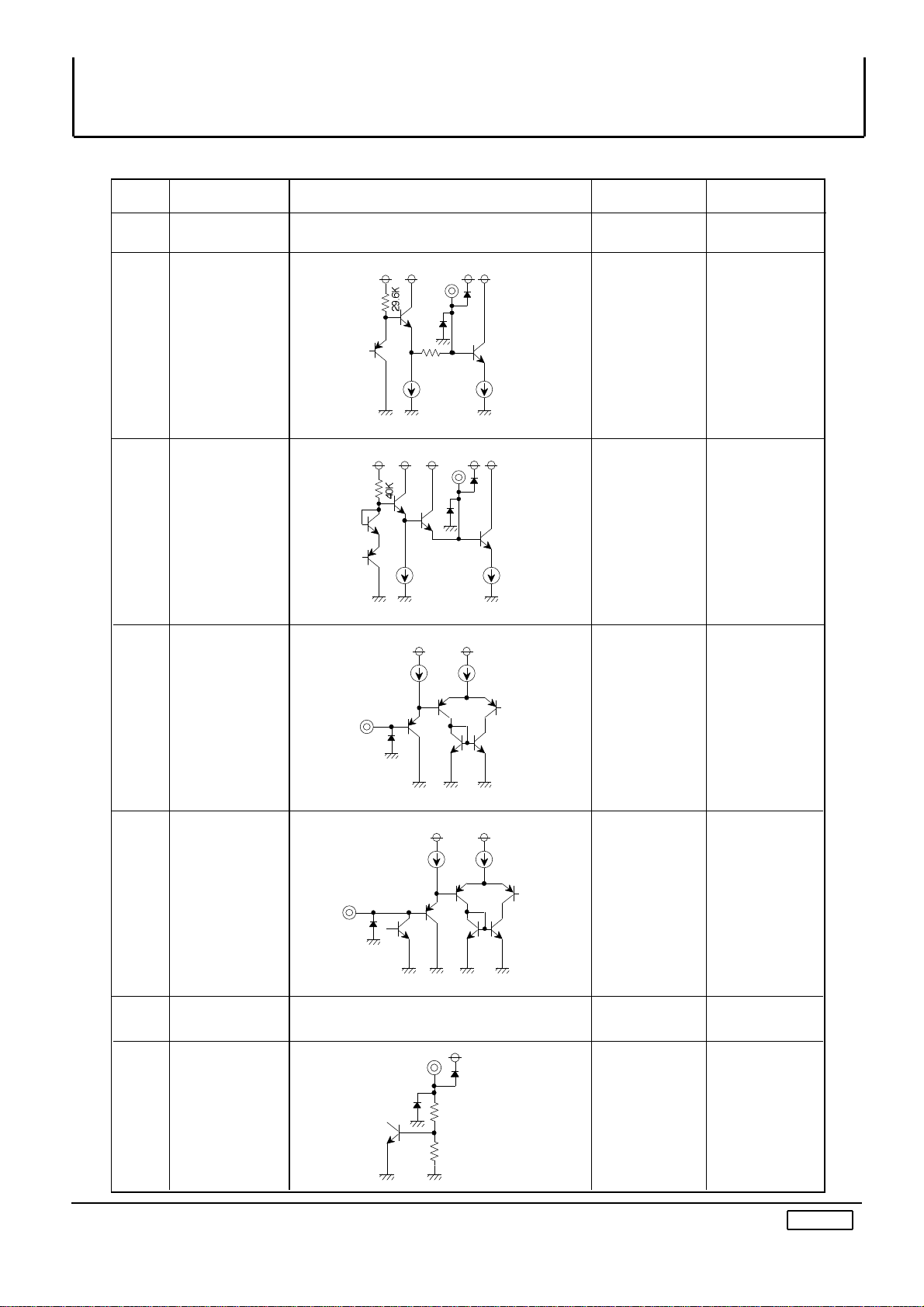

Name

Peripheral circuit pins

Remarks

Vcc3Lch 2 IN

45VIDEO 2 IN

Rch 2 IN

6

Lch 3 IN

7

VIDEO 3 IN

8

Rch 3 IN

9

Lch 4 IN

10

VIDEO 4 IN

11

Rch 4 IN

1213SDA

SCL25Rch T IN

26

TUNER IN

27

Lch T IN

3.6V

4.7V

GND

30K

SELECT

70K

30K

OPEN------90H

Notice. This is not a final specification.

DESCRIPTION OF PIN

Pin No.

1

2

DC voltage(V)

9V

5~9V

Clamp in

15

16

17 CHIP

VIL max.=1.5V

VIH min.=3.0V

VIL max.=1.5V

VIH min.=3.0V

VOL max.=0.4V

(at Iin=3mA)

SLAVE

ADDRESS

0~1.5V-----90H

2.5V~Vcc--92H

3

AUG.'98

Page 4

M I T S U B I S H I

- 9

MITSUBISHI ICs (AV COMMON)

M52797SP/FP

AV SWITCH with I2C BUS CONTROL

PRELIMINARY

Some parametric limits are subject to change.

Pin No.

Name

Peripheral circuit pins

Remarks

D519D4

20

23

21

BIAS

22

Rch 1 OUT

24

Lch 1 OUT

4.2V

1.5K

1.5K

15K

30K5K5K

DC=2.2V

Notice. This is not a final specification.

DESCRIPTION OF PIN (cont.)

DC voltage(V)

18

V 2 OUT

V 1 OUT

VOL max.=0.4V

(at Iin=1mA)

SYNC CHIP

SYNC CHIP

DC=2.9V

4.0V

4

AUG.'98

Page 5

M I T S U B I S H I

- 9

MITSUBISHI ICs (AV COMMON)

M52797SP/FP

AV SWITCH with I2C BUS CONTROL

PRELIMINARY

Some parametric limits are subject to change.

5

A ; Acknownledge

This IC controls channel switchs with 1-byte data ( DATA1) .

the

wired-AND function .

2

123456789129LSBAMSB

SCL

S

A

P : Stop

receiver )

2

Notice. This is not a final specification.

I C BUS

I C BUS(Inter IC BUS)is multi master bus system developed by PHILIPS . Two wires ( SDA - serial data,

SCL - serial clock ) realize functions of start , stop , transferring data , synchronization and arbitration. The

output stages of device connected to the bus must have an open drain or open collector in order to perform

SDA

MSB

S ; Start condition, a high to low transition of the SDA line while SCL is high

P ; Stop condition, a low to high transition of the SDA line while SCL is high

Every byte put on the SDA line must be 8-bits long . Each byte has to be followed by an acknowledge bit. Data

is transferred with the most significant bit (MSB ) first . The data on the SDA line must be stable during the

HIGH period of the clock . The HIGH or LOW state of the data line can only change when the clock signal on

the SCL line is LOW .

LSB

P

CONTROL

S

SLAVE ADDRESS

S : Start

A : Acknowledge

A

DATA1PA

SLAVE ADDRESS

1 0

0

0

1

X

0

0

R/W bit

Usually ` 0 ` ( W : Master transmitter transmits to slave

Possible to select

17PIN Hi:1,Lo:0

(at 28P4B)

AUG.'98

Page 6

M I T S U B I S H I

- 9

MITSUBISHI ICs (AV COMMON)

M52797SP/FP

AV SWITCH with I2C BUS CONTROL

PRELIMINARY

Some parametric limits are subject to change.

6

M52797 FUNCTION TABLE

S

SLAVE ADDRESS

A

DATA(D7~D0)

APSLAVE ADDRESS

SLAVE ADDRESS

A6A5A4A3A2A1A0

R/W100100

0 / 10DATA1 CONT

DATA

D7D6D5D4D3D2D1D0CONT

AUDIO MODE

I/O

I/O

V AMP

SW CONT

VIDEO SW CONT

AUDIO MODE CONT

DATA

OUT

DATA

MODE

V-SW

V OUT

D7D6D1D000MUTE

00T IN01

R/R01

V 2 IN

10L/L10

V 3 IN

11NORMAL

11V 4 IN

AUDIO SW CONT

MODE

MUTE

R/R

L/L

NORMAL

DATA

OUT

OUT

OUT

OUTD1D0

Lch OUT 1

Rch OUT 1

Lch OUT 1

Rch OUT 1

Lch OUT 1

Rch OUT 1

Lch OUT 1

Rch OUT 1

00MUTE

MUTE

Rch T IN

Rch T IN

Lch T IN

Lch T IN

Lch T IN

Rch T IN

01MUTE

MUTE

Rch 2 IN

Rch 2 IN

Lch 2 IN

Lch 2 IN

Lch 2 IN

Rch 2 IN

10MUTE

MUTE

Rch 3 IN

Rch 3 IN

Lch 3 IN

Lch 3 IN

Lch 3 IN

Rch 3 IN

11MUTE

MUTE

Rch 4 IN

Rch 4 IN

Lch 4 IN

Lch 4 IN

Lch 4 IN

Rch 4 IN

AMP GAIN CONT.

I/O CONT.

DATA

AMP

DATA

OUT

DATA

OUTD3V AMP1

D4

D4 OUT

D5

D5 OUT

0

0dB0HI0HI16dB1LO1LO

Notice. This is not a final specification.

Data byte format

AUG.'98

Page 7

M I T S U B I S H I

- 9

MITSUBISHI ICs (AV COMMON)

M52797SP/FP

AV SWITCH with I2C BUS CONTROL

PRELIMINARY

Some parametric limits are subject to change.

7

Parameter

Test condition

Max.

Unit

Supply voltage

V

VIDEO

Icc

Vcc=9V,Vin=0Vp-p ,Rl=∞Ω

9.324322027

(Ta=25°C,Vcc=9V,unless otherwise noted)

-

ELECTRICAL CHARACTERISTICS

characteristics

Input impedance

AUDIO

F

D

dBdBVp-p

dB

distortion<1.0%

0

5.566.5

0

-2.042

-54----

-

Frequency characteristics

6.0

0

Notice. This is not a final specification.

Circuit current

Voltage gain

Frequency

Dynamic Range

Crosstalk

Voltage gain

Total harmonic distortion

Dynamic Range

Output DC offset voltage

Input impedance

Crosstalk

Symbol

Vcc

G

ZIV

CT

G

F

THD

D

VOFF

Z1

CT

Vcc=5V,Vin=0Vp-p ,Rl=∞Ω

f=100kHz,1Vp-p (0dB)(T V1OUT)

f=100kHz,1Vp-p (6dB)(T V1OUT)

f=10MHz/100kHz,1Vp-p (0dB)(T V1OUT)

f=10MHz/100kHz,1Vp-p (6dB)(T V1OUT)

Vcc=9V(0dB)(T V1OUT)

Vcc=5V(0dB)(T V1OUT)

Clamp in(T,V2,V3,V4)

f=1MHz,1Vp-p T V1OUT (at V2 mode)

f=1kHz ,1Vp-p (Vcc9V)(RT R1OUT)

f=1kHz ,1Vp-p (Vcc5V)(RT R1OUT)

f=100kHz/1kHz , 1Vp-p(RT R1OUT)

f=1kHz,2Vp-p,at 400HzHPF+30kHzLPF

(RT R1OUT)

f=1kHz ,Maximum with distortion<0.5%

(RT R1OUT)

(MODE:RT,R2,R3,R4 R1OUT )

(RT,R2,R3,R4,LT,L2,L3,L4 )

1kHz,1Vp-p RT R1OUT(at R2 mode)

f=100kHz

Maximum with

Min.

4.7

-0.5

-2.0

-0.5

-0.5

-2.0

5.5

-20

22

-

-

-

Typ.

-

0.5

2.0

2.0

-

-

-60

0

0.5

0.5

0

0 1.0

0.01 0.05

-

0

20

30

-90- -84

38

mA

kΩ

dB

dB

%

Vp-p

mV

kΩ

dB

AUG.'98

Page 8

M I T S U B I S H I

- 9

MITSUBISHI ICs (AV COMMON)

M52797SP/FP

AV SWITCH with I2C BUS CONTROL

PRELIMINARY

Some parametric limits are subject to change.

tBUF

P

tHD;STA

tLOWtRtHD;DAT

tHIGHtFtSU;DAT

tSU;STA

Sr

tHD;STA

tSU;STO

P

SDA

I C BUS CONTROL SIGNAL

2

I2C BUS CONTROL SIGNAL

(Ta=25°C,Vcc=9V,unless otherwise noted)

ELECTRICAL CHARACTERISTICS

Max. input high voltage

4.0

4.0

5.0

4.0--

1000

kHzµSµSnS-------

Low level input current

Time of bus must be free before

Hold time at start condition

The high period of the clock

Hold time DATA

Rise time of both SDA and SCL line

Setup time for stop condition

V

SDA , SCL = 4.5 V

3.0

0.0

-10

1.5

1010----------------0.0

Symbol

Min.

Typ.

a new transmission can start

Notice. This is not a final specification.

Parameter

Min. input low voltage

Low level output voltage(SDA)

High level input current

SCL clock frequency

The low period of the clock

Setup time for start condition

Setup time DATA

VIH

VIL

VOL

IIH

IIL

fSCL

tBUF

tHD;STA

tLOW

tHIGH

tSU;STA

tHD;DAT

tSU;DAT

tR

Test condition

SDA = 3mA

SDA , SCL = 0.4 V

0.0

-10

4.7

4.7

4.7

250

Max.

5.0

0.4

100

Unit

µA

Fall time of both SDA and SCL line

SCL

S

tF

tSU;STO

300

-

8

AUG.'98

Page 9

M I T S U B I S H I

- 9

MITSUBISHI ICs (AV COMMON)

M52797SP/FP

AV SWITCH with I2C BUS CONTROL

PRELIMINARY

Some parametric limits are subject to change.

9

Application Circuit Example

slave address Cange(VCC/GND)

272625242322151617181920212345671413121110981NCRch T IN

Lch T IN

VIDEO 3 IN

Rch 1 OUT

V 2 OUT

TUNER IN

Lch 1 OUT

VCC

Rch 2 IN

Lch 3 IN

VIDEO 2 IN

Lch 2 IN

Rch 4 IN

Rch 3 IN

VIDEO 4 IN

Lch 4 IN

SDA

NC

SCL

V 1 OUT

BIAS

D4D5CHIP SELECT

GND

VCC

GND

100u

10u750.47u

10u

10u750.47u

10u

10u750.47u

10u

10K

220

10K

220

10u

0.47u7510u

10u

5V

0.01u

75

75

Notice. This is not a final specification.

VCC

28

10K

10K

5V

Note how to use this IC

Input signal with sufficient low impedance to input terminal.

The capacitance of output terminal as small as possible.

Set the capacitance between Vcc and GND near the pins if possible.

Assign an area as large as possible for grounding.

Power-on Reset

The M52797 has an intermal power-on reset function that sets each

control r egister to "0" during IC power ON.

The power-on reset VTH has 2.5V.

(at 28P4B)

AUG.'98

Loading...

Loading...