Datasheet M34570M4-XXXFP, M34570EDFP, M34570E8FP, M34570MD-XXXFP, M34570M8-XXXFP Datasheet (Mitsubishi)

Page 1

DESCRIPTION

The 4570 Group is a 4-bit single-chip microcomputer designed

with CMOS technology. Its CPU is that of the 4500 series using

a simple, high-speed instruction set. The computer is equipped

with a carrier wave output circuit for remote control, an 8-bit timer

with a reload register, a 10-bit timer with a reload register, and

an 8-bit timer with two reload registers.

The various microcomputers in the 4570 Group include variations

of the built-in memory size. The mask ROM version and One

Time PROM version of 4570 Group are produced as shown in

the table below.

FEATURES

●Minimum instruction execution time

When f(X

(f(X

When f(X

(f(X

●Supply voltage

............................. 2.5 V to 5.5 V (One Time PROM version)

.......................................2.0 V to 5.5 V (Mask ROM version)

IN) is selected for system clock.......................1.5

IN)=2.0 MHz, VDD=4.5 V to 5.5 V)

IN)/4 is selected for system clock................. 2.86

IN)=4.2 MHz, VDD=2.0 V to 5.5 V)

µ

µ

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

●System clock switch function

.............................................................f(X

●Timers

Timer 1... 10-bit timer with a reload register and carrier wave

output auto-control function

Timer 2 ................................8-bit timer with a reload register

Timer 3... 8-bit timer with two reload registers and carrier wave

generation function

●Interrupt ...................................................................4 sources

●Power-on reset circuit

●Watchdog timer ............................................................16 bits

●Key-on wakeup function (Ports P0, P1, and P4, ON/OFF of

port P4 can be switched)

●Pull-up transistor.............. (Ports P0, P1, and P4, ON/OFF of

s

port P4 can be switched)

●Voltage drop detection circuit

s

●Clock generating circuit (ceramic resonance)

APPLICATION

Remote control transmitter

IN)/4 or not divided

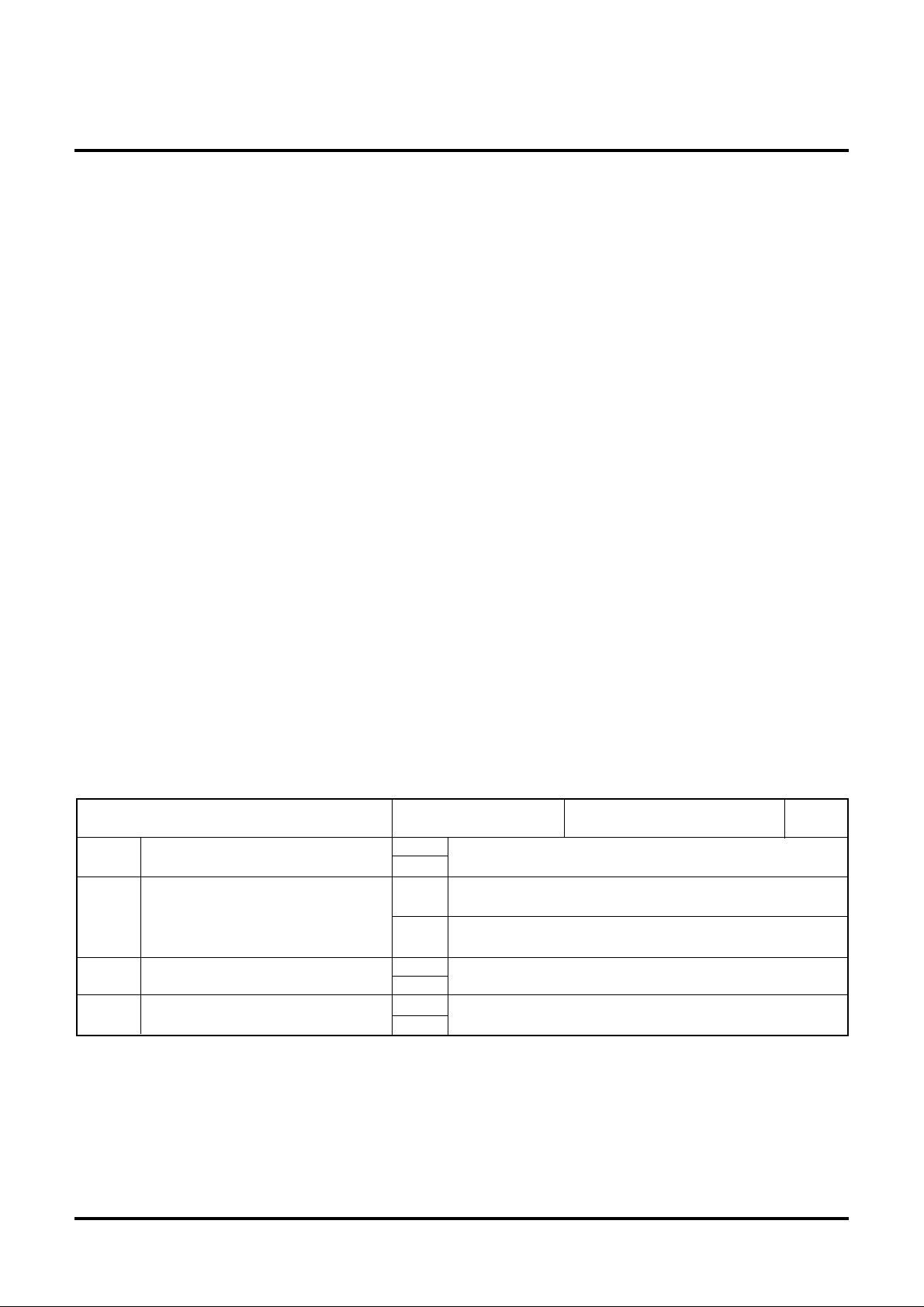

Product

M34570M4-XXXFP

M34570M8-XXXFP

M34570MD-XXXFP

M34570E8FP

M34570EDFP *

*: Under development (Jan. 1999)

ROM (PROM) size

(✕ 10 bits)

4096 words

8192 words

16384 words

8192 words

16384 words

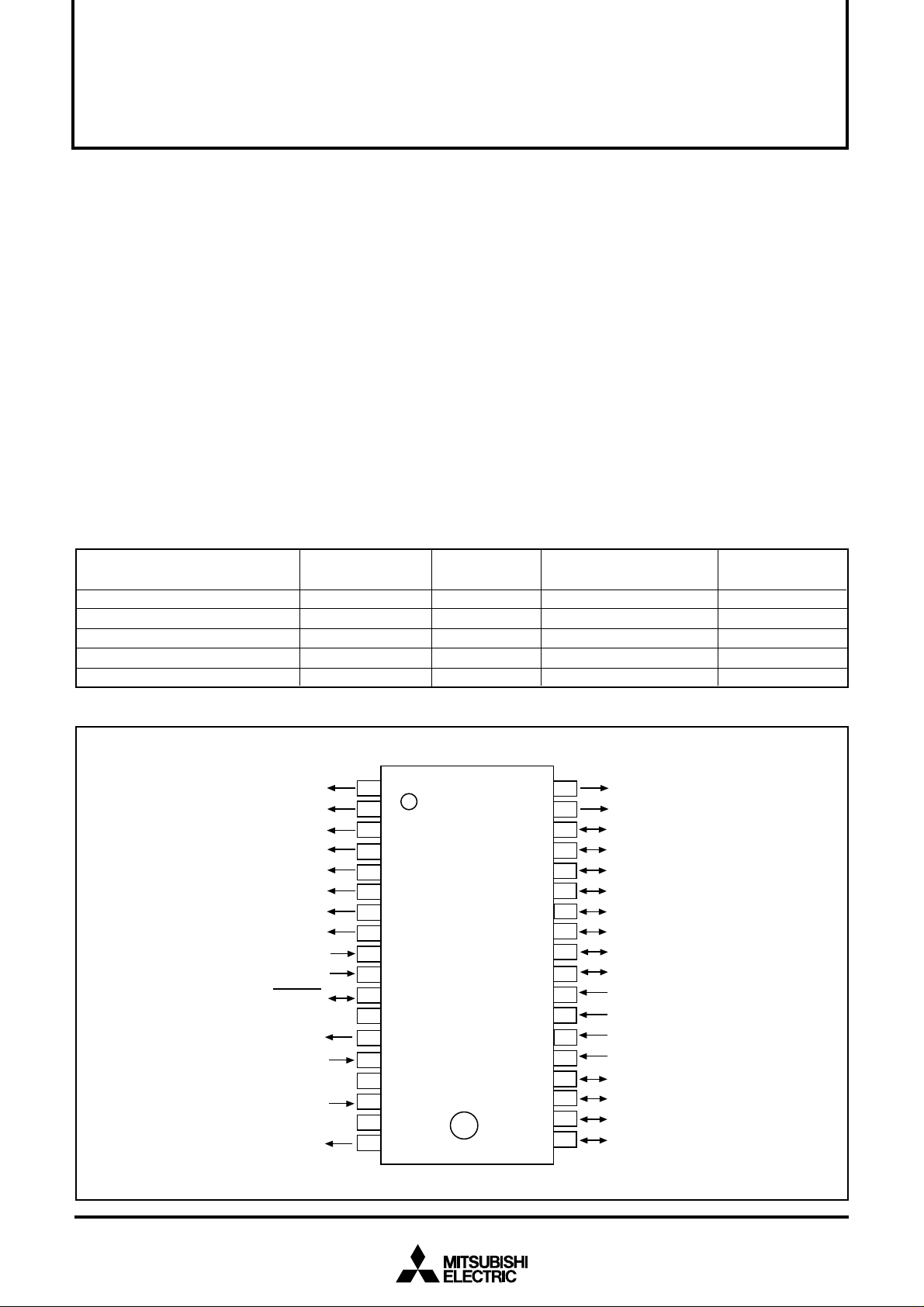

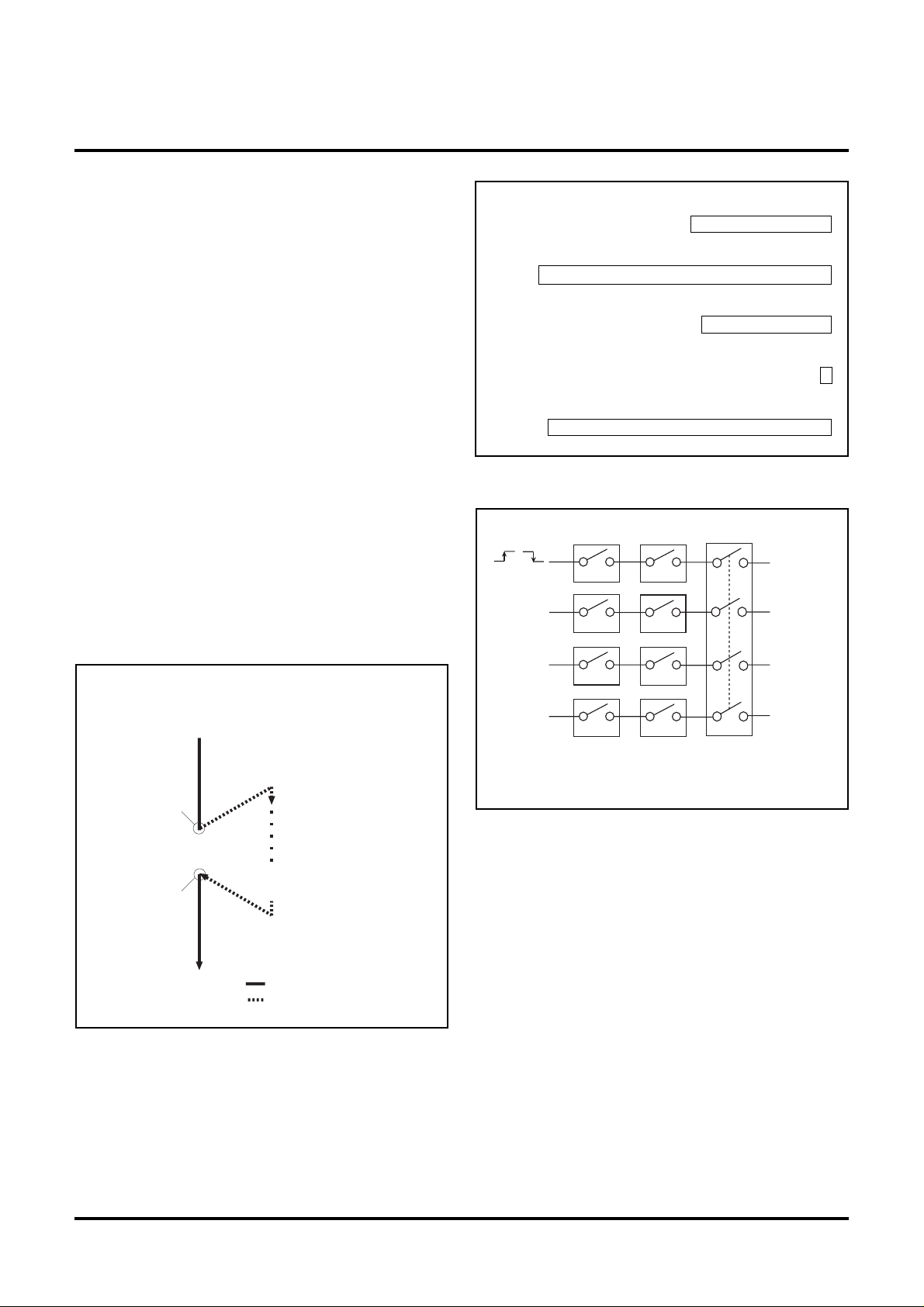

PIN CONFIGURATION (TOP VIEW)

M34570Mx-XXXFP

D9/T

P21/INT

RESET

CNV

X

VDCE

CARR

D

D

D

D

D

D

D

OUT

P2

SS

OUT

X

IN

V

SS

V

DD

2

3

4

5

6

7

8

0

10

11

12

13

14

15

16

17

18

RAM size

(✕ 4 bits)

128 words

128 words

128 words

128 words

128 words

1

2

3

4

M34570Mx-XXXFP

5

6

7

8

9

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

Package

36P2R-A

36P2R-A

36P2R-A

36P2R-A

36P2R-A

D

1

D

0

P1

3

P1

2

P1

1

P1

0

P0

3

P0

2

P0

1

P0

0

P4

3

P4

2

P4

1

P4

0

P3

3

P3

2

P3

1

P3

0

ROM type

Mask ROM

Mask ROM

Mask ROM

One Time PROM

One Time PROM

Outline 36P2R-A

Page 2

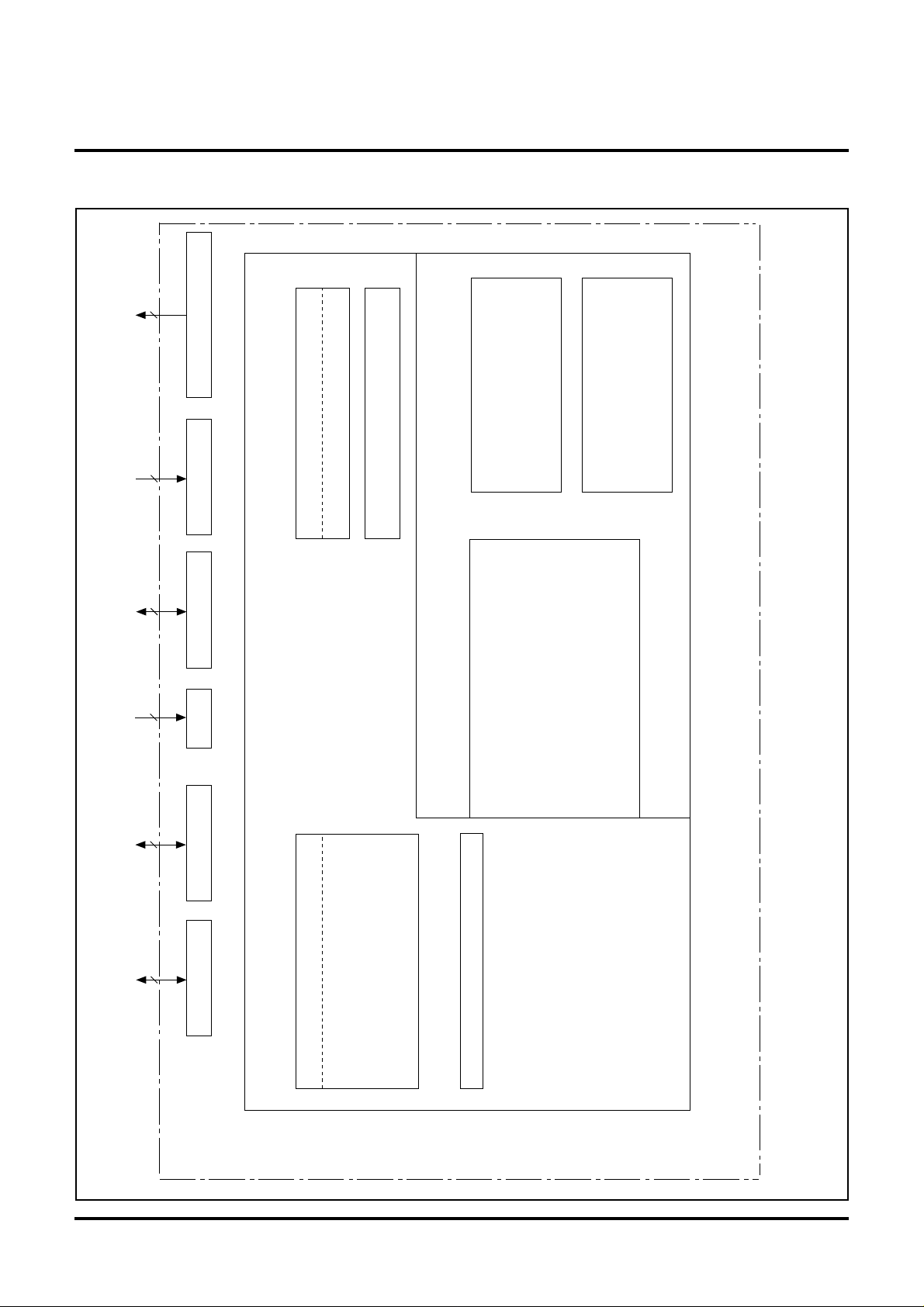

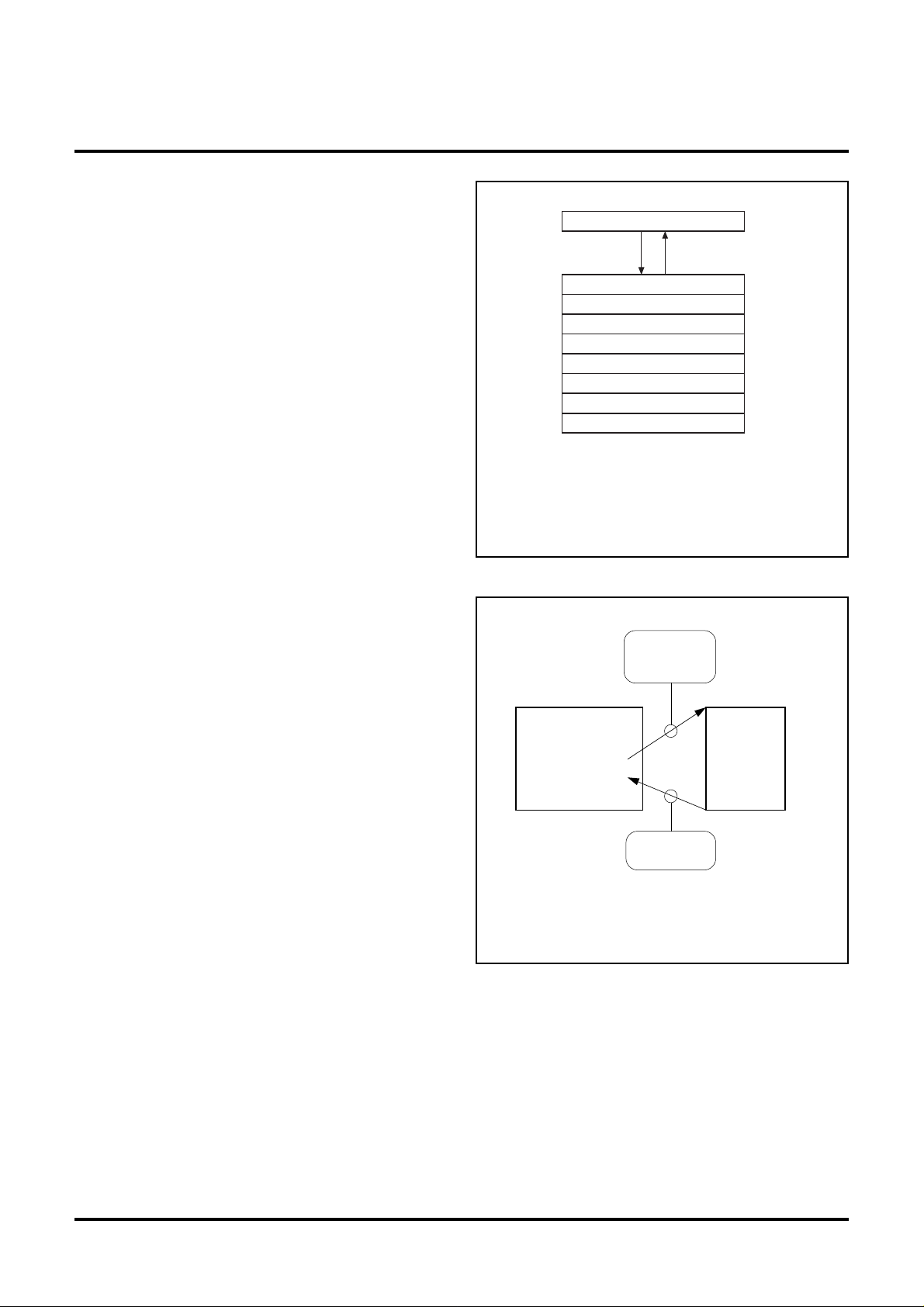

BLOCK DIAGRAM

10

Port D

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

OUT

–X

IN

X

4

Port P4

4

Port P3

2

Port P2

Clock generating circuit

Reset (Voltage drop detection circuit)

Memory

ROM (Note)

4096 to 16384 words ✕ 10 bits

CPU core

ALU(4 bits)

RAM

128 words ✕ 4 bits

Register B (4 bits)

Register E (8 bits)

4500 Series

Stack registers SKs (8 levels)

Interrupt stack register SDP(1 level)

Register D (3 bits)

Register A (4 bits)

4

Note: PROM 16384 words ✕ 10 bits for the built-in PROM version.

Port P1

4

Port P0

Timers/Carrier wave generation

Timer 2 (8 bits)

Timer 3 (8 bits)

Timer 1 (10 bits)

(Carrier wave generation)

Watchdog timer (16 bits)

Internal peripheral functions

I/O port

2

Page 3

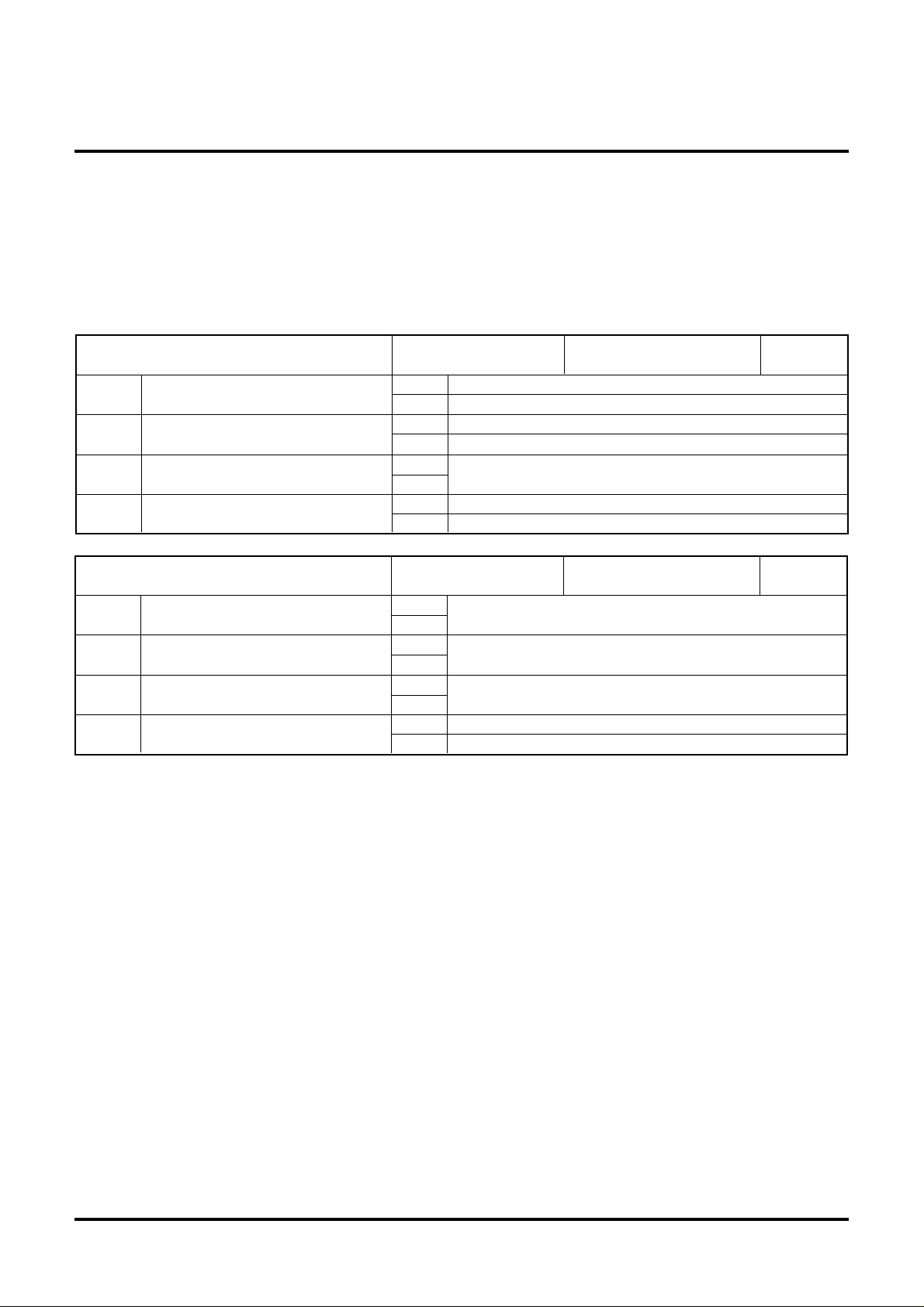

PERFORMANCE OVERVIEW

Parameter

Number of basic instructions

Minimum instruction execution time

Memory sizes

ROM

RAM

Input/Output

ports

0–D9

D

P00–P03

P10–P13

P20, P21

P30–P33

P40–P43

CARR

OUT

T

INT

Timers

Timer 1

Timer 2

Timer 3

Interrupt

Sources

Nesting

Subroutine nesting

Device structure

Package

Operating temperature range

Supply voltage

Power

at active

dissipation

(typical value)

at RAM back-up

M34570M4

M34570M8

M34570MD

M34570E8

M34570ED

Output

I/O

I/O

Input

I/O

Input

Output

Output

Input

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Function

99

µ

s (f(XIN) = 2.0 MHz:system clock = f(XIN): VDD = 5.0 V)

1.5

µ

s (f(XIN) = 4.2 MHz:system clock = f(XIN)/4: VDD = 5.0 V)

2.86

4096 words ✕ 10 bits

8192 words ✕ 10 bits

16384 words ✕ 10 bits

8192 words ✕ 10 bits

16384 words ✕ 10 bits

128 words ✕ 4 bits

Ten independent output ports; port D

4-bit I/O port; every pin of the ports has a key-on wakeup function and a pull-up function.

4-bit I/O port; every pin of the ports has a key-on wakeup function and a pull-up function.

2-bit input port, port P2

1 is also used as INT input pin.

4-bit I/O port

4-bit input port; both pull-up function and key-on wakeup function can be switched by software.

1-bit output port (CMOS output)

1-bit output pin; T

OUT output pin is also used as port D9.

1-bit input pin with a key-on wakeup function. INT input pin is also used as port P2

10-bit timer with a reload register and carrier wave output auto-control function

8-bit timer with a reload register

8-bit timer with two reload registers and carrier wave generation function

4 (one for external and three for timer)

1 level

8 levels (however, only 7 levels can be used when an interrupt is used or the TABP p instruction

is executed)

CMOS silicon gate

36-pin plastic molded SSOP

–20 °C to 70 °C

2.0 V to 5.5 V for mask ROM version (2.5 V to 5.5 V for One Time PROM version)

1.3 mA (f(X

0.5 mA (f(X

µ

0.1

IN) = 4.2 MHz: system clock = f(XIN)/4, VDD=5.0 V)

IN) = 1.0 MHz: system clock = f(XIN), VDD=3.0 V)

A (Ta=25 °C, VDD=5V, typical value)

9 is also used as the TOUT output pin.

1.

DEFINITION OF CLOCK AND CYCLE

●System clock

The system clock is the basic clock for controlling this product.

The system clock can be selected by bit 3 of the clock control

register MR as shown in the table below.

Table Selection of system clock

MR3

Note: f(X

from reset.

f(X

f(X

IN)

IN)/4

0

1

IN)/4 is selected immediately after system is released

System clock

●Instruction clock

The instruction clock is the standard clock for controlling CPU.

The instruction clock is a signal derived from dividing the

system clock by 3. The one cycle of the instruction clock is

equivalent to the one machine cycle.

●Machine cycle

The machine cycle is the standard cycle required to execute

the instruction.

3

Page 4

PIN DESCRIPTION

Pin

DD

V

VSS

CNVSS

RESET

XIN

XOUT

D0–D9

P00–P03

P10–P13

P20, P21

P30–P33

P40–P43

CARR

INT

OUT

T

VDCE

Name

Power supply

Ground

SS

CNV

Reset input

Clock input

Clock output

Output port D

I/O port P0

I/O port P1

Input port P2

I/O port P3

Input port P4

Carrier wave output

for remote control

Interrupt input

Timer output

Voltage drop

detection circuit

enable

Input/Output

—

—

Input

I/O

Input

Output

Output

I/O

I/O

I/O

I/O

Input

Output

Input

Output

Input

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Function

Connected to a plus power supply.

Connected to a 0 V power supply.

Connect CNV

An N-channel open-drain I/O pin for a system reset. A pull-up transistor and a

capacitor are built-in this pin. When the watchdog timer causes the system to be

reset or the low-supply voltage is detected, the

I/O pins of the clock generating circuit. Connect a ceramic resonator between X

pin and XOUT pin. A feedback resistor is built-in between them.

Each pin of port D has an independent 1-bit wide output function. Port D

used as T

4-bit I/O port. It can be used as an input port when the output latch is set to “1.”

The output structure is N-channel open-drain. Every pin of the ports has a key-on

wakeup function and a pull-up function.

4-bit I/O port. It can be used as an input port when the output latch is set to “1.”

The output structure is N-channel open-drain. Every pin of the ports has a key-on

wakeup function and a pull-up function.

2-bit input port. Port P2

4-bit I/O port. It can be used as an input port when the output latch is set to “1.”

The output structure is N-channel open-drain.

4-bit input port. Every pin of the ports has a key-on wakeup function and a pull-up

function. Both functions can be switched by software.

Carrier wave output pin for remote control transmit. The output structure is the

CMOS circuit.

INT input pin accepts an external interrupt and has a key-on wakeup function. INT

input pin is also used as port P2

OUT output pin has the function to output the timer 2 underflow signal divided by

T

OUT output pin is also used as port D9.

2. T

VDCE pin is used to control the operation/stop of the voltage drop detection circuit.

The circuit is operating when “H” level is input to the VDCE pin. It is stopped when

“L” level is input to this pin.

SS to VSS and apply “L” (0V) to CNVSS certainly.

RESET pin outputs “L” level.

9 is also

OUT output pin. The output structure is N-channel open-drain.

1 is also used as the INT input pin.

1.

IN

4

Page 5

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

MULTIFUNCTION

Pin

9

D

P21

OUT

T

INT

Notes 1: Pins except above have just single function.

2: The port D

9 is the output port and port P21 is the input port.

CONNECTIONS OF UNUSED PINS

Pin

0–D8

D

D9/TOUT

P00–P03

P10–P13

P20, P21/INT

Notes 1: When the P21/INT pin is connected to VSS pin, set the return level to “H” level by software (interrupt control register I12=“1”).

When the P2

state immediately after system enters the RAM back-up state.

2: In order to connect ports P4

also invalidate the key-on wakeup functions (key-on wakeup control register K0i=“0”). When these pins are connected to

V

SS while the key-on wakeup functions are left valid, the system fails to return from RAM back-up state. In order to make

these pins open, turn on their pull-up transistors (register PU0i=“1”) by software (i = 0, 1, 2, 3).

Be sure to select the key-on wakeup function and the pull-up function with every one port.

3: In order to make ports P4

Connect to V

“0” and open.

Set the output latch to “1” and open.

Connect to V

1/INT pin is connected to VSS pin while the return level is set to “L” level, system returns from RAM back-up

Multifunction

Connection

SS, or set the output latch to

T

INT

P3

OUT

0–P33

Pin

Pin

9

D

P21

Connect to V

Multifunction

Connection

SS, or set the output latch to

“0” and open.

P40–P43

CARR

SS (Note 1).

0–P43 to VSS, turn off their pull-up transistors (pull-up control register PU0i=“0”) by software and

0–P43 open, turn on their pull-up transistors (register PU0i = “1”) by software (i = 0, 1, 2, 3).

Connect to V

Open.

SS (Note 2) or open (Note 3).

(Note in order to set the output latch to “0” or “1” or make pins open)

• After system is released from reset, a port is in a high-impedance state until the output latch of the port is set to “0” by software.

Accordingly, the voltage level of pins is undefined and the excess of the supply current may occur.

• To set the output latch periodically is recommended because the value of output latch may change by noise or a program run away

(caused by noise).

(Note in order to connect unused pins to V

• To avoid noise, connect the unused pins to V

SS)

SS at the shortest distance using a thick wire.

PORT FUNCTION

Port

Port D

Pin

D

0–D8, D9/TOUT

Input/

Output

Output

Output structure

N-channel open-drain

Control

bits

(10)

Port P0

P00–P03

I/O

N-channel open-drain

(4)

Port P1

P10–P13

I/O

N-channel open-drain

(4)

Port P2

P20

Input

(2)

P21/INT

Port P3

Port P4

0–P33

P3

P40–P43

I/O

Input

N-channel open-drain

(4)

Note: Level of the P21/INT pin can be examined with the SNZI0 instruction.

1

4

4

2

4

4

Control

instructions

SD

RD

CLD

OP0A

IAP0

OP1A

IAP1

IAP2

SNZI0

(Note)

OP3A

IAP3

IAP4

Control

registers

2

W2

PU0

K0

Remark

W22 controls the switch of D9/

OUT pin

T

Pull-up functions

Key-on wakeup functions

Pull-up functions

Key-on wakeup functions

Key-on wakeup function

Pull-up functions

(programmable)

Key-on wakeup functions

(programmable)

5

Page 6

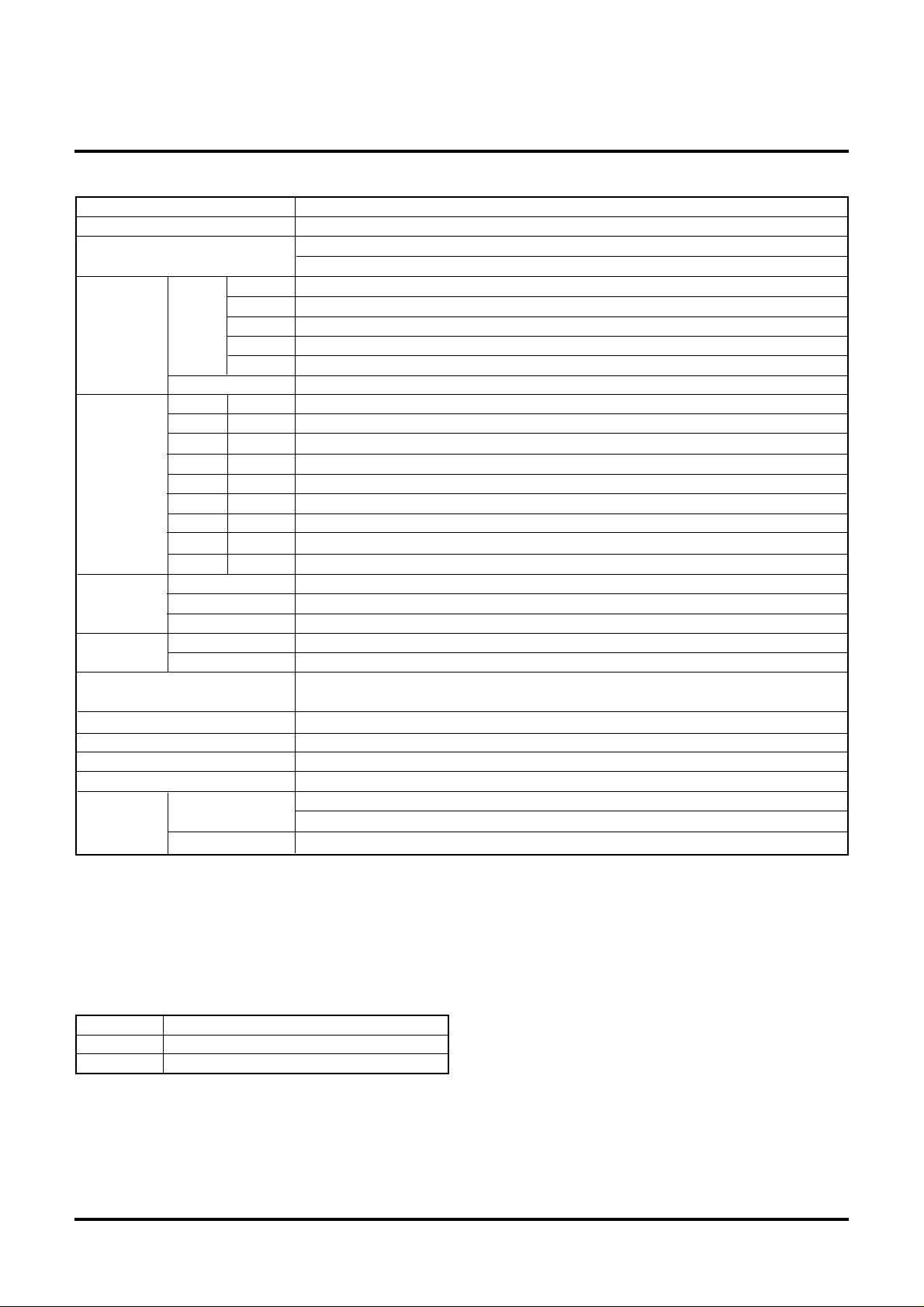

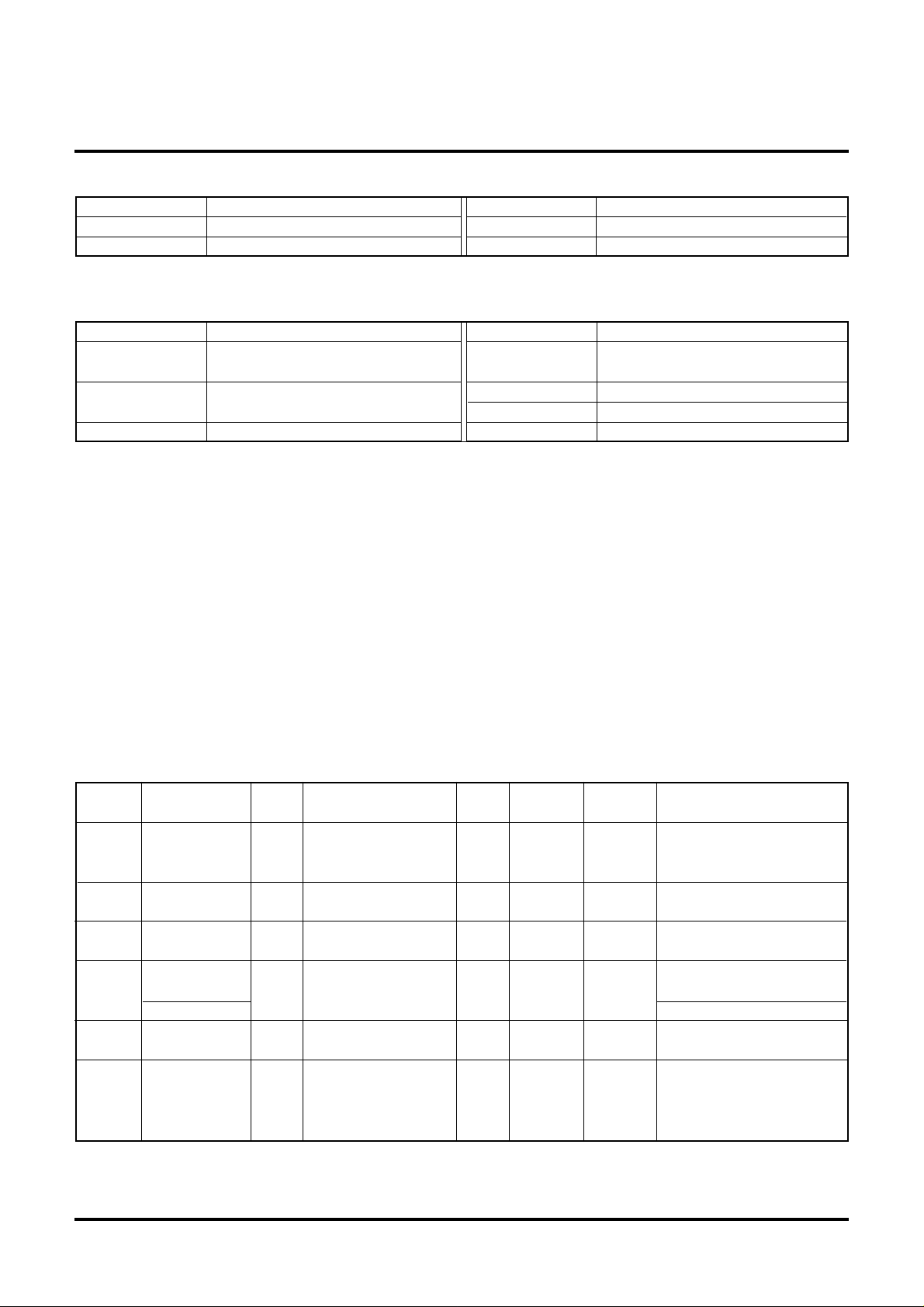

PORT BLOCK DIAGRAMS

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Key-on wakeup

Register A

(Note 2)

Key-on wakeup

Register A

(Note 2)

Key-on wakeup

input

Register A

input

Ai

OP0A instruction

input

Ai

OP1A instruction

K00

IAP4 instruction

IAP0 instruction

Q

D

T

IAP1 instruction

DTQ

Pull-up

transistor

PU00

Pull-up

transistor

Pull-up

transistor

(Note 1)

P40

(Note 1)

(Note 1)

P00–P03

P10–P13

Register A

(Note 2)

Register A

Key-on wakeup

Register A

instruction

input

IAP3 instruction

Ai

OP3A

IAP2 instruction

External interrupt circuit

IAP2 instruction

D

Q

T

P20

(Note 1)

P21/INT

(Note 1)

P30–P33

(Note 1)

Key-on wakeup

Key-on wakeup

Key-on wakeup

input

Register A

input

Register A

input

Register A

K01

IAP4 instruction

K02

IAP4 instruction

K03

IAP4 instruction

Pull-up

transistor

PU01

Pull-up

transistor

PU02

Pull-up

transistor

PU03

(Note 1)

(Note 1)

(Note 1)

Register Y

SD instruction

RD instruction

P41

Register Y

SD instruction

RD instruction

Timer 2 underflow signal output

P42

Notes 1.

P43

Decoder

CLD

instruction

Decoder

CLD

instruction

This symbol represents a parasitic diode.

Applied potential to ports P2

2. i represents 0, 1, 2 or 3.

S

RQ

S

W22

RQ

1/2

0

1

0 and P21 must be VDD or less.

D0–D8

(Note 1)

D9/TOUT

(Note 1)

6

Page 7

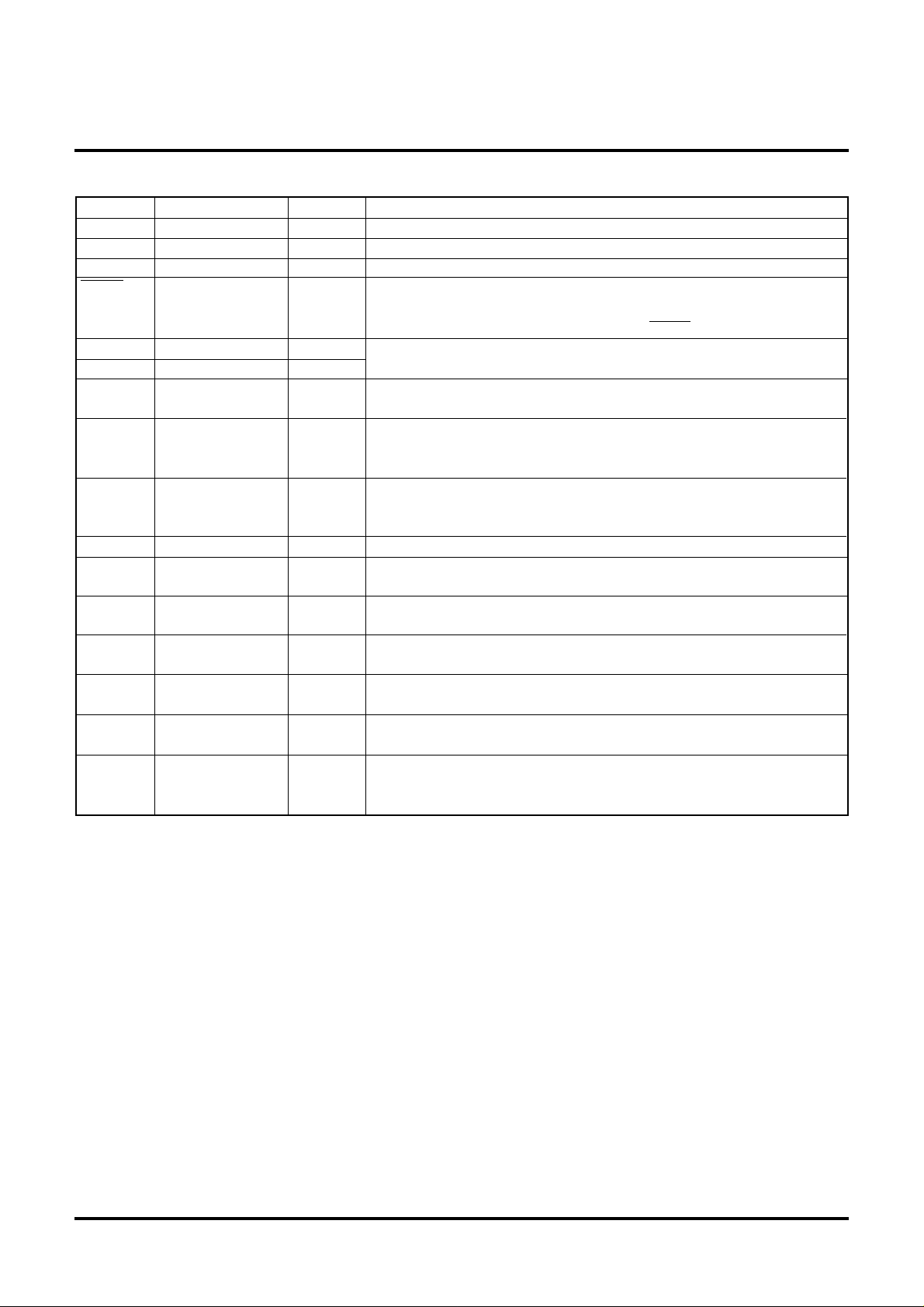

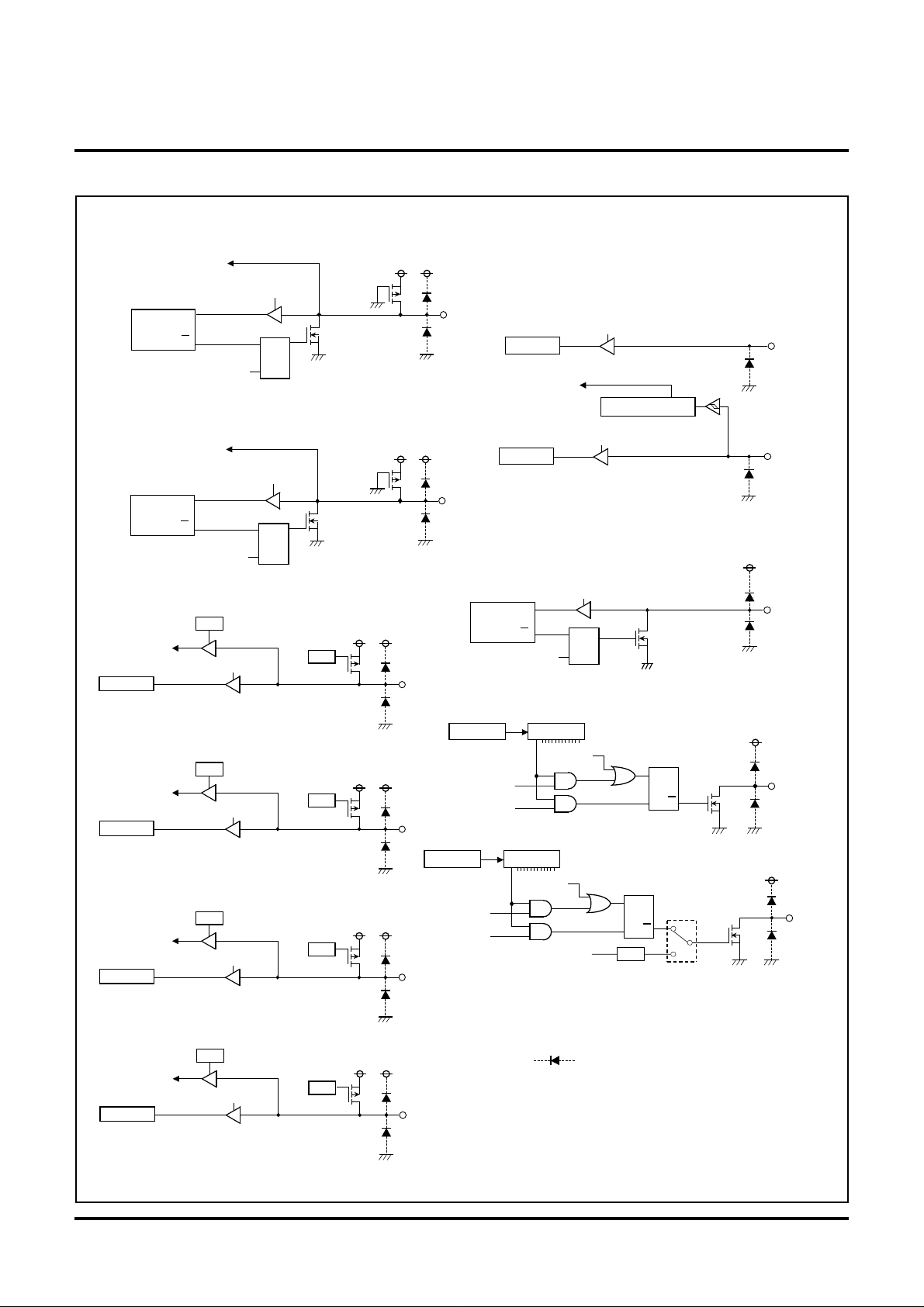

PORT BLOCK DIAGRAMS (continued)

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Timer 2 underflow

signal

ORCLK

X

Register B Register A

(T3HAB)

Reload register R3H (8)

W31,W3

0

W3

00

01

10

MR

3

IN

1/2

11

0

Not available

1

0

1

(TAB3)

3

(T3AB)

Reload register R3L (8)

Register B Register A

Timer 3(8)

(T3AB)

Timer 1 underflow

signal

Reload control circuit

(TAB3)

C2

0

Q

T

R

W3

3

Q

T

R

W1

0

To timer 1

C2

1

CARRY

(Note)

Port CARR

T3F

This symbol represents a parasitic diode.Note :

Timer 3

interrupt

7

Page 8

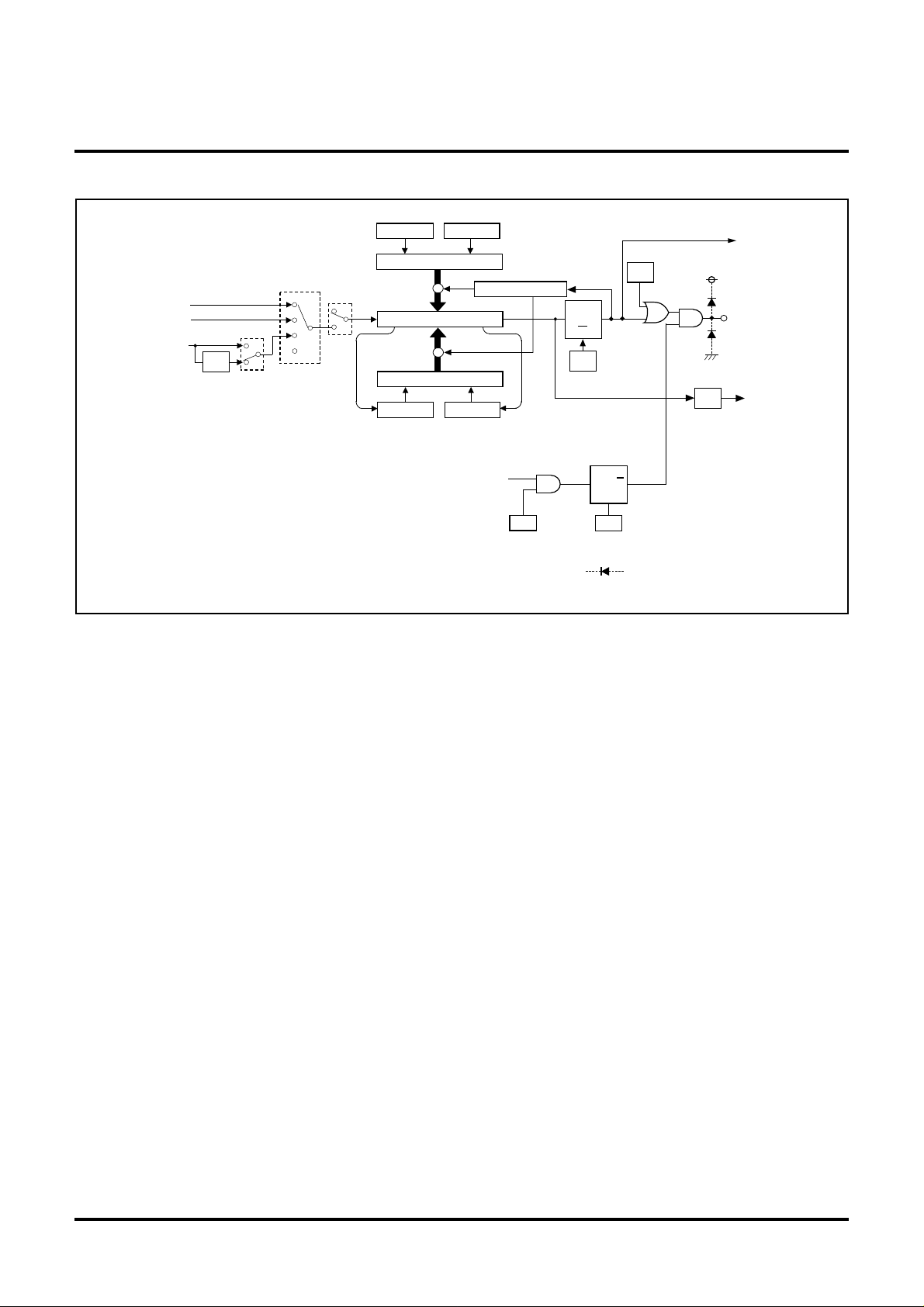

FUNCTION BLOCK OPERATIONS

CPU

(1) Arithmetic logic unit (ALU)

The arithmetic logic unit ALU performs 4-bit arithmetic such

as 4-bit data addition, comparison, AND operation, OR

operation, and bit manipulation.

(2) Register A and carry flag (CY)

Register A is a 4-bit register used for arithmetic, transfer,

exchange, and I/O operation.

Carry flag CY is a 1-bit flag that is set to “1” when there is a

carry with the AMC instruction (Figure 1).

It is unchanged with both A n instruction and AM instruction.

The value of A

instruction (Figure 2).

Carry flag CY can be set to “1” with the SC instruction and

cleared to “0” with the RC instruction.

(3) Registers B and E

Register B is a 4-bit register used for temporary storage of 4bit data, and for 8-bit data transfer together with register A.

Register E is an 8-bit register. It can be used for 8-bit data

transfer with register B used as the high-order 4 bits and

register A as the low-order 4 bits (Figure 3).

0 is stored in carry flag CY with the RAR

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

<Carry>

(CY)

(M(DP))

Addition

(A)

Fig. 1 AMC instruction execution example

<Set>

SC instruction

<Clear>

RC instruction

CY A3A2A1A

A

0

Fig. 2 RAR instruction execution example

ALU

<Result>

<Rotation>

RAR instruction

CY A3A2A

0

1

(4) Register D

Register D is a 3-bit register.

It is used to store a 7-bit ROM address together with register

A and is used as a pointer within the specified page when the

TABP p, BLA p, or BMLA p instruction is executed (Figure 4).

TABP p instruction

Specifying address

PC

H

p6p5p4p3p2p1p

Immediate field

value p

DR2DR1DR

0

The contents of

register D

PC

L

0

A3A2A1A

The contents of

register A

Register B Register A

B3B2B1B

Register E

E7E6E5E4E3E2E1E

B3B2B1B

Register B Register A

TAB instruction

0

TEAB instruction

TABE instruction

0

TBA instruction

A3A2A1A

A3A2A1A

Fig. 3 Registers A, B and register E

ROM

840

Low-order 4 bits

0

Middle-order 4 bits

High-order 2 bits

Register W5 (2)

0

0

0

Register A (4)

Register B (4)

Register B (4)

Fig. 4 TABP p instruction execution example

8

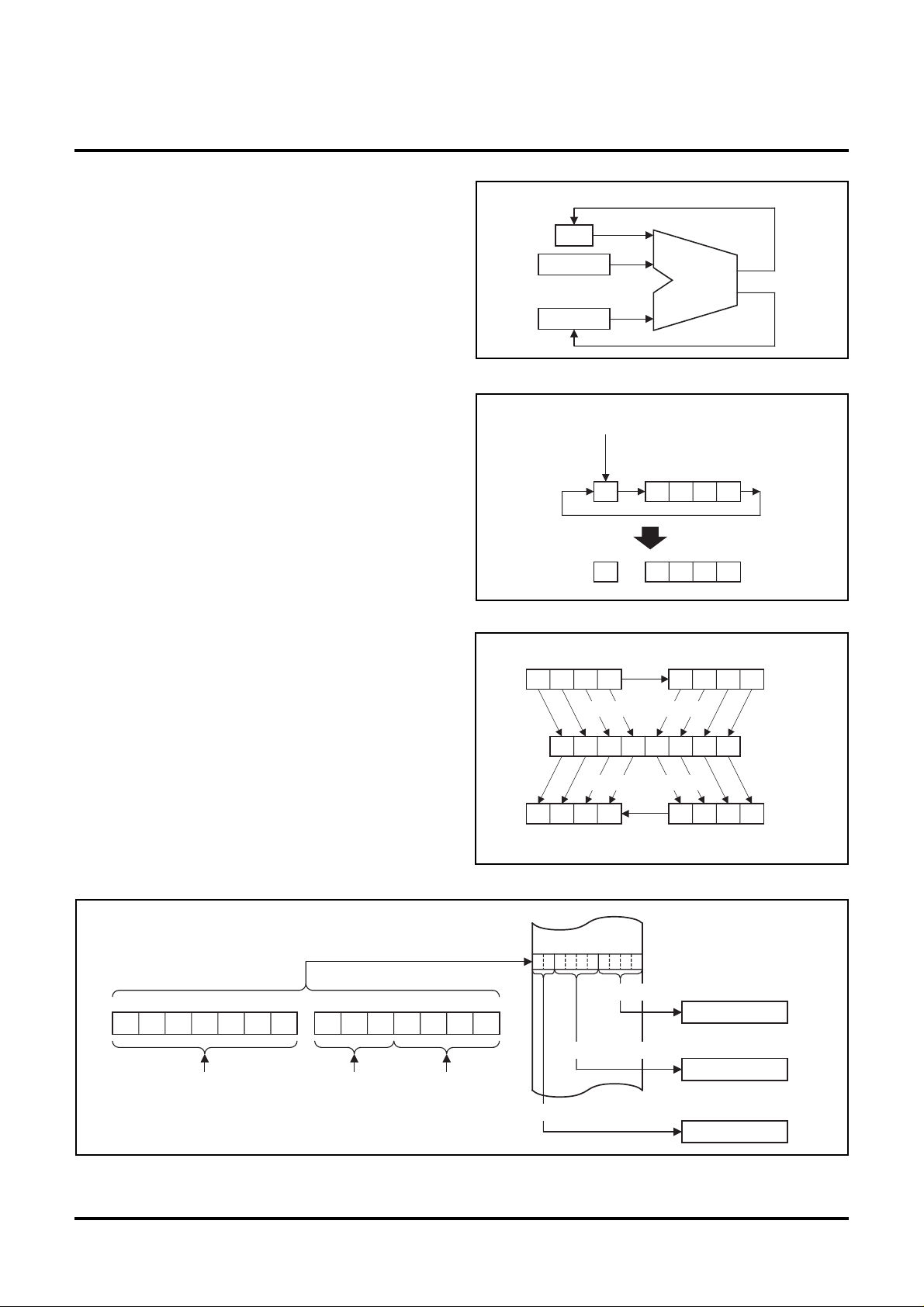

Page 9

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

(5) Stack registers (SK

S) and stack pointer (SP)

Stack registers (SKs) are used to temporarily store the

contents of program counter (PC) just before branching until

returning to the original routine when;

• branching to an interrupt service routine (referred to as

an interrupt service routine),

• performing a subroutine call, or

• executing the table reference instruction (TABP p).

Stack registers (SKs) are eight identical registers, so that

subroutines can be nested up to 8 levels. However, one of

stack registers is used when using an interrupt service routine

or when executing a table reference instruction. Accordingly,

be careful not to stack over when performing these operations

together. The contents of registers SKs are destroyed when

8 levels are exceeded.

The register SK nesting level is pointed automatically by 3bit stack pointer (SP). The contents of the stack pointer (SP)

can be transferred to register A with the TASP instruction.

Figure 5 shows the stack registers (SKs) structure.

Figure 6 shows the example of operation at subroutine call.

(6) Interrupt stack register (SDP)

Interrupt stack register (SDP) is a 1-stage register. When an

interrupt occurs, this register (SDP) is used to temporarily

store the contents of data pointer, carry flag, skip flag, register

A, and register B just before an interrupt until returning to the

original routine.

Unlike the stack registers (SKs), this register (SDP) is not

used when executing the subroutine call instruction and the

table reference instruction.

(7) Skip flag

Skip flag controls skip decision for the conditional skip

instructions and continuous described skip instructions. When

an interrupt occurs, the contents of skip flag is stored

automatically in the interrupt stack register (SDP) and the

skip condition is retained.

Program counter (PC)

Executing the subroutine

call or table reference

instruction

Executing the return or

table reference instruction

SK0

SK1

SK2

SK3

SK4

SK5

SK6

SK7

Stack pointer (SP) points “7” at reset or

returning from RAM back-up mode. It points “0”

by executing the first BM instruction, and the

contents of program counter is stored in SK

When the BM instruction is executed after eight

stack registers are used ((SP) = 7), (SP) = 0

and the contents of SK

0 is destroyed.

Fig. 5 Stack registers (SKs) structure

➝

(SP) 0

➝

(SK

0

) 0001

➝

(PC) SUB1

Main program

Address

16

NOP

0000

0001

16

BM SUB1

000216 NOP

16

Subroutine

SUB1 :

(SP) = 0

(SP) = 1

(SP) = 2

(SP) = 3

(SP) = 4

(SP) = 5

(SP) = 6

(SP) = 7

NOP

·

·

·

RT

0.

➝

(PC) (SK0)

➝

(SP) 7

Note:

Returning to the BM instruction execution

address with the RT instruction, and the BM

instruction is equivalent to the NOP instruction.

Fig. 6 Example of operation at subroutine call

9

Page 10

(8) Program counter (PC)

Program counter (PC) is used to specify a ROM address (page

and address). It determines a sequence in which instructions

stored in ROM are read. It is a binary counter that increments

the number of instruction bytes each time an instruction is

executed. However, the value changes to a specified address

when branch instructions, subroutine call instructions, return

instructions, or the table reference instruction (TABP p) is

executed.

Program counter consists of PC

7) which specifies to a ROM page and PC

H (most significant bit to bit

L (bits 6 to 0) which

specifies an address within a page. After it reaches the last

address (address 127) of a page, it specifies address 0 of the

next page (Figure 7).

Make sure that the PC

H does not specify after the last page

of the built-in ROM.

(9) Data pointer (DP)

Data pointer (DP) is used to specify a RAM address and

consists of registers Z, X, and Y. Register Z specifies a RAM

file group, register X specifies a file, and register Y specifies

a RAM digit (Figure 8).

Register Y is also used to specify the port D bit position.

When using port D, set the port D bit position to register Y

certainly and execute the SD or RD instruction (Figure 9).

MITSUBISHI MICROCOMPUTERS

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Program counter (PC)

p5p4p3p2p1p0a6a5a4a3a2a1a

p

6

PC

H

Specifying page

Fig. 7 Program counter (PC) structure

Data pointer (DP)

Z1Z0X3X2X1X0Y3Y2Y1Y

Register X (4)

Register Z (2)

Specifying address

Register Y (4)

Specifying RAM file

Specifying RAM file group

4570 Group

0

PC

L

0

Specifying

RAM digit

Fig. 8 Data pointer (DP) structure

Specifying bit position

D

9

D

6

0101 1

Register Y (4)

Port D output latch

Fig. 9 SD instruction execution example

Set

D

5

D

0

D

4

10

Page 11

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

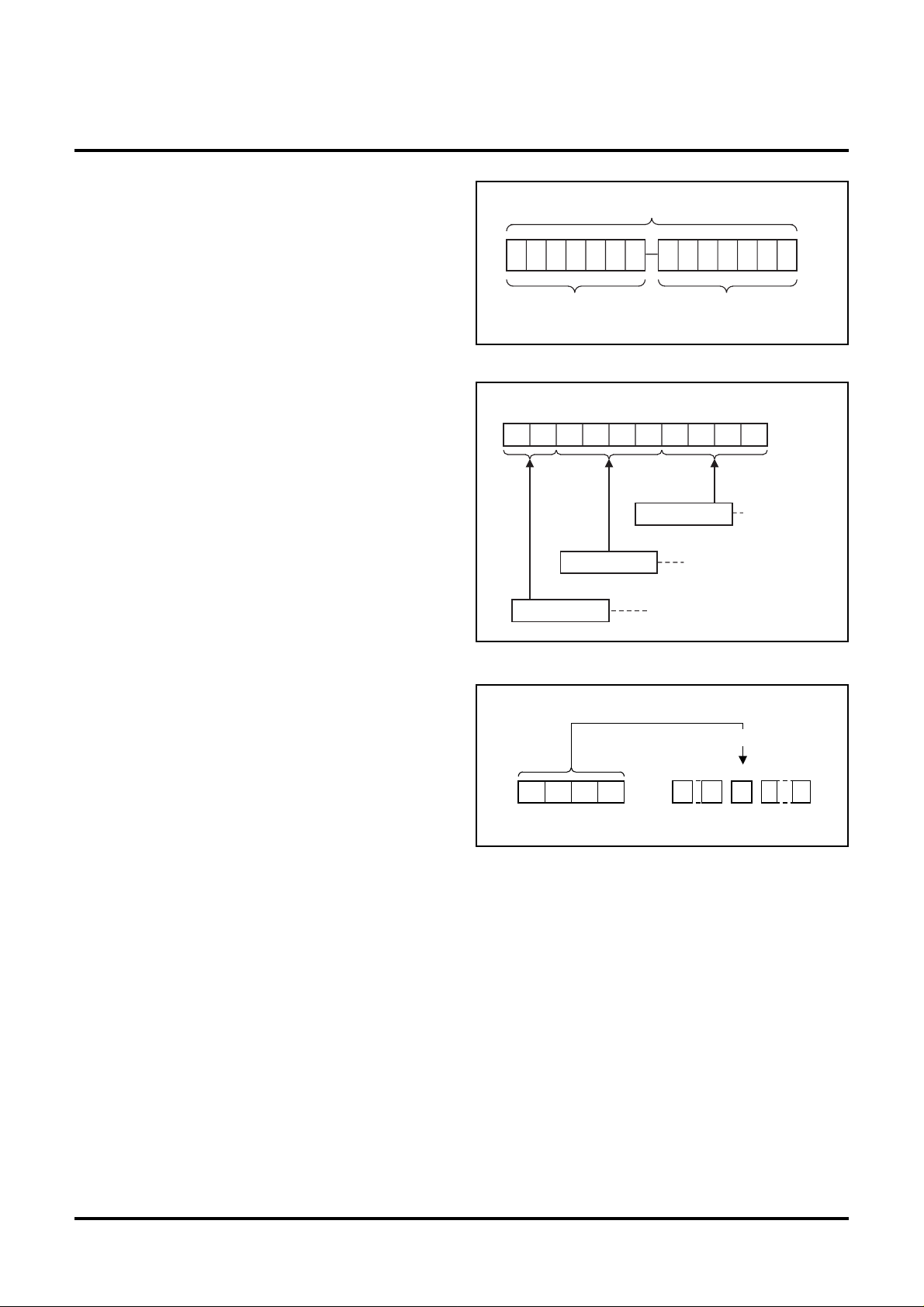

PROGRAM MEMORY (ROM)

1 word of ROM is composed of 10 bits. ROM is separated every

128 words by the unit of page (addresses 0 to 127). Table 1

shows the ROM size and pages. Figure 10 shows the ROM map

of M34570M8.

Table 1 ROM size and pages

Product

M34570M4

M34570M8

M34570E8

M34570MD

M34570ED

Note: When the TABP instruction is executed after executing

the SBK instruction, data in pages 64 to 127 can be

referred. When the TABP instruction is executed after

executing the RBK instruction, data in pages 0 to 63 can

be referred.

A top part of page 1 (addresses 0080

for interrupt addresses (Figure 11). When an interrupt occurs,

the address (interrupt address) corresponding to each interrupt

is set in the program counter, and the instruction at the interrupt

address is executed. When using an interrupt service routine,

write the instruction generating the branch to that routine at an

interrupt address.

Page 2 (addresses 0100

subroutine calls. Subroutines written in this page can be called

from any page with the 1-word instruction (BM). Subroutines

extending from page 2 to another page can also be called with

the BM instruction when it starts on page 2.

ROM pattern (bits 9 to 0) of all addresses can be used as data

areas with the TABP p instruction.

ROM size

(✕ 10 bits)

4096 words

8192 words

8192 words

16384 words

16384 words

16 to 00FF16) is reserved

16 to 017F16) is the special page for

Pages

32 (0 to 31)

64 (0 to 63)

64 (0 to 63)

128 (0 to 127)

128 (0 to 127)

9087654321

16

0000

F

16

007

0080

16

00

FF

0100

017

0180

0

FFF

1

FFF

F

Interrupt address page

16

16

Subroutine special page

16

16

16

16

Fig. 10 ROM map of M34570Mx

9087654321

0080

0084

0086

0088

External 0 interrupt address

16

Timer 1 interrupt address

16

Timer 2 interrupt address

16

Timer 3 interrupt address

16

Page 0

Page 1

Page 2

Page 3

Page 31

Page 127

Fig. 11

00FF

16

Interrupt address page (addresses 008016 to 00FF16) structure

11

Page 12

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

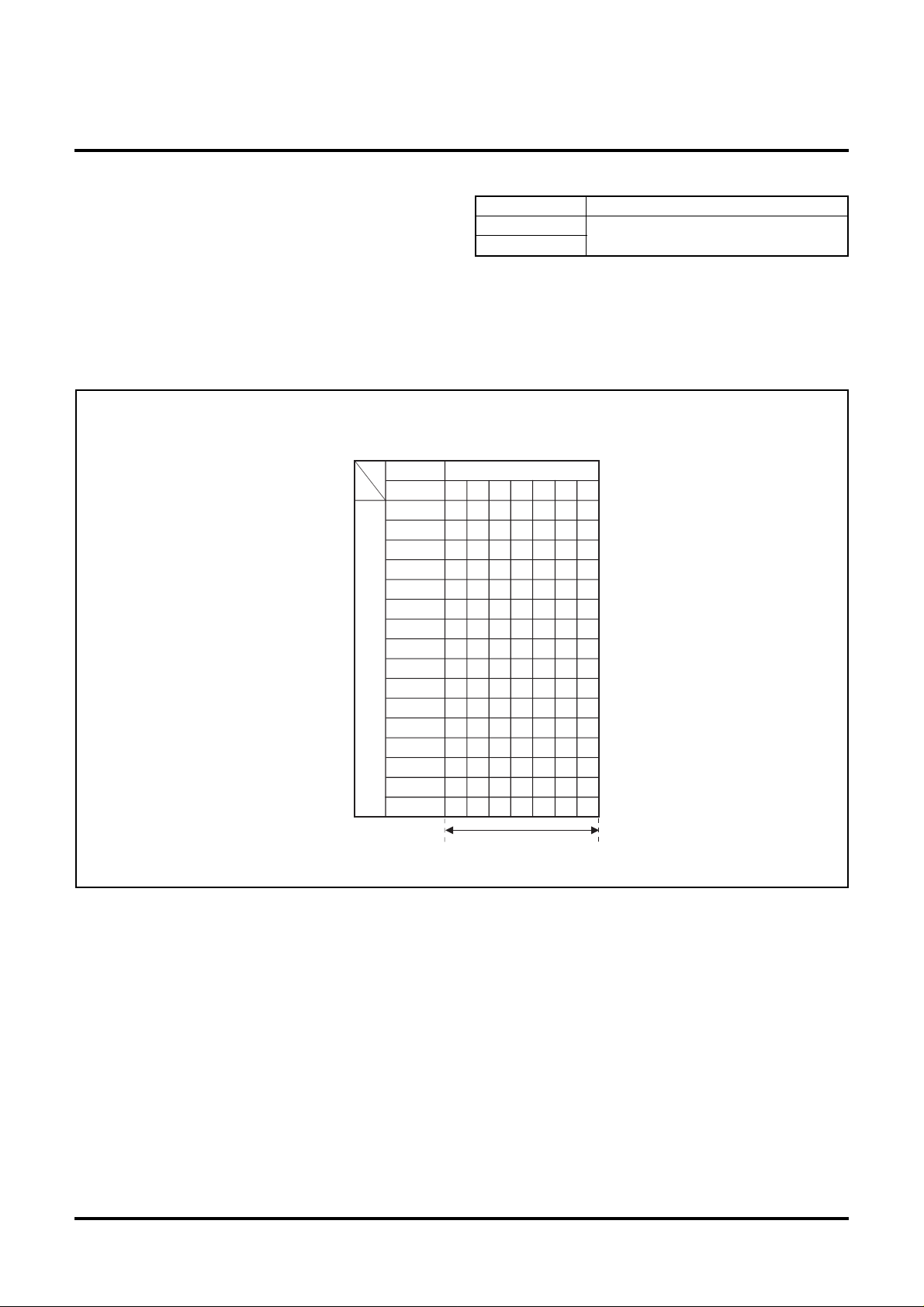

DATA MEMORY (RAM)

1 word of RAM is composed of 4 bits, but 1-bit manipulation

(with the SB j, RB j, and SZB j instructions) is enabled for the

entire memory area. A RAM address is specified by a data

pointer. The data pointer consists of registers Z, X, and Y. Set a

value to the data pointer certainly when executing an instruction

to access RAM.

Table 2 shows the RAM size. Figure 12 shows the RAM map.

RAM 128 words ✕ 4 bits (512 bits)

Register Z

Register X

0

1

2

3

4

5

6

7

Register Y

8

9

10

11

12

13

14

15

Table 2 RAM size

Product

M34570Mx

M34570Ex

0

23 6

0

1

RAM size

128 words ✕ 4 bits (512 bits)

...

7

128 words

Fig. 12 RAM map

12

Page 13

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

INTERRUPT FUNCTION

The interrupt type is a vectored interrupt branching to an individual

address (interrupt address) according to each interrupt source.

An interrupt occurs when the following 3 conditions are satisfied.

• Interrupt enable flag (INTE) = “1” (Interrupt enabled)

• Interrupt enable bit = “1” (Interrupt request occurrence enabled)

• An interrupt activated condition is satisfied

(request flag = “1”)

Table 3 shows interrupt sources. (Refer to each interrupt request

flag for details of activated conditions.)

(1) Interrupt enable flag (INTE)

The interrupt enable flag (INTE) controls whether the every

interrupt enable/disable. Interrupts are enabled when INTE

flag is set to “1” with the EI instruction and disabled when

INTE flag is cleared to “0” with the DI instruction. When any

interrupt occurs, the INTE flag is automatically cleared to “0,”

so that other interrupts are disabled until the EI instruction is

executed.

(2) Interrupt enable bits (V1

Use an interrupt enable bit of interrupt control registers V1

and V2 to select the corresponding interrupt request or skip

instruction.

Table 4 shows the interrupt request flag, interrupt enable bit

and skip instruction.

Table 5 shows the interrupt enable bit function.

(3) Interrupt request flag

When the activated condition for each interrupt is satisfied,

the corresponding interrupt request flag is set to “1.” Each

interrupt request flag is cleared to “0” when either;

• an interrupt occurs, or

• the next instruction is skipped with a skip instruction.

Each interrupt request flag is set when the activated condition

is satisfied even if the interrupt is disabled by the INTE flag or

its interrupt enable bit. Once set, the interrupt request flag

retains set until a clear condition is satisfied.

Accordingly, an interrupt occurs when the interrupt disable

state is released while the interrupt request flag is set.

If more than one interrupt request flag is set when the interrupt

disable state is released, the interrupt priority level is as follows

shown in Table 3.

0–V13, V20–V23)

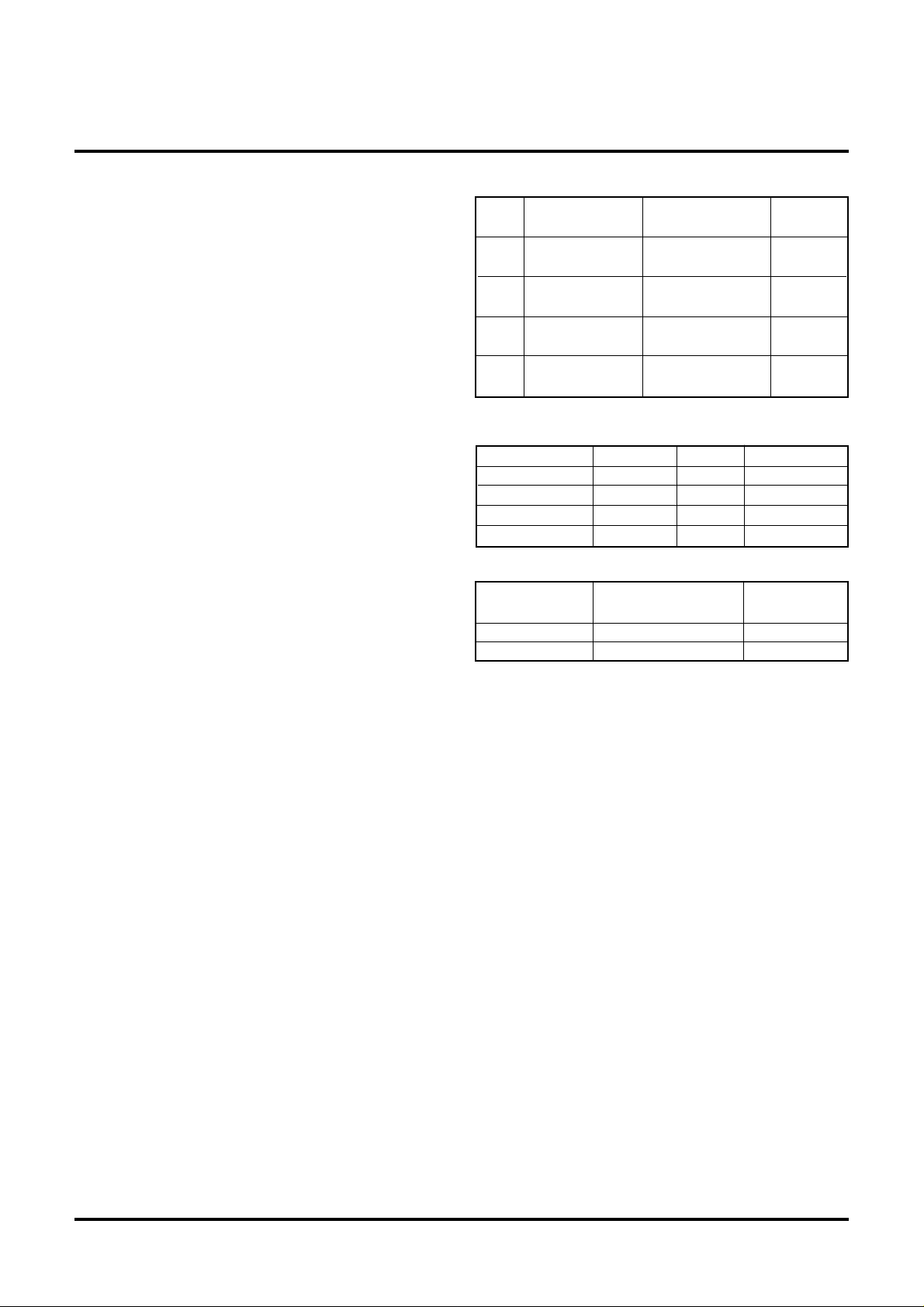

Table 3 Interrupt sources

Priority

level

Table 4 Interrupt request flag, interrupt enable bit and skip

Interrupt name

External 0 interrupt

Timer 1 interrupt

Timer 2 interrupt

Timer 3 interrupt

Table 5 Interrupt enable bit function

Interrupt enable bit

Interrupt name

1

External 0 interrupt

2

Timer 1 interrupt

3

Timer 2 interrupt

4

Timer 3 interrupt

instruction

1

0

Request flag

Activated condition

Level change of

INT pin

Timer 1 underflow

Timer 2 underflow

Timer 3 underflow

Enable bit

EXF0

T1F

T2F

T3F

Occurrence of

interrupt request

Enabled

Disabled

V1

V12

V13

V20

0

Interrupt

address

Address 0

in page 1

Address 4

in page 1

Address 6

in page 1

Address 8

in page 1

Skip instruction

SNZ0

SNZT1

SNZT2

SNZT3

Skip instruction

Invalid

Valid

13

Page 14

(4) Internal state during an interrupt

The internal state of the microcomputer during an interrupt is

as follows (Figure 14).

• Program counter (PC)

An interrupt address is set in program counter. The

address to be executed when returning to the main routine

is automatically stored in the stack register (SK).

• Interrupt enable flag (INTE)

INTE flag is cleared to “0” so that interrupts are disabled.

• Interrupt request flag

Only the request flag for the current interrupt source is

cleared to “0.”

• Data pointer, carry flag, skip flag, registers A and B

The contents of these registers and flags are stored

automatically in the interrupt stack register (SDP).

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

•Program counter (PC)

..................................................... Each interrupt address

•Stack register (SK)

The address of main routine to be executed when returning

...........

•Interrupt enable flag (INTE)

........................................................ 0 (Interrupt disabled)

•

Interrupt request flag (only the flag for the current interrupt source)

........................................................................................ 0

•Data pointer, carry flag, registers A and B, skip flag

...............

Stored in the interrupt stack register (SDP) automatically

(5) Interrupt processing

When an interrupt occurs, a program at an interrupt address

is executed after a branch to a sequence for storing data into

stack register is performed. Write the branch instruction to

an interrupt service routine at an interrupt address.

Use the RTI instruction to return to main routine.

Interrupt enabled by executing the EI instruction is performed

after executing 1 instruction (just after the next instruction is

executed). Accordingly, when the EI instruction is executed

just before the RTI instruction, interrupts are enabled after

returning to the main routine. (Refer to Figure 13)

Main

routine

Interrupt

service routine

Interrupt

occurs

EI

Interrupt

is enabled

RTI

Fig. 14 Internal state when interrupt occurs

INT pin

(L → H or

H → L input)

EXF0

V1

0

Timer 1

underflow

Timer 2

underflow

Timer 3

underflow

Activated

condition

T1F

T2F V1

T3F V2

Request

flag

(state retained)

V1

2

3

0

Enable

bit

INTE

Enable

flag

Fig. 15 Interrupt system diagram

Address 0 in

page 1

Address 4 in

page 1

Address 6 in

page 1

Address 8 in

page 1

: Interrupt enabled state

: Interrupt disabled state

Fig. 13 Program example of interrupt processing

14

Page 15

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

(6) Interrupt control register

●Interrupt control register V1

Interrupt enable bits of external 0, timer 1 and timer 2 are

assigned to register V1. Set the contents of this register

through register A with the TV1A instruction. The TAV1

instruction can be used to transfer the contents of register

V1 to register A.

Table 6 Interrupt control register

Interrupt control register V1 at reset : 0000

Interrupt disabled (SNZT2 instruction is valid)

V13

V12

V11

V10

V23

V22

V21

V20

Note: “R” represents read enabled, and “W” represents write enabled.

Timer 2 interrupt enable bit

Timer 1 interrupt enable bit

Not used

External 0 interrupt enable bit

Interrupt control register V2 at reset : 0000

Not used

Not used

Not used

Timer 3 interrupt enable bit

0

Interrupt enabled (SNZT2 instruction is invalid)

1

Interrupt disabled (SNZT1 instruction is valid)

0

Interrupt enabled (SNZT1 instruction is invalid)

1

0

This bit has no function, but read/write is enabled.

1

0

Interrupt disabled (SNZ0 instruction is valid)

1

Interrupt enabled (SNZ0 instruction is invalid)

0

This bit has no function, but read/write is enabled.

1

0

This bit has no function, but read/write is enabled.

1

0

This bit has no function, but read/write is enabled.

1

0

Interrupt disabled (SNZT3 instruction is valid)

1

Interrupt enabled (SNZT3 instruction is invalid)

●Interrupt control register V2

Interrupt enable bit of timer 3 is assigned to register V2.

Set the contents of this register through register A with the

TV2A instruction. The TAV2 instruction can be used to

transfer the contents of register V2 to register A.

2 RAM back-up : 00002 R/W

2 at RAM back-up : 00002 R/W

15

Page 16

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

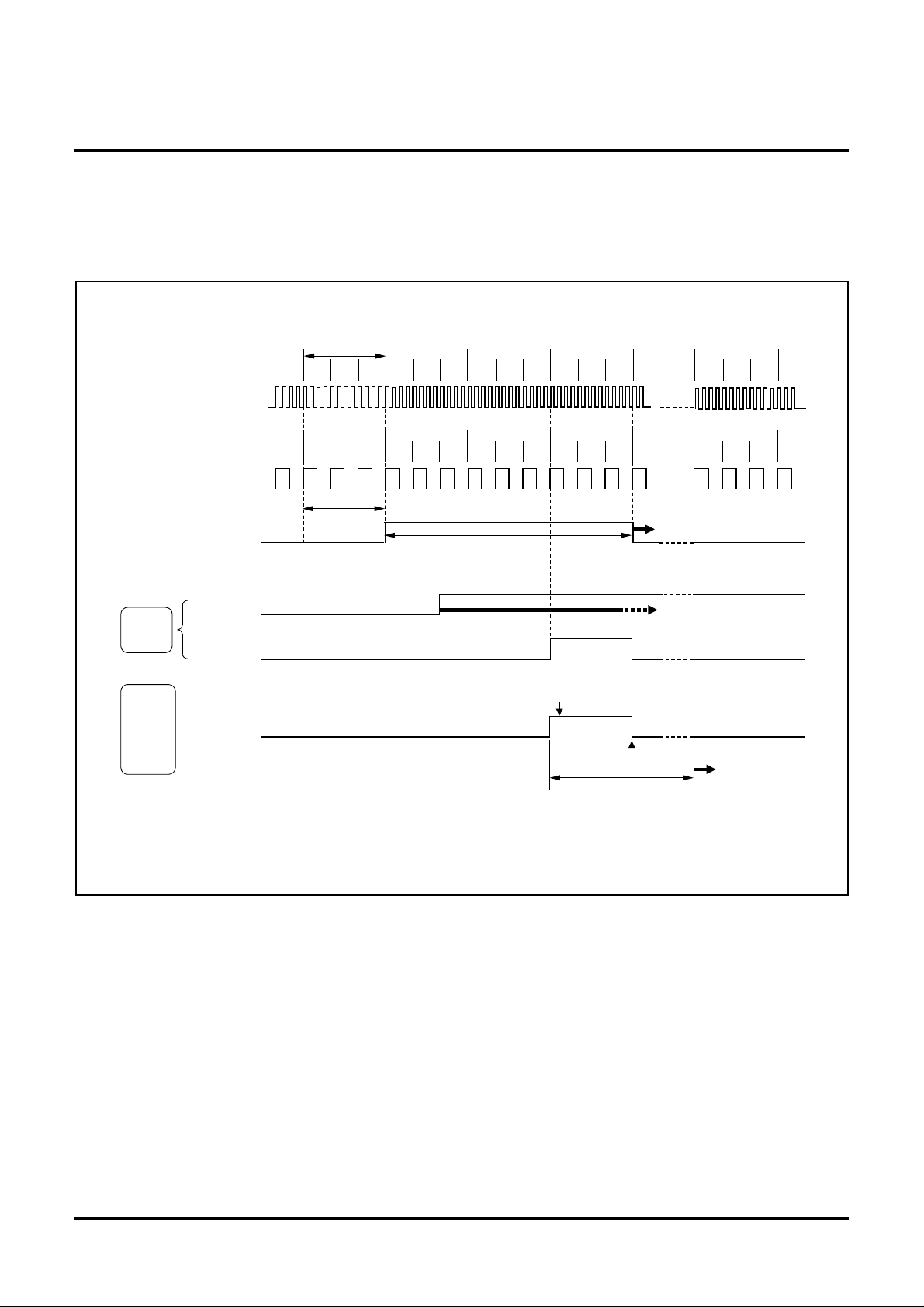

(7) Interrupt sequence

Interrupts occur only when the respective INTE flag, interrupt

enable bits (V1

0–V13 and V20–V23), and interrupt request

flags (EXF0, T1F, T2F, T3F) are “1.” The interrupt actually

occurs 2 to 3 machine cycles after the cycle in which all three

● When an interrupt request flag is set after its interrupt is enabled (Note 1)

1 machine cycle

T2 T3

f(XIN)

System clock=f(X

f(XIN)

System clock=f(X

Interrupt enable

flag (INTE)

External

interrupt

Timer 1,

timer 2,

timer 3

interrupts

IN)/4 selected

IN) selected

INT pin

Flag

EXF0

Flag

T1F, T2F

T3F

T1

T2 T3

T1

EI instruction

execution cycle

T1

T1

T2 T3

T2 T3

T1

T1

Interrupt enabled state

conditions are satisfied. The interrupt occurs after 3 machine

cycles only when the three interrupt conditions are satisfied

on execution of instructions other than one-cycle instructions

(Refer to Figure 16).

T2 T3

T2 T3

Interrupt activated

condition satisfied

T2 T3

T1

T2 T3

T1

Flag cleared

2 to 3 machine cycles

(Notes 2, 3)

T2 T3

T1

T2 T3

T1

Interrupt disabled state

Retaining level for 4 cycles or

more of f(X

IN) is necessary.

Software starts

from interrupt address.

Notes 1: The system clock = f(XIN)/4 is selected just after system is released from reset.

2: The address is stacked to the last cycle.

3: This interval of cycles depends on the instruction executed at the time when each

interrupt activated condition is satisfied.

Fig. 16 Interrupt sequence

16

Page 17

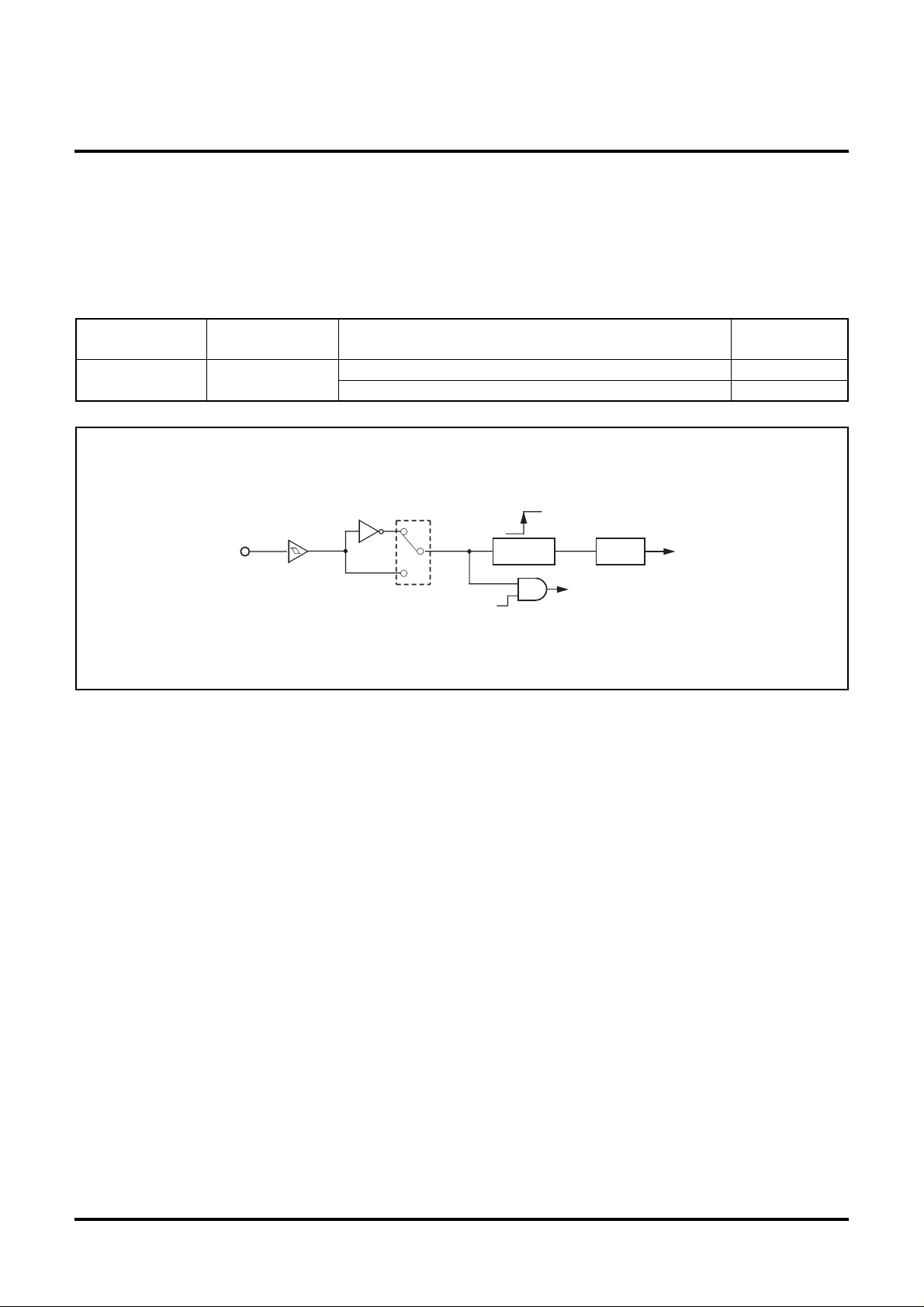

EXTERNAL INTERRUPTS

An external interrupt request occurs when a valid waveform (=

waveform causing the external 0 interrupt) is input to an interrupt

input pin (edge detection).

The external 0 interrupt can be controlled with the interrupt control

register I1.

Table 7 External interrupt activated condition

Name

External 0 interrupt

P2

1/INT

Input pin

Falling waveform (“H”→“L”)

Rising waveform (“L”→“H”)

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Valid waveform

MITSUBISHI MICROCOMPUTERS

4570 Group

Valid waveform

selection bit (I1

2)

0

1

P21/INT

Fig. 17 External interrupt circuit structure

I1

Falling

0

1

Rising

2

SNZI0

instruction

One-sided edge

detection circuit

Skip

EXF0

External 0

interrupt

17

Page 18

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

(1) External 0 interrupt request flag (EXF0)

External 0 interrupt request flag (EXF0) is set to “1” when a

valid waveform is input to P2

1/INT pin.

The valid waveforms causing the interrupt must be retained

at their level for 4 cycles or more of the system clock (Refer

to Figure 16).

The state of EXF0 flag can be examined with the skip

instruction (SNZ0). Use the interrupt control register V1 to

select the interrupt or the skip instruction. The EXF0 flag is

cleared to “0” when an interrupt occurs or when the next

instruction is skipped with the skip instruction.

The P2

1/INT pin need not be selected the external interrupt

input INT function or the normal input port P2

1 function.

However, the EXF0 flag is set to “1” when a valid waveform

is input to P2

1/INT pin even if it is used as an input port P21.

●External 0 interrupt activated condition

External 0 interrupt activated condition is satisfied when a

valid waveform is input to P2

1/INT pin.

The valid waveform can be selected from rising waveform or

falling waveform. An example of how to use the external 0

interrupt is as follows.

➀ Select the valid waveform with the bit 2 of register I1.

➁ Clear the EXF0 flag to “0” with the SNZ0 instruction.

➂ Set the NOP instruction for the case when a skip is performed

with the SNZ0 instruction.

➃ Set both the external 0 interrupt enable bit (V1

0) and the

INTE flag to “1.”

(2) External interrupt control register

●Interrupt control register I1

Register I1 controls the valid waveform for the external 0

interrupt, the return level (valid level of wakeup signal) from

the RAM back-up and P2

1/INT pin function. Set the contents

of this register through register A with the TI1A instruction.

The TAI1 instruction can be used to transfer the contents of

register I1 to register A.

The external 0 interrupt is now enabled. Now when a valid

waveform is input to the P2

1/INT pin, the EXF0 flag is set to

“1” and the external 0 interrupt occurs.

Table 8 External interrupt control register

Interrupt control register I1

Not used

I13

Interrupt valid waveform for INT pin/return

I12

level selection bit (Note 2)

0

This bit has no function, but read/write is enabled.

1

Falling waveform (“L” level of INT pin is recognized with the SNZI0

0

instruction)/“L” level

Rising waveform (“H” level of INT pin is recognized with the SNZI0

1

instruction)/“H” level

0

I11

I10

Not used

Not used

This bit has no function, but read/write is enabled.

1

0

This bit has no function, but read/write is enabled.

1

Notes 1: “R” represents read enabled, and “W” represents write enabled.

2: Depending on the input state of P2

of I1

2 is changed. Accordingly, set a value to bit 2 of register I1 and execute the SNZ0 instruction to clear the EXF0 flag after

1/INT pin, the external interrupt request flag EXF0 may be set to “1” when the contents

executing at least one instruction.

at RAM back-up : state retained

R/Wat reset : 00002

18

Page 19

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

TIMERS

The 4570 Group has the programmable timers and a fixed

dividing frequency timer.

●Programmable timer

The programmable timer has a reload register and enables

the frequency dividing ratio to be set. It is decremented from a

set value n. When it underflows (count to n + 1), a timer interrupt

request flag is set to “1,” new data is loaded from the reload

register, and count continues (auto-reload function).

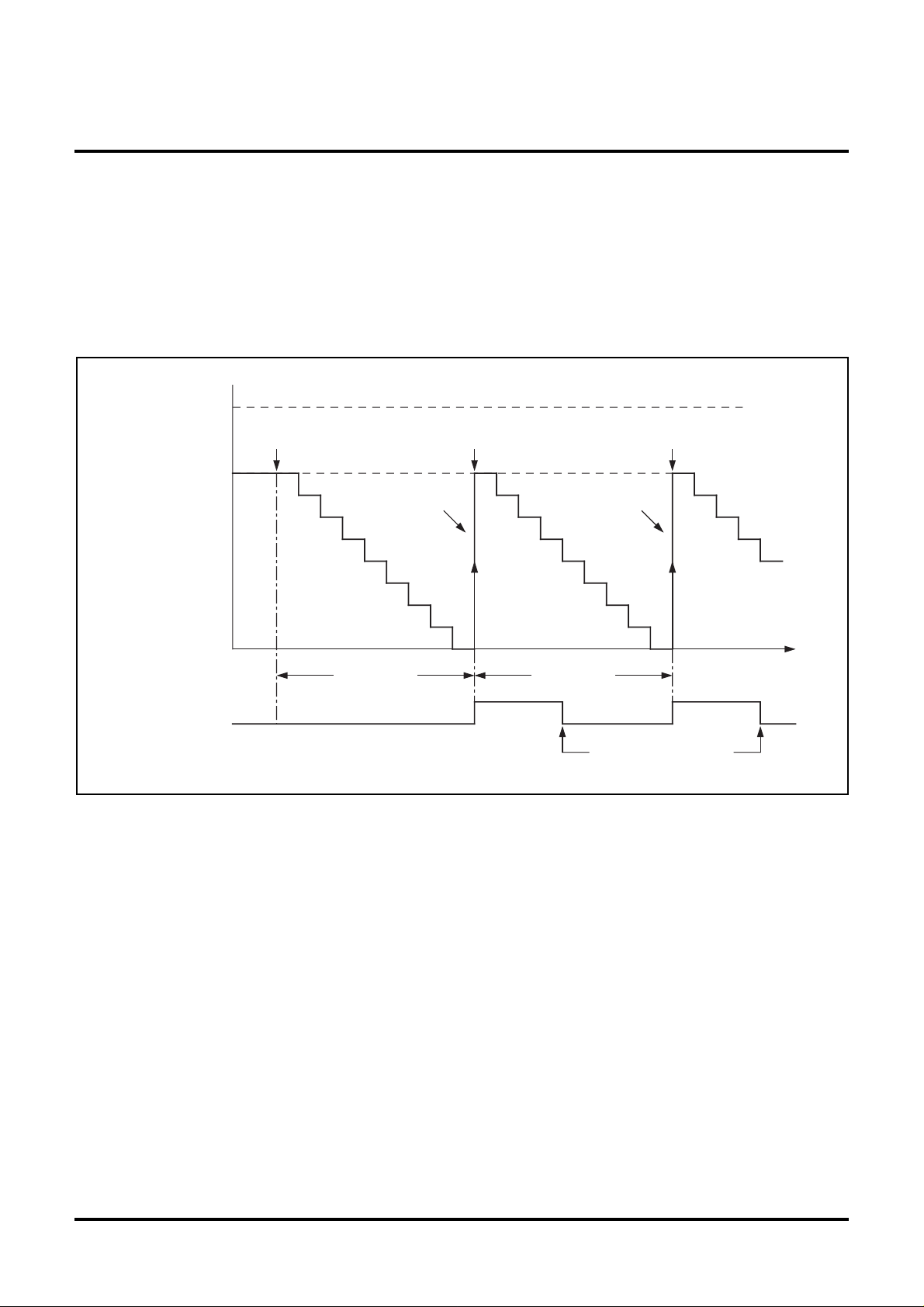

FF16

n : Counter initial value

Count starts

n

1st underflow 2nd underflow

The contents of counter

●Fixed dividing frequency timer

The fixed dividing frequency timer has the fixed frequency

dividing ratio (n). An interrupt request flag is set to “1” every n

count of a count pulse.

Reload Reload

16

00

Timer 1 interrupt

request flag

“1”

“0”

Fig. 18 Auto-reload function

n+1 count n+1 count

Time

An interrupt occurs or

a skip instruction is executed.

19

Page 20

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

The 4570 Group timer consists of the following circuits.

• Prescaler : frequency divider

• Timer 1 : 10-bit programmable timer with the interrupt function

and the carrier wave output auto-control function

• Timer 2 : 8-bit programmable timer with the interrupt function

• Timer 3 : 8-bit programmable timer with the interrupt function

and the carrier wave generation function

• 16-bit timer

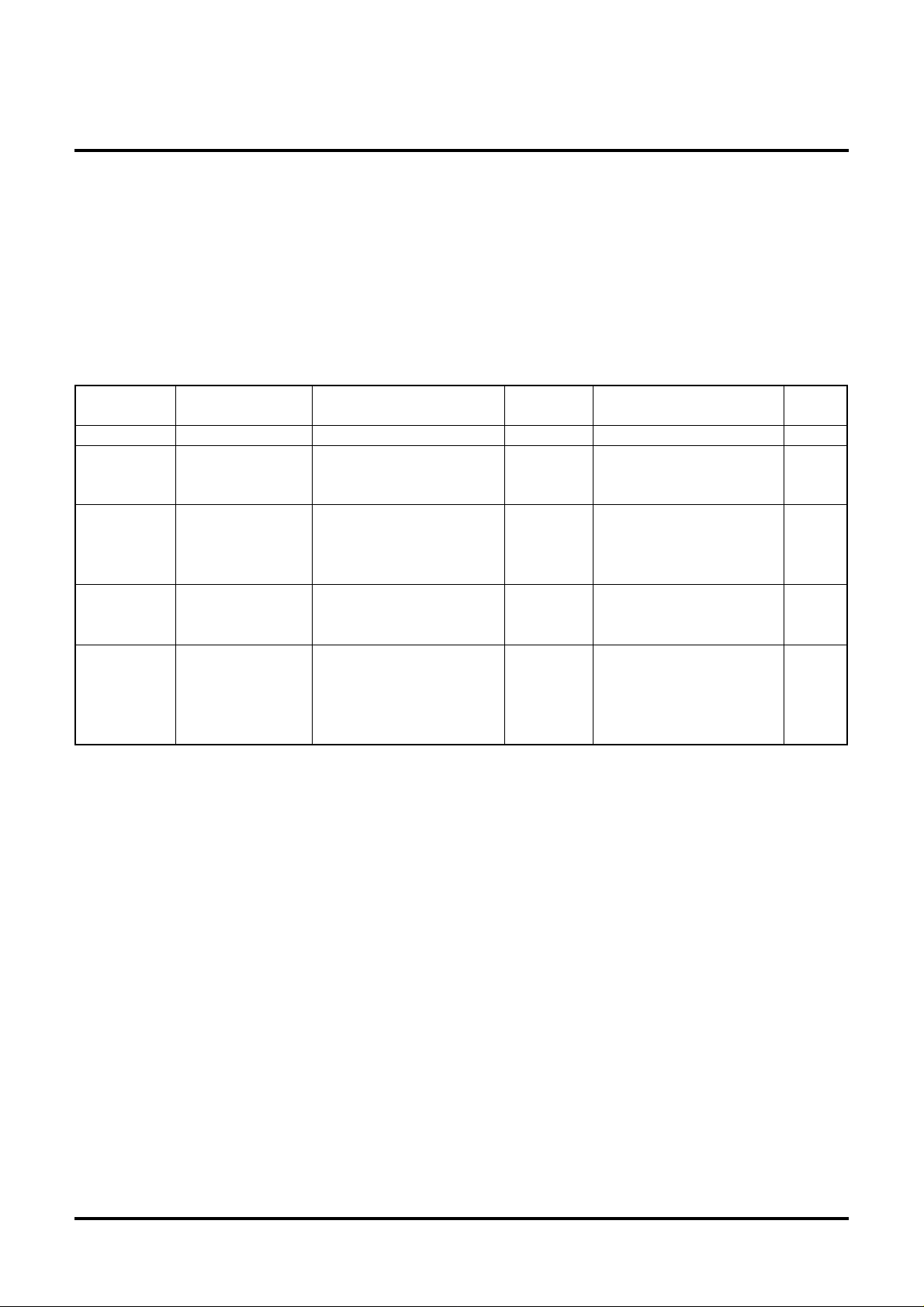

Table 9 Function related timers

Circuit

Prescaler

Timer 1

Timer 2

Timer 3

16-bit timer

Structure

Frequency divider

10-bit programmable

binary down counter

8-bit programmable

binary down counter

8-bit programmable

binary down counter

16-bit fixed

dividing frequency

• Instruction clock

• Prescaler output (ORCLK)

• Carrier wave generating circuit

output (CARRY)

• Prescaler output (ORCLK)

• Timer 1 underflow

• Instruction clock

• 16-bit timer underflow

• Prescaler output (ORCLK)

• Timer 2 underflow

• f(X

• Instruction clock

Count source

IN) or f(XIN)/2

Prescaler, timer 1, timer 2 and timer 3 can be controlled with the

timer control registers W1, W2 and W3.

16-bit timer is the free-run counter without the control register.

Each function is described below.

Frequency

dividing ratio

4, 8

1 to 1024

1 to 256

1 to 256

65536

Use of output signal

• Timer 1, 2 and 3 count sources

• Timer 1 interrupt

•

Carrier wave output auto-control

• Timer 2 count source

• Timer 2 interrupt

• Timer 3 count source

OUT output

• T

• Timer 3 interrupt

• Timer 1 count source

• Carrier wave

• Watchdog timer

(15-th bit output is counted

twice.)

• Timer 2 count source

(16-bit timer underflow)

Control

register

W1

W1

(W5)

W2

W3

20

Page 21

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

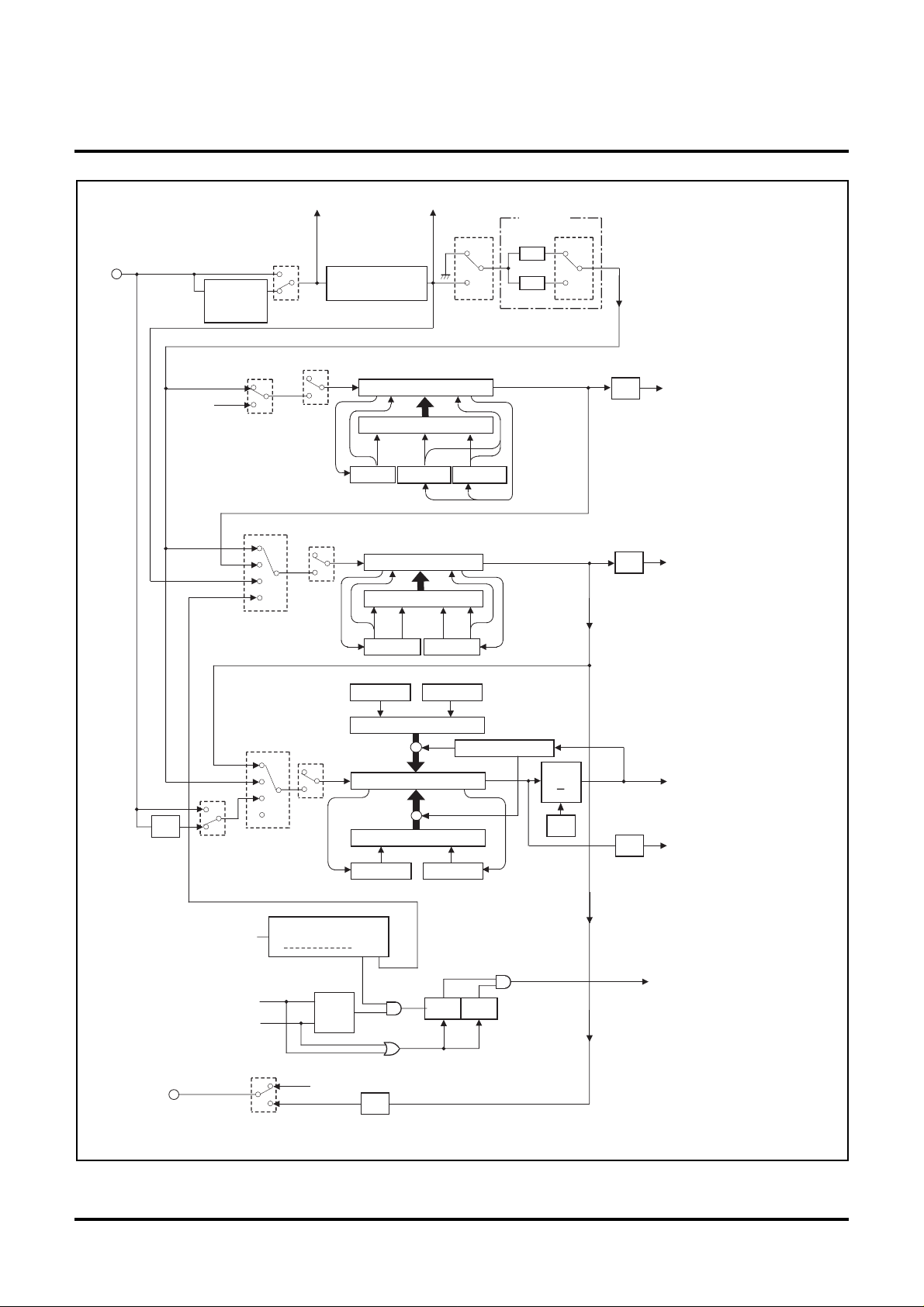

System clock

Instruction clock

Prescaler

W1

3 (Note 1)

MR

3

W1

0

Internal clock generating

circuit (divided by 3)

1

W1

1

0

1

0(Note 1)

0

1

Timer 1(10)

X

IN

Frequency

dividing circuit

(divided by 4)

CARRY

0

1

ORCLK

1/4

1/8

W1

2

0

1

T1F

Timer 1

interrupt

Reload register R1 (10)

(Note 2)

(T1AB)

Register W5

Register B

Timer 2 (8)

Reload register R2 (8)

T

(TR2AB)

2

A

B

Register B

(TAB1)

Register A

Timer 1 underflow signal

T

2

A

B

(TAB2)

Register A

T2F

Timer 2

interrupt

W21,W2

00

01

10

11

(TAB1)

0

W2

3(Note 1)

0

1

(TAB2)

D9/T

1/2

OUT

W31,W3

00

01

MR

10

3

11

0

Not available

1

16-bit timer underflow signal

Instruction clock

WRST instruction

Reset signal

W2

0

W3

3(Note1)

0

1

(TAB3)

16-bit timer (WDT)

R

2

0

1

D9 output

Register B

Reload register R3H (8)

Timer 3(8)

(T3AB)

Reload register R3L (8)

Register B

15116

S

WEF

Q

1/2

Timer 2 underflow signal

Register A

(T3HAB)

(T3AB)

Register A

WDF1 WDF2

Timer 2 underflow signal

Reload control circuit

T

(TAB3)

W3

Q

R

3

T3F

CARRY

(to timer 1/port CARR)

Timer 3

interrupt

System reset

Notes 1: Count source is stopped by setting to “0.”

2: When the T1AB instruction is executed after

setting W1

register R1.

0

to “1,” data is only written to reload

Fig. 19 Timers structure

21

Page 22

Table 10 Timer control registers

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

W13

W12

W11

W10

W2

W22

W21

W20

Timer control register W1

Prescaler control bit

Prescaler dividing ratio selection bit

Timer 1 count source selection bit

Timer 1 control bit

Timer control register W2

3

Timer 2 control bit

9/TOUT pin function selection bit

Port D

Timer 2 count source selection bits

at reset : 00002 at RAM back-up : 00002

Stop (prescaler state initialized)

0

Operating

1

Instruction clock divided by 4

0

Instruction clock divided by 8

1

Prescaler output (ORCLK)

0

Carrier output (CARRY)

1

Stop (state retained)

0

Operating

1

at reset : 0000

2 at RAM back-up : state retained R/W

01Stop (state retained)

Operating

9

Port D

0

TOUT pin

1

W21

0

0

1

1

W20

Prescaler output (ORCLK)

0

Timer 1 underflow signal

1

Instruction clock

0

16-bit timer underflow signal

1

Count source

R/W

Timer control register W3

W33

W32

Timer 3 control bit

Not used

W31

Timer 3 count source selection bits

W30

Timer count value store register W5

W31

0

0

1

1

0

1

0

1

W30

0

1

0

1

at reset : 0000

Stop (state retained)

Operating

This bit has no function, but read/write is enabled.

Timer 2 underflow signal

Prescaler output (ORCLK)

IN) or f(XIN)/2

f(X

Not available

at reset : 00

2 at RAM back-up : state retained R/W

Count source

2 at RAM back-up : state retained R/W

2-bit register. The contents of the high-order 2 bits (bits 9 and 8) of the 10-bit ROM pattern at address (D2D1D0A3A2A1A0) in page

p specified by registers D and A is stored in this register W5 with the TABP p instruction.

In addition, data can be transferred between the low-order 2 bits of register A and this register W5 with the TW5A or TAW5

instruction. Data can be read/written to/from the high-order 2 bits of timer 1 with the T1AB or TAB1 instruction.

Note: “R” represents read enabled, and “W” represents write enabled.

22

Page 23

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

(1) Timer control registers

●Timer control register W1

Register W1 controls the count source and count operation

of timer 1, the frequency dividing ratio and count operation

of prescaler. Set the contents of this register through

register A with the TW1A instruction. The TAW1 instruction

can be used to transfer the contents of register W1 to

register A.

●Timer control register W2

Register W2 controls the count operation and count source

of timer 2 and D

this register through register A with the TW2A instruction.

The TAW2 instruction can be used to transfer the contents

of register W2 to register A.

●Timer control register W3

Register W3 controls the count operation and count source

of timer 3. Set the contents of this register through register

A with the TW3A instruction. The TAW3 instruction can

be used to transfer the contents of register W3 to register

A.

●Timer count value store register W5

2-bit register. The contents of the high-order 2 bits (bits 9

and 8) of the 10-bit ROM pattern at address in page p

specified by registers D and A is stored in this register

W5 with the TABP p instruction.

In addition, data can be transferred between the low-order

2 bits of register A and this register W5 with the TW5A or

TAW5 instruction. Data can be read/written to/from the

high-order 2 bits of timer 1 with the T1AB or TAB1

instruction.

(2) Precautions

Note the following for the use of timers.

●Prescaler

Stop the prescaler operation to change its frequency

dividing ratio.

●Count source

Stop timer 1, 2 or 3 counting to change its count source.

●Reading the timer count value

Stop each of the timers and then execute the TAB1, TAB2

or TAB3 instruction to read timer 1, 2 or 3 data.

●Writing to reload register R1

When writing data to reload register R1 while timer 1 is

operating, avoid a timing when timer 1 underflows.

●Writing to reload register R3H

When writing data to reload register R3H while timer 3 is

operating, avoid a timing when timer 3 underflows.

(3) Prescaler

Prescaler is a frequency divider. Its frequency dividing ratio

can be selected. The count source of prescaler is the

instruction clock.

Use the bit 2 of register W1 to select the prescaler dividing

ratio and the bit 3 to start and stop its operation. When the bit

3 of register W1 is cleared to “0,” prescaler is initialized, and

the output signal (ORCLK) stops.

9/TOUT pin function. Set the contents of

(4) Timer 1 (interrupt function)

Timer 1 is a 10-bit binary down counter with the timer 1 reload

register (R1). The 10-bit data can be set in timer 1 through

registers A, B and W5. Set bits 0 to 3 to register A, bits 4 to

7 to regiser B and bits 8 to 9 to register W5 to set data to

timer 1. Also, ROM pattern (bits 0 to 9) can be set to registers

A, B and W5 with the TABP p instruction. Execute the T1AB

instruction to set data in timer 1.

When timer 1 stops, 10-bit data can be set simultaneously in

timer 1 and the reload register (R1) with the T1AB instruction.

When timer 1 is operating, data can be set only in the reload

register (R1) with the T1AB instruction.

When setting the next count data to reload register R1 while

timer 1 is operating, be sure to set data before timer 1

underflows.

Timer 1 starts counting after the following process;

➀ set data in timer 1,

➁ select the count source with bit 1 of register W1,

➂ set the bit 0 of register W1 to “1.”

Once count is started, when timer 1 underflows (the next

count pulse is input after the contents of timer 1 becomes

“0”), the timer 1 interrupt request flag (T1F) is set to “1,” new

data is loaded from reload register R1, and count continues

(auto-reload function).

When a value set in reload register R1 is n, timer 1 divides

the count source signal by n + 1 (n = 0 to 1023).

Data can be read from timer 1 to registers A, B and W5.

Stop counting and then execute the TAB1 instruction to read

its data.

(5) Timer 2 (interrupt function)

Timer 2 is an 8-bit binary counter with the timer 2 reload

register (R2). Data can be set simultaneously in timer 2 and

the reload register (R2) with the TAB2 instrucion. Also, data

can be set only in the reload register (R2) with the TR2AB

instruction.

Timer 2 starts counting after following process;

➀ set data in timer 2,

➁ select the count source with bits 0 and 1 of register W2,

➂ set the bit 3 of register W2 to “1.”

Once count is started, when timer 2 underflows (the next

count pulse is input after the contents of timer 2 becomes

“0”), the timer 2 interrupt request flag (T2F) is set to “1,” new

data is loaded from reload register R2, and count continues

(auto-reload function).

When a value set in reload register R2 is n, timer 2 divides

the count source signal by n+1 (n = 0 to 255).

Data can be read from timer 2 to registers A and B with the

TAB2 instruction. Stop counting and then execute the TAB2

instruction to read its data.

23

Page 24

(6) Timer 3

Timer 3 is an 8-bit binary down counter with the timer 3 reload

registers (R3H, R3L). Data can be set simultaneously in timer

3 and the reload register (R3L) with the T3AB instruction.

Data can be set in reload register R3H with the T3HAB

instruction.

Timer 3 starts counting after the following process;

➀ set data in timer 3,

➁ select the count source with the bits 1 and 0 of register

W3,

➂ set the bit 3 of register W3 to “1.”

The f(X

IN) or f(XIN)/2 is selected as the count source by setting

W3

1 to “1” and W30 to “0.”

When the f(X

control register MR= “0”), f(X

IN) is selected as the system clock (bit 3 of clock

IN) is selected as the count

source.

When the f(X

clock control register MR= “1”), f(X

IN)/4 is selected as the system clock (bit 3 of

IN)/2 is selected as the

count source.

Once count is started, when timer 3 underflows (the next count

pulse is input after the contents of timer 3 become “0”), the

timer 3 interrupt request flag (T3F) is set to “1,” new data is

loaded from reload register R3H, and count coutinues (autoreload function).

When the timer 3 underflows again after auto-reload is

performed, the timer 3 interrupt request flag (T3F) is set to

“1” and new data is reloaded from the reload register R3L

and count continues. Timer 3 reloads data from reload register

R3H or R3L alternately every underflow.

When the T3AB instruction is executed while timer 3 is

operating, new data is set in timer 3 and reload register R3L,

count is started again at the next machine cycle. At the next

underflow, data is reloaded from R3H and count continues

regardless that auto-reload is performed from reload register

R3H or R3L at the previous underflow.

Data can be read from timer 3 through registers A and B.

Stop counting and then execute the TAB3 instruction to read

its data. Timer 3 can be also used as the carrier wave

generating circuit.

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

(7) Timer output pin (D

Timer output pin (D

9/TOUT)

9/TOUT) is used to output the timer 2

underflow signal.

The D

9/TOUT pin function can be selected by the bit 2 of register

W2.

(8) Timer interrupt request flags (T1F, T2F, T3F)

Each timer interrupt request flag is set to “1” when each timer

underflows. The state of these flags can be examined with

the skip instructions (SNZT1, SNZT2, SNZT3).

Use the interrupt control registers V1 and V2 to select an

interrupt or a skip instruction.

An interrupt request flag is cleared to “0” when an interrupt

occurs or when the next instruction is skipped with a skip

instruction.

24

Page 25

WATCHDOG TIMER

Watchdog timer provides a method to reset the system when a

program runs wild. Watchdog timer consists of 16-bit timer (WDT),

watchdog timer enable flag (WEF), and watchdog timer flags

(WDF1, WDF2).

Timer WDT starts downcounting the instruction clocks as the

count source immediately after system is released from reset.

The underflow signal is generated when the count value reaches

“0000

16.” This underflow signal can be used as the timer 2 count

source.

When the WRST instruction is executed after system is released

from reset, the WEF flag is set to “1.” At this time, the watchdog

timer starts operating.

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

When the count value of timer WDT reaches “BFFF

“3FFF

16,” WDF1 flag is set to “1.” Then, if the WRST instruction

is not executed while the timer WDT counts 32767, the WDF2

flag is set to “1” and the RESET pin outputs “L” level to reset the

microcomputer. In software using the watchdog timer, make sure

that the WRST instruction is executed in 32766 machine cycles

or less in order to keep the microcomputer operating normally.

To prevent the watchdog timer from stopping in the event of

misoperation, the WEF flag is designed not to be initialized once

the WRST instruction has been executed. Note also that, if the

WRST instruction is never executed, the watchdog timer does

not start.

______

16” or

FFFF16

Value of timer WDT

0000 16

Flag WEF

Flag WDF1

Flag WDF2

RESET pin output

WRST instruction

execution

Fig. 20 Watchdog timer function

The contents of the WEF flag, the WDF1 and WDF2 flags and

the timer WDT are initialized at the RAM back-up mode.

However, if the WDF2 flag is set to “1” at the same time that the

microcomputer enters the RAM back-up mode, system reset may

be performed.

When using the watchdog timer and the RAM back-up mode,

initialize the WDF1 flag with the WRST instruction just before

the microcomputer enters the RAM back-up mode (refer to Figure

21).

BFFF16

3FFF16

WRST instruction

execution

•

•

•

•

•

•

WRST ; Clear WDF1 flag

EPOF ; POF instruction execution enabled

POF

System reset

Oscillation stop

Fig. 21 Program example to enter the RAM back-up mode

when using the watchdog timer

(RAM back-up mode)

25

Page 26

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

CARRIER WAVE GENERATING CIRCUIT

The 4570 Group has a carrier wave generating circuit that

generates the transfer waveform for various remote control carrier

wave.

The carrier wave generating circuit outputs the signal inverted

every timer 3 underflow (CARRY) from port CARR.

When using the carrier wave generating circuit, select the f(X

or f(X

IN)/2 for the timer 3 count source (W31=“1”, W30=“0”).

When the bit 3 of the clock control register MR is “0” (system

clock=f(X

IN)), f(XIN) is selected as the count source.

When the bit 3 of the clock control register MR is “1” (system

clock=f(X

IN)/4), f(XIN)/2 is selected as the count source.

Set the count value corresponding to “L” interval of carrier wave

output to timer 3 reload register R3L.

Set the count value corresponding to “H” interval of carrier wave

output to timer 3 reload register R3H.

Also, timer 1 can auto-control the carrier wave output of port

CARR by setting the carrier wave output control register (C2).

When timer 3 is stopped, the output level of port CARR is

initialized. (“L” level)

(1) Carrier wave output control register (C2)

Timer 1 can auto-control the output enable interval and the

output disable interval of the carrier wave output from port

CARR by setting the bit 0 of register C2 to “1.” Set the

contents of this register through register A with the TC2A

instruction.

The setting of the output enable/disable interval is described

below.

➀Validate the carrier wave output auto-control function

(C2

0=“1”).

➁Set the count value (“L” interval of carrier wave output) to

timer 3 and reload register R3L.

➂Set the count value (“H” interval of carrier wave output) to

timer 3 reload register R3H.

➃Set the count value (the output enable interval of carrier

wave from port CARR) to timer 1.

➄Select the carrier wave (W1

1 = “1”) as the timer 1 count

source.

➅Operate timer 1 (W1

➆Operate timer 3 (W3

0=“1”).

3=“1”).

➇Set the next count value (the output disable interval of

carrier wave from port CARR) to reload register R1 before

timer 1 underflow occurs.

IN)

The carrier wave is output from port CARR until the first timer

3 underflow occurs. The output of the carrier wave from port

CARR is disabled and the next count value is loaded from

reload register R1 to timer 1 by the first timer 1 underflow.

Then, the output of carrier wave is disabled until the second

timer 1 underflow occurs. Also, the next enable interval of

the carrier wave output can be set by setting the third count

value to timer 1 reload register R1 before the second timer 1

underflow occurs.

If the carrier wave output auto-control function is invalidated

(C2

0=“0”) while the carrier wave output is auto-controlled, the

output of port CARR retains the state when the auto-control

is invalidated regardless of timer 1 underflow. This state can

be terminated by timer 1 stop (W1

0=“0”).

When the carrier wave output auto-control function is validated

(C2

0=“1”) again after it is invalidated (C20=“0”), the auto-

control of carrier wave output is started again when the next

timer 1 underflow occurs.

Stop the timer 3 and invalidate the auto-control function by

timer 1 to use the port CARR output contorl bit (C2

(2)

Notes when using the carrier wave output auto-control function

1).

●Set the timer 1 and register C2 before timer 3 is started to

operate (W3

●Stop the timer 1 (W1

(W3

3=“0”) while the carrier wave output is disabled in order

3=“1”).

0=“0”) after stopping the timer 3

to stop the carrier wave output auto-control operation.

●If the carrier wave output auto-control function is invalidated

(C2

0=“0”) while the carrier wave output is auto-controlled,

the output of port CARR retains the state when the autocontrol is invalidated regardless of timer 1 underflow.

When the carrier wave output auto-control function is

validated (C2

0=“1”) again after it is invalidated (C20=“0”),

the auto-control by timer 1 is validated again when the next

timer 1 underflow occurs.

However, when the carrier wave output auto-control bit (C2

0)

is changed during timer 1 underflow, the error-operation may

occur.

●When the carrier wave output auto-control function is

selected, use the carrier wave CARRY as the timer 1 count

source.

If the ORCLK is used as the count source, a short pulse

may occur in port CARR output because ORCLK is not

synchronized with the carrier wave.

●When the carrier wave output auto-control function is

selected and data is set to reload register R1 while timer 1

is operating, avoid the timing that the contents of timer 1

becomes “0” to execute the T1AB instruction.

Table 11 Carrier wave output control register

C21

C20

Port CARR output control bit

Carrier wave output auto-control bit

Note: “W” represents write enabled.

26

at reset : 002Carrier wave output control register C2 at RAM back-up : 002 W

0

Port CARR “L” level output

1

Port CARR “H” level output

Auto-control output by timer 1 is invalid

0

Auto-control output by timer 1 is valid

1

Page 27

Machine cycle

f(XIN) (divided by 3)

“H”

“L”

TW3A

instruction

Timer 3 start

▼

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Timer 3 underflow

CARRY

Port CARR output

Timer 1 underflow

(C20) 1

Timer 3

CARRY

“H”

“L”

“H”

“L”

Timer 1 start

“1”

“0”

➝

▼

▼

Interval “a” is set

by timer 1

210

“1”

“0”

“H”

“L”

“L” interval

set by

R3L

▼

▼▼

Interval “b” is set by

reload register R1

“a”

3 210

R3H

“H” interval

set by R3H

2

R3L

“L” interval

set by

R3L

10

2

10

3

R3H

“H” interval

set by R3H

“b”

Interval “c” is set by

reload register R1

2

Timer 3 reload register R3H

10

Timer 3 reload register R3L

R3L

“c”

▼

Interval “d” is set by

reload register R1

0316

0216

“d”

Carrier wave output start

“H”

CARRY

“L”

Port CARR output

Timer 1 underflow

Register C20

“H”

“L”

“1”

“0”

“1”

“0”

Carrier wave output start

Fig. 22 Carrier wave output auto-control by timer 1

(C2

0) 0

▼

➝

(C2

0) 1

▼

▼

➝➝➝

(C2

0) 0

▼

(C20) 1

27

Page 28

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

RESET FUNCTION

System reset is performed by applying “L” level to RESET pin

for 1 machine cycle or more when the following condition is

satisfied;

____________

f(XIN)

RESET

“H”

“L”

(Note)

f(XIN) is counted

10757 to 10786 times

Note: The number of clock cycles depends on the internal state of

the microcomputer when reset is performed.

Fig. 23 Reset release timing

Reset input

0.85V

=

1machine cycle or more

DD

f(XIN) is counted

10757 to 10786 times

RESET

0.3V

DD

Note: Keep the value of supply voltage the minimum value or more

(Note)

of the recommended operating conditions.

• the value of supply voltage is the minimum value or more of

the recommended operating conditions.

Then when “H” level is applied to RESET pin, software starts

from address 0 in page 0.

____________

Software start

(Address 0 in page 0)

Software start

(Address 0 in page 0)

Fig. 24 RESET pin input waveform and reset operation

(1) Power-on reset

Reset can be automatically performed at power on (poweron reset) by the built-in power-on reset circuit. When the builtin power-on reset circuit is used, the time for the supply voltage

to reach the minimum operating voltage must be set to 100

Pull-up

transistor

RESET

pin

(Note)

Power-on

reset circuit

WEF

Note:

This symbol represents a parasitic

diode.

Applied potential to RESET pin must

DD

or less.

be V

µ

s or less. If the rising time exceeds 100 µs, connect a

capacitor between the

distance, and input “L” level to

supply voltage reaches the minimum operating voltage.

Internal reset

signal

Voltage drop detection circuit

Watchdog timer

output

Power-on

RESET pin and VSS at the shortest

RESET pin until the value of

V

DD

Power-on reset circuit

output voltage

Reset state

Internal reset signal

Reset released

Fig. 25 Power-on reset circuit example

28

Page 29

MITSUBISHI MICROCOMPUTERS

4570 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

(2) Internal state at reset

Table 12 shows port state at reset, and Figure 26 shows

internal state at reset (they are retained after system is

The contents of timers, registers, flags and RAM except those

shown in Figure 26 are undefined, so set the initial values to

them.

released from reset).

Table 12 Port state at reset

Function

High impedance (Note 1)

“H” (VDD) level (Note 1)

High impedance

High impedance (Note 1)

High impedance (Note 2)

SS) level

“L” (V

D

0–D8, D9/TOUT

P00–P03

P10–P13

P20, P21/INT

0–P33

P3

P40–P43

CARR

Name

0–D8, D9

D

P00–P03

P10–P13

P20, P21

P30–P33

P40–P43

CARR

Notes 1: Output latch is set to “1.”

2: The pull-up transistor is turned off.

• Program counter (PC)............................................................................................

00000000000000

Address 0 in page 0 is set to program counter.

• Interrupt enable flag (INTE) ...................................................................................

• Power down flag (P)...............................................................................................

• External 0 interrupt request flag (EXF0)................................................................

• Interrupt control register V1 ...................................................................................

• Interrupt control register V2 ...................................................................................

• Interrupt control register I1 ....................................................................................

0 0 0 0 (Interrupt disabled)

0 0 0 0 (Interrupt disabled)

0000

• Timer 1 interrupt request flag (T1F) ......................................................................

• Timer 2 interrupt request flag (T2F) ......................................................................

• Timer 3 interrupt request flag (T3F) ......................................................................

• Watchdog timer flags (WDF1, WDF2) ...................................................................

• Watchdog timer enable flag (WEF) .......................................................................

• Timer control register W1 ......................................................................................

• Timer control register W2 ......................................................................................

• Timer control register W3 ......................................................................................

0 0 0 0 (Prescaler and timer 1 stopped)

0 0 0 0 (Timer 2 stopped)

0 0 0 0 (Timer 3 stopped)

• Timer count value store register W5 .....................................................................

• Clock control register MR ......................................................................................

• 8-bit general-purpose register SI ...........................................................................

0000

1000

0000

• Carrier wave output control register C2.................................................................

• Key-on wakeup control register K0 .......................................................................

• Pull-up control register PU0...................................................................................

0000

0000