Page 1

FA ST ACCESS TIME: 180ns

EXTENDED TEMPERATURE RANGE

SINGLE 5V SUPPLY VOLT AGE

LOW STANDBY CURRE NT: 35mA max

TTL COMP A TIBLE DURING READ and PROGRAM

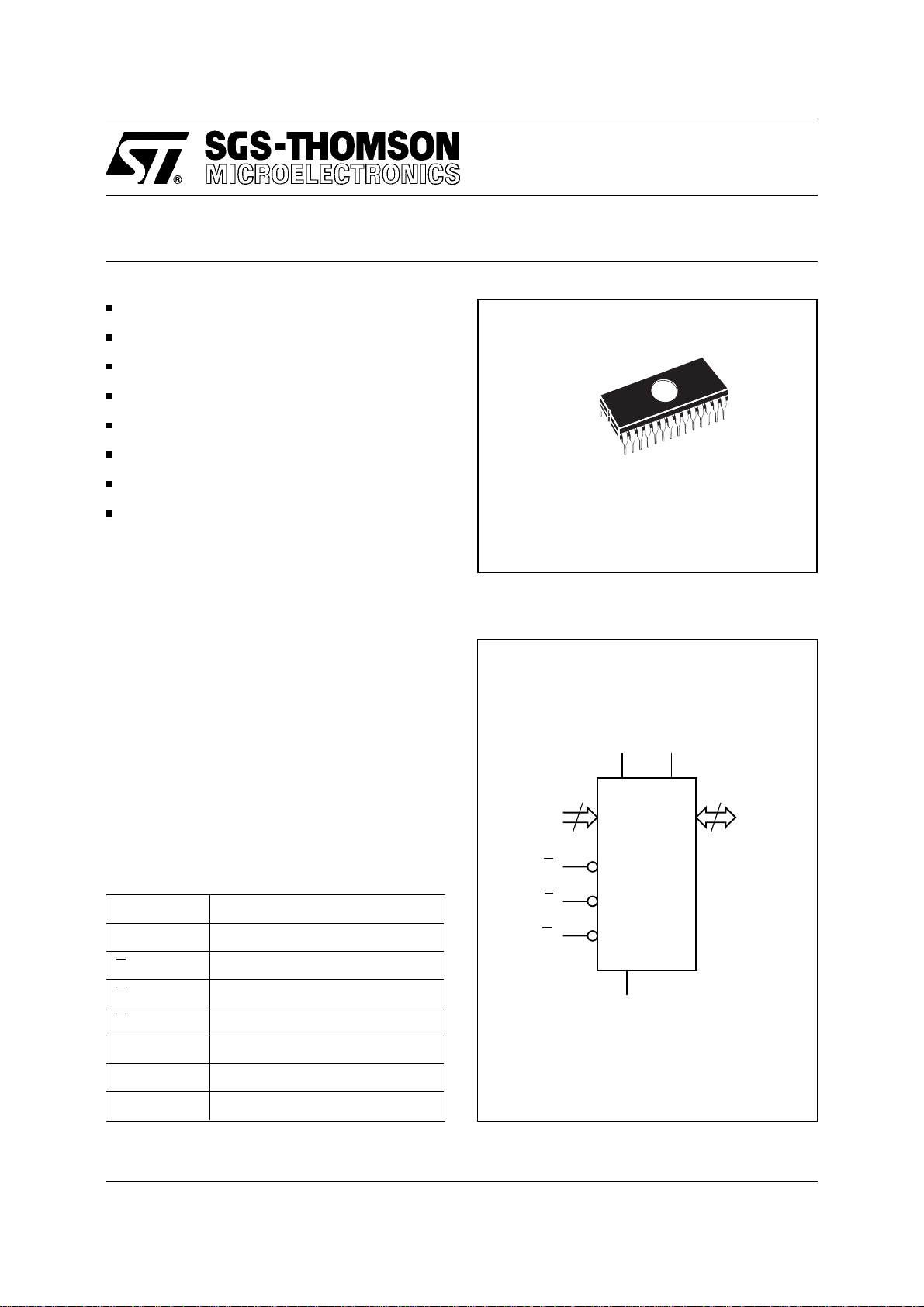

M2764A

NMOS 64K (8K x 8) UV EPROM

28

FAST PROGRAMMING ALGORITHM

ELECTRONIC SIGNATURE

PROGRAMMING VOLTAGE: 12V

DESCRIPTION

The M2764A is a 65,536 bit UV erasable and

electrically programmable memory EPROM. It is

organized as 8,192 words by 8 bits.

The M27C64A is housed in a 28 pin Window Ceramic Frit-Seal Dual-in-Line package. The transparent lid allows the user to expose the chip to

ultraviolet light to erase the bit pattern. A new

pattern can then be written to the device by following the programming procedure.

T able 1. Signal Names

A0 - A12 Address Inputs

Q0 - Q7 Data Outputs

1

FDIP28W (F)

Figure 1. Logic Diag ra m

V

CC

13

A0-A12

P

E

G

M2764A

V

PP

8

Q0-Q7

E Chip Enable

G Output Enable

P Program

V

PP

V

CC

V

SS

March 1995 1/10

Program Supply

Supply Voltage

Ground

V

SS

AI00776B

Page 2

M2764A

Table 2. Absolute Maximum Ratings

Symbol Parameter Value Unit

T

A

T

BIAS

T

STG

V

IO

V

CC

V

A9

V

PP

Note: Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Rati ngs" may cause

permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those

indicated in the Operating sections of t hi s specification is not implied. Expos ure to Absolut e Maximum Rati ng conditions for extended periods

may affect device reliability. Refer also to the SGS-THOMSON SURE Program and other relevant quality documents.

Ambient Operating Temperature grade 1

grade 6

Temperature Under Bias grade 1

grade 6

Storage Temperature –65 to 125 °C

Input or Output Voltages –0.6 to 6.5 V

Supply Voltage –0.6 to 6.5 V

A9 Voltage –0.6 to 13.5 V

Program Supply –0.6 to 14 V

0 to 70

–40 to 85

–10 to 80

–50 to 95

°C

°C

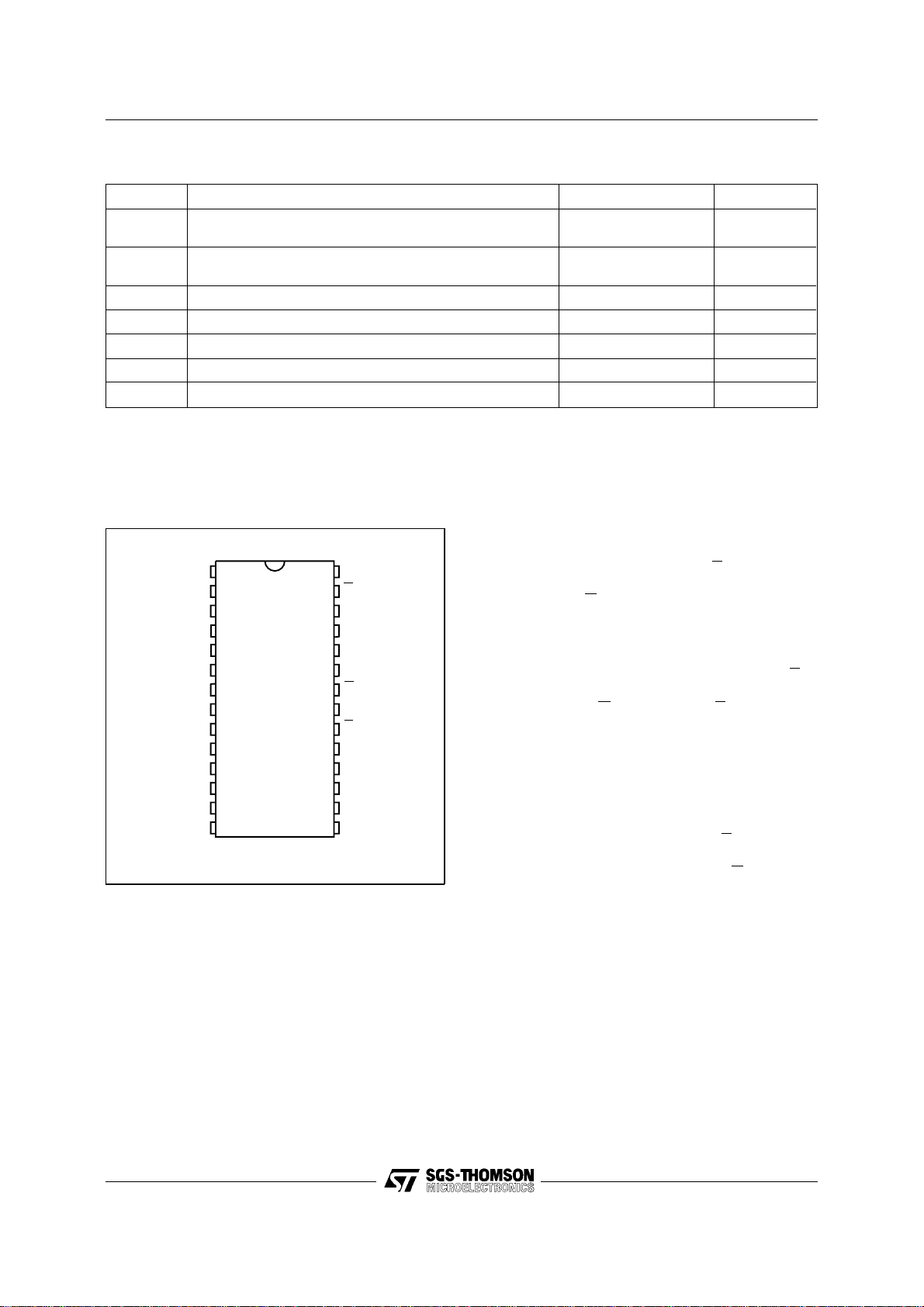

Figure 2. DIP Pin Connection s

V

1

PP

2

A7

3

4

A6

5

A5

A4

6

7

A3

A2

A1

A0

Q0

Q1

Q2

V

SS

Warning: NC = Not Connected.

8

9

10

11

12

13

14

M2764A

28

27

26

25

24

23

22

21

20

19

18

17

16

15

AI00777

V

CC

PA12

NC

A8

A9

A11

G

A10

E

Q7

Q6

Q5

Q4

Q3

DEVICE OPER ATION

The seven modes of operations of the M2764A are

listed in the Operating Modes table. A single 5V

power supply is required in the read mode. All

inputs are TTL levels except f or V

and 12V on A 9

PP

for Electronic Signature.

Read Mode

The M2764A has two control functions, both of

which must be logically satisfied in order to obtain

data at the outputs. Chip Enable (

E) is the power

control and should be used for device selection.

Output Enable (

G) is the output control and should

be used to gate data to the output pins, independent of device selection.

Assuming that the addresses are stable, address

access time (t

output (t

ELQV

the falling edge of

) is equal to the delay from E to

AVQV

). Data is available at the outputs after

G, assuming that E has been low

and the addresses have been stable for at least

t

AVQ V-tGLQV

.

Stand by Mod e

The M2764A has a standby mode which reduces

the maximum active power current from 75mA to

35mA. The M2764A is placed in the standby mode

by applying a TTL high signal to the

E input. Whe n

in the standby mode, the outputs are in a high

impedance state, independent of the

G input.

Two Line Output Control

Because EPROM s are usually used in larger memory arrays, the product features a 2 line control

function which accommodates the use of multiple

memory connection. The two line control function

allows :

a. the lowest possible memory power dissipation,

b. complete ass urance that output bus contention

will not occur .

2/10

Page 3

M2764A

DEVICE OPER ATION (cont’d)

For the most efficient us e of these two control lines,

E should be decoded and used as the primary

device selecting function, while

G should be made

a common connection to all devices in the array

and connected to the

READ line from the system

control bus.

This ensures that all deselected memory devices

are in their low power standby mode and that the

output pins are only active when data is desired

from a particular memory device.

System Considerati ons

The power switching characteristics of fast

EPROMs require careful decoupling of the devices.

The supply current, I

, has three segments that

CC

are of interest to the system designer: the standby

current level, the active c urrent level, and transient

current peaks that are produced by the falling and

rising edges of

E. The magnitude of the transient

current peaks is dependent on the capacitive and

inductive loading of the device at the output. The

associated transient voltage peaks can be suppressed by complying with the two line output

control and by properly selected decoupling capacitors. It is recommended that a 1µF ceramic

capacitor be used on every device between V

CC

and VSS. This should be a high frequency capacitor

of low inherent inductance and should be placed

as close to the device as possible. In addition, a

4.7µF bulk electrolytic capacitor should be used

between V

and VSS for every eight devices. The

CC

bulk capacitor should be located near the power

supply connection point. The purpose of the bulk

capacitor is to overcome the voltage drop caused

by the inductive effects of PCB trac es.

Programming

When delivered (and after each erasure for UV

EPROM), all bits of the M2764A are in t he “1" st ate.

Data is introduced by selectively programming ”0s"

into the desired bit locations. Alth ough only “0s” will

be programmed, both “1s” and “0s” can be present

in the data word. The only way to change a “0" to

a ”1" is by ultraviolet light erasure.

The M2764A is in the programming mode when

input is at 12.5V and E and P are at TTL low.

V

PP

The data to be programmed is applied, 8 bits in

parallel, to the data output pins. The lev els required

for the address and data inputs are TTL.

Fast Programmi ng Al gor ithm

Fast Programming Algorithm rapidly programs

M2764A EPROMs using an efficient and reliable

method suited to the production programming environment. Programming reliability is also ensured

as the incremental program margin of each byte is

continually monitored to determine when it has

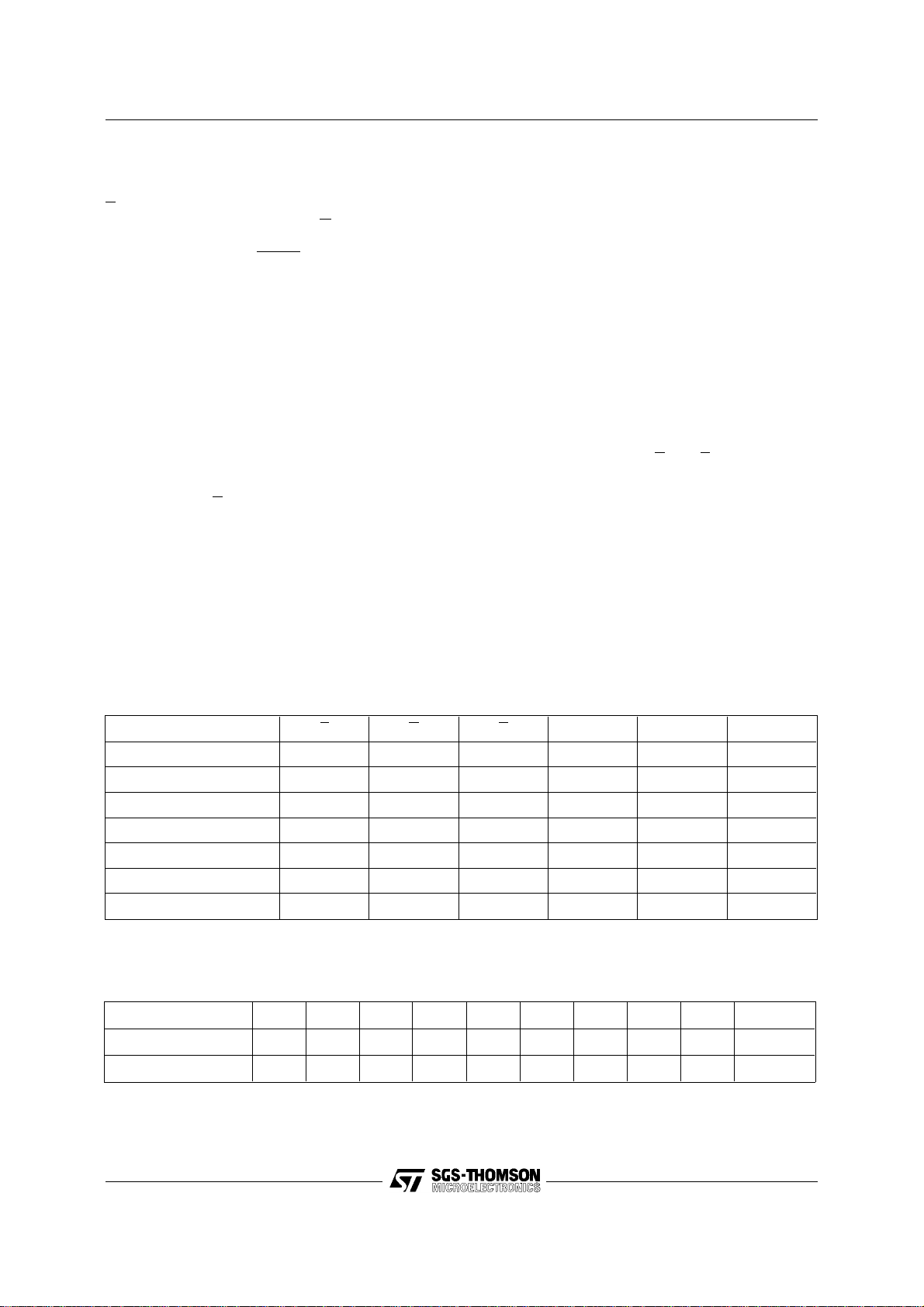

Table 3. Operating Modes

Mode E G PA9VPPQ0 - Q7

Read V

Output Disable V

Program V

Verify V

Program Inhibit V

Standby V

Electronic Signature V

Note: X = VIH or VIL, VID = 12V ± 0.5%.

IL

IL

IL

IL

IH

IH

IL

V

IL

V

IH

V

IH

V

IL

XXXVPPHi-Z

XXXVCCHi-Z

V

IL

V

IH

V

IH

VIL Pulse X V

V

IH

V

IH

XVCCData Out

XVCCHi-Z

XVPPData Out

V

ID

PP

V

CC

Tab le 4. Electronic Sig natu r e

Identifier A0 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0 Hex Data

Manufacturer’s Code V

Device Code V

IL

IH

00100000 20h

00001000 08h

Data In

Codes Out

3/10

Page 4

M2764A

AC MEASUREMENT CONDITIONS

Input Rise and Fall Times ≤ 20ns

Figure 4. AC T esti ng Load Circui t

1.3V

Input Pulse Voltages 0.45V to 2.4V

Input and Output Timing Ref. Voltages 0.8V to 2.0V

1N914

Note that Output Hi-Z is defined as the point where data

is no longer driven.

Figure 3. AC Test ing Input Outp ut W avefo rm s

3.3kΩ

DEVICE

UNDER

2.4V

0.45V

T ab le 5. Capacitance

(1)

(TA = 25 °C, f = 1 MHz )

2.0V

0.8V

AI00827

Symbol Parameter Test Condition Min Max Unit

C

IN

C

OUT

Note: 1. Sampled only, not 100% tested.

Input Capacitance VIN = 0V 6 pF

Output Capacitance V

OUT

TEST

CL = 100pF

CL includes JIG capacitance

= 0V 12 pF

OUT

AI00828

Figure 5. Read Mode AC Wavefor m s

A0-A12

tAVQV

E

G

tELQV

Q0-Q7

tGLQV

VALID

tAXQX

tEHQZ

tGHQZ

Hi-Z

DATA OUT

AI00778

4/10

Page 5

M2764A

Tab l e 6. Read Mode DC Characteristics

(1)

(TA = 0 to 70 °C or –40 to 85 °C; VCC = 5V ± 5% or 5V ± 10%; VPP = VCC)

Symbol Parameter Test Condition Min Max Unit

I

I

LO

I

CC

I

CC1

I

PP

V

V

V

V

OH

Note: 1. VCC must be applied simultaneously with or bef o re VPP and removed simultaneously or after VPP.

T ab le 7A. Read Mode AC Charact eristi cs

Input Leakage Current 0 ≤ VIN ≤ V

LI

Output Leakage Current V

OUT

Supply Current E = VIL, G = V

Supply Current (Standby) E = V

Program Current VPP = V

Input Low Voltage –0.1 0.8 V

IL

Input High Voltage 2 VCC + 1 V

IH

Output Low Voltage IOL = 2.1mA 0.45 V

OL

= V

CC

CC

IL

IH

CC

Output High Voltage IOH = –400µA 2.4 V

(1)

±10 µA

±10 µA

75 mA

35 mA

5mA

(TA = 0 to 70 °C or –40 to 85 °C; VCC = 5V ± 5% or 5V ± 10%; VPP = VCC)

M2764A

Symbol Alt Parameter

t

AVQVtACC

t

ELQV

t

GLQV

(2)

t

EHQZ

(2)

t

GHQZ

t

AXQX

Address Valid to

Output Valid

Chip Enable Low

t

CE

to Output Valid

Output Enable

t

OE

Low to Output Valid

Chip Enable High

t

DF

to Output Hi-Z

Output Enable

t

DF

High to Output Hi-Z

Address Transition

t

OH

to Output Transition

Test

Condition

E = VIL,

G = V

IL

G = V

IL

E = V

IL

G = V

IL

E = V

IL

E = VIL,

G = V

IL

-1 -2, -20 blank, -25

Min Max Min Max Min Max

180 200 250 ns

180 200 250 ns

65 75 100 ns

055055060ns

055055060ns

000ns

Unit

T ab le 7B. Read Mode AC Charact eristi cs

(1)

(TA = 0 to 70 °C or –40 to 85 °C; VCC = 5V ± 5% or 5V ± 10%; VPP = VCC)

Symbol Alt Parameter

Test

Condition

-3 -4

Min Max Min Max

t

AVQVtACC

t

ELQV

t

GLQV

(2)

t

EHQZ

(2)

t

GHQZ

t

AXQX

Notes: 1. VCC must be applied simultaneously with or before VPP and removed simultaneously or after VPP.

2. Sampled only, not 100% tested.

Address Valid to

Output Valid

Chip Enable Low

t

CE

to Output Valid

Output Enable

t

OE

Low to Output Valid

Chip Enable High

t

DF

to Output Hi-Z

Output Enable

t

DF

High to Output Hi-Z

Address Transition

t

OH

to Output Transition

E = VIL,

G = V

IL

G = V

IL

E = VIL, 120 150 ns

G = V

E = V

E = VIL,

G = V

IL

IL

IL

0 105 0 130 ns

0 105 0 130 ns

00ns

M2764A

300 450 ns

300 450 ns

Unit

5/10

Page 6

M2764A

Tab le 8. Programmin g Mode DC Characteristics

(1)

(TA = 25 °C; VCC = 6V ± 0.25V; VPP = 12.5V ± 0.3V)

Symbol Parameter Test Condition Min Max Units

I

LI

I

CC

I

PP

V

IL

V

IH

V

OL

V

OH

Input Leakage Current VIL ≤ VIN ≤ V

IH

±10 µA

Supply Current 75 mA

Program Current E = V

IL

50 mA

Input Low Voltage –0.1 0.8 V

Input High Voltage 2 VCC + 1 V

Output Low Voltage IOL = 2.1mA 0.45 V

Output High Voltage IOH = –400µA 2.4 V

VA9 A9 Voltage 11.5 12.5 V

Note: 1. VCC must be applied simultaneously with or before VPP and removed simultaneously or after VPP.

T ab le 9. Programming Mod e AC Character istics

(1)

(TA = 25 °C; VCC = 6V ± 0.25V; VPP = 12.5V ± 0.3V)

Symbol Alt Parameter Test Condition Min Max Units

t

AVPL

t

QVPL

t

VPHPL

t

VCHPL

t

ELPL

t

PLPH

t

PLPH

t

PHQX

t

QXGL

t

GLQV

t

GHQZ

t

GHAX

Notes: 1. VCC must be applied simultaneously with or bef o re VPP and removed simultaneously or after VPP.

2. The Initial Program Pulse width tolerance is 1 ms ± 5%.

3. The length of the Over-program Pulse varies from 2.85 ms to 78.95 ms, d e p endi n g of t h e multi plication value of the iteration c ounter.

4. Sampled only, not 100% tested.

t

Address Valid to Program Low 2 µs

AS

t

t

VPS

t

VCS

t

CES

t

t

OPW

t

t

OES

t

(4)

t

DFP

t

Input Valid to Program Low 2 µs

DS

VPP High to Program Low 2 µs

VCC High to Program Low 2 µs

Chip Enable Low to Program

Low

Program Pulse Width (Initial) Note 2 0.95 1.05 ms

PW

Program Pulse Width

(Overprogram)

Program High to Input

DH

Transition

Note 3 2.85 78.75 ms

Input Transition to Output

Enable Low

Output Enable Low to Output

OE

Valid

Output Enable High to Output

Hi-Z

Output Enable High to Address

AH

Transition

2 µs

2 µs

2 µs

0 130 ns

0ns

150 ns

6/10

Page 7

Figure 6. Programming and Verify Modes AC Wavefo r m s

M2764A

A0-A12

tAVPL

Q0-Q7

V

PP

V

CC

E

P

G

DATA IN DATA OUT

tQVPL

tVPHPL

tVCHPL

tELPL

tPLPH

PROGRAM VERIFY

Figure 7. Fast Programming Flowchart

VCC = 6V, VPP = 12.5V

n = 1

P = 1ms Pulse

NO

NO

VERIFY

YES

P = 3ms Pulse by n

Last

NO

Addr

YES

CHECK ALL BYTES

VCC = 5V, VPP 5V

++ Addr

AI00775B

YES

++n

> 25

FAIL

VALID

tPHQX

tGLQV

tQXGL

tGHQZ

tGHAX

AI00779

DEVICE OPERATION (cont’d)

been successfully programmed. A flowchart of the

M2764A Fast Programm ing Algorithm is shown on

the last page. The Fast Programming Algorithm

utilizes two different pulse types: initial and overprogram.

The duration of the initial

P pulse(s) is 1ms, which

will then be followed by a longer overprogr am pulse

of length 3ms by n (n is equal to the number of the

initial one millisecond pulses applied to a particular

M2764A location), before a correct verify occurs.

Up to 25 one-millisecond pulses per byte are provided for before the overprogram pulse is applied.

The entire sequence of program pulses and byte

verifications is performed at V

= 6V and VPP =

CC

12.5V . When the Fast Programming cycle has been

completed, all bytes should be compared to the

original data with V

= 5V and VPP = 5V.

CC

Program Inhibit

Programming of multiple M2764A in parallel with

different data is also easily accomplished. Except

E, all like inputs (including G) of the parallel

for

M2764A may be comm on. A TTL low pulse applied

to a M2764A’s

program that M2764A. A high level

E input, with VPP at 12.5V, will

E input inhibits

the other M2764As from being programmed.

7/10

Page 8

M2764A

Program V eri fy

A verify should be performed on the programmed

bits to determine that they were correctly programmed. The verify is accomplished with

G = VIL,

E = VIL, P = VIH and VPP = 12.5V.

Electronic Signature

The Electronic Signature mode allows the reading

out of a binary code from an EPROM that will

identify its manufacturer and type. This mode is

intended for use by programming equipment to

automatically matc h the devic e to be programm ed

with its corresponding programming algorithm.

This mode is functional in t he 25°C ± 5°C ambient

temperature ran ge that is required wh en programming the M2764A.

T o act ivate this mode, the pr ogramming equipment

must force 1 1.5V to 12.5V on address line A9 of the

M2764A. Two identifier bytes may then be sequenced from the device outputs by toggling address line A0 from V

must be held at V

mode. Byte 0 (A0 = V

turer code and byte 1 (A0 = V

to VIH. All other address lines

IL

during Electronic Signature

IL

) represents the manufac-

IL

) the device identifier

IH

code. For the SGS -THOMSON M2764A, these two

identifier bytes are given below.

ERASURE OP ERA TION (applies to U V EPPRO M)

The erasure characteristic of the M2764A is such

that erasure begins when the cells are exposed to

light with wavelengths shorter than approximately

4000 Å. It should be noted that sunlight and some

type of fluorescent lamps have wavelengt hs in th e

3000-4000 Å range. Research shows that constant

exposure to room level fluorescent lighting could

erase a typical M2764A in about 3 years, while it

would take approximately 1 week to cause erasure

when exposed to direct sunlight. If the M2764A is

to be exposed to these types of lighting conditions

for extended periods of time, it is suggested that

opaque labels be put over the M2764A window to

prevent unintentional erasure. The recommended

erasure procedure for the M2764A is exposure to

short wave ultraviolet light which has wavelength

2537 Å. The integrated dose (i.e. UV intensity x

exposure time) for erasure should be a minimum

of 15 W-s ec/cm

is approximately 15 to 20 minutes using an ultraviolet lamp with 12000 µW/cm

2

. The erasure time with this d osage

2

power rating. The

M2764A should be placed within 2.5 c m (1 inch) of

the lamp tubes during the erasure. Some lamps

have a filter on their tubes which should be removed before erasure.

ORDERI NG INFO RM ATION SCHEME

Example: M2764A -1 F 1

Speed and VCC Tolerance

-1 180 ns, 5V ±5%

-2 200 ns, 5V ±5%

blank 250 ns, 5V ±5%

-3 300 ns, 5V ±5%

-4 450 ns, 5V ±5%

-20 200 ns, 5V ±10%

-25 250 ns, 5V ±10%

For a list of available options (Speed, V

T olerance, Package, etc ...) refer to the current Memory Shor tform

CC

Package

F FDIP28W

Temperature Range

1 0 to 70 °

6 –40 to 85 °C

catalogue.

For further information o n any aspect of this device, please contact SGS-THOM SON Sales O ffice nearest

to you.

8/10

Page 9

FDIP28W - 28 pin Ceramic Frit-seal DIP, with window

M2764A

Symb

Typ Min Max Typ Min Max

A 5.71 0.225

A1 0.50 1.78 0.020 0.070

A2 3.90 5.08 0.154 0.200

B 0.40 0.55 0.016 0.022

B1 1.17 1.42 0.046 0.056

C 0.22 0.31 0.009 0.012

D 38.10 1.500

E 15.40 15.80 0.606 0.622

E1 13.05 13.36 0.514 0.526

e1 2.54 – – 0.100 – –

e3 33.02 – – 1.300 – –

eA 16.17 18.32 0.637 0.721

L 3.18 4.10 0.125 0.161

S 1.52 2.49 0.060 0.098

∅ 7.11 – – 0.280 – –

α 4° 15° 4° 15°

N28 28

FDIP28W

mm inches

Drawing is not to scale

A1AL

B1 B e1

e3

D

S

N

∅

1

A2

Cα

eA

E1 E

FDIPW-a

9/10

Page 10

M2764A

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the

consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No

license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specificat ions mentioned

in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied.

SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express

written approval of SGS-THOMSON Microelectronics.

© 1995 SGS-THOMSON Microelectronics - All Rights Reserved

Australia - Brazil - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocc o - The Netherlands -

Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

SGS-THOMSON Microelectronics GROUP OF COMPANIES

10/10

Loading...

Loading...