Page 1

FEATURES

■

One External Resistor Sets the Frequency

■

1kHz to 20MHz Frequency Range

■

500µA Typical Supply Current, VS = 3V, 3MHz

■

Frequency Error ≤1.5% Max, 5kHz to 10MHz

(TA = 25°C)

■

Frequency Error ≤2% Max, 5kHz to 10MHz

(TA = 0°C to 70°C)

■

±40ppm/°C Temperature Stability

■

0.04%/V Supply Stability

■

50% ±1% Duty Cycle 1kHz to 2MHz

■

50% ±5% Duty Cycle 2MHz to 10MHz

■

Fast Start-Up Time: 50µs to 1.5ms

■

100Ω CMOS Output Driver

■

Operates from a Single 2.7V to 5.5V Supply

■

Low Profile (1mm) ThinSOTTM Package

U

APPLICATIO S

■

Portable and Battery-Powered Equipment

■

PDAs

■

Cell Phones

■

Low Cost Precision Oscillator

■

Charge Pump Driver

■

Switching Power Supply Clock Reference

■

Clocking Switched Capacitor Filters

■

Fixed Crystal Oscillator Replacement

■

Ceramic Oscillator Replacement

LTC6900

Low Power, 1kHz to 20MHz

Resistor Set SOT-23 Oscillator

U

DESCRIPTIO

The LTC®6900 is a precision, low power oscillator that is

easy to use and occupies very little PC board space. The

oscillator frequency is programmed by a single external

resistor (R

accuracy operation (≤1.5% frequency error) without the

need for external trim components.

The LTC6900 operates with a single 2.7V to 5.5V power

supply and provides a rail-to-rail, 50% duty cycle square

wave output. The CMOS output driver ensures fast rise/fall

times and rail-to-rail switching. The frequency-setting

resistor can vary from 10kΩ to 2MΩ to select a master

oscillator frequency between 100kHz and 20MHz (5V

supply). The three-state DIV input determines whether the

master clock is divided by 1, 10 or 100 before driving the

output, providing three frequency ranges spanning 1kHz

to 20MHz (5V supply). The LTC6900 features a proprietary

feedback loop that linearizes the relationship between

R

and frequency, eliminating the need for tables to

SET

calculate frequency. The oscillator can be easily programmed using the simple formula outlined below:

f MHz

=•

OSC

, LTC and LT are registered trademarks of Linear Technology Corporation.

ThinSOT is a trademark of Linear Technology Corporation.

). The LTC6900 has been designed for high

SET

100

,

DIV Pin V

N Open

=

,

10

,

DIV Pin

1

,

DIV Pin GND

10

NR

•

20

k

SET

=

=

=

+

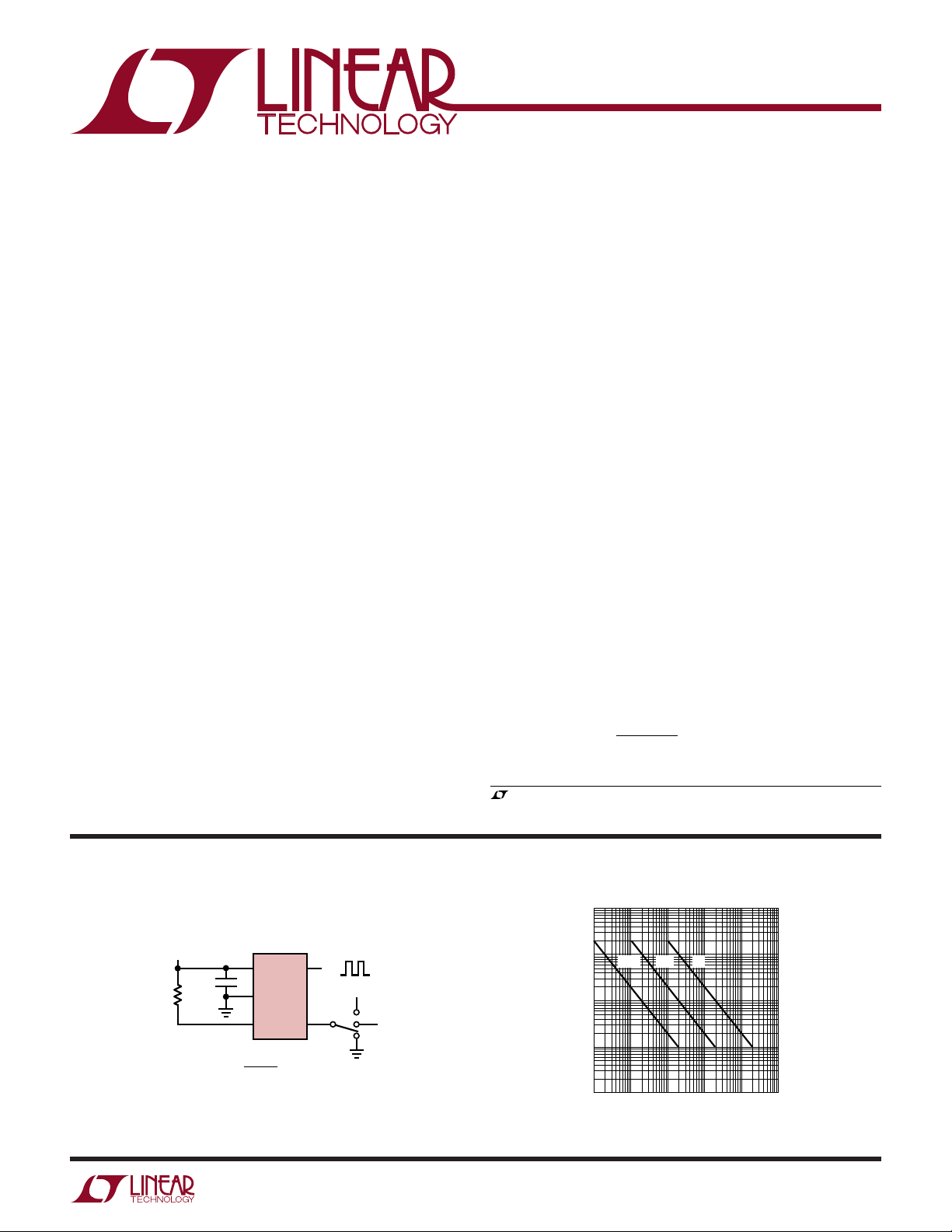

TYPICAL APPLICATIO

Clock Generator

10k ≤ R

SET

≤ 2M

5V

f

OSC

0.1µF

= 10MHz •

1

+

OUT

V

LTC6900

2

GND

3

SET

DIV

20k

()

N • R

SET

U

1kHz ≤ f

5

4

OSC

5V, N = 100

N = 1

≤ 20MHz

OPEN, N = 10

6900 TA01

R

vs Desired Output Frequency

SET

10000

1000

(kΩ)

SET

R

100

÷100 ÷10 ÷1

10

1

1k 100k 1M 10M

10k

DESIRED OUTPUT FREQUENCY (Hz)

100M

6900 F02

6900f

1

Page 2

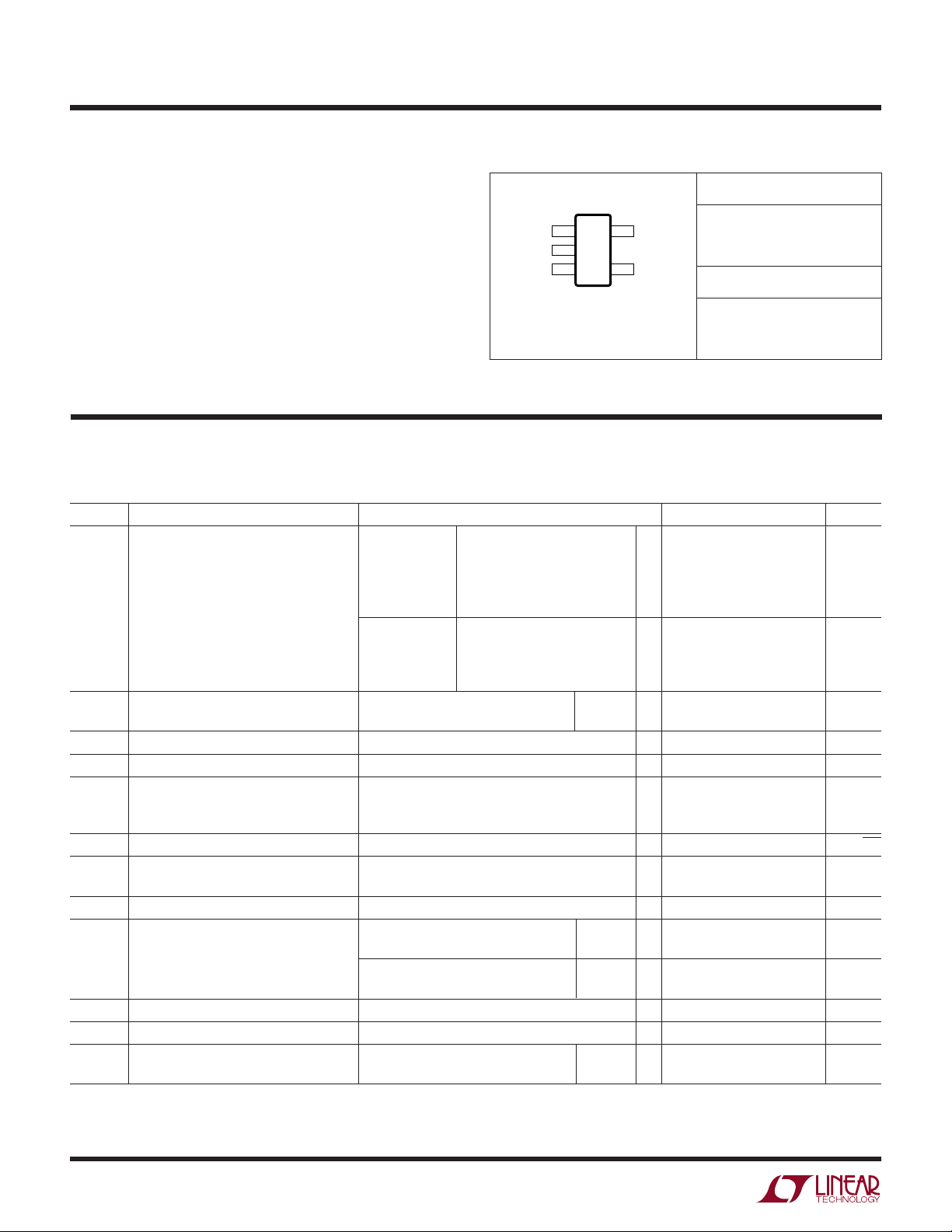

LTC6900

TOP VIEW

S5 PACKAGE

5-LEAD PLASTIC SOT-23

1

2

3

V

+

GND

SET

54OUT

DIV

PACKAGE/ORDER I FOR ATIO

UU

W

WWWU

ABSOLUTE AXI U RATI GS

(Note 1)

Supply Voltage (V+) to GND ........................– 0.3V to 6V

DIV to GND ....................................–0.3V to (V+ + 0.3V)

SET to GND ...................................–0.3V to (V+ + 0.3V)

Operating Temperature Range (Note 8)

LTC6900C .......................................... – 40°C to 85°C

LTC6900I............................................ –40°C to 85°C

Storage Temperature Range ................. –65°C to 150°C

Lead Temperature (Soldering, 10 sec).................. 300°C

ORDER PART NUMBER

LTC6900CS5

LTC6900IS5

S5 PART MARKING

T

= 150°C, θJA = 256°C/W

JMAX

Consult LTC Marketing for parts specified with wider operating temperature ranges.

LTZM

ELECTRICAL CHARACTERISTICS

The ● denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at TA = 25°C. V+ = 2.7V to 5.5V, RL= 5k, CL = 5pF, Pin 4 = V+ unless otherwise noted.

All voltages are with respect to GND.

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

∆f Frequency Accuracy (Notes 2, 3) V+ = 5V 5kHz ≤ f ≤ 10MHz ±0.5 ±1.5 %

V+ = 3V 5kHz ≤ f ≤ 10MHz ±0.5 ±1.5 %

R

SET

∆f/∆T Freq Drift Over Temp (Note 3) R

∆f/∆V Freq Drift Over Supply (Note 3) V+ = 3V to 5V, R

+

V

I

S

V

IH

V

IL

I

DIV

Frequency-Setting Resistor Range ∆f < 1.5% V+ = 5V 20 400 kΩ

= 63.2k ● ±0.004 %/°C

SET

Timing Jitter (Note 4) Pin 4 = V+, 20k ≤ R

Pin 4 = Open, 20k ≤ R

Pin 4 = 0V, 20k ≤ R

Long-Term Stability of Output Frequency 300 ppm/√kHr

Duty Cycle (Note 7) Pin 4 = V+ or Open (DIV Either by 100 or 10) ● 49 50 51 %

Pin 4 = 0V (DIV by 1), R

Operating Supply Range ● 2.7 5.5 V

Power Supply Current R

High Level DIV Input Voltage ● V+ – 0.4 V

Low Level DIV Input Voltage ● 0.5 V

DIV Input Current (Note 5) Pin 4 = V

= 400k, Pin 4 = V+, RL = ∞ V+ = 5V ● 0.32 0.42 mA

SET

f

= 5kHz V+ = 3V ● 0.29 0.38 mA

OSC

R

= 20k, Pin 4 = 0V, RL = ∞ V+ = 5V ● 0.92 1.20 mA

SET

= 10MHz V+ = 3V ● 0.68 0.86 mA

f

OSC

+

Pin 4 = 0V V

5kHz ≤ f ≤ 10MHz, LTC6900C

5kHz ≤ f ≤ 10MHz, LTC6900I

1kHz ≤ f < 5kHz ±2%

10MHz < f ≤ 20MHz ±2%

5kHz ≤ f ≤ 10MHz, LTC6900C

5kHz ≤ f ≤ 10MHz, LTC6900I

1kHz ≤ f < 5kHz ±2%

+

V

= 63.2k ● 0.04 0.1 %/V

SET

≤ 400k 0.1 %

SET

≤ 400k 0.2 %

SET

≤ 400k 0.6 %

SET

= 20k to 400k ● 45 50 55 %

SET

V+ = 5V ● 2 4 µA

+

● ±2.0 %

● ±2.5 %

● ±2.0 %

● ±2.5 %

= 3V 20 400 kΩ

= 5V ● –4 –2 µA

2

6900f

Page 3

LTC6900

ELECTRICAL CHARACTERISTICS

The ● denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at TA = 25°C. V+ = 2.7V to 5.5V, RL= 5k, CL = 5pF, Pin 4 = V+ unless otherwise noted.

All voltages are with respect to GND.

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OH

V

OL

t

r

t

f

Note 1: Absolute Maximum Ratings are those values beyond which the life

of the device may be impaired.

Note 2: Frequencies near 100kHz and 1MHz may be generated using two

different values of R

paragraph in the Applications Information section). For these frequencies,

the error is specified under the following assumption: 20k < R

Note 3: Frequency accuracy is defined as the deviation from the

f

OSC

Note 4: Jitter is the ratio of the peak-to-peak distribution of the period to

the mean of the period. This specification is based on characterization and

is not 100% tested. Also, see the Peak-to-Peak Jitter vs Output Frequency

curve in the Typical Performance Characteristics section.

Note 5: To conform with the Logic IC Standard convention, current out of

a pin is arbitrarily given as a negative value.

High Level Output Voltage (Note 5) V+ = 5V IOH = –1mA ● 4.8 4.95 V

= –4mA ● 4.5 4.8 V

I

OH

V+ = 3V IOH = –1mA ● 2.7 2.9 V

I

= –4mA ● 2.2 2.6 V

OH

Low Level Output Voltage (Note 5) V+ = 5V IOL = 1mA ● 0.05 0.15 V

= 4mA ● 0.2 0.4 V

I

OL

V+ = 3V IOL = 1mA ● 0.1 0.3 V

= 4mA ● 0.4 0.7 V

I

OL

OUT Rise Time V+ = 5V Pin 4 = V+ or Floating, RL = ∞ 14 ns

(Note 6) Pin 4 = 0V, R

V+ = 3V Pin 4 = V+ or Floating, RL = ∞ 19 ns

Pin 4 = 0V, R

OUT Fall Time V+ = 5V Pin 4 = V+ or Floating, RL = ∞ 13 ns

(Note 6) Pin 4 = 0V, R

V+ = 3V Pin 4 = V+ or Floating, RL = ∞ 19 ns

Pin 4 = 0V, R

(see the Selecting the Divider Setting Resistor

SET

≤ 200k.

SET

equation.

= ∞ 7ns

L

= ∞ 11 ns

L

= ∞ 6ns

L

= ∞ 10 ns

L

Note 6: Output rise and fall times are measured between the 10% and

90% power supply levels. These specifications are based on

characterization.

Note 7: Guaranteed by 5V test.

Note 8: The LTC6900C is guaranteed to meet specified performance from

0°C to 70°C. The LTC6900C is designed, characterized and expected to

meet specified performance from –40°C to 85°C but is not tested or QA

sampled at these temperatures. The LTC6900I is guaranteed to meet

specified performance from –40°C to 85°C.

6900f

3

Page 4

LTC6900

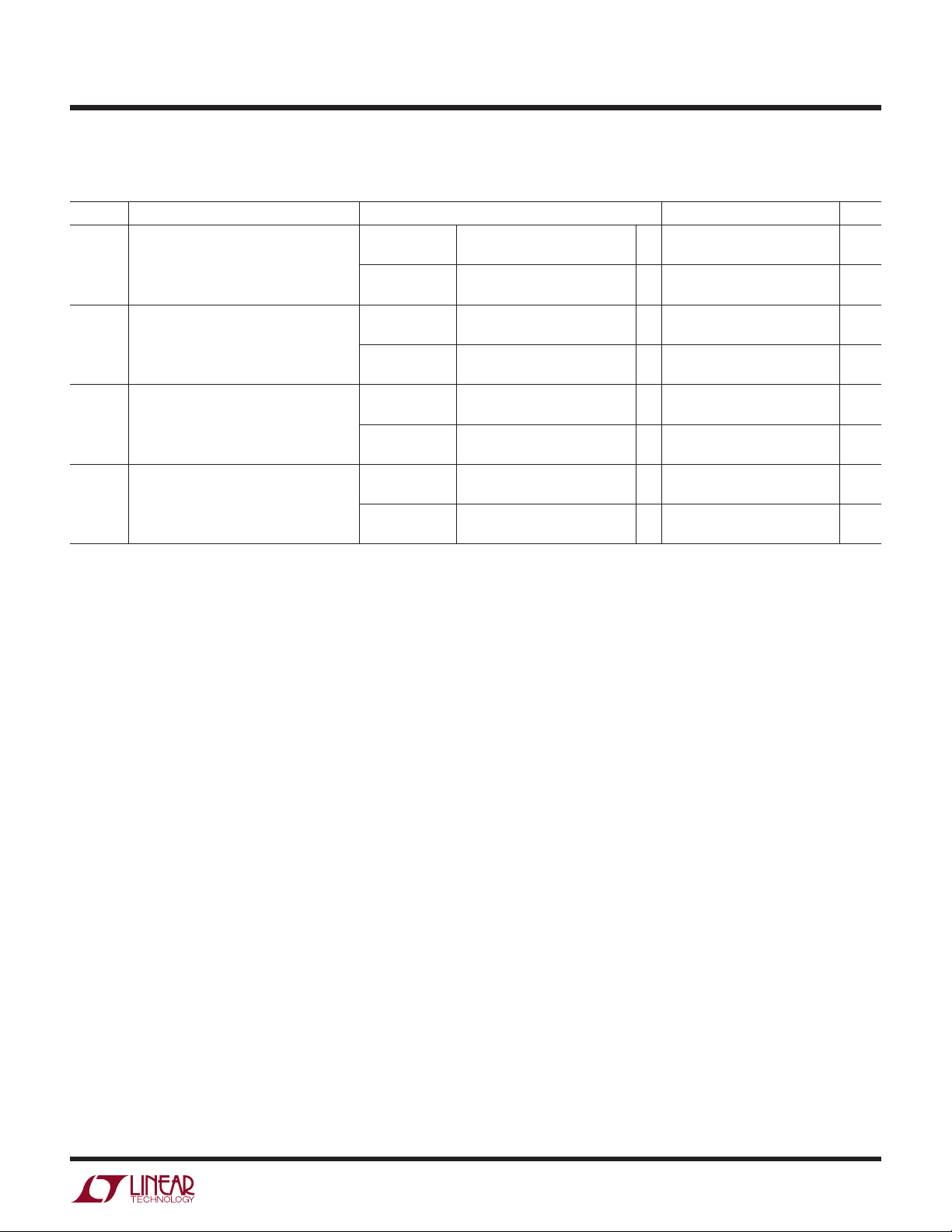

UW

TYPICAL PERFOR A CE CHARACTERISTICS

Frequency Variation vs R

4

TA = 25°C

3

GUARANTEED LIMITS APPLY OVER

20kΩ ≤ R

2

1

0

–1

VARIATION (%)

–2

–3

–4

1k

≤ 400kΩ

SET

10k 100k 1M

R

Supply Current vs Output

Frequency

2.0

TA = 25°C

C

= 5pF

L

1.5

1.0

SUPPLY CURRENT (mA)

0.5

÷100, 3V ÷10, 3V ÷1, 3V

0

0

1k 10k 100k 1M 10M

÷100, 5V

OUTPUT FREQUENCY (Hz)

TYPICAL HIGH

TYPICAL LOW

(Ω)

SET

SET

÷10, 5V

÷1, 5V

6900 G01

6900 G04

Frequency Variation Over

Temperature

1.00

R

= 63.4k

SET

0.75

÷1 OR ÷10 OR ÷100

0.50

0.25

0

–0.25

VARIATION (%)

–0.50

–0.75

–1.00

–20 0 20 40 60 80

–40

TEMPERATURE (°C)

Output Resistance

vs Supply Voltage

140

120

OUTPUT SOURCING CURRENT

100

80

OUTPUT RESISTANCE (Ω)

60

OUTPUT SINKING CURRENT

40

2.5 3.0

3.5

SUPPLY VOLTAGE (V)

TYPICAL

HIGH

TYPICAL

LOW

4.0

4.5

5.0

T

A

6900 G02

= 25°C

5.5

6900 G05

6.0

Peak-to-Peak Jitter vs Output

Frequency

1.0

0.9

0.8

0.7

)

0.6

P-P

0.5

0.4

JITTER (%

0.3

0.2

0.1

0

1k

÷1, VA = 3V

÷10

÷100

OUTPUT FREQUENCY (Hz)

÷1, VA = 5V

100k 1M10k 10M

LTC6900 Output Operating at

20MHz, VS = 5V

V+ = 5V, R

1V/DIV

0V

= 10k, CL = 10pF

SET

12.5ns/DIV

6900 G03

6900 G06

4

LTC6900 Output Operating at

10MHz, VS = 3V

V+ = 3V, R

1V/DIV

0V

= 20k, CL = 10pF

SET

25ns/DIV

6900 G07

6900f

Page 5

LTC6900

U

UU

PI FU CTIO S

V+ (Pin 1): Voltage Supply (2.7V ≤ V+ ≤ 5.5V). This supply

must be kept free from noise and ripple. It should be

bypassed directly to a ground plane with a 0.1µF capacitor.

GND (Pin 2): Ground. Should be tied to a ground plane for

best performance.

SET (Pin 3): Frequency-Setting Resistor Input. The value

of the resistor connected between this pin and V+ determines the oscillator frequency. The voltage on this pin is

held by the LTC6900 to approximately 1.1V below the V

voltage. For best performance, use a precision metal film

resistor with a value between 10kΩ and 2MΩ and limit the

capacitance on this pin to less than 10pF.

DIV (Pin 4): Divider-Setting Input. This three-state input

selects among three divider settings, determining the

value of N in the frequency equation. Pin 4 should be tied

to GND for the ÷1 setting, the highest frequency range.

+

Floating Pin 4 divides the master oscillator by 10. Pin 4

should be tied to V+ for the ÷100 setting, the lowest

frequency range. To detect a floating DIV pin, the LTC6900

attempts to pull the pin toward midsupply. Therefore,

driving the DIV pin high requires sourcing approximately

2µA. Likewise, driving DIV low requires sinking 2µA.

When Pin 4 is floated, it should preferably be bypassed by

a 1nF capacitor to ground or it should be surrounded by a

ground shield to prevent excessive coupling from other

PCB traces.

OUT (Pin 5): Oscillator Output. This pin can drive 5kΩ

and/or 10pF loads. Heavier loads may cause inaccuracies

due to supply bounce at high frequencies. Voltage transients, coupled into Pin 5, above or below the LTC6900

power supplies will not cause latchup if the current into/

out of the OUT pin is limited to 50mA.

BLOCK DIAGRA

+

V

1

R

SET

I

RES

SET

3

V

BIAS

GND

2

PATENT PENDING

W

I

V

+

–

RES

= (V+ – V

RES

GAIN = 1

) = 1.1V TYPICALLY

SET

ƒ

MO

MASTER OSCILLATOR

= 10MHz • 20kΩ •

I

RES

(V+ – V

SET

PROGRAMMABLE

DIVIDER (N)

(÷1, 10 OR 100)

DIVIDER

)

SELECT

THREE-STATE

INPUT DETECT

+

–

+

–

V

GND

OUT

5

+

2µA

DIV

4

2µA

6900 BD

6900f

5

Page 6

LTC6900

THEORY OF OPERATIO

U

As shown in the Block Diagram, the LTC6900’s master

oscillator is controlled by the ratio of the voltage between

the V+ and SET pins and the current (I

) is entering the

RES

SET pin. The voltage on the SET pin is forced to approximately 1.1V below V+ by the PMOS transistor and its gate

bias voltage. This voltage is accurate to ±8% at a particular

input current and supply voltage (see Figure 1).

A resistor R

“locks together” the voltage (V+ – V

, connected between the V+ and SET pins,

SET

) and current, I

SET

RES

,

variation. This provides the LTC6900’s high precision. The

master oscillation frequency reduces to:

ƒ=

MO

10

MHz

•

20

R

k

SET

Ω

The LTC6900 is optimized for use with resistors between

10k and 2M, corresponding to master oscillator frequencies between 100kHz and 20MHz.

To extend the output frequency range, the master oscillator signal may be divided by 1, 10 or 100 before driving

OUT (Pin 5). The divide-by value is determined by the state

of the DIV input (Pin 4). Tie DIV to GND or drive it below

0.5V to select ÷1. This is the highest frequency range, with

the master output frequency passed directly to OUT. The

DIV pin may be floated or driven to midsupply to select

÷10, the intermediate frequency range. The lowest frequency range, ÷100, is selected by tying DIV to V+ or

driving it to within 0.4V of V+. Figure 2 shows the relationship between R

, divider setting and output frequency,

SET

including the overlapping frequency ranges near 100kHz

and 1MHz.

The CMOS output driver has an on resistance that is

typically less than 100Ω. In the ÷1 (high frequency) mode,

the rise and fall times are typically 7ns with a 5V supply and

11ns with a 3V supply. These times maintain a clean

square wave at 10MHz (20MHz at 5V supply). In the ÷10

and ÷100 modes, where the output frequency is much

lower, slew rate control circuitry in the output driver

increases the rise/fall times to typically 14ns for a 5V

supply and 19ns for a 3V supply. The reduced slew rate

lowers EMI (electromagnetic interference) and supply

bounce.

1.4

1.3

1.2

SET

– V

+

1.1

= V

RES

V

1.0

0.9

0.8

Figure 1. V+ – V

V+ = 3V

10.1

V+ = 5V

10 100 1000

I

(µA)

RES

Variation with I

SET

6900 F01

RES

10000

1000

(kΩ)

100

SET

R

Figure 2. R

÷100 ÷10 ÷1

10

1

10k

1k 100k 1M 10M

DESIRED OUTPUT FREQUENCY (Hz)

vs Desired Output Frequency

SET

100M

6900 F02

6900f

6

Page 7

WUUU

V

+

1

2

3

5

182kHz TO 18MHz (TYPICALLY ±8%)

V

+

0.1µF

I

CONTROL

1µA TO 100µA

6900 F03

4

GND

N = 1

LTC6900

SET

OUT

DIV

10MHz

N

ƒ

OSC

≅

••I

CONTROL

I

CONTROL

EXPRESSED IN (A)

20kΩ

1.1V

APPLICATIO S I FOR ATIO

LTC6900

SELECTING THE DIVIDER SETTING AND RESISTOR

The LTC6900’s master oscillator has a frequency range

spanning 0.1MHz to 20MHz. However, accuracy may

suffer if the master oscillator is operated at greater than

10MHz with a supply voltage lower than 4V. A programmable divider extends the frequency range to greater than

three decades. Table 1 describes the recommended frequencies for each divider setting. Note that the ranges

overlap; at some frequencies there are two divider/resistor

combinations that result in the desired frequency.

In general, any given oscillator frequency (f

) should be

OSC

obtained using the lowest master oscillator frequency.

Lower master oscillator frequencies use less power and

are more accurate. For instance, f

obtained by either R

= 10MHz or R

The R

= 200k approach is preferred for lower power and

SET

= 200k, N = 10, master oscillator = 1MHz.

SET

= 20k, N = 100, master oscillator

SET

= 100kHz can be

OSC

better accuracy.

Table 1. Frequency Range vs Divider Setting

DIVIDER SETTING FREQUENCY RANGE

< 20kΩ), the

SET

*

÷1 ⇒ DIV (Pin 4) = GND > 500kHz

÷10 ⇒ DIV (Pin 4) = Floating 50kHz to 1MHz

÷100 ⇒ DIV (Pin 4) = V

*

At master oscillator frequencies greater than 10MHz (R

LTC6900 may experience reduced accuracy with a supply voltage less than

4V.

+

< 100kHz

ALTERNATIVE METHODS OF SETTING THE OUTPUT

FREQUENCY OF THE LTC6900

The oscillator may be programmed by any method that

sources a current into the SET pin (Pin 3). The circuit in

Figure 3 sets the oscillator frequency using a programmable current source and in the expression for f

resistor R

is replaced by the ratio of 1.1V/I

SET

CONTROL

OSC

, the

. As

already explained in the “Theory of Operation,” the voltage

difference between V+ and SET is approximately 1.1V,

therefore, the Figure 3 circuit is less accurate than if a

resistor controls the oscillator frequency.

Figure 4 shows the LTC6900 configured as a VCO. A

voltage source is connected in series with an external 20k

resistor. The output frequency, f

V

CONTROL

, that is the voltage source connected between

, will vary with

OSC

V+ and the SET pin. Again, this circuit decouples the

relationship between the input current and the voltage

between V+ and SET; the frequency accuracy will be

degraded. The oscillator frequency, however, will monotonically increase with decreasing V

CONTROL

.

After choosing the proper divider setting, determine the

correct frequency-setting resistor. Because of the linear

correspondence between oscillation period and resistance, a simple equation relates resistance with frequency.

100

= 2M)

10

1

Rk

=

20

SET

(R

SETMIN

Any resistor, R

oscillator, f

•

= 10k, R

SET

.

OSC

10

Nf

MHz

•

OSC

SETMAX

, N =

, tolerance adds to the inaccuracy of the

Figure 3. Current Controlled Oscillator

+

V

CONTROL

0V TO 1.1V

V

0.1µF

+

–

R

SET

20k

≅

ƒ

OSC

TYPICAL f

±0.5%, V

±8%, V

1

2

3

10MHz

N

OSC

CONTROL

CONTROL

+

OUT

V

LTC6900

GND

SET

DIV

6900 F04

20k

• • 1 –

R

SET

ACCURACY

= 0V

= 0.5V

5

4

()

Figure 4. Voltage Controlled Oscillator

N = 1

V

CONTROL

1.1V

6900f

7

Page 8

LTC6900

WUUU

APPLICATIO S I FOR ATIO

POWER SUPPLY REJECTION

Low Frequency Supply Rejection (Voltage Coefficient)

Figure 5 shows the output frequency sensitivity to power

supply voltage at several different temperatures. The

LTC6900 has a guaranteed voltage coefficient of 0.1%/V

but, as Figure 5 shows, the typical supply sensitivity is

twice as low.

High Frequency Power Supply Rejection

The accuracy of the LTC6900 may be affected when its

power supply generates significant noise with a frequency

content in the vicinity of the programmed value of f

OSC

. If

a switching power supply is used to power the LTC6900,

and if the ripple of the power supply is more than 20mV,

make sure the switching frequency and its harmonics are

not related to the output frequency of the LTC6900.

Otherwise, the oscillator may show additional frequency

error.

If the LTC6900 is powered by a switching regulator and the

switching frequency or its harmonics coincide with the

output frequency of the LTC6900, the jitter of the oscillator

output may be affected. This phenomenon will become

noticeable if the switching regulator exhibits ripples beyond 30mV.

START-UP TIME

The start-up time and settling time to within 1% of the final

value can be estimated by t

10µs. Note the start-up time depends on R

START

≅ R

(3.7µs/kΩ) +

SET

and it is

SET

independent from the setting of the divider pin. For instance with R

= 100k, the LTC6900 will settle with 1%

SET

of its 200kHz final value (N = 10) in approximately 380µs.

Figure 6 shows start-up times for various R

resistors.

SET

Figure 7 shows an application where a second set resistor

R

is connected in parallel with set resistor R

SET2

SET1

via

switch S1. When switch S1 is open, the output frequency

of the LTC6900 depends on the value of the resistor R

SET1

.

When switch S1 is closed, the output frequency of the

LTC6900 depends on the value of the parallel combination

of R

SET1

and R

SET2

.

The start-up time and settling time of the LTC6900 with

switch S1 open (or closed) is described by t

START

shown

above. Once the LTC6900 starts and settles, and switch S1

closes (or opens), the LTC6900 will settle to its new output

frequency within approximately 70µs.

Jitter

The Peak-to-Peak Jitter vs Output Frequency graph, in the

Typical Performance Characteristics section, shows the

typical clock jitter as a function of oscillator frequency and

power supply voltage. The capacitance from the SET pin,

(Pin 3), to ground must be less than 10pF. If this requirement is not met, the jitter will increase.

8

0.15

R

= 63.2k

SET

PIN 4 = FLOATING (÷10)

0.10

0.05

0

FREQUENCY DEVIATION (%)

–0.05

2.5

3.0 3.5 4.0 4.5

SUPPLY VOLTAGE (V)

Figure 5. Supply Sensitivity

25°C

–40°C

85°C

5.0 5.5

6900 F05

70

60

50

40

30

20

FREQUENCY ERROR (%)

10

–10

63.2k

0

20k

200 400 800

0

TIME AFTER POWER APPLIED (µs)

Figure 6. Start-Up Time

400k

600

TA = 25°C

+

= 5V

V

6900 F06

1000

6900f

Page 9

WUUU

APPLICATIO S I FOR ATIO

LTC6900

S1

R

SET1

R

SET2

3V OR 5V

1

2

3

+

V

LTC6900

GND

SET

OUT

DIV

5

V

÷100

4

÷1

Figure 7

+

÷10

6900 F07

f

= 10MHz •

OSC

OR

f

= 10MHz •

OSC

20k

()

N • R

SET1

20k

()

N • R

//R

SET1

SET2

A Ground Referenced Voltage Controlled Oscillator

The LTC6900 output frequency can also be programmed

by steering current in or out of the SET pin, as conceptually

shown in Figure 8. This technique can degrade accuracy as

the ratio of (V+ – V

dependent of the value of R

SET

) / I

is no longer uniquely

RES

, as shown in the LTC6900

SET

Block Diagram. This loss of accuracy will become noticeable when the magnitude of I

is comparable to I

PROG

RES

.

The frequency variation of the LTC6900 is still monotonic.

Figure 9 shows how to implement the concept shown in

Figure 8 by connecting a second resistor, RIN, between the

SET pin and a ground referenced voltage source, VIN.

For a given power supply voltage in Figure 9, the output

frequency of the LTC6900 is a function of VIN, RIN, R

and (V+ – V

f

OSC

()

+

1

) = V

SET

MHz

10 20

=

••

N

+

−

VV

IN

•

V

RES

:

RES

k

RR

IN SET

1

R

1

+

R

IN

SET

SET

(1)

When VIN = V+, the output frequency of the LTC6900

assumes the highest value and it is set by the parallel

combination of RIN and R

quency, f

V

) so the accuracy of f

SET

, is independent of the value of V

OSC

. Also note, the output fre-

SET

= (V+ –

RES

is within the data sheet limits.

OSC

When VIN is less than V+, and expecially when VIN approaches the ground potential, the oscillator frequency,

f

, assumes its lowest value and its accuracy is affected

OSC

by the change of V

RES

= (V+ – V

). At 25°C V

SET

RES

varies

by ±8%, assuming the variation of V+ is ±5%. The temperature coefficient of V

By manipulating the algebraic relation for f

is 0.02%/°C.

RES

above, a

OSC

simple algorithm can be derived to set the values of

external resistors R

and RIN, as shown in Figure 9.

SET

1. Choose the desired value of the maximum oscillator

frequency, f

age V

IN(MAX)

OSC(MAX)

≤ V+.

, occurring at maximum input volt-

2. Set the desired value of the minimum oscillator frequency, f

V

IN(MIN)

≥ 0.

3. Choose V

OSC(MIN)

RES

, occurring at minimum input voltage

= 1.1 and calculate the ratio of RIN/R

SET

from the following:

R

IN

=

R

SET

f

VV

()

IN MAX

()

++

−

V

RES

OSC MAX

−

f

OSC MIN

f

()

OSC MAX

f

OSC MIN

()

()

()

()

−

VV

()

IN MIN

−

()

(2)

−

1

1

+

V

0.1µF

R

SET

I

PR

Figure 8. Concept for Programming via Current Steering

1

+

V

LTC6900

2

GND

3

SET

I

RES

OUT

DIV

5

5V

÷100

4

÷10

OPEN

÷1

6900 F08

+

V

+

0.1µF

V

R

SET

RES

–

R

IN

+

V

IN

–

Figure 9. Implementation of Concept Shown in Figure 8

1

2

3

+

V

LTC6900

GND

SET

OUT

DIV

5

f

OSC

5V

÷100

4

÷10

OPEN

÷1

6900 F09

9

6900f

Page 10

LTC6900

WUUU

APPLICATIO S I FOR ATIO

Once RIN/R

R

SET

VVV

()

IN MAX RES

is known, calculate R

SET

MHz

10 20

=

()

••

N

f

OSC MAX

+

−

++

RES

R

R

V

k

()

1

IN

SET

from:

SET

R

IN

R

SET

(3)

Example 1:

In this example, the oscillator output frequency has small

excursions. This is useful where the frequency of a system

should be tuned around some nominal value.

Let V+ = 3V, f

f

OSC(MIN)

OSC(MAX)

= 1.5MHz for VIN = 0V. Solve for RIN/R

Equation (2), yielding RIN/R

Equation (4). RIN = 9.9R

resistor values, use R

(1%). Figure 10 shows the measured f

= 2MHz for V

= 9.9/1. R

SET

= 1.089M. For standard

SET

= 110k (1%) and RIN = 1.1M

SET

IN(MAX)

= 3V and

= 110.1k by

SET

vs VIN. The

OSC

SET

by

1.5MHz to 2MHz frequency excursion is quite limited, so

the curve of f

OSC

vs V

is linear.

IN

Example 2:

Vary the oscillator frequency by one octave per volt.

Assume f

OSC(MIN)

= 1MHz and f

OSC(MAX)

= 2MHz, when the

input voltage varies by 1V. The minimum input voltage is

half supply, that is V

IN(MIN)

= 1.5V, V

IN(MAX)

= 2.5V and

V+ = 3V.

Equation (2) yields RIN/R

yields R

= 142.8k. RIN = 1.273R

SET

standard resistor values, use R

182k (1%). Figure 11 shows the measured f

= 1.273 and Equation (3)

SET

= 181.8k. For

SET

= 143k (1%) and RIN =

SET

vs VIN. For

OSC

VIN higher than 1.5V, the VCO is quite linear; nonlinearities

occur when VIN becomes smaller than 1V, although the

VCO remains monotonic.

Maximum VCO Modulation Bandwidth

The maximum VCO modulation bandwidth is 25kHz; that

is, the LTC6900 will respond to changes in VIN at a rate up

to 25kHz. In lower frequency applications however, the

modulation frequency may need to be limited to a lower

rate to prevent an increase in output jitter. This lower limit

is the master oscillator frequency divided by 20, (f

OSC

/20).

In general, for minimum output jitter the modulation

frequency should be limited to f

/20 or 25kHz, which-

OSC

ever is less. For best performance at all frequencies, the

value for f

should be the master oscillator frequency

OSC

(N␣ = 1) when VIN is at the lowest level.

10

2.00

1.95

1.90

1.85

1.80

1.75

(MHz)

OSC

f

1.70

1.65

1.60

1.55

1.50

Figure 10. Output Frequency vs Input Voltage

0.5 1 1.5 2 2.5 3

0

RIN = 1.1M

R

= 110k

SET

+

V

= 3V

N = 1

VIN (V)

6900 F10

3000

2500

2000

(kHz)

1500

OSC

f

1000

500

0

0.5 1 1.5 2 2.5 3

0

Figure 11. Output Frequency vs Input Voltage

VIN (V)

RIN = 182k

R

= 143k

SET

+

V

= 3v

N = 1

6900 F11

6900f

Page 11

WUUU

APPLICATIO S I FOR ATIO

LTC6900

Example 3:

V+ = 3V, f

V

IN(MAX)

R

IN/RSET

OSC(MAX)

= 2.5V, V

= 8.5, R

= 5MHz, f

IN(MIN)

= 43.2k, RIN = 365k

SET

OSC(MIN)

= 0.5V

= 4MHz, N = 1

Maximum modulation bandwidth is the lesser of 25kHz or

f

OSC(MIN)

/20 (4MHz/20 = 200kHz)

Maximum VIN modulation frequency = 25kHz

Example 4:

V+ = 3V, f

V

IN(MAX)

R

IN/RSET

OSC(MAX)

= 2.5V, V

= 3.1, R

= 400kHz, f

IN(MIN)

= 59k, RIN = 182k

SET

OSC(MIN)

= 0.5V

= 200kHz, N = 10

U

PACKAGE DESCRIPTIO

S5 Package

5-Lead Plastic TSOT-23

(Reference LTC DWG # 05-08-1635)

Maximum modulation bandwidth is the lesser of 25kHz or

f

OSC(MIN)

/20 calculated at N =1 (2MHz/20 = 100kHz)

Maximum VIN modulation frequency = 25kHz

Table 2. Variation of V

RIN || R

20k 0.98V 1.03V

40k 1.03V 1.08V

80k 1.07V 1.12V

160k 1.1V 1.15V

320k 1.12V 1.17V

V

RES

Note: All of the calculations above assume V

Table 2 shows the variation of VRES against various parallel combinations of R

(VIN = V+). Calulate first with V

then recalculate the resistor values using the new value for V

(VIN = V+)V

SET

= Voltage across R

for Various Values of RIN || R

RES

, V+ = 3V V

RES

SET

= 1.1V, although V

RES

≈ 1.1V, then use Table 2 to get a better approximation of V

RES

≈ 1.1V. For completeness,

RES

.

RES

, V+ = 5V

RES

SET

IN

and R

RES

SET

,

0.62

MAX

3.85 MAX

2.62 REF

RECOMMENDED SOLDER PAD LAYOUT

PER IPC CALCULATOR

0.20 BSC

DATUM ‘A’

0.30 – 0.50 REF

NOTE:

1. DIMENSIONS ARE IN MILLIMETERS

2. DRAWING NOT TO SCALE

3. DIMENSIONS ARE INCLUSIVE OF PLATING

4. DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH AND METAL BURR

5. MOLD FLASH SHALL NOT EXCEED 0.254mm

6. JEDEC PACKAGE REFERENCE IS MO-193

0.95

REF

1.22 REF

1.4 MIN

0.09 – 0.20

(NOTE 3)

2.80 BSC

1.50 – 1.75

(NOTE 4)

1.00 MAX

PIN ONE

0.95 BSC

0.80 – 0.90

2.90 BSC

(NOTE 4)

1.90 BSC

0.30 – 0.45 TYP

5 PLCS (NOTE 3)

0.01 – 0.10

S5 TSOT-23 0302

6900f

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

11

Page 12

LTC6900

TYPICAL APPLICATIO S

THERMISTOR

U

Temperature-to-Frequency Converter

5V

C1

T

0.1µF

: YSI 44011 800 765-4974

R

T

100k

R

1

2

3

+

V

LTC6900

GND

SET

OUT

DIV

5

4

6900 TA02

f

OSC

=

10MHz

10

20k

•

R

T

Output Frequency vs Temperature

1400

1200

1000

800

600

FREQUENCY (kHz)

400

200

0

–20–100 102030405060708090

MAX

TYP

MIN

TEMPERATURE (°C)

6900 TA03

RELATED PARTS

PART NUMBER DESCRIPTION COMMENTS

LTC1799 1kHz to 30MHz ThinSOT Oscillator Identical Pinout, Higher Frequency Operation

Linear Technology Corporation

12

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 ● FAX: (408) 434-0507

●

www.linear.com

LINEAR TECHNOLOGY CORPORATION 2002

6900f

LT/TP 0902 2K • PRINTED IN USA

Loading...

Loading...