Datasheet LTC222CJ, LTC221CN, LTC221CJ, LTC222MJ, LTC222CS Datasheet (Linear Technology)

...Page 1

FEATURES

■

Micropower Operation

■

Single 5V or ±15V Supply Operation

■

Low Charge Injection

■

Low R

■

■

■

■

■

■

ON

Low Leakage

Guaranteed Break Before Make

Latch Resistant Design

TLL/CMOS Compatible

Improved Second Source for DG221/DG222

Microprocessor Bus Compatible

U

KEY SPECIFICATIO S

■

Supply Current ..................... I+ = 40µA, I– = 5µA Max

■

Charge Injection

±15V Supplies .................................±25pC Max

Single 5V Supply .................................. 2pC Typ

■

RON............................................................... 65ΩTyp

■

Signal Range ..................................................... ±15V

LTC221/LTC222

Micropower, Low Charge

Injection, Quad CMOS Analog

Switches with Data Latches

U

DESCRIPTIO

The LTC®221 and LTC222 are micropower, quad CMOS

analog switches which typically dissipate only 250µW

from ±15V supplies and 40µW from a single 5V supply.

Onboard latches allow the LTC221 and LTC222 to interface directly to most microprocessor buses. The switches

have 65Ω typical on resistance and a very high off resistance. A break before make characteristic is inherent in

these switches to prevent the shorting of two channels.

The signal range is ±15V with a supply voltage of ±15V and

0V to 5V with a single 5V supply. The switches have special

charge compensation circuitry which greatly reduces

charge injection to a maximum of ±25pC (±15V supplies).

The LTC221 and LTC222 are designed for applications

such as microprocessor controlled programmable gain

amplifiers, automatic test equipment, communication

systems, and data acquisition systems. The LTC221 is

normally closed and the LTC222 is normally open as

shown in the Logic Table.

, LTC and LT are registered trademarks of Linear Technology Corporation.

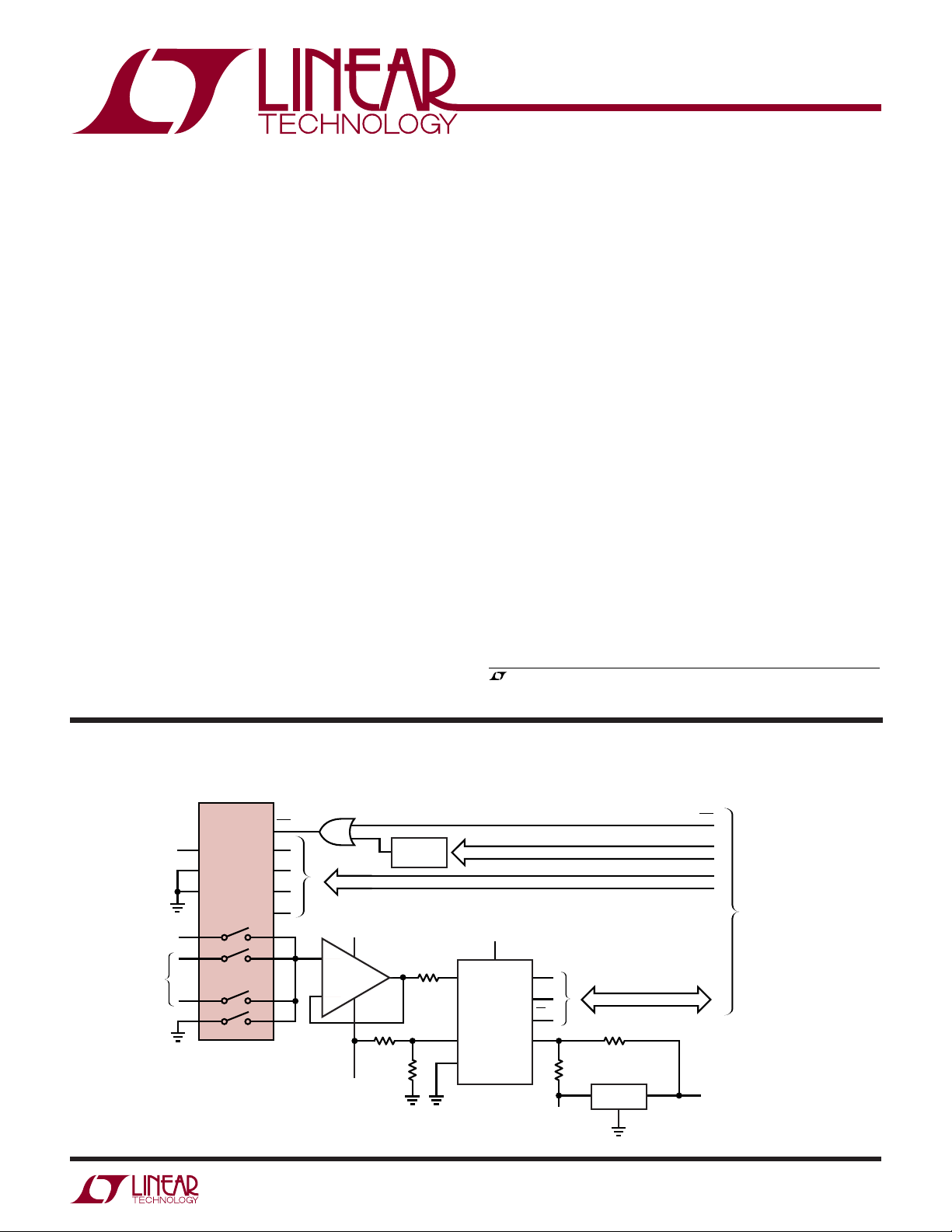

TYPICAL APPLICATIO

V

OV TO 5V

LTC221/LTC222

+

V

5V

GND IN3

–

V

V

FS

IN

WR

IN4

IN2

IN1

D1S1

D2S2

D3S3

D4S4

U

Two-Channel, 12-Bit, Self Calibrating Data Acquisition System

LOGIC

DECODER

DATA BUS B0 – B3

15V

+

LT1 006

–

–15V

10k

150k 100k

120Ω

–IN

GND

5V

LTC1292

IN

12-BIT

ADC

R1

ADDRESS BUS

CLK

D

OUT

CS

V

REF

270Ω

V

FS

SERIAL PORT

LT1027

WR

15V

LTC221/222 • TA01

TO MICROPROCESSOR

e.g. TMS320C25

2212fa

1

Page 2

LTC221/LTC222

WWWU

ABSOLUTE AXI U RATI GS

(Note 1)

Voltages Referenced to V

+

V

...........................................................................................

GND..................................................................... 25V

Digital Inputs, S, D (Note 2) .......... –2V to (V+ 2V) or

Digital Inputs, S, D (N2020mA, Whichever Occurs First

Current

Any Input Except S or D ................................... 30mA

Continuous S or D ............................................ 20mA

Peak S or D

(Pulsed at 1 ms, 10% Duty Cycle Max) ......... 70mA

ESD Susceptibility (Note 3) ......................................4kV

Power Dissipation (Plastic) ............................... 500mW

Power Dissipation (Ceramic) ............................. 900mW

Operating Temperature Range

LTC221C/LTC222C .................................. 0°C to 70°C

LTC221M/LTC222M (OBSOLETE).......– 55°C to 125°C

Storage Temperature Range ................. –65°C to 150°C

Lead Temperature (Soldering, 10 sec).................. 300°C

–

44V

UU

W

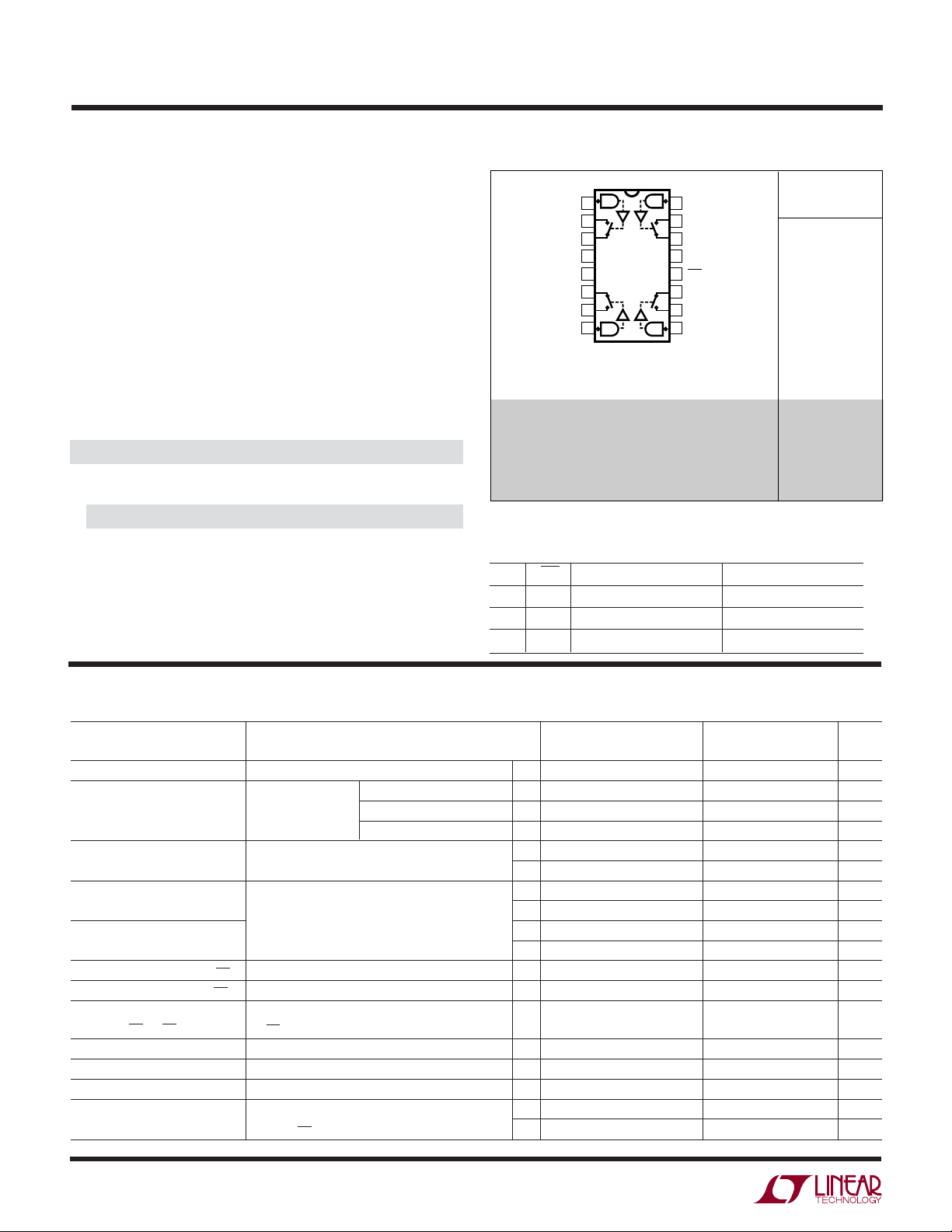

PACKAGE/ORDER I FOR ATIO

TOP VIEW

IN1

D1

S1

V

GND

S4

D4

IN4

N PACKAGE

16-LEAD PDIP

= 110°C, θJA = 120°C/W

J

MAX

1

2

3

–

4

5

6

7

8

J PACKAGE

16-LEAD CERDIP

16

IN2

15

D2

14

S2

+

13

V

12

WR

11

S3

10

D3

9

IN3

S PACKAGE

16-LEAD PLASTIC SO

= 110°C, θJA = 130°C/W

J

MAX

OBSOLETE PACKAGE

Consider the N or S Package for Alternate Source

Consult LTC Marketing for parts specified with wider operating temperature ranges.

ORDER PART

NUMBER

LTC221CN

LTC221CS

LTC222CN

LTC222CS

LTC221MJ

LTC221CJ

LTC222MJ

LTC222CJ

LOGIC TABLE

INX WR LTC221 LTC222

00 On Off

10 Off On

X1Maintain Previous State Maintain Previous State

U

DIGITAL A D DC ELECTRICAL CHARACTERISTICS

over full operating temperature range, otherwise specifications are at TA = 25°C. V+ = ±15V, V– = –15V, GND = 0V, unless noted.

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

Analog Signal Range

R

ON

Off Input Leakage IS (OFF) VD = 14V, VS = ±14V 0.01 ±1 0.01 ±5nA

Off Output Leakage ID (0FF) VIN = 2.4V, LTC221 0.01 ±1 0.01 ±5nA

On Channel Leakage lD (ON) VD = VS = ±14V, VIN = 2.4V, LTC222 0.02 ±1 0.02 ±5nA

Input High Voltage V

Input Low Voltage V

Input High or Low Current VIN = 15V, 0V

I

, I

, I

INH

INL

WRH, IWRL

CS (OFF) 55pF

CD (OFF) 12 12 pF

CD, CS (ON) 30 30 pF

+

I

INH

INL

, V

, V

VS = ±10V T

ID = 1mA 25°C65906590Ω

VIN = 0.8V, LTC222

VIN = 0.8V, LTC221

WRH

WRL

VWR = 15V, 0V

All Channels On or Off 16 40 16 40 µA

VIN = VWR = 0V or 4.0V

T

MIN

MAX

●

●

●

●

●

2.4 2.4 V

●

●

●

The ● denotes the specifications which apply

LTC221M/LTC222M LTC221C/LTC222C

±15 ±15 V

90 90 Ω

135 135 Ω

±100 ±100 nA

±100 ±100 nA

±200 ±200 nA

0.8 0.8 V

±1 ±1 µA

60 60 µA

2212fa

2

Page 3

LTC221/LTC222

U

DIGITAL A D DC ELECTRICAL CHARACTERISTICS

over full operating temperature range, otherwise specifications are at T

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

–

I

= 25°C. V+ = ±15V, V– = –15V, GND = 0V, unless noted.

A

LTC221M/LTC222M LTC221C/LTC222C

0.1 5 0.1 5 µA

●

The ● denotes the specifications which apply

10 10

AC ELECTRICAL CHARACTERISTICS

V+ = 15V, V– = –15V, GND = 0V, unless otherwise noted.

LTC221M/LTC222M LTC221C/LTC222C

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

t

ON

t

OFF

t

OPEN

Off Isolation VS = 2Vp-p, RL = 1kΩ 75 75 dB

Crosstalk f = 100kHz 90 90

Charge Injection O

Total Harmonic Distortion THD VS = 2Vp-p, RL = 10kΩ 0.01 0.01 %

tON, WR VS = 2V, RL = 1kΩ, CL = 35pF 270 400 270 400 ns

t

, WR 160 300 160 300

OFF

INJ

VS = 2V, RL = 1kΩ, CL = 35pF 290 400 290 400 ns

210 300 210 300

20 85 20 85 ns

R

= 0Ω, CL = 1000pF, V

GEN

= 0 5 ±25 8 ±25 pC

GEN

U

DIGITAL A D DC ELECTRICAL CHARACTERISTICS

over full operating temperature range, otherwise specifications are at TA = 25°C. V+ = 5V, V– = GND = 0V, unless noted.

LTC221M/LTC222M LTC221C/LTC222C

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

Analog Signal Range

R

ON

Off Input Leakage IS (OFF) VD = 4V, 1V; VS = 1V, 4V 0.01 ±1 0.01 ± 5nA

Off Output Leakage ID (0FF) 0.01 ±1 0.01 ±5nA

On Channel Leakage lD (ON) VD = VS = 1V, 4V 0.01 ±1 0.01 ± 5nA

Input High Voltage V

Input Low Voltage V

Input High or Low Current VIN = 5V, 0V

I

, I

, I

INH

INL

WRH, IWRL

CS(OFF) 5 5 pF

CD (OFF) 12 12 pF

CD, CS (ON) 30 30 pF

+

I

INH

INL

, V

, V

WRL

VS = 1.5V, 3V T

ID = 0.25mA 25°C 280 450 280 520 Ω

(Note 4)

(Note 4)

WRH

VWR = 5V, 0V

All Channels On or Off 8 20 8 20 µA

VIN = VWR = 0V or 4.0V

T

MIN

MAX

●

0505 V

●

●

●

●

2.4 2.4 V

●

●

●

The ● denotes the specifications which apply

450 520 Ω

650 650 Ω

±100 ±100 nA

±100 ±100 nA

±200 ±200 nA

0.8 0.8 V

±1 ±1 µA

30 30 µA

2212fa

3

Page 4

LTC221/LTC222

AC ELECTRICAL CHARACTERISTICS

V+ = 5V, V– = GND = 0V, unless otherwise noted.

LTC221M/LTC222M LTC221C/LTC222C

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

t

ON

t

OFF

t

OPEN

Off Isolation VS = 2V

VS = 2V, RL = 1kΩ, CL = 35pF 450 600 450 600 ns

190 300 190 300 ns

100 250 100 250 ns

, RL = 1kΩ 75 75 dB

P-P

Crosstalk f = 100kHz 90 90 dB

Charge Injection O

INJ

Total Harmonic Distortion THD VS = 2V

R

= 0Ω, CL = 1000pF, V

GEN

, RL = 10kΩ 0.01 0.01 %

P-P

= 2.5V 2 2 pC

GEN

tON, WR VS = 2V, RL = 1kΩ, CL = 35pF 430 600 430 600 ns

t

, WR 160 300 160 300 ns

OFF

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: Signals on S, D, or IN exceeding V

+

or V– will be clamped by

internal diodes. Limit forward diode current to maximum current rating.

Note 3: In-circuit ESD on the switch pins (S or D) exceeds 4kV (see test

circuit).

Note 4: Leakage current with a 5V supply is guaranteed by correlation with

the ±15V leakage current.

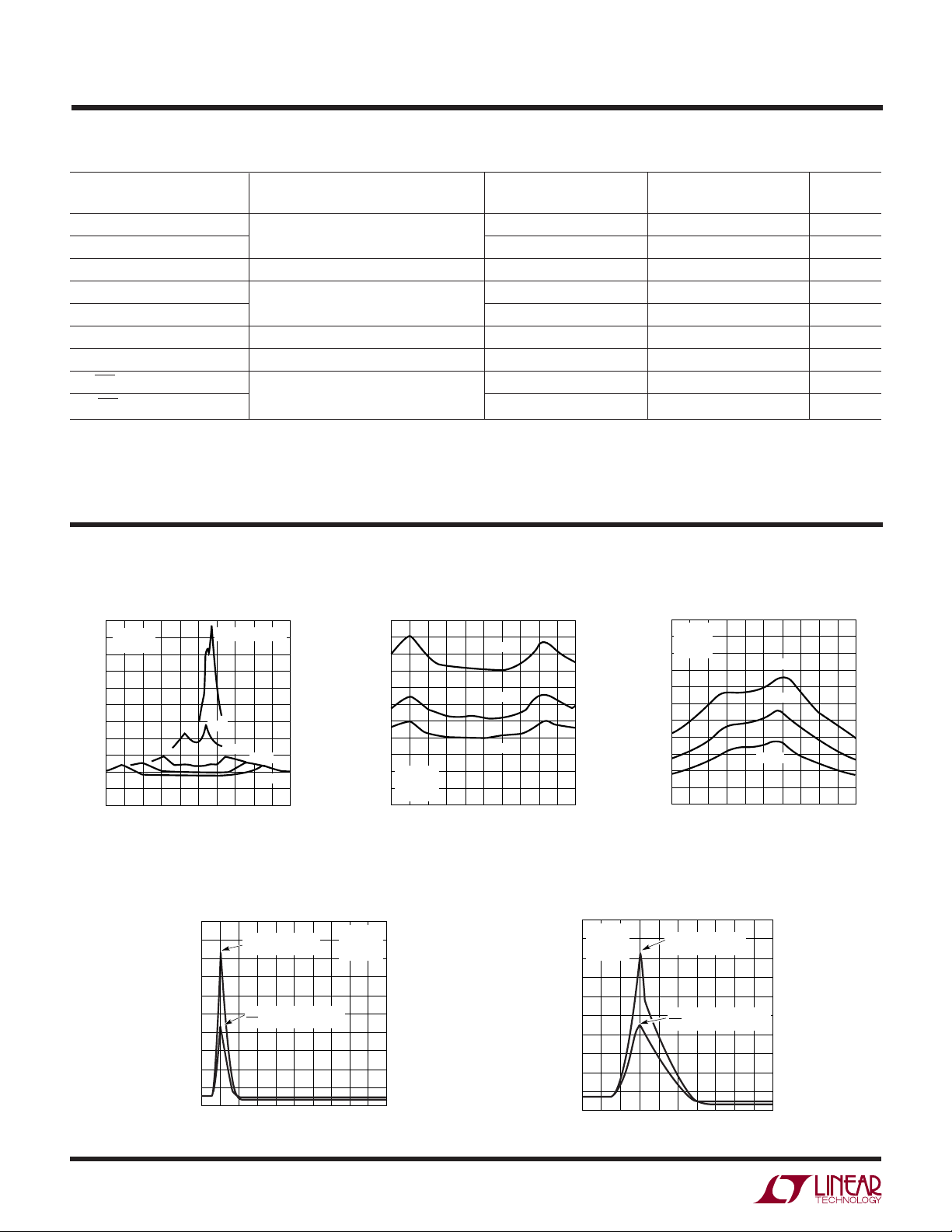

UW

TYPICAL PERFOR A CE CHARACTERISTICS

RON vs VS Over Supply Voltage

TA = 25°C

250

= 1mA

I

D

200

150

(Ω)

ON

R

100

50

0

–8

–16

–12–20 16

V

SUPPLY

±5V

±10V

–4

0

4

VS (V)

Positive Supply Current vs

Logic Input Voltage

250

200

150

(µA)

+

I

100

= 5V, OV

±15V

±20V

8

12

20

LTC221/222 • TPC01

ALL LOGIC INPUTS

TIED TOGETHER

ALL I

TIED TOGETHER

NX

WR TIED TO GROUND

(Ω)

ON

R

V+ = 15V

–

= –15V

V

= 25°C

T

A

RON vs VS Over Temperature RON vs VS Over Temperature

V+ = 5V

–

100

80

60

40

20

V+ = 15V

–

= –15V

V

= 1mA

I

D

0

–6

–12

–3

–9–15 12

0

VS (V)

125°C

25°C

–55°C

3

6

9

LTC221/222 • TPC02

15

500

= 0V

V

= 1mA

I

D

400

300

(Ω)

ON

R

200

100

0

10

2

125°C

25°C

–55°C

3

VS (V)

Positive Supply Current vs

Logic Input Voltage

250

V+ = 5V

–

= 0V

V

= 25°C

T

A

200

150

(µA)

+

I

100

ALL LOGIC INPUTS

TIED TOGETHER

ALL I

TIED TOGETHER

NX

WR TIED TO GROUND

4

LTC221/222 • TPC03

5

4

50

0

3

0

6

VIN (V)

9

12

LTC221/222 • TPC04

15

50

0

1

0

2

VIN (V)

3

4

LTC221/222 • TPC05

5

2212fa

Page 5

WUUU

LTC221/222 • AI06

V

S1

V

+

V

–

C

OIRR = 20 LOG

C = 0.001µF//0.1µF

CHIP CAPACITORS

SIGNAL

GENERATOR

C

NC

50Ω

15V

–15V

V

D2

V

S2

V

D1

V

L

GND

V

IN

V

IN

IN2IN1

V

S1

V

D2

R

L

1k

V

S

= 2Vp-p

f = 100kHz

CHAN A

ANALYZER

CHAN B

APPLICATIO S I FOR ATIO

Switching Time Test Circuit

LTC221/LTC222

Switch output waveform shown for VS = constant with

logic input waveform as shown. Note that V

or (–) as per switching time test circuit. V

50%

50%

V

t

ON

SX

LOGIC "1" = SW ON

LOGIC "0" = SW ON

0.9 0.9

O

DX

INX

LTC222

LOGIC INPUT

< 20ns

t

r

< 20ns

t

r

LTC221

LOGIC INPUT

< 20ns

t

r

t

< 20ns

r

SWITCH

INPUT

SWITCH

OUTPUT

3V

OV

3V

OV

V

S

OV

R

GEN

V

GEN

may be (+)

S

is the steady

O

Switching Time Test Circuit

V

O

t

OFF

LTC221/222 • AI01

Charge Injection Test Circuit

V

O

CL = 1000pF

state output switch on. Feedthrough via gate capacitance

may result in spikes at leading and trailing edge of output

waveform.

SWITCH

INPUT

= 2V

V

S

LOGIC

INPUT

IN1

S1

∆V

O

V

O

D1

R

1k

(REPEAT TEST FOR IN2, IN3 AND IN4)

SWITCH

OUTPUT

V

O

C

L

L

35pF

VO = V

S

RL+ R

LTC221/222 • AI02

R

L

DS(ON)

OIRR-Off Isolation Test Circuit

SIGNAL

GENERATOR

V

= 2V

S

f = 100kHz

CHAN A

ANALYZER

CHAN B

C = 0.001µF//0.1µF

CHIP CAPACITORS

P-P

R

L

1k

OIRR = 20 LOG

LTC221/222 • AI03

OV

OV

3V

ON

ON

3V

LTC221 INX

LTC222 INX

∆VO IS THE MEASURED VOLTAGE ERROR DUE TO CHARGE INJECTION.

THE ERROR VOLTAGE IN COULOMBS IS ∆Q = V

OFF

OFF

• ∆VO

L

ON

ON

LTC221/222 • AI04

CCRR-Channel to Channel Crosstalk Test Circuit

C

15V

+

V

V

S

INX

V

D

GND

V

S

V

D

–15V

–

V

C

LTC221/222 • AI05

V

IN

2212fa

5

Page 6

LTC221/LTC222

WUUU

APPLICATIO S I FOR ATIO

ANY SOURCE OR DRAIN PIN

In-Circuit ESD Test Circuit

WR

LTC221 IN

LTC222 IN

3V

0V

3V

0V

3V

0V

V

S

V

O

0V

LOGIC INPUT

< 20ns

t

r

< 20ns

t

r

S OR D

LTC221/

LTC 222

GND

V

V

+

–

0.1µF

LTC221/222 • TA07

15V

0.1µF

–15V

POWER APPLIED

OR OPEN CIRCUT

ESD TESTER

1.5k

±4kV

100pF

PER MIL-STD-883C

METHOD 3015.2

WR Switching Time Test Circuit

50%

V

0.9 0.9V

O

WR

t

ON

t

OFF

50%

O

WR

LTC221/222 • AI08

LOGIC

INPUT

SWITCH

INPUT

= 2V

V

S

LOGIC

INPUT

S1

IN1

GND

OV

WR

VO = V

S

RL+ r

15V

V

V

–15V

R

L

DS(ON)

+

–

D1

R

L

1k

(REPEAT TEST FOR

IN2, IN3 AND IN4)

LTC221/222 • AI09

SWITCH

OUTPUT

C

L

35pF

V

O

LTC221 IN

LTC222 IN

6

WR

OV

OV

OV

WR Setup Conditions

3V

3V

3V

1.5V 1.5V

t

WW

t

DW

t

WD

0.8V0.8V

2.4V2.4V

LTC221/222 • AI10

t

t

t

WW

DW

WD

WR/Input Minimum Timing Requirements

PARAMETER MIN LIMIT UNITS

Write Pulse Width 230 ns

Data Valid to Write 180 ns

Data Valid After Write 30 ns

2212fa

Page 7

WUUU

APPLICATIO S I FOR ATIO

Auto Ranging an 8-Channel, 10-Bit A/D Converter

LTC221/LTC222

V

OV – 5V

CH0

CH1

CH2

IN

CH3

CH4

LTC1090

CH5

CH6

CH7

COM

DGND AGND

V

CC

ACLK

SCLK

D

IN

D

OUT

CS

REF

REF

–

V

15V

GND

SERIAL PORT

D1S1

20kΩ

D2S2

10kΩ

D3S3

4.99kΩ

D4S4

2.49kΩ

IN1

IN2

IN3

IN4

WR

5V

LT1027

15V

DATA BUS B0 – B3

LOGIC

DECODER

WR

ADDRESS BUS

LTC221/222 • AI11

TO

MICROCONTROLLER

e.g. HD64180

5V

15V

+

–

+

LT1006

LTC221/

LTC222

–

–

V

2212fa

7

Page 8

LTC221/LTC222

WUUU

APPLICATIO S I FOR ATIO

8-Channel, 14-Bit A/D Converter

V

0V TO 5V

CH0

CH1

CH2

IN

CH3

CH4

LTC1090

CH5

CH6

CH7

COM

DGND AGND

15V

LTC221/

LTC 222

–

V

GND

ACLK

SCLK

D

IN

D

OUT

CS

REF

REF

–

V

D1S1

D2S2

D3S3

D4S4

IN1

IN2

IN3

IN4

WR

5V

SERIAL PORT

+

–

1kΩ

DATA BUS B0 – B3

LOGIC

DECODER

1kΩ1kΩ1kΩ

LT1027

ADDRESS BUS

15V

WR

LTC221/222 • AI12

TO

MICROCONTROLLER

e.g. TMS370

8

2212fa

Page 9

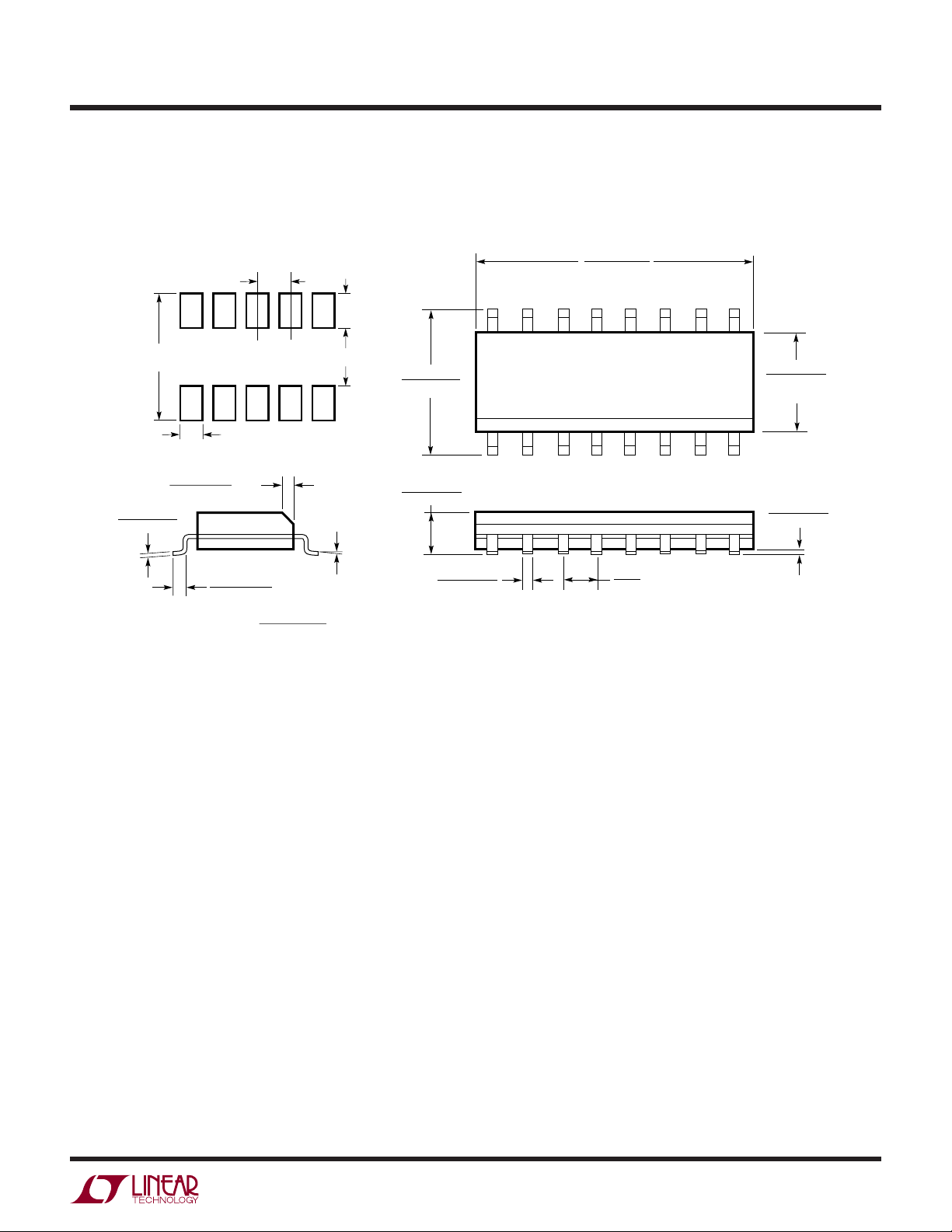

PACKAGE DESCRIPTIO

CORNER LEADS OPTION

(4 PLCS)

.023 – .045

(0.584 – 1.143)

HALF LEAD

OPTION

.045 – .065

(1.143 – 1.65)

FULL LEAD

OPTION

.300 BSC

(7.62 BSC)

U

J Package

16-Lead CERDIP (Narrow .300 Inch, Hermetic)

(Reference LTC DWG # 05-08-1110)

.840

.005

(0.127)

MIN

.025

(0.635)

RAD TYP

.015 – .060

(0.380 – 1.520)

16

1

23

(21.336)

MAX

13

4

LTC221/LTC222

10

11121415

5

6

9

.220 – .310

(5.588 – 7.874)

78

.200

(5.080)

MAX

.008 – .018

(0.203 – 0.457)

NOTE: LEAD DIMENSIONS APPLY TO SOLDER DIP/PLATE

OR TIN PLATE LEADS

0° – 15°

OBSOLETE PACKAGE

.125

(3.175)

MIN

.045 – .065

(1.143 – 1.651)

.014 – .026

(0.360 – 0.660)

.100

(2.54)

BSC

J16 0801

2212fa

9

Page 10

LTC221/LTC222

PACKAGE DESCRIPTIO

U

N Package

16-Lead PDIP (Narrow .300 Inch)

(Reference LTC DWG # 05-08-1510)

15

16

.255 ± .015*

(6.477 ± 0.381)

2

1

.770*

(19.558)

MAX

14

3

12

13

4

11

6

5

910

8

7

.300 – .325

(7.620 – 8.255)

.009 – .015

(0.229 – 0.381)

+.035

.325

–.015

+0.889

8.255

()

–0.381

NOTE:

1. DIMENSIONS ARE

*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 INCH (0.254mm)

INCHES

MILLIMETERS

.130 ± .005

(3.302 ± 0.127)

.020

(0.508)

MIN

.125

(3.175)

MIN

.100

(2.54)

BSC

.045 – .065

(1.143 – 1.651)

.065

(1.651)

TYP

.018 ± .003

(0.457 ± 0.076)

N16 0502

10

2212fa

Page 11

PACKAGE DESCRIPTIO

.050 BSC

N

U

S Package

16-Lead Plastic Small Outline (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1610)

.386 – .394

.045 ±.005

16

15

(9.804 – 10.008)

13

14

NOTE 3

LTC221/LTC222

12

11

10

9

.245

MIN

.030 ±.005

TYP

.008 – .010

(0.203 – 0.254)

.160 ±.005

123 N/2

RECOMMENDED SOLDER PAD LAYOUT

.010 – .020

(0.254 – 0.508)

NOTE:

1. DIMENSIONS IN

2. DRAWING NOT TO SCALE

3. THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .006" (0.15mm)

×

°

45

.016 – .050

(0.406 – 1.270)

(MILLIMETERS)

0° – 8° TYP

INCHES

.228 – .244

(5.791 – 6.197)

.053 – .069

(1.346 – 1.752)

.014 – .019

(0.355 – 0.483)

TYP

N

.150 – .157

(3.810 – 3.988)

NOTE 3

N/2

4

5

.050

(1.270)

BSC

3

2

1

7

6

8

.004 – .010

(0.101 – 0.254)

S16 0502

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

2212fa

11

Page 12

LTC221/LTC222

RELATED PARTS

PART NUMBER DESCRIPTION COMMENTS

LTC201/LTC202/LTC203 Micropower, Low Charge Injection, Quad CMOS Analog Switches DG201/DG202 Compatible

LTC1380/LTC1393 8-Channel/4-Channel Analog Multiplexer with SMBus Interface 3V to ±15V, 8 Single Ended/4 Differential Inputs

LTC1390/LTC1391 8-Channel, Analog Multiplexer with Serial Interface 3V to ±15V Operation

12

Linear Technology Corporation

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 ● FAX: (408) 434-0507

●

www.linear.com

2212fa

LW/TP 1002 1K REV A • PRINTED IN USA

LINEAR TE CHNO LO G Y CORPOR AT IO N 1991

Loading...

Loading...