Page 1

FEATURES

■

Allows Safe Board Insertion and Removal from a

Live PCI Slot

■

Works on either a Motherboard (LTC1643H) or

CompactPCITM Card (LTC1643L/LTC1643L-1)

■

Controls –12V, 3.3V, 5V, 12V Supplies

■

Programmable Foldback Current Limit with

Circuit Breaker

■

User-Programmable Supply Voltage Power-Up Rate

■

High Side Drive for External N-Channels

■

–12V and 12V On-Chip Switches

■

Fault and Power-Good Outputs

U

APPLICATIO S

■

PCI-Based Servers

■

CompactPCI Compliant Boards

, LTC and LT are registered trademarks of Linear Technology Corporation.

Hot Swap is a trademark of Linear Technology Corporation.

CompactPCI is a trademark of PCI Industrial Computer Manufacturing Group.

LTC1643L/LTC1643L-1/LTC1643H

PCI-Bus Hot Swap

Controller

U

DESCRIPTIO

The LTC®1643 is a Hot SwapTM controller that allows a board

to be safely inserted and removed from a live PCI-Bus slot.

Two external N-channel transistors control the 3.3V and 5V

supplies while on-chip switches control the –12V and 12V

supplies. All supply voltages can be ramped up at a programmable rate. An electronic circuit breaker protects all four

supplies against overcurrent faults. The foldback current limit

feature limits current spikes and power dissipation when

shorts occur and allows boards with large capacitances to be

powered up without tripping the circuit breaker. The PWRGD

output indicates when all of the supply voltages are within

tolerance and the FAULT output indicates an overcurrent

condition. The ON(LTC1643H)/ON (LTC1643L/LTC1643L-1)

pin is used to cycle the board power or reset the circuit

breaker. The LTC1643L-1 has the ±12V power good comparators disabled.

The LTC1643 is available in a 16-pin narrow SSOP package.

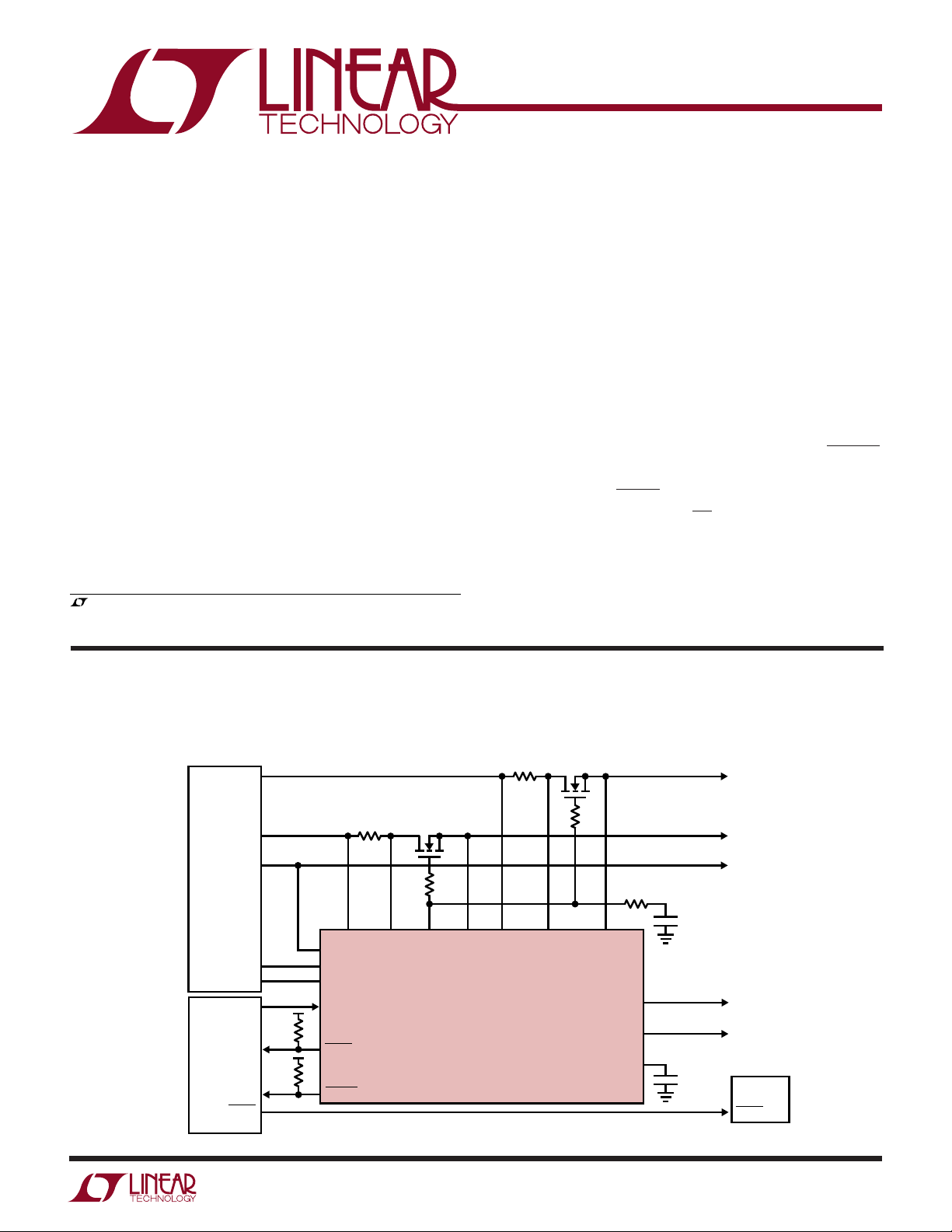

TYPICAL APPLICATION

SYSTEM

POWER

SUPPLY

8

1

2

5

R3

PCI

POWER

SYSTEM

CONTROLLER

RESET

10k

10k

6

R4

7

U

0.005ΩQ2IRF7413

3V

IN

GND

12V

IN

V

EEIN

ON

FAULT

PWRGD

Hot Swappable PCI Supply

R2

R5

10Ω

109

11 3 13 12 14

3V

SENSE

GATE

3V

OUT

LTC1643H

5V

R1

0.007Ω

IN

5V

SENSE

Q1

IRF7413

R6

10Ω

5V

5A

3.3V

7.6A

R7

100Ω

C1

5V

OUT

12V

OUT

V

EEOUT

TIMER

0.047µF

16

15

4

C2

0.1µF

GND

12V

500mA

–12V

100mA

LOGIC

RESET

1643 TA01

1

Page 2

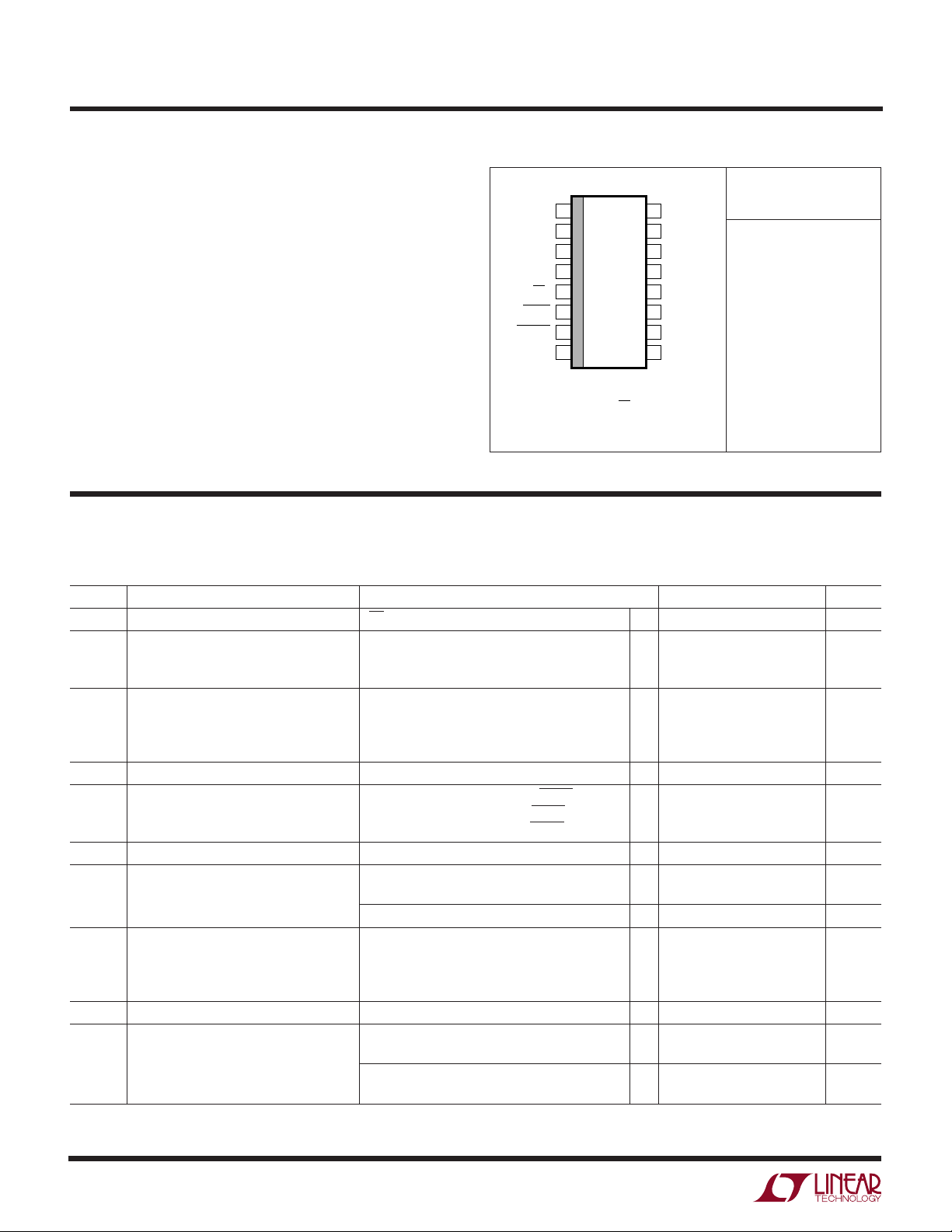

LTC1643L/LTC1643L-1/LTC1643H

WW

W

ABSOLUTE MAXIMUM RATINGS

U

U

W

PACKAGE/ORDER INFORMATION

(Note 1)

Supply Voltages

12VIN................................................................ 13.2V

V

.............................................................. –13.2V

EEIN

Input Voltage (Pin 5) ................ –0.3V to (12VIN + 0.3V)

Output Voltages (Pins 6, 7) ...... –0.3V to (12VIN + 0.3V)

Analog Voltages

(Pins 3, 4, 9, 10 to 14) ........ –0.3V to (12VIN + 0.3V)

V

12V

............................................ –13.2V to + 0.3V

EEOUT

.............................................. –0.3V to 13.2V

OUT

Operating Temperature Range

Commercial .............................................0°C to 70°C

Industrial ........................................... –40°C to 85°C

12V

V

EEIN

3V

OUT

TIMER

ON/ON*

FAULT

PWRGD

GND

16-LEAD NARROW PLASTIC SSOP

* ON FOR LTC1643H, ON FOR LTC1643L

TOP VIEW

1

IN

2

3

4

5

6

7

8

GN PACKAGE

T

= 150°C, θJA = 135°C/ W

JMAX

ORDER PART

12V

16

OUT

15

V

EEOUT

14

5V

OUT

13

5V

IN

12

5V

SENSE

11

GATE

10

3V

SENSE

9

3V

IN

NUMBER

LTC1643HCGN

LTC1643LCGN

LTC1643L-1CGN

LTC1643HIGN

LTC1643LIGN

Storage Temperature Range ................. –65°C to 150°C

Lead Temperature (Soldering, 10 sec).................. 300°C

Consult factory for Military grade parts.

DC ELECTRICAL CHARACTERISTICS

The ● denotes specifications which apply over the full operating temperature range, otherwise specifications are TA = 25°C.

V

= 12V, VEE = –12V, V

12VIN

= 3.3V, V

3VIN

= 5V. (Note 2)

5VIN

U

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

I

DD

V

LKO

V

FB

t

CB

I

CP

∆V

V

DROP

I

CL

T

TS

V

TH

GATE

V

Supply Current ON = 3V, ON = GND ● 3.5 8 mA

12VIN

Undervoltage Lockout 12V

3V

5V

IN

IN

IN

Foldback Current Limit Voltage VFB = (V

= (V

V

FB

V

= (V

FB

= (V

V

FB

5VIN

5VIN

3VIN

3VIN

– V

– V

– V

– V

5VSENSE

5VSENSE

3VSENSE

3VSENSE

), V

), V

), V

), V

= 0V ● 4 7.5 12 mV

5VOUT

> 4V ● 40 53 65 mV

5VOUT

= 0V ● 4 7.5 12 mV

3VOUT

> 2V ● 40 53 65 mV

3VOUT

● 7 9.5 10.8 V

● 2.25 2.5 2.75 V

● 2.25 2.5 2.75 V

Circuit Breaker Trip Filter Time 14.6 µs

GATE Pin Output Current Charge Pump On, V

Charge Pump Off, V

Charge Pump Off, V

External Gate Voltage (V

Internal Switch Voltage Drop (V

(V

12VIN

12VIN

EEOUT

– V

– V

– V

GATE

12VOUT

EEIN

Current Foldback 12VIN = 12V, 12V

, 12V

12V

V

EEIN

V

EEIN

IN

= –12V, V

, V

= 12V ● 525 850 1500 mA

OUT

= –12V ● 225 450 800 mA

EEOUT

= GND, FAULT = High ● – 20 – 50 –100 µA

GATE

= 5V, FAULT = High 200 µA

GATE

= 2V, FAULT = Low ● 3 1020 mA

GATE

) 100 200 mV

), I

), I

VEEIN

OUT

EEOUT

= 500mAC Grade ● 250 600 mV

12VOUT

I Grade

● 250 750 mV

= 100mA ● 120 250 mV

= 0V ● 50 250 500 mA

= 0V ● 100 160 215 mA

Thermal Shutdown Temperature 150 °C

Power-Good Threshold Voltage V

12VOUT

LTC1643H/LTC1643L Only I Grade

V

EEOUT

LTC1643H/LTC1643L Only I Grade

C Grade ● 10.8 11.1 11.4 V

● 10.4 11.1 11.4 V

C Grade ● – 10.2 –10.5 –10.8 V

● –10.0 –10.5 –10.8 V

2

Page 3

LTC1643L/LTC1643L-1/LTC1643H

DC

ELECTRICAL CHARACTERISTICS

The ● denotes specifications which apply over the full operating temperature range, otherwise specifications are TA = 25°C.

V

= 12V, VEE = –12V, V

12VIN

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

TH

V

IL

V

IH

V

OL

I

IN

Power-Good Threshold Voltage V

Input Low Voltage ON/ON, FAULT ● 0.8 V

Input High Voltage ON/ON, FAULT ● 2V

Output Low Voltage FAULT, PWRGD, I = 3mA ● 0.4 V

ON/ON Pin Input Current ON/ON = GND ● ±0.08 ±10 µA

5V

Input Current 5V

SENSE

3V

Input Current 3V

SENSE

5VIN Input Current 5VIN = 5V ● 460 700 µA

3VIN Input Current 3VIN = 3V ● 320 600 µA

5V

Input Current 5V

OUT

3V

Input Current 3V

OUT

R

DIS

I

TIMER

V

TIMER

5V

Discharge Impedance ON = GND or ON = 3V 100 Ω

OUT

Discharge Impedance ON = GND or ON = 3V 70 Ω

3V

OUT

12V

Discharge Impedance ON = GND or ON = 3V 450 Ω

OUT

Discharge Impedance ON = GND or ON = 3V 1600 Ω

V

EEOUT

TIMER Pin Current Timer On, V

TIMER Threshold Voltage (V

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

= 3.3V, V

3VIN

= 5V.(Note 2)

5VIN

3VOUT

V

5VOUT

ON/ON= 12V

Timer Off, V

12VIN

C Grade ● 2.8 2.9 3.0 V

I Grade

● 2.75 2.9 3.0 V

C Grade ● 4.5 4.65 4.75 V

I Grade

IN

= 5V ● 50 100 µA

SENSE

= 3V ● 50 100 µA

SENSE

= 5V, ON = 3V, ON = GND ● 240 500 µA

OUT

= 3.3V, ON = 3V, ON = GND ● 220 500 µA

OUT

= GND ● –15 –22 –27 µA

TIMER

= 5V 45 mA

TIMER

– V

) ● 0.5 0.9 1.3 V

TIMER

● 4.4 4.65 4.75 V

● ±0.08 ±10 µA

Note 2: All currents into device pins are positive; all currents out of device

pins are negative. All voltages are referenced to ground unless otherwise

specified.

UW

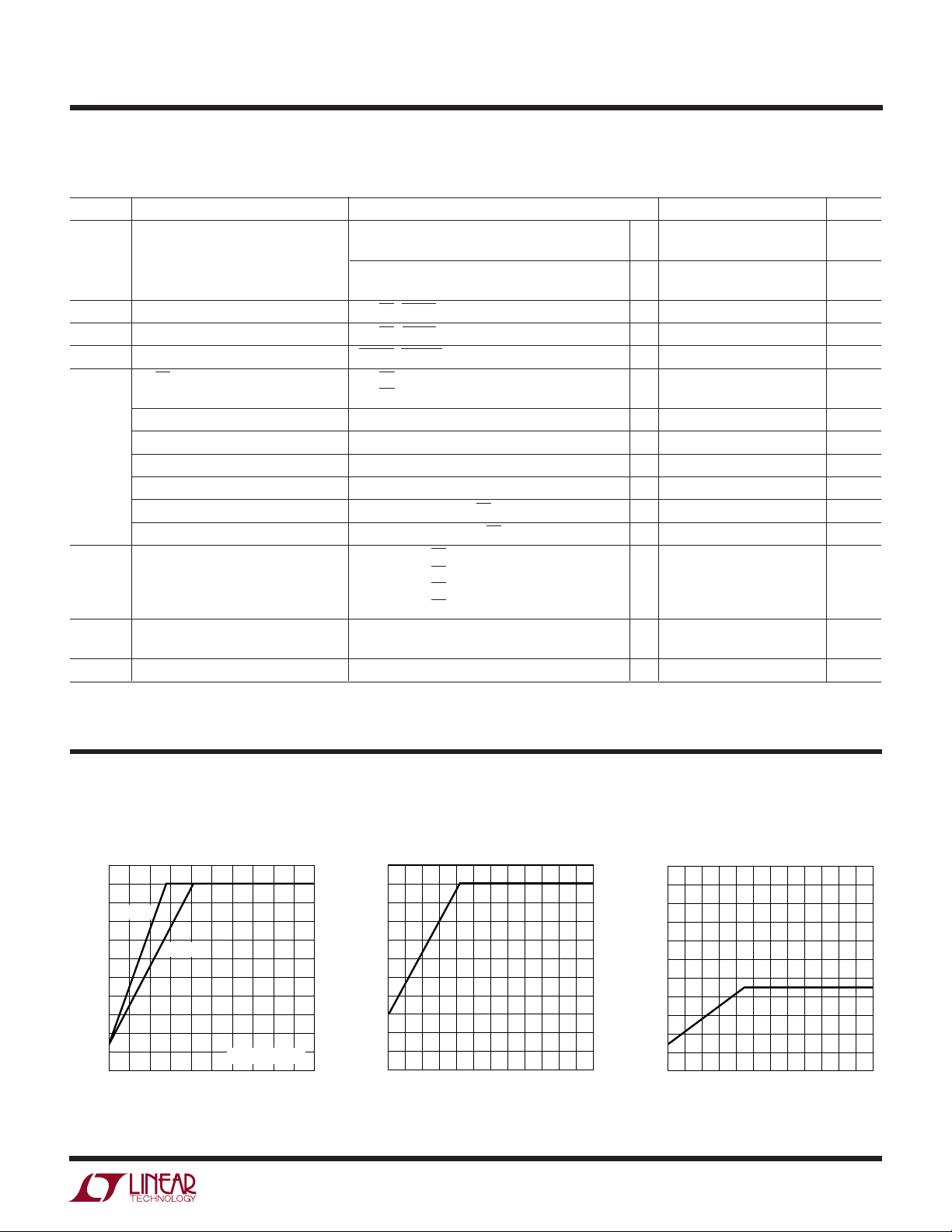

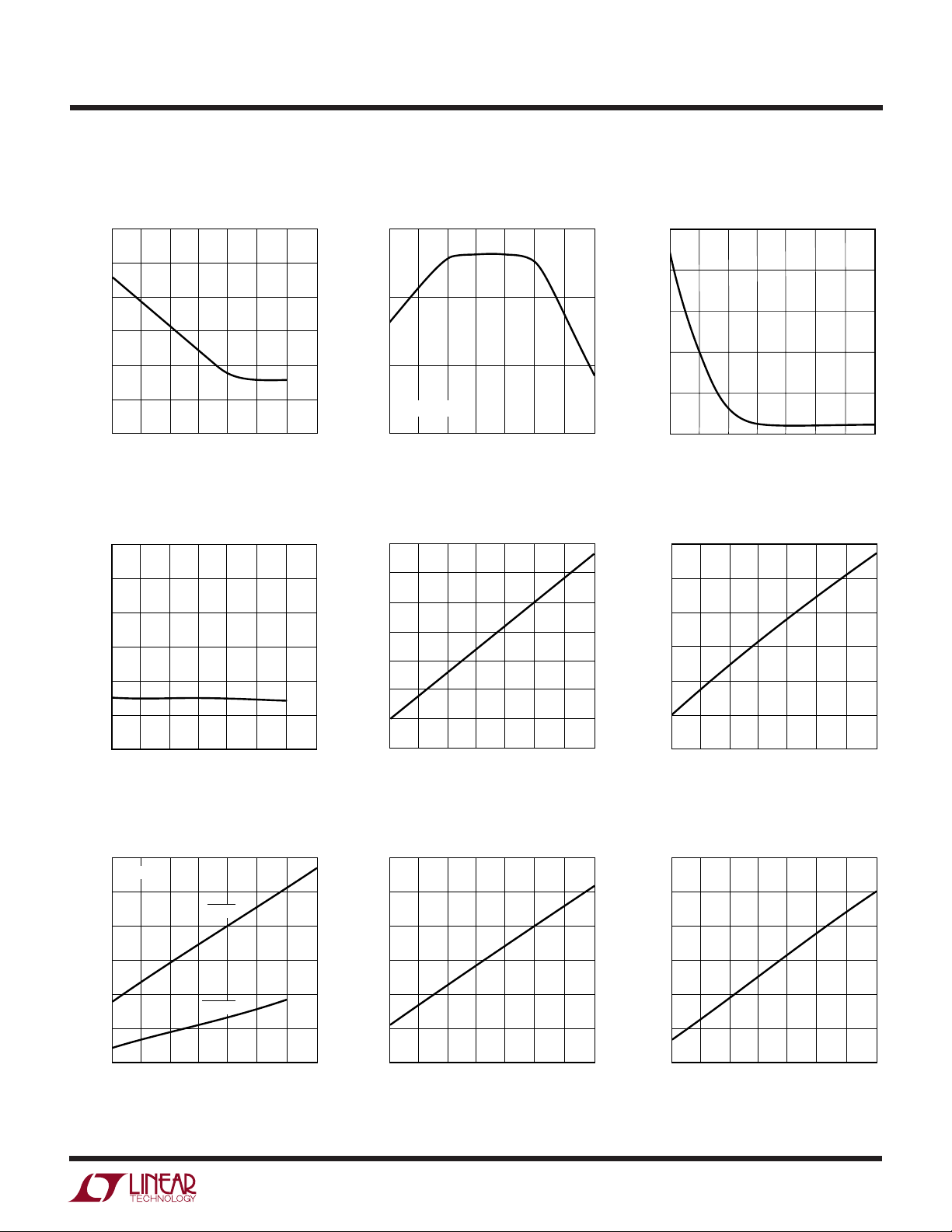

TYPICAL PERFORMANCE CHARACTERISTICS

3.3V and 5V Current

Foldback Profile

11

10

9

3V

OUT

8

7

6

5

4

OUTPUT CURRENT (A)

3

2

1

0

1

0

OUTPUT VOLTAGE (V)

5V

OUT

R

= 0.005Ω

SENSE

3

4

2

5

1643 G01

12V Current Foldback Profile –12V Current Foldback Profile

1.0

0.5

OUTPUT CURRENT (A)

0

2

0

6

4

OUTPUT VOLTAGE (V)

810

1643 G02

1.0

0.5

OUTPUT CURRENT (A)

12

0

–2

0

–6

–4

OUTPUT VOLTAGE (V)

–8 –10

–12

1643 G03

3

Page 4

LTC1643L/LTC1643L-1/LTC1643H

TEMPERATURE (°C)

–50

GATE CURRENT (µA)

90

80

70

60

50

40

0

50

75

1643 G06

–25

25

100

125

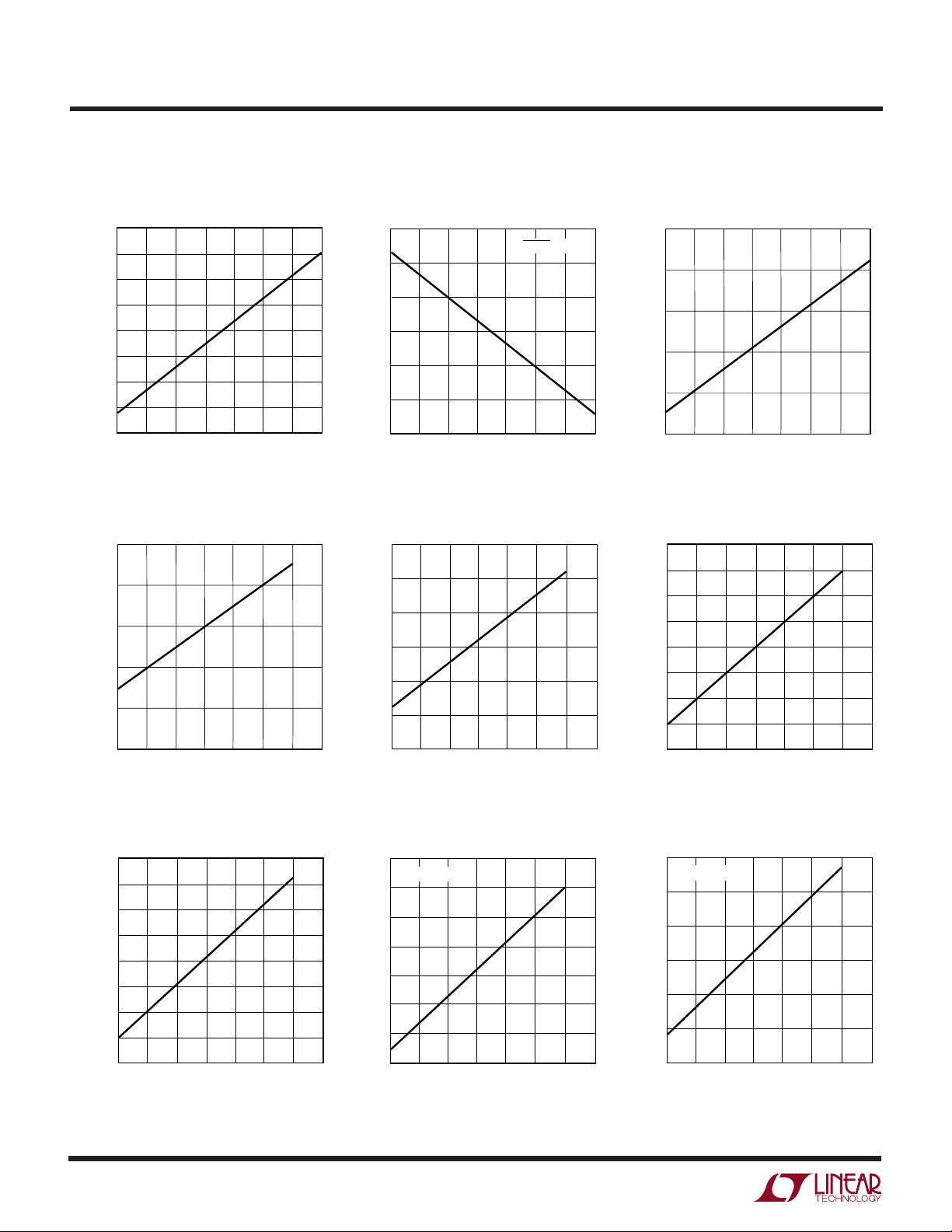

UW

TYPICAL PERFORMANCE CHARACTERISTICS

Timer Current vs Temperature

23.5

23.0

22.5

22.0

21.5

21.0

TIMER CURRENT (µA)

20.5

20.0

19.5

–50

050

–25 25 75 125

TEMPERATURE (°C)

Power Good Threshold Voltage vs

Temperature (12V

11.08

11.06

11.04

11.02

11.00

POWER GOOD THRESHOLD VOLTAGE (V)

10.98

–50

0

–25

TEMPERATURE (°C)

)

OUT

50

25

Gate Current vs Temperature

Power Good Threshold Voltage vs

Temperature (3V

2.904

2.903

2.902

2.901

2.900

2.899

2.898

2.897

POWER GOOD THRESHOLD VOLTAGE (V)

2.896

–50

050

–25 25 75 125

TEMPERATURE (°C)

OUT

)

100

1643 G09

100

1643 G04

25.0

22.5

20.0

(mA)

17.5

SINK

GATE I

15.0

12.5

10.0

Gate I

–50

vs Temperature

SINK

–25 0

TEMPERATURE (°C)

FAULT = LOW

50 100 125

25 75

1643 G05

Power Good Threshold Voltage vs

Temperature (5V

4.64

4.63

4.62

4.61

4.60

4.59

POWER GOOD THRESHOLD VOLTAGE (V)

100

125

1643 G07

75

4.58

–50

–25 0

TEMPERATURE (°C)

)

OUT

50 100 125

25 75

1643 G08

Power Good Threshold Voltage

vs Temperature (V

–10.50

–10.48

–10.46

–10.44

–10.42

–10.40

–10.38

–10.36

POWER GOOD THRESHOLD VOLTAGE (V)

–10.34

4

–50

050

–25 25 75 125

TEMPERATURE (°C)

EEOUT

)

100

1643 G10

12V Internal Switch Voltage Drop

vs Temperature

325

I

= 500mA

12VOUT

300

275

250

225

200

175

INTERNAL SWITCH VOLTAGE DROP (mV)

150

–50 25 75

–25 0

50 100 125

TEMPERATURE (°C)

LT1643 G11

VEE Internal Switch Voltage Drop

vs Temperature

180

I

= 100mA

VEEIN

160

140

120

100

80

INTERNAL SWITCH VOLTAGE DROP (mV)

60

–50

–25 0

TEMPERATURE (°C)

50 100 125

25 75

1643 G12

Page 5

LTC1643L/LTC1643L-1/LTC1643H

UW

TYPICAL PERFORMANCE CHARACTERISTICS

Circuit Breaker Trip Filter Time

vs Temperature

15.50

15.25

15.00

14.75

14.50

14.25

CIRCUIT BREAKER TRIP FILTER TIME (µs)

14.00

–50

–25 0

V

Supply Current

EEIN

TEMPERATURE (°C)

50 100 125

25 75

vs Temperature

0.90

0.89

0.88

0.87

0.86

SUPPLY CURRENT (mA)

EEIN

V

0.85

1643 G13

Timer Threshold Voltage

vs Temperature

1.0

0.9

0.8

TIMER THRESHOLD VOLTAGE (V)

V

– V

12VIN

TIMER

0.7

–50

–25 0

25 75

TEMPERATURE (°C)

5VIN Supply Current

vs Temperature

270

268

266

264

262

SUPPLY CURRENT (µA)

260

IN

5V

258

50 100 125

1643 G14

12VIN Supply Current

vs Temperature

3.72

3.70

3.68

3.66

SUPPLY CURRENT (mA)

IN

3.64

12V

3.62

–50

–25

0

TEMPERATURE (°C)

3VIN Supply Current

vs Temperature

275.0

272.5

270.0

267.5

265.0

SUPPLY CURRENT (µA)

IN

3V

262.5

50

25

75

100

125

1643 G15

0.84

–50

–25 0

VOL vs Temperature

350

I = 3mA

300

250

(mV)

200

OL

V

150

100

50

–50

–25 0

50 100 125

25 75

TEMPERATURE (°C)

FAULT

PWRGD

50 100 125

25 75

TEMPERATURE (°C)

1643 G16

1643 G19

256

–50 25 75

–25 0

TEMPERATURE (°C)

12VIN Undervoltage Lockout

vs Temperature

9.515

9.510

9.505

9.500

9.495

UNDERVOLTAGE LOCKOUT (V)

9.490

9.485

–50

–25 0

25 75

TEMPERATURE (°C)

50 100 125

LT1643 G17

50 100 125

1643 G20

260.0

–50

–25 0

25 75

TEMPERATURE (°C)

5VIN Undervoltage Lockout

vs Temperature

2.454

2.452

2.450

2.448

2.446

UNDERVOLTAGE LOCKOUT (V)

2.444

2.442

–50

–25 0

25 75

TEMPERATURE (°C)

50 100 125

1643 G18

50 100 125

1643 G21

5

Page 6

LTC1643L/LTC1643L-1/LTC1643H

TEMPERATURE (°C)

70

60

50

40

30

20

10

0

LT1643 G24

FOLDBACK CURRENT LIMIT VOLTAGE (mV)

–50 25 75

–25 0

50 100 125

3V

OUT

= 3.3V

3V

OUT

= 0V

UW

TYPICAL PERFORMANCE CHARACTERISTICS

3VIN Undervoltage Lockout

vs Temperature

2.454

2.452

2.450

2.448

2.446

UNDERVOLTAGE LOCKOUT (V)

2.444

2.442

–50

–25 0

25 75

TEMPERATURE (°C)

VEE Current Foldback

vs Temperature

600

500

400

300

200

CURRENT FOLDBACK (mA)

100

0

–50

–25 0

V

TEMPERATURE (°C)

50 100 125

= –12V

EEOUT

V

= 0V

EEOUT

50 100

25 75

1643 G21

1643 G25

5VIN Foldback Current Limit

Voltage vs Temperature

70

60

50

40

30

20

10

FOLDBACK CURRENT LIMIT VOLTAGE (mV)

0

–50 25 75

–25 0

5V

= 5V

OUT

5V

= 0V

OUT

50 100 125

TEMPERATURE (°C)

12V Current Foldback

vs Temperature

1200

12V

= 12V

1000

800

600

400

CURRENT FOLDBACK (mA)

200

0

–50

OUT

12V

OUT

–25 0

TEMPERATURE (°C)

= 0V

25 75

50 100

LT1643 G23

1643 G26

3VIN Foldback Current Limit

Voltage vs Temperature

800

700

600

500

(mV)

400

OL

V

300

200

100

VOL vs I

0

0

(25°C)

SINK

PWRGD

24 8

I

(mA)

SINK

6

FAULT

10

1643 G27

PIN FUNCTIONS

12VIN (Pin 1): 12V Supply Input. It powers all the chip’s

internal circuitry. A 0.5Ω switch is connected between

12VIN and 12V

undervoltage lockout circuit prevents the switches from

turning on while the 12VIN pin voltage is less than 9.5V

typically.

V

connected between V

current limit.

3V

output supply voltage. The PWRGD signal cannot go high

until the 3V

6

(Pin 2): –12V Supply Input. A 1.2Ω switch is

EEIN

(Pin 3): Analog Input. Used to monitor the 3.3V

OUT

OUT

pin exceeds 2.9V typically.

OUT

UUU

with a foldback current limit. An

EEIN

and V

with a fold-back

EEOUT

TIMER (Pin 4): Analog Current Fault Inhibit Timing Input.

Connect a capacitor from TIMER to GND. With the chip

turned off (ON = GND or ON = High) or the internal circuit

breaker tripped (FAULT = GND), the TIMER pin is internally

held at GND. When the chip is turned on, a 20µA pull-up

current source is connected to TIMER. Current limit faults

will be ignored until the voltage at the TIMER pin rises to

within 0.9V of 12VIN.

ON/ON (Pin 5): Digital Input.The LTC1643L/LTC1643L-1

have an active low enable, ON, and the LTC1643H has an

active high enable, ON. When the ON pin is pulled high or

Page 7

UUU

PIN FUNCTIONS

LTC1643L/LTC1643L-1/LTC1643H

the ON pin pulled low, the GATE pin is pulled high by a

50µA current source and the internal 12V and –12V

switches are turned on. When the ON pin is pulled low or

the ON pin pulled high, the GATE pin will be pulled to

ground by a 200µA current source and the 12V and –12V

switches turned off.

The ON/ON pin is also used to reset the electronic circuit

breaker. If the ON/ON pin is cycled following the trip of the

circuit breaker, the circuit breaker is reset and a normal

power-up sequence will occur.

FAULT (Pin 6): Open-Drain Digital I/O. FAULT is pulled low

when a current limit fault is detected. Current limit faults

are ignored while the voltage at the TIMER pin is less than

12VIN – 0.9V. Once the TIMER cycle is complete, FAULT

will pull low typically 14.6µs after any of the supplies go

into current limit. At the same time the GATE and TIMER

pins are pulled to GND and the 12V and –12V switches are

turned off. The chip will remain latched in the off state until

the ON/ON pin is toggled or the power is cycled.

Forcing the FAULT pin low with an external pull-down will

immediately turn off the internal switches and force the

GATE and TIMER pins to GND independent of the state of

the ON/ON pin. However, the chip is not latched into the off

state, so when the FAULT pin is released, the state of the

chip will be determined by the ON pin.

PWRGD (Pin 7): Open-Drain Digital Power-Good Output.

PWRGD remains low while V

V

≥ 4.75V and V

5VOUT

EEOUT

has the power good comparators connected to the 12V

and V

pins disabled, with only the 3V

EEOUT

12VOUT

≥ 11.4V, V

3VOUT

≥ 3V,

≤ –10.8V. The LTC1643L-1

OUT

and 5V

OUT

OUT

outputs being monitored to generate PWRGD. When one

of the supplies falls below its power-good threshold

voltage, PWRGD will go high after a 15µs deglitching time.

The switches will

not

be turned off when PWRGD goes

high.

GND (Pin 8): Chip Ground.

3VIN (Pin 9): 3.3V Supply Sense Input. An undervoltage

lockout circuit prevents the switches from turning on

when the voltage at the 3VIN pin is less than 2.5V typically.

If no 3.3V input supply is available, tie 3VIN to the 5VIN pin.

3V

(Pin 10): The 3.3V Current Limit Set Pin. With a

SENSE

sense resistor placed in the supply path between 3VIN and

3V

, the GATE pin voltage will be adjusted to maintain

SENSE

a constant voltage across the sense resistor and a constant current through the switch. A foldback feature makes

the current limit decrease as the voltage at the 3V

approaches GND. To disable the current limit, 3V

OUT

SENSE

pin

and 3VIN can be shorted together.

GATE (Pin 11): High Side Gate Drive for the External

N-Channels. Requires an external series RC network for

the current limit loop compensation and setting the minimum ramp-up rate. During power-up, the slope of the

voltage rise at the GATE is set by the 50µA current source

connected to 12VIN and the external capacitor connected

to GND or by the 3.3V or 5V current limit and the bulk

capacitance on the 3V

OUT

or 5V

suppy lines. During

OUT

power-down, the slope of the falling voltage is set by the

200µA current source connected to GND and the external

GATE capacitor.

The voltage at the GATE pin will be modulated to maintain

a constant current when either the 3V or 5V supplies go

into current limit. When a current limit fault occurs after

the inhibit period set by the TIMER pin capacitance, the

undervoltage lockout circuit on 3.3V, 5V or 12V trips or

the FAULT pin is pulled low, the GATE pin is immediately

pulled to GND.

5V

(Pin 12): 5V Current Limit Set Pin. With a sense

SENSE

resistor placed in the supply path between 5VIN and

5V

, the GATE pin voltage will be adjusted to maintain

SENSE

a constant voltage across the sense resistor and a constant current through the switch. A foldback feature makes

the current limit decrease as the voltage at the 5V

approaches GND. To disable the current limit, 5V

OUT

SENSE

pin

and 5VIN can be shorted together.

5VIN (Pin 13): Analog Input. Used to monitor the 5V input

supply voltage. An undervoltage lockout circuit prevents

the switches from turning on when the voltage at the 5V

IN

pin is less than 2.5V typically.

5V

(Pin 14): Analog Input. Used to monitor the 5V

OUT

output supply voltage. The PWRGD signal cannot go high

until the 5V

pin exceeds 4.65V typically.

OUT

7

Page 8

LTC1643L/LTC1643L-1/LTC1643H

UUU

PIN FUNCTIONS

V

connected between V

(Pin 15): –12V Supply Output. A 1.2Ω switch is

EEOUT

EEIN

and V

EEOUT

. V

EEOUT

must

exceed –10.8V before the PWRGD signal can go high on

the LTC1643H and LTC1643L.

W

BLOCK DIAGRAM

ON/ON

FAULT

PWRGD

5V

IN5VSENSE

13

12 11 10 9 3 14

–

5V

+

2.5V

UVL

5

6

Q3

7

Q4

OUT

+

–

GATE

12V

Q5

LOGIC

12V

connected between 12VIN and 12V

(Pin 16): 12V Supply Output. A 0.5Ω switch is

OUT

. 12V

OUT

OUT

must

exceed 11.4V before the PWRGD signal can go high on the

LTC1643H and LTC1643L.

3V

IN

50µA

200µA

3V

SENSE

IN

3V

OUT

–

+

+

–

2.5V

UVL

C

C

3V

5V

OUT

OUT

Q8

P3

+

–

REF

P4

+

–

Q7

12V

9.5V

UVL

Q1

1 16 4 2 15 8

12V

12V

IN

U

Q9

REF

LTC1643H/LTC1643L

OUT

WUU

+

–

ONLY

C

P7

IN

20µA

Q6

TIMER

APPLICATIONS INFORMATION

Hot Circuit Insertion

When a circuit board is inserted into a live PCI slot, the

supply bypass capacitors on the board can draw huge

transient currents from the PCI power bus as they charge

up. The transient currents can cause permanent damage

to the connector pins and cause glitches on the power bus,

causing other boards in the system to reset.

The LTC1643 is designed to turn a board’s supply voltages

on and off in a controlled manner, allowing the board to be

REF

Q2

C

P5

+

Q10

V

V

EEIN

EEOUT

–

LTC1643H/LTC1643L

ONLY

REF

1643 BD

GND

safely inserted or removed from a live PCI slot without

glitching the system power supplies. The chip also protects the PCI supplies from shorts and monitors the

supply voltages.

The LTC1643H is designed for motherboard applications, while the LTC1643L/LTC1643L-1 are designed for

CompactPCI applications where the chip resides on the

plug-in board.

8

Page 9

LTC1643L/LTC1643L-1/LTC1643H

U

WUU

APPLICATIONS INFORMATION

LTC1643 FEATURE SUMMARY

1. Allows safe board insertion and removal from either a

motherboard (LTC1643H) or CompactPCI board

(LTC1643L/LTC1643L-1).

2. Controls all four PCI supplies: –12V, 12V, 3.3V and 5V.

3. Programmable foldback current limit: a programmable

analog current limit with a value that depends on the

output voltage. If the output is shorted to ground, the

current limit drops to keep power dissipation and

supply glitches to a minimum.

4. Programmable circuit breaker: if a supply remains in

current limit too long, the circuit breaker will trip, the

supplies will be turned off and the FAULT pin pulled low.

5. Current limit power-up: the supplies are allowed to

power up in current limit. Allows the chip to power up

boards with widely varying capacitive loads without

tripping the circuit breaker. The maximum allowable

power-up time is programmable using the TIMER pin.

6. –12V and 12V power switches on chip.

7. Power good output: monitors the voltage status of the

four supply voltages, except the LTC1643L-1 which

only monitors 3V

8. Space saving 16-pin SSOP package.

PCI Power Requirements

PCI systems usually require four power rails: 5V, 3.3V,

12V and –12V. Systems implementing the 3.3V signaling

environment are usually required to provide all four rails in

every system. Systems implementing the 5V signaling

environment may either ship the 3.3V supply with the

system or provide a means to add it afterward. The

tolerance of the supplies as measured at the components

on the plug-in card is summarized in Table 1.

Table 1. PCI Power Supply Requirements

SUPPLY TOLERANCE LOAD

5V 5V ±5% <3000µF

3.3V 3.3V ±0.3V < 3000µF

12V 12V ±5% <500µF

–12V –12V ±10% <120µF

OUT

and 5V

CAPACITIVE

OUT

.

Some ±12V supplies in CompactPCI applications are not

well regulated and can violate the tolerance specification.

For these applications, the LTC1643L-1 should be used

because the PWRGD signal does not depend on ±12V

outputs.

Power-Up Sequence

The power supplies are controlled by placing external

N-channel pass transistors in the 3.3V and 5V power

paths, and internal pass transistors for the 12V and –12V

power paths (Figure 1).

Resistors R1 and R2 provide current fault detection and

R7 and C1 provide current control loop compensation.

Resistors R5 and R6 prevent high frequency oscillations

in Q1 and Q2.

When the ON pin (Pin 5) is pulled high, the pass transistors

are allowed to turn on and a 20µA current source is

connected to the TIMER pin (Pin 4) (Figure 2).

The current in each pass transistor increases until it

reaches the current limit for each supply. Each supply is

then allowed to power up at the rate dv/dt = 50µA/C1 or as

determined by the current limit and the load capacitance

whichever is slower. Current limit faults are ignored while

the TIMER pin (Pin 4) voltage is ramping up and is less

than 0.9V below 12VIN (Pin 1). Once all four supply

voltages are within tolerance, the PWRGD pin (Pin 7) will

pull low.

Power-Down Sequence

When the ON (Pin 5) is pulled low, a power-down

sequence begins (Figure 3).

Internal switches are connected to each of the output

supply voltage pins to discharge the bypass capacitors to

ground. The TIMER pin (Pin 4) is immediately pulled low.

The GATE pin (Pin 11) is pulled down by a 200µA current

source to prevent the load currents on the 3.3V and 5V

supplies from going to zero instantaneously and glitching

the power supply voltages. When any of the output

voltages dip below its threshold, the PWRGD pin (Pin 7)

pulls high.

9

Page 10

LTC1643L/LTC1643L-1/LTC1643H

U

WUU

APPLICATIONS INFORMATION

R2

0.005ΩQ2IRF7413

SYSTEM

POWER

SUPPLY

109

3V

3V

IN

SENSE

IN

Figure 1. Typical Application

PCI

POWER

SYSTEM

CONTROLLER

RESET

10k

10k

8

GND

1

12V

2

V

EEIN

5

ON

R3

6

FAULT

R4

7

PWRGD

R1

0.007Ω

R5

10Ω

11 3 13 12 14

3V

GATE

OUT

LTC1643H

5V

IN

5V

SENSE

Q1

IRF7413

R6

10Ω

5V

5A

3.3V

7.6A

R7

100Ω

C1

5V

OUT

12V

OUT

V

EEOUT

TIMER

0.047µF

16

15

4

C2

0.1µF

GND

12V

500mA

–12V

100mA

LOGIC

RESET

1643 F01

10V/DIV

TIMER

10V/DIV

GATE

10V/DIV

12V

OUT

5V/DIV

5V

OUT

5V/DIV

3V

OUT

5V/DIV

V

EEOUT

5V/DIV

FAULT

10V/DIV

PWRGD

10V/DIV

ON

ON

10V/DIV

TIMER

10V/DIV

GATE

10V/DIV

12V

OUT

5V/DIV

5V

OUT

5V/DIV

3V

OUT

5V/DIV

V

EEOUT

5V/DIV

FAULT

10V/DIV

PWRGD

10V/DIV

10

10ms/DIV

Figure 2. Normal Power-Up Sequence

1643 F02

10ms/DIV

Figure 3. Normal Power-Down Sequence

1643 F03

Page 11

LTC1643L/LTC1643L-1/LTC1643H

U

WUU

APPLICATIONS INFORMATION

Timer

During a power-up sequence, a 20µA current source is

connected to the TIMER pin (Pin 4) and current limit faults

are ignored until the voltage ramps to within 0.9V of 12V

(Pin 1). This feature allows the chip to power up a PCI slot

that can accept boards with widely varying capacitive

loads on the supplies. The power-up time will be:

CV

t

ON

For C

SUPPLY

= 5A, the turn-on time will be ~10ms. The timer period

should be set longer than the maximum supply turn-on

time but short enough to not exceed the maximum safe

operating area of the pass transistor during a short circuit.

The timer period will be:

t

TIMER

For C

TIMER

TIMER pin (Pin 4) is immediately pulled low when ON

(Pin 5) goes low.

Thermal Shutdown

The internal switches for the 12V and –12V supplies are

protected by an internal current limit and thermal shutdown circuit. When the temperature of chip reaches

150°C, all switches will be latched off and the FAULT pin

(Pin 6) will be pulled low.

Short-Circuit Protection

During a normal power-up sequence, if the TIMER (Pin 4)

is done ramping and a supply is still in current limit, all of

the pass transistors will be immediately turned off and the

FAULT pin (Pin 6) will be pulled low as shown in Figure 4.

SUPPLY SUPPLY

≅−2

= 2000µF, V

C

=

= 0.1µF, the timer period will be ~50ms. The

•

II

LIMIT LOAD

SUPPLY

1

V

•.11

TIMER

A

22µ

= 5V, I

LIMIT

= 7A, I

IN

LOAD

turning on —from causing false trips of the circuit breaker.

The chip will stay in the latched-off state until ON (Pin 5)

is cycled low then high, or the 12VIN pin (Pin 1) power

supply is cycled.

To prevent excessive power dissipation in the pass transistors and to prevent voltage spikes on the supplies

during short-circuit conditions, the current limit on each

supply is designed to be a function of the output voltage.

As the output voltage drops, the current limit decreases.

Unlike a traditional circuit breaker function where huge

currents can flow before the breaker trips, the current

foldback feature assures that the supply current will be

kept at a safe level and prevent voltage glitches when

powering up into a short.

The current limit for the 5V and 3.3V supplies is set by

placing a sense resistor between 5VIN (Pin 13) and 5V

(Pin 12) and between 3VIN (Pin 9) and 3V

The current limit will be set by:

I

= 53mV/R

LIMIT

For a 0.005Ω resistor, the current limit will be set at 10.6A

and fold back to 1.5A when the output is shorted. For a

0.007Ω resistor, the current limit will be set at 7.6A and

fold back to 1.1A when the output is shorted.

The current limit for the internal 12V switch is set at

850mA folding back to 250mA and the –12V switch at

450mA folding back to 160mA.

In systems where it is possible to exceed the current limit

for a short amount of time, it might be necessary to

prevent the analog current loop from responding quickly

so the output voltage does not droop. This can be accomplished by adding an RC filter across the sense resistor as

shown in Figure 6. R1 should be 20Ω or less to prevent

offset errors. A 0.1µF capacitor gives a delay of about

1.5µs and a 1µF capacitor gives a delay of about 15µs.

SENSE

SENSE

SENSE

(Pin 10).

If a short circuit occurs after the supplies are powered up,

the shorted supply’s current will drop immediately to the

limit value (Figure 5).

If the supply remains in current limit for more than 15µs,

all of the supplies will be latched off. The 15µs delay

prevents quick current spikes—for example, from a fan

CompactPCI Application

The LTC1643L is designed for hot swapping CompactPCI

boards. The typical application is shown in Figure 7. The

3.3V, 5V, 12V and –12V inputs to the LTC1643L come

from the medium length power pins. The long 3.3V, 5V and

V(I/O) pins power up the pull-up resistors, bus precharge

11

Page 12

LTC1643L/LTC1643L-1/LTC1643H

U

WUU

APPLICATIONS INFORMATION

ON

10V/DIV

TIMER

10V/DIV

GATE

10V/DIV

12V

OUT

5V/DIV

5V

OUT

5V/DIV

3V

OUT

5V/DIV

V

EEOUT

5V/DIV

FAULT

10V/DIV

PWRGD

10V/DIV

ON

10V/DIV

TIMER

10V/DIV

GATE

10V/DIV

12V

OUT

5V/DIV

3V

OUT

5V/DIV

5V

OUT

5V/DIV

V

EEOUT

5V/DIV

FAULT

10V/DIV

PWRGD

10V/DIV

20ms/DIV

Figure 4. Power-Up into a Short on 3.3V Output

5V

R2

3.3V

0.005ΩQ2IRF7413

C2

R3

1µF

20Ω

3VIN3V

SENSE

R5

10Ω

11 3

GATE

Figure 6. Delay in the Current Limit Loop

1643 F05

3V

OUT

LTC1643L

5V

0.007Ω

1µF

13

IN

20ms/DIV

1643 F04

Figure 5. Short Circuit on 5V

R1

C3

5V

R4

20Ω

12 14109

SENSE

Q1

IRF7413

R6

10Ω

5V

5V

5A

3.3V

7.6A

R7

100Ω

C1

0.047µF

OUT

1643 F06

12

Page 13

LTC1643L/LTC1643L-1/LTC1643H

U

WUU

APPLICATIONS INFORMATION

MED 5V

MED 3.3V

12V

–12V

BD_SEL#

HEALTHY#

LONG GND

PCI_RST#

CompactPCI CONNECTOR

I/O

D2*

12V

C6

0.1µF

*1SMA12CAT3

R8

1.2k

5%

C7

0.1µF

V(I/O)

V(I/O)

R10

2k

5%

R9

2k

5%

V(I/O)

1

2

5

6

7

R1

0.005Ω

1%

3V

IN

12V

IN

V

EEIN

ON

FAULT

PWRGD

DATA LINE EXAMPLE

3V

SENSE

DATA BUS

109

R2

0.007Ω

1%

Q2

IRF7413

R3

10Ω

5%

11 3 13 12 14

5V

5V

IN

LOCAL_PCI_RESET#

10Ω, 5%

SENSE

GND

GATE

8

3V

OUT

LTC1643L

IRF7413

TIMER

R14

Q1

4

R4

10Ω

5%

C2

0.1µF

5V

5A

3.3V

7.6A

R5

100Ω

5%

C1

5V

OUT

12V

OUT

V

EEOUT

0.047µF

16

12V

500mA

15

–12V

100mA

PRECHARGE OUT

1V ±20%

I

= ±40mA

OUT

C3

0.01µF

R13

LONG

10k

5%

I/O

RESET#

3.3V

3.3V

D1

1N4148

R11

24Ω

5%

LONG

PCI

BRIDGE

(21154)

LONG

3.3V

LT1117

IN

1643 F07

OUT

C4

1µF

ADJ

R6

130Ω

1%

R7

56.2Ω

1%

5V

5V

Figure 7. Typical CompactPCI Application

circuit, PCI bridge chip and the LOCAL_PCI_RESET# logic

circuitry. The BD_SEL# signal is connected to the ON pin

while the PWRGD pin is connected to the HEALTHY#

signal. The HEATHLY# signal is combined with the

PCI_RESET# signal to generate the LOCAL_PCI_RESET#

signal. Capacitors C6 and C7 provide chip bypassing on

the 12V and –12V inputs. Diode D2 protects the part from

voltage surges below –13.2V on the –12V supply.

The 1V precharge voltage for the data bus lines is generated by an LT1117 low dropout regulator. The output of the

LT1117 is set to 1.8V, then the voltage is dropped by a

1N4148 diode to generate 1V. The precharge circuit is

capable of sourcing and sinking 40mA.

LTC1643L-1

The LTC1643L-1 is designed for CompactPCI designs

where the ±12V supplies are not being used on the board

or the supplies are not well regulated. The power good

comparators on the 12V

The V

pin can be connected to GND and the part will

EEIN

still operate normally if a –12V

OUT

and V

OUT

pins are disabled.

EEOUT

output is not needed.

However, 12V is still required at the 12VIN pin for the part

to function. Refer to Figure 10 for a typical LTC1643L-1

application circuit.

Increasing 12V and –12V Current Capability

The internal switches in the LTC1643 are designed for up

to 500mA loads on 12V and 200mA on –12V. If more

current is needed, then the circuits in Figure 8 can be used.

13

Page 14

LTC1643L/LTC1643L-1/LTC1643H

U

WUU

APPLICATIONS INFORMATION

For the 12V supply, P-channel transistor Q4 is placed in

parallel with the internal switch. When the LTC1643H is

turned off, the GATE pin is held low and transistor Q3 is

turned on which pulls the gate of Q4 high, turning it off.

When the LTC1643H is turned on, the GATE pin goes high,

turning off Q3 and allowing R8 to pull the gate of Q4 low

to turn it on.

Because Q4 is in parallel with the internal 12V switch, the

load current will be shared in proportion to their respective

R

switch is 0.2Ω and the internal switch is 0.4Ω, then, at

1.5A load current, the external switch will provide 1A and

the internal switch 500mA. The circuit breaker current will

be reached when the internal current reaches 1A and the

external current is 2A or 3A load current.

values. For example, if the R

DS(ON)

of the external

DS(ON)

For the –12V supply, N-channel transistor Q6 is used to

provide the extra load current. When the LTC1643H is

turned on, the internal VEE switch is turned on and the

–12V output starts to pull down through D1 and turns on

Q5. When Q5 turns on, the gate of Q6 starts to rise, turning

it on. When the LTC1643H turns off, the V

EEOUT

pin is

pulled up to ground, diode D1 is reversed biased, and

transistor Q5 turns off, which allows resistor R10 to turn

off Q6.

The internal –12V switch provides the current limit for the

supply, but because the high R

of the internal switch

DS(ON)

(1.2Ω) is in series with D1, very large currents can flow

through Q6 before the circuit breaker trips. However, if a

short to ground occurs on the –12V output, diode D1 will

prevent Q5 from turning on, which will prevent Q6 from

turning on.

Q4

Si9400

Q3

TP0610T

12V

1.5A

SYSTEM

POWER

SUPPLY

PCI

POWER

SYSTEM

CONTROLLER

10k

10k

5V

12

SENSE

C3

0.1µF

12V

V

EEOUT

TIMER

16

OUT

Q1

IRF7413

15

4

R6

10Ω

C2

0.1µF

R7

100Ω

Q5

TP0610T

R9

200Ω

R10

200Ω

Si9410DY

D1

1N4148

Q6

5V

5A

3.3V

7.6A

GND

C1

0.047µF

–12V

1.5A

1643 F08

R8

100k

R1

R2

0.005ΩQ2IRF7413

R5

10Ω

1

3V

3V

12V

IN

IN

8

GND

2

V

EEIN

5

ON

R3

6

FAULT

R4

7

PWRGD

109

SENSE

GATE

11 3 13

3V

OUT

LTC1643H

0.007Ω

5V

IN

Figure 8. Increasing 12V and –12V Current Capability

14

Page 15

PACKAGE DESCRIPTION

LTC1643L/LTC1643L-1/LTC1643H

U

Dimensions in inched (millimeters) unless otherwise noted.

GN Package

16-Lead Plastic SSOP (Narrow 0.150)

(LTC DWG # 05-08-1641)

0.189 – 0.196*

(4.801 – 4.978)

16

15

14

12 11 10

13

0.009

(0.229)

9

REF

0.007 – 0.0098

(0.178 – 0.249)

0.016 – 0.050

(0.406 – 1.270)

* DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH

SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

** DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD

FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

U

TYPICAL APPLICATIONS

SYSTEM

POWER

SUPPLY

8

GND

1

12V

2

V

5

ON

PCI

POWER

SYSTEM

CONTROLLER

10k

10k

R3

6

FAULT

R4

7

PWRGD

EEIN

IN

0.015

0° – 8° TYP

3V

IN

± 0.004

(0.38 ± 0.10)

0.007Ω

5V

IN

× 45°

R1

109

3V

SENSE5VSENSE

LTC1643H

0.229 – 0.244

(5.817 – 6.198)

0.053 – 0.068

(1.351 – 1.727)

0.008 – 0.012

(0.203 – 0.305)

Q1

IRF7413

R6

10Ω

1113 12 143

GATE

0.150 – 0.157**

(3.810 – 3.988)

5

OUT

12V

V

EEOUT

TIMER

3

R7

100Ω

OUT

4

678

0.004 – 0.0098

(0.102 – 0.249)

0.0250

(0.635)

BSC

GN16 (SSOP) 1098

5V

5A

GND

C1

0.047µF

16

15

4

C2

0.1µF

12V

500mA

–12V

100mA

1643 G09

12

5V

3V

OUT

Figure 9. System Without 3.3V Supply

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

15

Page 16

LTC1643L/LTC1643L-1/LTC1643H

U

TYPICAL APPLICATIONS

MED 5V

MED 3.3V

12V

BD_SEL#

HEALTHY#

LONG GND

1.2k

CompactPCI CONNECTOR

C7

0.1µF

R8

5%

V(I/O)

V(I/O)

R10

2k

5%

R9

2k

5%

V(I/O)

1

2

5

6

7

3V

12V

IN

V

EEIN

ON

FAULT

PWRGD

0.005Ω

1%

IN

R1

3V

Q2

IRF7413

R3

10Ω

5%

11 3 13 12 14

109

3V

GATE

SENSE

LTC1643L-1

GND

8

OUT

5V

R2

0.007Ω

1%

IN

5V

IRF7413

SENSE

TIMER

Q1

5V

5A

3.3V

R4

10Ω

100Ω

5%

5%

5V

OUT

12V

OUT

V

EEOUT

4

C2

0.1µF

R5

16

15

PRECHARGE OUT

1V ±20%

= ±40mA

I

OUT

7.6A

C1

0.047µF

C3

0.01µF

D1

1N4148

R11

24Ω

5%

R6

130Ω

1%

R7

56.2Ω

1%

LT1117

OUT

C4

1µF

ADJ

LONG

3.3V

IN

R13

LONG

3.3V

3.3V

RESET#

BRIDGE

(21154)

PCI

LONG

5V

5V

1643 F10

PCI_RST#

LOCAL_PCI_RESET#

R14

I/O

*1SMA12CAT3

DATA LINE EXAMPLE

DATA BUS

10Ω, 5%

10k

5%

I/O

Figure 10. CompactPCI Application Without ±12V Outputs

RELATED PARTS

PART NUMBER DESCRIPTION COMMENTS

LTC1421 Hot Swap Controller Multiple Supply

LTC1422 Hot Swap Controller Single Supply, SO-8 Package

LT1640 –48V Hot Swap Controller Negative High Voltage Supplies, SO-8 Package

LTC1642 Fault Protected Hot Swap Controller Operation up to 15V, Handles Surges to 33V

16

Linear Technology Corporation

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 ● FAX: (408) 434-0507

●

www.linear-tech.com

1643fs, sn1643 LT/TP 0899 4K • PRINTED IN USA

LINEAR TECHNOLOGY CORPORATION 1998

Loading...

Loading...