Page 1

FEATURES

■

Very Low Noise: 1mV

■

–5V at 150mA from a 5V Input

■

Better Regulation Than a Charge Pump

■

Effective Output Impedance: 0.14Ω

■

Uses Tiny Capacitors and Inductors

■

Internally Compensated

■

Fixed Frequency 1.4MHz Operation

■

Low Shutdown Current: <1µA

■

Low V

■

Tiny 5-Lead SOT-23 Package

Switch: 300mV at 300mA

CESAT

Output Ripple

P–P

U

APPLICATIO S

■

MR Head Bias

■

Digital Camera CCD Bias

■

LCD Bias

■

GaAs FET Bias

■

Positive-to-Negative Conversion

LT1611

Inverting 1.4MHz Switching

Regulator in SOT-23

U

DESCRIPTIO

The LT®1611 is the industry’s first inverting 5-lead SOT-23

current mode DC/DC converter. Intended for use in small,

low power applications, it operates from an input voltage

as low as 1.1V and switches at 1.4MHz, allowing the use

of tiny, low cost capacitors and inductors 2mm or less in

height. Its small size and high switching frequency enable

the complete DC/DC converter function to consume less

than 0.25 square inches of PC board area. Capable of

generating –5V at 150mA from a 5V supply or –5V at

100mA from a 3V supply, the LT1611 replaces nonregulated

“charge pump” solutions in many applications.

The LT1611 operates in a dual inductor inverting topology

which filters the input side as well as the output side of the

DC/DC converter. Fixed frequency switching ensures a

clean output free from low frequency noise typically present

with charge pump solutions. No load quiescent current of

the LT1611 is 3mA, while in shutdown quiescent current

drops to 0.5µA. The 36V switch allows VIN to V

differential of up to 33V.

OUT

U

TYPICAL APPLICATIO

R1

29.4k

R2

10k

C2

1µF

L1B

22µH

D1

1200pF

C3

22µF

L1A

V

IN

SHDN

22µH

SW

LT1611

NFB

GND

V

IN

5V

+

C1

22µF

C1: AVX TAJB226M010

C2: TAIYO YUDEN LMK212BJ105MG

C3: TAIYO YUDEN JMK325BJ226MM (1210 SIZE)

D1: MBR0520

L1: SUMIDA CLS62-220 OR 2× MURATA LQH3C220 (UNCOUPLED)

Figure 1. 5V to –5V, 150mA Low Noise Inverting DC/DC Converter

The LT1611 is available in the 5-lead SOT-23 package.

, LTC and LT are registered trademarks of Linear Technology Corporation.

Transient Response

V

OUT

–5V

150mA

LOAD CURRENT

1611 TA01

V

OUT

20mV/DIV

AC COUPLED

150mA

50mA

100µs/DIV

1611 F10

1

Page 2

LT1611

WW

W

ABSOLUTE MAXIMUM RATINGS

(Note 1)

VIN Voltage .............................................................. 10V

SW Voltage ................................................–0.4V to 36V

NFB Voltage .............................................................–3V

Current into NFB Pin ............................................. ±1mA

U

U

W

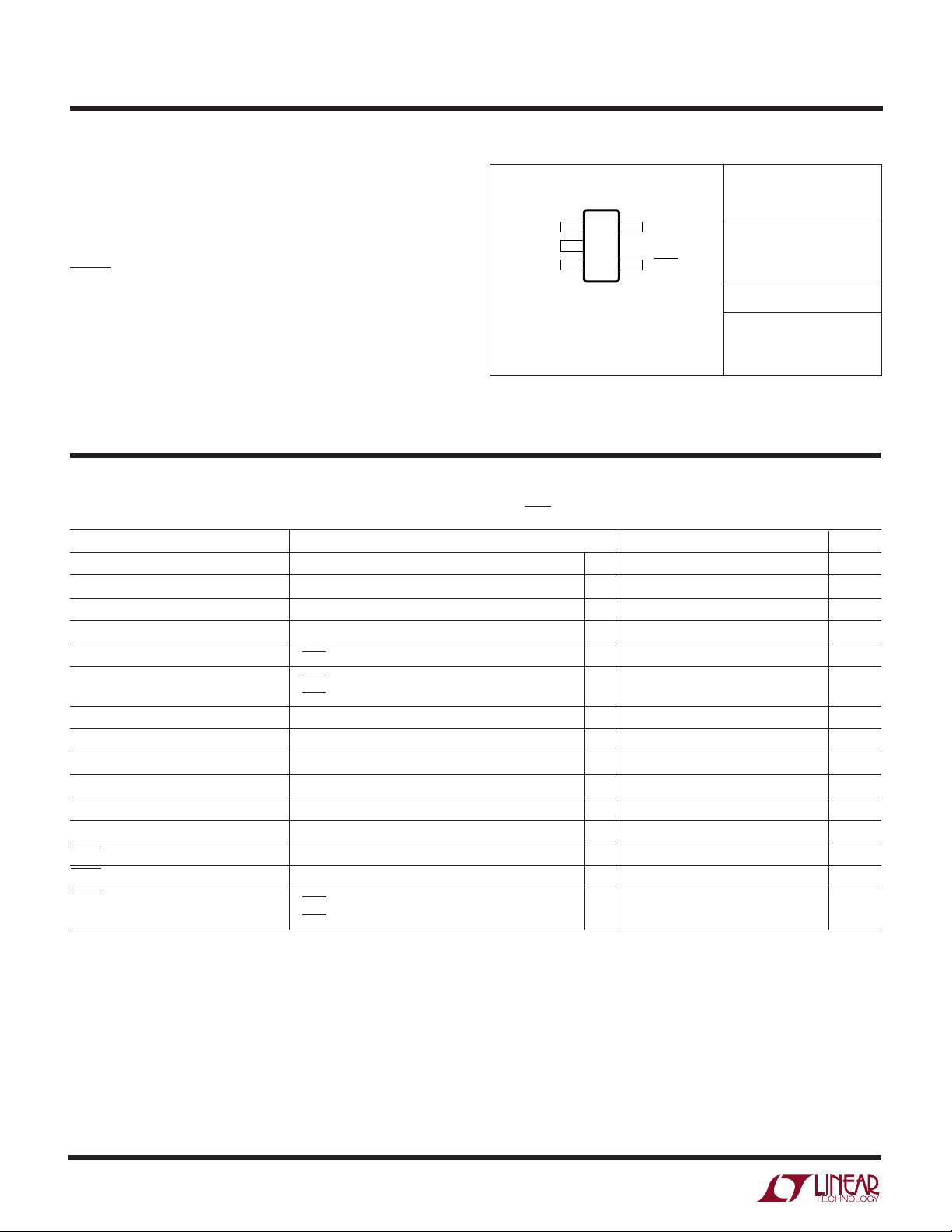

PACKAGE/ORDER INFORMATION

ORDER PART

SW 1

GND 2

NFB 3

TOP VIEW

5 V

IN

4 SHDN

NUMBER

LT1611CS5

U

SHDN Voltage .......................................................... 10V

Maximum Junction Temperature .......................... 125°C

S5 PACKAGE

5-LEAD PLASTIC SOT-23

S5 PART MARKING

Operating Temperature Range

Commercial .............................................0°C to 70°C

T

= 125°C, θJA = 256°C/W

JMAX

LTES

Extended Commercial (Note 2)........... – 40°C to 85°C

Storage Temperature Range ................. –65°C to 150°C

Consult factory for Industrial and Military grade parts.

Lead Temperature (Soldering, 10 sec)..................300°C

ELECTRICAL CHARACTERISTICS

temperature range, otherwise specifications are at TA = 25°C. VIN = 1.5V, V

PARAMETER CONDITIONS MIN TYP MAX UNITS

Minimum Operating Voltage 0.9 1.1 V

Maximum Operating Voltage 10 V

NFB Pin Bias Current V

Feedback Voltage ● –1.205 –1.23 –1.255 V

Quiescent Current V

Quiescent Current in Shutdown V

Reference Line Regulation 1.5V ≤ VIN ≤ 10V 0.02 0.2 %/V

Switching Frequency ● 1.0 1.4 1.8 MHz

Maximum Duty Cycle ● 82 86 %

Switch Current Limit (Note 3) 550 800 mA

Switch V

CESAT

Switch Leakage Current VSW = 5V 0.01 1 µA

SHDN Input Voltage High 1V

SHDN Input Voltage Low 0.3 V

SHDN Pin Bias Current V

= –1.23V ● –2.7 –4.7 –6.7 µA

NFB

= 1.5V, Not Switching 3 4.5 mA

SHDN

= 0V, VIN = 2V 0.01 0.5 µA

SHDN

= 0V, VIN = 5V 0.01 1.0 µA

V

SHDN

ISW = 300mA 300 350 mV

= 3V 25 50 µA

SHDN

V

= 0V 0 0.1 µA

SHDN

The ● denotes the specifications which apply over the full operating

= VIN unless otherwise noted.

SHDN

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: C grade device specifications are guaranteed over the 0°C to 70°C

temperature range. In addition, C grade device specifications are assured

over the –40°C to 85°C temperature range by design or correlation, but

are not production tested.

2

Note 3: Current limit guaranteed by design and/or correlation to static test.

Slope compensation reduces current limit at higher duty cycle.

Page 3

UW

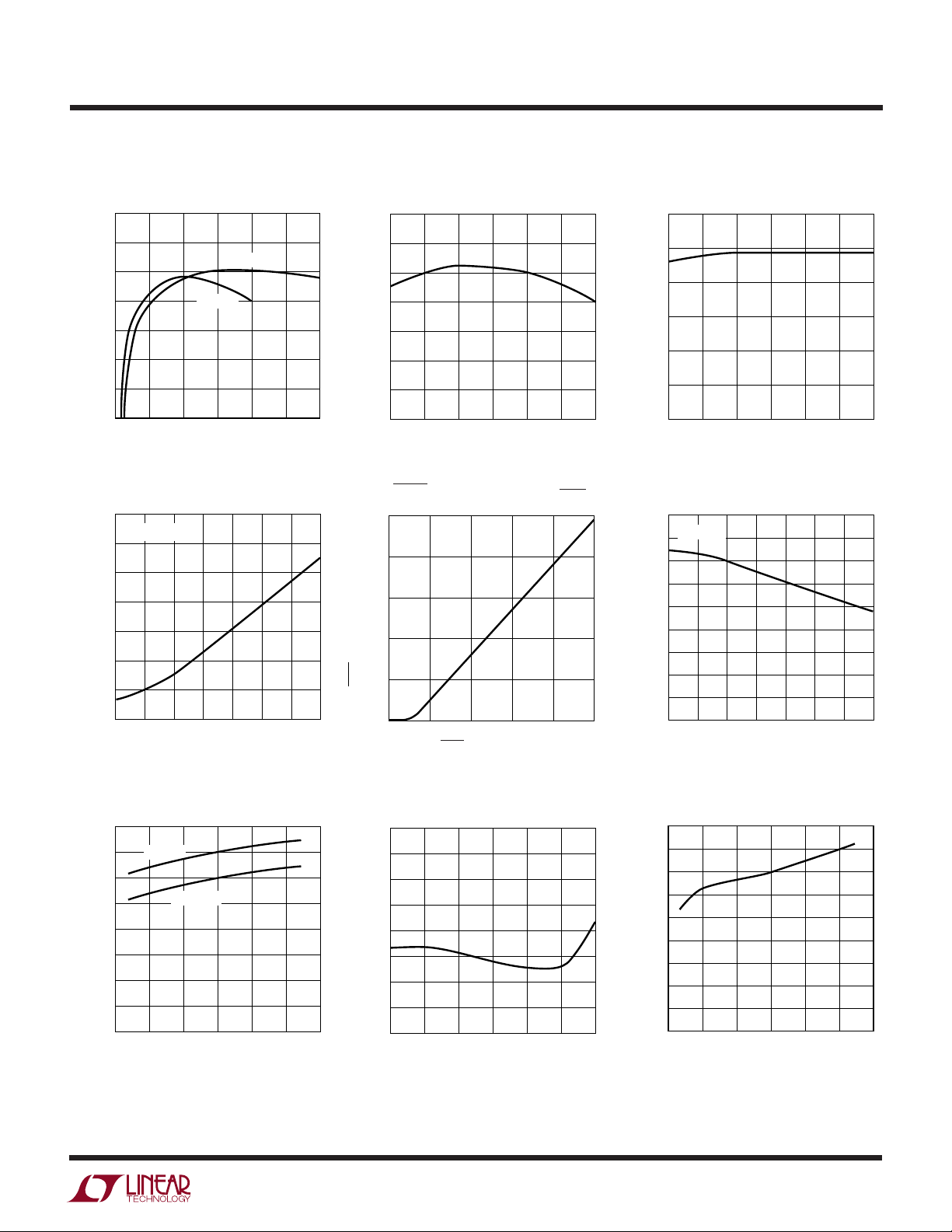

TYPICAL PERFOR A CE CHARACTERISTICS

Efficiency, V

85

OUT

= –5V

–1.245

vs Temperature

NFB

LT1611

NFB Pin Bias Current vs

TemperatureV

6

80

75

70

65

EFFICIENCY (%)

60

55

50

0

Switch V

700

TA = 25°C

600

500

400

(mV)

300

CESAT

V

200

100

0

0 100 200 300 400 500 600 700

50 75 100 125 150

25

LOAD CURRENT (mA)

CESAT

SWITCH CURRENT (mA)

VIN = 5V

VIN = 3V

vs Switch Current Switch Current Limit vs Duty CycleSHDN Pin Bias Current vs V

Oscillator Frequency vs

Temperature

2.00

1.75

1.50

1.25

1.00

0.75

0.50

SWITCHING FREQUENCY (MHz)

0.25

VIN = 5V

VIN = 1.5V

0

–50 –25 0 25 50 75 100

TEMPERATURE (°C)

1611 G01

1611 G04

1611 G07

–1.240

–1.235

–1.230

(V)

NFB

V

–1.225

–1.220

–1.215

–1.210

–50 0 50–25 25 75 100

50

40

30

20

10

SHDN PIN BIAS CURRENT (µA)

0

012345

TEMPERATURE (°C)

SHDN PIN VOLTAGE (V)

No-Load Operating Quiescent

Current vs Temperature*

6.0

5.5

5.0

4.5

4.0

3.5

3.0

OPERATING CURRENT (mA)

2.5

2.0

–50 0 50–25 25 75 100

TEMPERATURE (°C)

1611 G02

SHDN

1611 G05

1611 G08

5

4

3

2

NFB PIN BIAS CURRENT (µA)

1

0

–50 0 50–25 25 75 100

900

TA = 25°C

800

700

600

500

400

300

200

SWITCH CURRENT LIMIT (mA)

100

0

10

TEMPERATURE (°C)

20 30 40 50 60 70 80

DUTY CYCLE (%)

Switch Current Limit vs

Temperature (Duty Cycle = 30%)

900

800

700

600

500

400

300

200

SWITCH CURRENT LIMIT (mA)

100

0

–25 0 25 50 75 100

–50

TEMPERATURE (°C)

1611 G03

1611 G06

1611 G09

* Includes bias current through R1, R2 and Schottky leakage current at T ≥ 75°C

3

Page 4

LT1611

UUU

PIN FUNCTIONS

SW (Pin 1): Switch Pin. Minimize trace area at this pin to

keep EMI down.

GND (Pin 2): Ground. Tie directly to local ground plane.

NFB (Pin 3): Negative Feedback Pin. Minimize trace area.

Reference voltage is –1.23V. Connect resistive divider tap

here. The suggested value for R2 is 10k. Set R1 and R2

according to:

W

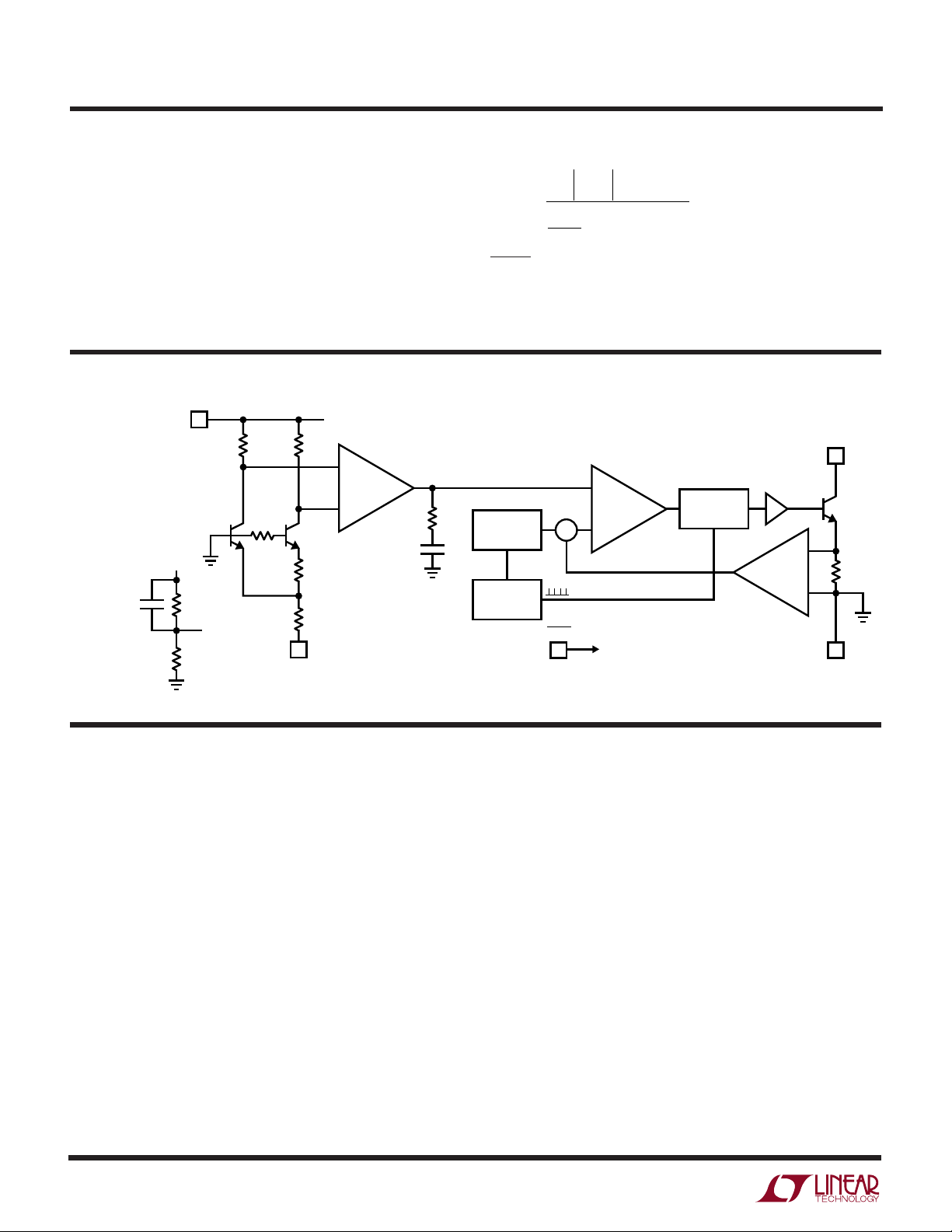

BLOCK DIAGRAM

V

IN

R6

40k

+

A1

g

m

–

Q2

x10

R3

30k

R4

140k

3

NFB

R

C

C

C

C

(OPTIONAL)

V

5

IN

R5

40k

Q1

V

OUT

PL

R1

(EXTERNAL)

NFB

R2

(EXTERNAL)

V

R

1

=

123

.

R

2

OUT

+

−

45

.•

123

.

10

6

−

SHDN (Pin 4): Shutdown Pin. Tie to 1V or more to enable

device. Ground to shut the device down.

VIN (Pin 5): Input Supply Pin. Must be locally bypassed.

1

SW

Q3

+

0.15Ω

–

2

GND

1611 BD

RAMP

GENERATOR

1.4MHz

OSCILLATOR

SHDN

4

Σ

COMPARATOR

–

A2

+

SHUTDOWN

FF

RQ

S

A = 3

DRIVER

Figure 2

U

OPERATIO

The LT1611 combines a current mode, fixed frequency

PWM architecture with a –1.23V reference to directly

regulate negative outputs. Operation can be best understood by referring to the block diagram of Figure 2. Q1 and

Q2 form a bandgap reference core whose loop is closed

around the output of the converter. The driven reference

point is the lower end of resistor R4, which normally sits

at a voltage of –1.23V. As the load current changes, the

NFB pin voltage also changes slightly, driving the output

of gm amplifier A1. Switch current is regulated directly on

a cycle-to-cycle basis by A1’s output. The flip-flop is set at

the beginning of each cycle, turning on the switch. When

the summation of a signal representing switch current and

a ramp generator (introduced to avoid subharmonic oscillations at duty factors greater than 50%) exceeds the V

signal, comparator A2 changes stage, resetting the flip-

C

flop and turning off the switch. Output voltage decreases

(the magnitude increases) as switch current is increased.

The output, attenuated by external resistor divider R1 and

R2, appears at the NFB pin, closing the overall loop.

Frequency compensation is provided internally by RC and

CC. Transient response can be optimized by the addition of

a phase lead capacitor, CPL, in parallel with R1 in applications where large value or low ESR output capacitors are

used.

As load current is decreased, the switch turns on for a

shorter period each cycle. If the load current is further

decreased, the converter will skip cycles to maintain

output voltage regulation.

The LT1611 can work in either of two topologies. The

simpler topology appends a capacitive level shift to a

4

Page 5

OPERATIO

LT1611

U

boost converter, generating a negative output voltage,

which is directly regulated. The circuit schematic is detailed in Figure 3. Only one inductor is required, and the

two diodes can be in a single SOT-23 package. Output

noise is the same as in a boost converter, because current

is delivered to the output only during the time when the

LT1611’s internal switch is off.

If D2 is replaced by an inductor, as shown in Figure 4, a

higher performance solution results. This converter topology was developed by Professor S. Cuk of the California

Institute of Technology in the 1970s. A low ripple voltage

results with this topology due to inductor L2 in series with

the output. Abrupt changes in output capacitor current are

eliminated because the output inductor delivers current to

the output during both the off-time and the on-time of the

LT1611 switch. With proper layout and high quality output

capacitors, output ripple can be as low as 1mV

P–P

.

The operation of Cuk’s topology is shown in Figures 5

and␣ 6. During the first switching phase, the LT1611’s

switch, represented by Q1, is on. There are two current

loops in operation. The first loop begins at input capacitor

C1, flows through L1, Q1 and back to C1. The second loop

flows from output capacitor C3, through L2, C2, Q1 and

back to C3. The output current from R

L2 and C3. The voltage at node SW is V

SWX the voltage is –(VIN + |V

|). Q1 must conduct both

OUT

is supplied by

LOAD

and at node

CESAT

L1 and L2 current. C2 functions as a voltage level shifter,

with an approximately constant voltage of (VIN + |V

OUT

|)

across it.

When Q1 turns off during the second phase of switching,

the SW node voltage abruptly increases to (VIN + |V

OUT

|).

The SWX node voltage increases to VD (about 350mV).

Now current in the first loop, begining at C1, flows through

L1, C2, D1 and back to C1. Current in the second loop flows

from C3 through L2, D1 and back to C3. Load current

continues to be supplied by L2 and C3.

An important layout issue arises due to the chopped

nature of the currents flowing in Q1 and D1. If they are both

tied directly to the ground plane before being combined,

switching noise will be introduced into the ground plane.

It is almost impossible to get rid of this noise, once present

in the ground plane. The solution is to tie D1’s cathode to

the ground pin of the LT1611 before the combined currents are dumped into the ground plane as drawn in

Figures 4, 5 and 6. This single layout technique can

virtually eliminate high frequency “spike” noise so often

present on switching regulator outputs.

Output ripple voltage appears as a triangular waveform

riding on V

. Ripple magnitude equals the ripple current

OUT

of L2 multiplied by the equivalent series resistance (ESR)

of output capacitor C3. Increasing the inductance of L1

and L2 lowers the ripple current, which leads to lower

output voltage ripple. Decreasing the ESR of C3, by using

ceramic or other low ESR type capacitors, lowers output

ripple voltage. Output ripple voltage can be reduced to

arbitrarily low levels by using large value inductors and

low ESR, high value capacitors.

C2

V

IN

+

C1

Figure 3. Direct Regulation of Negative Output

Using Boost Converter with Charge Pump

L1

V

IN

LT1611

GND

1µF

SW

R1

NFBSHDNSHUTDOWN

R2

10k

D2

D1

+

–V

C3

1611 F03

OUT

C2

SW

NFB

1µF

R1

R2

10k

D1

–V

OUT

C3

+

1611 F04

V

IN

+

C1

Figure 4. L2 Replaces D2 to Make Low Output Ripple

Inverting Topology. Coupled or Uncoupled Inductors Can

Be Used. Follow Phasing If Coupled for Best Results

L1 L2

V

IN

LT1611

GND

5

Page 6

LT1611

OPERATIO

V

IN

U

+ V

V

CESAT

L1 L2

–(V

IN

C2

SW SWX

OUT

)

–V

OUT

+

C1 C3 R

Q1

D1

+

1611 F05

LOAD

Figure 5. Switch-On Phase of Inverting Converter. L1 and L2 Current Have Positive dI/dt

+ V

V

IN

V

IN

L1 L2

+

C1 C3 R

+ V

OUT

D

SW SWX

Q1

V

D

C2

–V

OUT

D1

+

LOAD

Figure 6. Switch-Off Phase of Inverting Converter. L1 and L2 Current Have Negative dI/dt

Transient Response

The inverting architecture of the LT1611 can generate a

very low ripple output voltage. Recently available high

value ceramic capacitors can be used successfully in

LT1611 designs with the addition of a phase lead capacitor, CPL (see Figure 7). Connected in parallel with feedback

resistor R1, this capacitor reduces both output perturba-

6

1611 F06

tions due to load steps and output ripple voltage to very

low levels. To illustrate, Figure 7 shows an LT1611 inverting converter with resistor loads R

and RL2. RL1 is

L1

connected across the output, while RL2 is switched in

externally via a pulse generator. Output voltage waveforms are pictured in subsequent figures, illustrating the

performance of output capacitor type and the effect of C

PL

connected across R1.

Page 7

OPERATIO

LT1611

U

R1

R2

10k

C2

1µF

C

PL

L1A

V

IN

SHDN

22µH

LT1611

GND

V

IN

5V

+

C1

C1: AVX TAJB226M010

C2: TAIYO YUDEN LMK212BJ105MG

C3: SEE TEXT

D1: MBR0520

L1A, L1B: SUMIDA CLS62-220

SW

NFB

Figure 7. Switching RL2 Provides 50mA to 150mA

Load Step for LT1611 5V to –5V Converter

V

OUT

50mV/DIV

AC COUPLED

D1

L1B

22µH

Figure 8 shows the output voltage with a 50mA to 150mA

load step, using an AVX TAJ “B” case 22µF tantalum

–V

OUT

R

L1

C3

100Ω

+

capacitor at the output. Output perturbation is approximately 100mV as the load changes from 50mA to 150mA.

R

L2

Steady-state ripple voltage is 20mV

50Ω

, due to L1’s ripple

P–P

current and C3’s ESR. Step response can be improved by

adding a 3.3nF capacitor (CPL) as shown in Figure 9.

Settling time improves from 150µs to 40µs, although

1611 F07

steady-state ripple voltage does not improve. Figure 10

pictures the output voltage and switch pin voltage at

200ns per division. Note the absence of high frequency

spikes at the output. This is easily repeatable with proper

layout, described in the next section.

V

OUT

20mV/DIV

AC COUPLED

LOAD CURRENT

150mA

50mA

100µs/DIV

Figure 8. Load Step Response of LT1611

with 22µF Tantalum Output Capacitor

V

OUT

10mV/DIV

SWITCH VOLTAGE

5V/DIV

LOAD = 150mA 200ns/DIV

Figure 10. 22µF “B” Case Tantalum Capacitor (AVX TAJ “B” Series)

Has ESR Resulting in 20mV

LOAD CURRENT

1611 F08

Figure 9. Addition of CPL to Figure 7’s Circuit

Improves Load Step Response. CPL = 3.3nF

Voltage Ripple at Output

P–P

150mA

50mA

1611 F10

20µs/DIV

1611 F09

7

Page 8

LT1611

OPERATIO

U

In Figure 11 (also shown on the first page), output capacitor C3 is replaced by a ceramic unit. These large value

ceramic capacitors have ESR of about 2mΩ and result in

very low output ripple. At the 20mV/division scale, output

voltage ripple cannot be seen. Figure 12 pictures the

output and switch nodes at 200ns per division. The output

voltage ripple is approximately 1mV

. Again, good

P–P

layout is mandatory to achieve this level of performance.

V

OUT

20mV/DIV

AC COUPLED

LOAD CURRENT

150mA

50mA

100µs/DIV

Figure 11. Replacing C3 with 22µF Ceramic Capacitor

(Taiyo Yuden JMK325BJ226MM) Improves Output

Noise. CPL = 1200pF Results in Best Phase Margin

1611 F11

Layout

The LT1611 switches current at high speed, mandating

careful attention to layout for best performance.

not get advertised performance with careless layout.

You will

Figure␣ 13

shows recommended component placement. Follow this

closely in your printed circuit layout. The cut ground

copper at D1’s cathode is essential to obtain the low noise

achieved in Figures 11 and 12’s oscillographs. Input

bypass capacitor C1 should be placed close to the LT1611

as shown. The load should connect directly to output

capacitor C2 for best load regulation. You can tie the local

ground into the system ground plane at C3’s ground

terminal.

V

OUT

5mV/DIV

AC COUPLED

SWITCH VOLTAGE

5V/DIV

LOAD = 150mA 200ns/DIV

Figure 12. 22µF Ceramic Capacitor at

Output Reduces Ripple to 1mV

. Proper

P–P

Layout Is Essential to Achieve Low Noise

1611 F12

8

L1A

C1

+

V

IN

1

2

3

R2

5

4

R1

SHUTDOWN

1611 F13

–V

OUT

GND

L1B

D1

C2

C3

+

Figure 13. Suggested Component Placement. Note Cut in Ground Copper at D1’s Cathode

Page 9

OPERATIO

LT1611

U

Start-Up/Soft-Start

The LT1611, starting from V

= 0V, reaches final voltage

OUT

in approximately 450µs after SHDN is pulled high, with

C

= 22µF, VIN = 5V and V

OUT

= – 5V. Charging the output

OUT

capacitor at this speed requires an inrush current of over

1A. If a longer start-up time is acceptable, a soft-start

circuit consisting of RSS and CSS, as shown in Figure 14,

can be used to limit inrush current to a lower value. Figure

15 pictures V

and input current, starting into a 33Ω

OUT

load, with RSS of 33kΩ and CSS of 33nF. Input current,

V

SS

V

IN

5V

R

SS

33k

D2

1N4148

C

33nF/0.1µF

CURRENT

PROBE

+

C1

22µF

SS

C1: AVX TAJB226M010

C2: TAIYO YUDEN LMK212BJ105MG

V

C3: TAIYO YUDEN JMK325BJ226MM (1210 SIZE)

OUT

D1: MBR0520

L1: SUMIDA CLS62-220 OR 2× MURATA LQH3C220 (UNCOUPLED)

V

IN

SHDN

L1A

22µH

SW

LT1611

NFB

GND

measured at VIN, is limited to a peak value of 450mA as the

time required to reach final value increases to 700µs. In

Figure 16, CSS is increased to 0.1µF, resulting in a lower

peak input current of 240mA with a V

ramp time of

OUT

2.1ms. CSS can be increased further for an even slower

ramp, if desired. Diode D2 serves to quickly discharge C

SS

when VSS is driven low to shut down the device. D2 can be

omitted, resulting in a “soft-stop” slow discharge of the

output capacitor.

R1

29.4k

R2

10k

C2

1µF

C

P

1200pF

D1

L1B

22µH

V

–5V

C3

22µF

1611 F14

OUT

Figure 14. RSS and CSS at SHDN Pin Provide Soft-Start to LT1611 Inverting Converter

V

OUT

2V/DIV

I

IN

200mA/DIV

V

S

5V/DIV

LOAD = 150mA 500µs/DIV

Figure 15. RSS = 33k, CSS = 33nF; V

OUT

–5V in 750µs; Input Current Peaks at 450mA

Reaches

1611 F15

V

OUT

2V/DIV

I

IN

200mA/DIV

V

S

5V/DIV

LOAD = 150mA 500µs/DIV

Figure 16. RSS = 33k, CSS = 0.1µF; V

OUT

–5V in 2.1ms; Input Current Peaks at 240mA

1611 F16

Reaches

9

Page 10

LT1611

OPERATIO

U

Output Current

The LT1611 will deliver 150mA at –5V from a 5V ±10%

input supply. If a higher voltage supply is available, more

output current can be obtained. Figure 17’s schematic

shows how to get more current. Although the LT1611’s

maximum voltage allowed at VIN is 10V, the SW pin can

handle higher voltage (up to 36V). In Figure 17, the VIN pin

of the LT1611 is driven from a 5V supply, while input

inductor L1A is driven from a separate 12V supply. Figure

18’s graph shows maximum recommended output current as the voltage on L1A is varied. Up to 300mA can be

delivered when driving L1A from a 12V supply.

COMPONENT SELECTION

Inductors

Each of the two inductors used with the LT1611 should

have a saturation current rating (where inductance is

approximately 70% of zero current inductance) of approximately 0.25A or greater. If the device is used in

“charge pump” mode, where there is only one inductor,

then its rating should be 0.5A or greater. DCR of the

inductors should be 0.5Ω or less. A value of 22µH is

suitable if using a coupled inductor such as Sumida

CLS62-220 or Coiltronics CTX20-1. If using two separate

inductors, increasing the value to 47µH will result in the

same ripple current. Inductance can be reduced if operating from a supply voltage below 3V. Table 1 lists several

inductors that will work with the LT1611, although this is

not an exhaustive list. There are many magnetics vendors

whose components are suitable.

V

L

(SEE TEXT)

350

300

250

200

OUTPUT CURRENT (mA)

MAXIMUM RECOMMENDED

150

100

5 6 7 8 9 10 11 12

34

VL (V)

1611 F18

5V

V

IN

SHDN

C1

1µF

C1, C2: TAIYO YUDEN LMK212BJ105MG

C3: TAIYO YUDEN JMK325BJ226MM

D1: MBR0520

L1A, L1B: SUMIDA CLS62-220

LT1611

GND

SW

NFB

L1A

22µH

29.4k

10k

C2

1µF

1200pF

D1

L1B

22µH

V

OUT

–5V

UP TO 300mA

C3

22µF

1611 F17

Figure 17. Increase Output Current By Driving L1A from a Higher Voltage Figure 18. Output Current Increases to

300mA When Driving VL from 12V Supply

10

Page 11

OPERATIO

LT1611

U

Capacitors

As described previously, ceramic capacitors can be used

with the LT1611 provided loop stability is considered. For

lower cost applications, small tantalum units can be used.

A value of 22µF is acceptable, although larger capacitance

values can be used. ESR is the most important parameter

in selecting an output capacitor. The “flying” capacitor (C2

in the schematic figures) should be a 1µF ceramic type. An

X5R or X7R dielectric should be used to avoid capacitance

decreasing severely with applied voltage. The input bypass capacitor is less critical, and either tantalum or

Table 1. Inductor Vendors

VENDOR PHONE URL PART COMMENT

Sumida (847) 956-0666 www.sumida.com CLS62-22022 22µH Coupled

Murata (404) 436-1300 www.murata.com LQH3C-220 22µH, 2mm Height

Coiltronics (407) 241-7876 www.coiltronics.com CTX20-1 20µH Coupled, Low DCR

Table 2. Capacitor Vendors

VENDOR PHONE URL PART COMMENT

Taiyo Yuden (408) 573-4150 www.t-yuden.com Ceramic Caps X5R Dielectric

AVX (803) 448-9411 www.avxcorp.com Ceramic Caps

Murata (404) 436-1300 www.murata.com Ceramic Caps

ceramic can be used with little trade-off in circuit performance. Some capacitor types appropriate for use with the

LT1611 are listed in Table 2.

Diodes

A Schottky diode is recommended for use with the LT1611.

The Motorola MBR0520 is a very good choice. Where the

input to output voltage differential exceeds 20V, use the

MBR0530 ( a 30V diode). If cost is more important than

efficiency, a 1N4148 can be used, but only at low current

loads.

CD43-470 47µH

Tantalum Caps

U

TYPICAL APPLICATIO S

3.3V

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

“Charge Pump” Inverting DC/DC Converter

SW

NFB

C2

1µF

29.4k

10k

D1

C3

22µF

1611 TA02

L1

10µH

V

IN

SHDN

C1

1µF

C1, C2: TAIYO YUDEN LMK212BJ105MG

C3: TAIYO YUDEN JMK325BJ226MM

D1, D2: MBR0520

L1: MURATA LQH3C-100

LT1611

GND

D2

–5V

70mA

11

Page 12

LT1611

U

TYPICAL APPLICATIO S

4-Cell to –10V Inverting Converter

L1A

V

IN

+

C1

22µF

C1: AVX TAJB226M010 (803) 946-0362

C2: TAIYO YUDEN LMK212BJ105MG

C3: AVX TAJA685M016

D1: MOTOROLA MBR0520 (800) 441-2447

L1: SUMIDA CL562-150 (847) 956-0666

15µH

V

IN

LT1611

GND

C2

1µF

SW

68.1k

NFBSHDNSHUTDOWN

10k

PACKAGE DESCRIPTION

2.60 – 3.00

(0.102 – 0.118)

1.50 – 1.75

(0.059 – 0.069)

4-Cell to –10V Inverting Converter Efficiency

85

80

75

70

65

EFFICIENCY (%)

60

55

50

0

VIN = 3.6V

25 50 75 100 125 150

LOAD CURRENT (mA)

D1

L1B

15µH

V

OUT

–10V/60mA

C3

+

6.8µF

1611 TA03

U

Dimensions in inches (millimeters) unless otherwise noted.

S5 Package

5-Lead Plastic SOT-23

(LTC DWG # 05-08-1633)

2.80 – 3.00

0.00 – 0.15

(0.00 – 0.006)

0.90 – 1.45

(0.035 – 0.057)

(0.110 – 0.118)

(NOTE 3)

VIN = 6.5V

VIN = 5V

1611 TA04

0.35 – 0.55

(0.014 – 0.022)

NOTE:

1. DIMENSIONS ARE IN MILLIMETERS

2. DIMENSIONS ARE INCLUSIVE OF PLATING

3. DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH AND METAL BURR

4. MOLD FLASH SHALL NOT EXCEED 0.254mm

5. PACKAGE EIAJ REFERENCE IS SC-74A (EIAJ)

0.09 – 0.20

(0.004 – 0.008)

(NOTE 2)

0.35 – 0.50

(0.014 – 0.020)

FIVE PLACES (NOTE 2)

0.90 – 1.30

(0.035 – 0.051)

1.90

(0.074)

REF

0.95

(0.037)

REF

S5 SOT-23 0599

RELATED PARTS

PART NUMBER DESCRIPTION COMMENTS

LT1307 Single Cell Micropower DC/DC with Low Battery Detector 3.3V/75mA from 1V, 600kHz Fixed Frequency

LT1316 Burst ModeTM Operation DC/DC with Programmable Current Limit 1.5V Minimum VIN, Precise Control of Peak Switch Current

LT1317 2-Cell Micropower DC/DC with Low Battery Detector 3.3V/200mA from Two Cells, 600kHz Fixed Frequency

LT1370/LT1371 500kHz High Efficiency DC/DC Converter 42V, 6A/3A Internal Switch, Negative Feedback Regulation

LT1610 Single Cell Micropower DC/DC 3V/30mA from 1V, 1.7MHz Fixed Frequency, 30µA I

LT1613 1.4MHz SOT-23 Step-Up DC/DC Converter 5V at 200mA from 3.3V Input

LT1614 Inverting Mode Switching Regulator with Low-Battery Detector –5V at 200mA from 5V Input in MSOP

LT1615 Micropower SOT-23 Step-Up DC/DC Converter 20µA Quiescent Current, V

LT1617 Micropower SOT-23 Inverting Regulator V

Up to –34V, 20µA Quiescent Current

OUT

Up to 34V

OUT

Burst Mode is a trademark of Linear Technology Corporation.

1611f LT/TP 0999 4K • PRINTED IN USA

LINEAR TECHNOLOGY CORPORATION 1998

12

Linear Technology Corporation

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 ● FAX: (408) 434-0507

●

www.linear-tech.com

Q

Loading...

Loading...