Page 1

LT1189

Low Power

Video Difference Amplifier

EATU

F

■

Differential or Single-Ended Gain Block (Adjustable)

■

–3dB Bandwidth, AV = ±10 35MHz

■

Slew Rate 220V/µs

■

Low Supply Current 13mA

■

Output Current ±20mA

■

CMRR at 10MHz 48dB

■

LT1193 Pin Out

■

Low Cost

■

Single 5V Operation

■

Drives Cables Directly

■

Output Shutdown

PPLICATI

A

■

Line Receivers

■

Video Signal Processing

■

Cable Drivers

■

Tape and Disc Drive Systems

RE

S

O

U

S

DUESCRIPTIO

The LT1189 is a difference amplifier optimized for operation on ± 5V, or a single 5V supply, and gain ≥10. This

versatile amplifier features uncommitted high input impedance (+) and (–) inputs, and can be used in differential

or single-ended configurations. Additionally, a second set

of inputs give gain adjustment and DC control to the

difference amplifier.

The LT1189’s high slew rate, 220V/µs, wide bandwidth,

35MHz, and ±20mA output current require only 13mA of

supply current. The shutdown feature reduces the power

dissipation to a mere 15mW, and allows multiple amplifiers to drive the same cable.

The LT1189 is a low power, gain of 10 stable version of the

popular LT1193, and is available in 8-pin miniDIPs and SO

packages. For lower gain applications see the LT1187

data sheet.

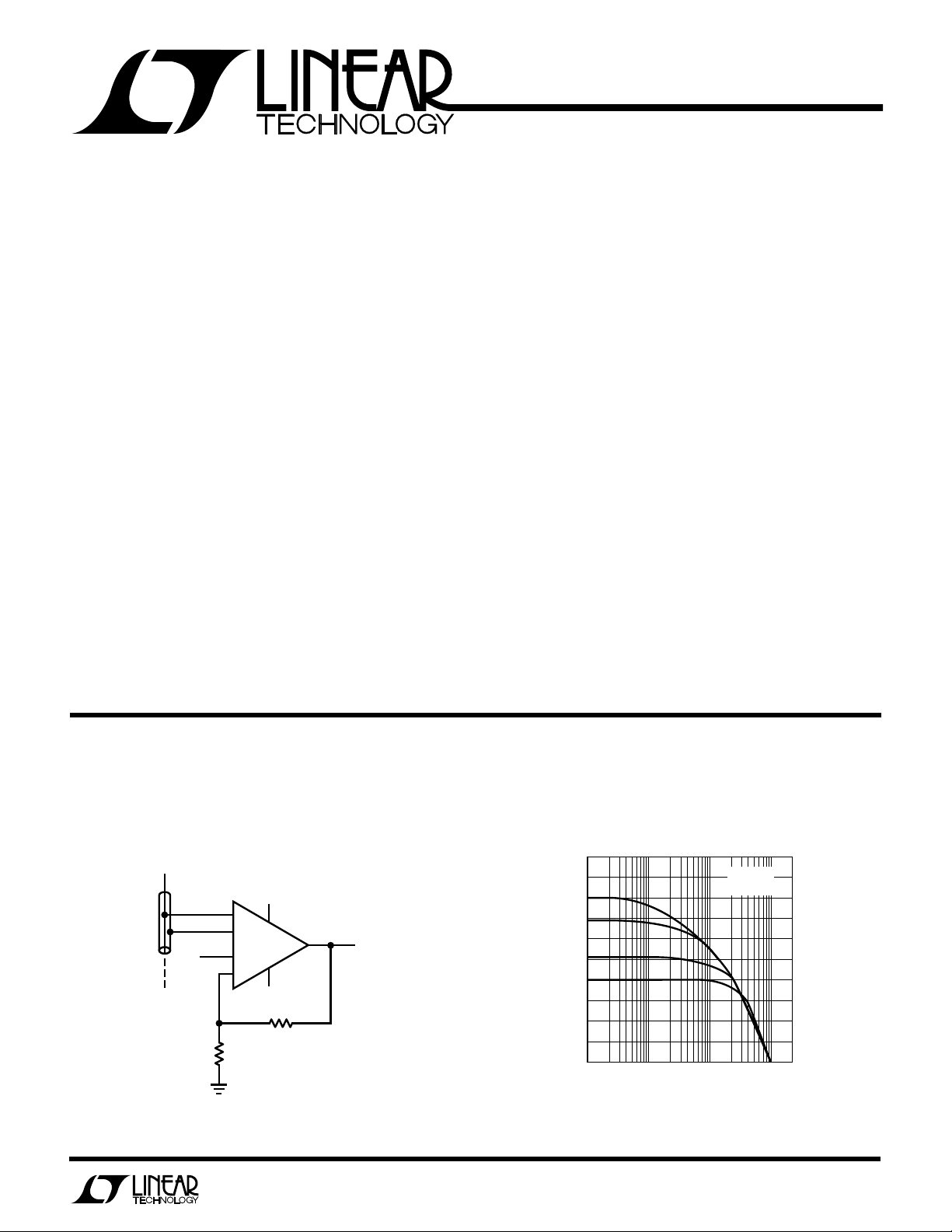

CABLE

U

O

A

PPLICATITYPICAL

Closed-Loop Gain vs FrequencyCable Sense Amplifier for Loop Through Connections

with DC Adjust

V

IN

5V

3

+

–

LT1189

+

–

–5V

7

4

909Ω

6

V

OUT

LT1189 • TA01

2

V

1

DC

8

100Ω

50

40

30

20

VOLTAGE GAIN (dB)

10

0

0.1 10 100

1

FREQUENCY (MHz)

VS = ±5V

= 1k

R

L

LT1189 • TA02

1

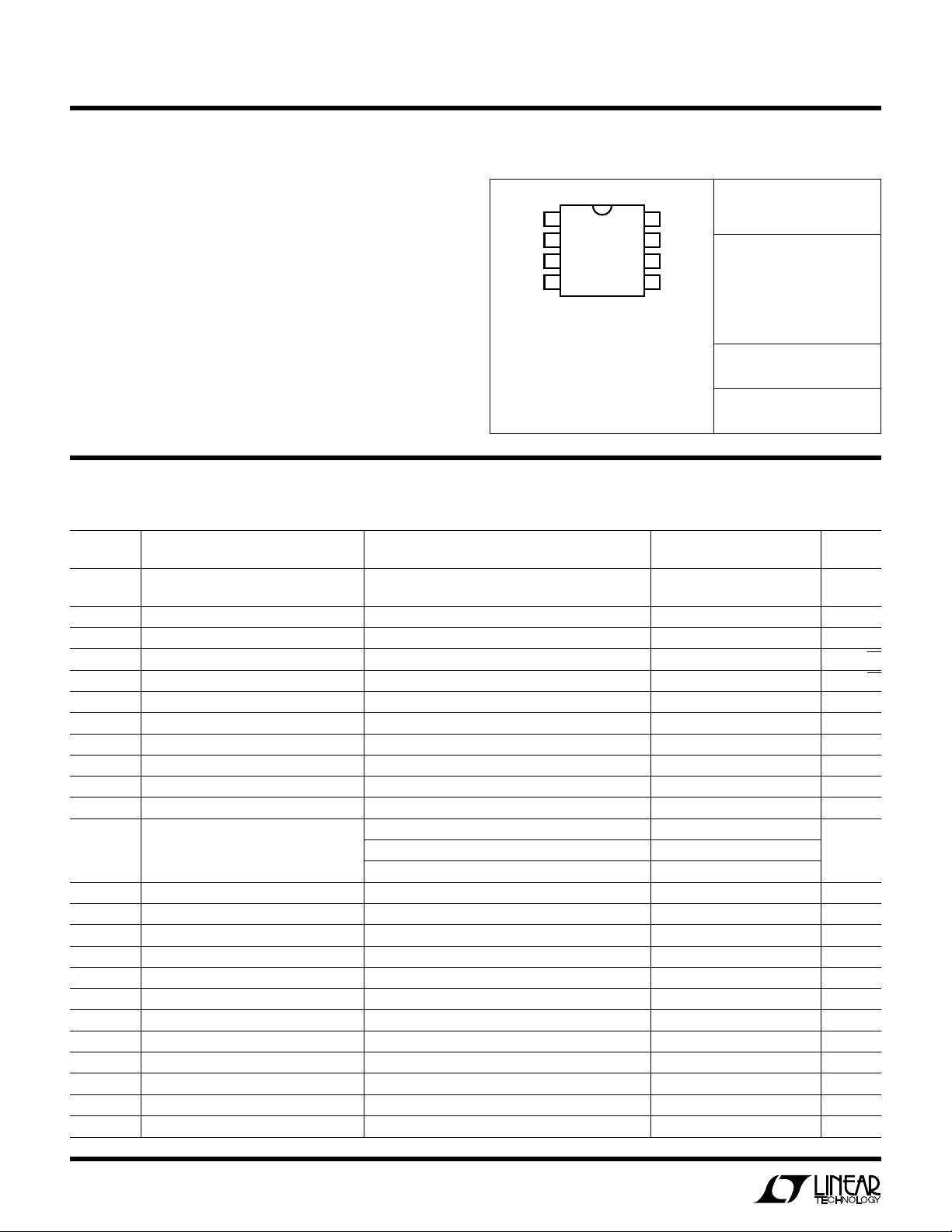

Page 2

LT1189

WU

U

PACKAGE

/

O

RDER I FOR ATIO

W

O

A

LUTEXI T

S

Total Supply Voltage (V+ to V–) ............................. 18V

Differential Input Voltage ........................................ ±6V

Input Voltage .......................................................... ±V

Output Short Circuit Duration (Note 1) ........ Continuous

Operating Temperature Range

LT1189M..................................... – 55°C to 150°C

LT1189C............................................. 0°C to 70°C

Junction Temperature (Note 2)

Plastic Package (CN8,CS8) ......................... 150°C

Ceramic Package (CJ8,MJ8) ....................... 175°C

Storage Temperature Range ................ – 65°C to 150°C

A

WUW

ARB

U

G

I

S

S

TOP VIEW

1+/REF

2

–IN

+IN

3

–

V

J8 PACKAGE

8-LEAD HERMETIC DIP

S8 PACKAGE

8-LEAD PLASTIC SOIC

T

= 175°C, θJA = 100°C/W (J8)

JMAX

T

= 150°C, θJA = 100°C/W (N8)

JMAX

T

= 150°C, θJA = 150°C/W (S8)

JMAX

–/FB

8

+

7

V

6

OUT

54

S/D

N8 PACKAGE

8-LEAD PLASTIC DIP

LT1189 • POI01

ORDER PART

NUMBER

LT1189MJ8

LT1189CJ8

LT1189CN8

LT1189CS8

S8 PART MARKING

1189

Lead Temperature (Soldering, 10 sec.)................ 300°C

+

5V

–

VS = ±5V, V

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OS

I

OS

I

B

e

n

i

n

R

IN

C

IN

VIN

LIM

CMRR Common-Mode Rejection Ratio VCM = –2.5V to 3.5V 80 105 dB

PSRR Power Supply Rejection Ratio VS = ±2.375V to ±8V 75 90 dB

V

OUT

G

E

SR Slew Rate (Note 6, 10) 150 220 V/µs

FPBW Full Power Bandwidth VO = 2V

BW Small Signal Bandwidth AV = 10 35 MHz

tr, t

f

t

PD

t

s

Diff A

Diff Ph Differential Phase RL = 1k, AV = 10, (Note 9) 0.75 DEG

I

S

LECTRICAL C CHARA TERIST

E

= 0V, R

REF

Input Offset Voltage Either Input, (Note 4) 1.0 3.0 mV

Input Offset Current Either Input 0.2 1.0 µA

Input Bias Current Either Input ±0.5 ±2.0 µA

Input Noise Voltage fO = 10kHz 30 nV/√Hz

Input Noise Current fO = 10kHz 1.25 pA/√Hz

Input Resistance Differential 30 kΩ

Input Capacitance Either Input 2.0 pF

Input Voltage Limit (Note 5) ±170 mV

Input Voltage Range –2.5 3.5 V

Output Voltage Swing VS = ±5V, RL = 1k, AV = 50 ±3.8 ±4.0 V

Gain Error VO = ±1.0V, AV = 10 1.0 3.5 %

Rise Time, Fall Time AV = 50, VO = ±1.5V, 20% to 80% (Note 10) 35 50 75 ns

Propagation Delay RL= 1k, VO = ±125mV, 50% to 50% 12 ns

Overshoot VO = ±50mV 10 %

Settling Time 3V Step, 0.1%, (Note 8) 1 µs

V

Differential Gain RL = 1k, AV = 10, (Note 9) 0.6 %

Supply Current 13 16 mA

Shutdown Supply Current Pin 5 at V

= 900Ω from pins 6 to 8, R

FB1

ICS

= 100Ω from pin 8 to ground, RL = R

FB2

SOIC Package 1.0 4.0 mV

VS = ±8V, RL = 1k, AV = 50 ±6.7 ±7.0

VS = ±8V, RL = 300Ω, AV = 50, (Note 3) ±6.4 ±6.8

P-P

–

TA = 25°C, (Note 3)

+ R

FB1

, (Note 7) 35 MHz

= 1k, CL ≤ 10pF, pin 5 open.

FB2

LT1189M/C

0.8 1.5 mA

P-P

2

Page 3

LT1189

+

5V

–

V

= ±5V, V

S

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

I

S/D

t

on

t

off

LECTRICAL C CHARA TERIST

E

= 0V, R

REF

Shutdown Pin Current Pin 5 at V

Turn On Time Pin 5 from V– to Ground, RL = 1k 500 ns

Turn Off Time Pin 5 from Ground to V–, RL = 1k 600 ns

= 900Ω from pins 6 to 8, R

FB1

ICS

= 100Ω from pin 8 to ground, RL = R

FB2

–

TA = 25°C, (Note 3)

FB1

+ R

= 1k, CL ≤ 10pF, pin 5 open.

FB2

LT1189M/C

525 µA

5V

V

LECTRICAL C CHARA TERIST

E

+

= 5V, V

S

–

= 0V, V

S

= 2.5V, R

REF

= 900Ω from pins 6 to 8, R

FB1

ICS

open.

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OS

I

OS

I

B

CMRR Common-Mode Rejection Ratio VCM = 2.0V to 3.5V 80 100 dB

V

OUT

SR Slew Rate VO = 1.5V to 3.5V 175 V/µs

BW Small-Signal Bandwidth AV = 10 30 MHz

I

S

I

S/D

+

5V

–

VS = ±5V, V

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OS

∆VOS/∆T Input V

I

OS

I

B

CMRR Common-Mode Rejection Ratio VCM = –2.5V to 3.5V 80 105 dB

PSRR Power Supply Rejection Ratio VS = ±2.375V to ±8V 65 90 dB

V

OUT

G

E

I

S

I

S/D

Input Offset Voltage Either Input, (Note 4) 1.0 3.0 mV

SOIC Package 1.0 5.0 mV

Input Offset Current Either Input 0.2 1.0 µA

Input Bias Current Either Input ±0.5 ±2.0 µA

Input Voltage Range 2.0 3.5 V

Output Voltage Swing RL = 300Ω to Ground V

(Note 3)

Supply Current 12 15 mA

Shutdown Supply Current Pin 5 at V

Shutdown Pin Current Pin 5 at V

LECTRICAL C CHARA TERIST

E

= 0V, R

REF

Input Offset Voltage Either Input, (Note 4) 1.0 7.5 mV

Input Offset Current Either Input 0.2 1.5 µA

Input Bias Current Either Input ±0.5 ±3.5 µA

Input Voltage Range –2.5 3.5 V

Output Voltage Swing VS = ±5V, RL = 1k, AV = 50 ±3.7 ±4.0 V

Gain Error VO = ±1V, AV = 10, RL = 1k 1.0 6.0 %

Supply Current 13 17 mA

Shutdown Supply Current Pin 5 at V–, (Note 11) 0.8 1.5 mA

Shutdown Pin Current Pin 5 at V

= 900Ω from pins 6 to 8, R

FB1

Drift 10 µV/°C

OS

= 100Ω from pin 8 to ground, RL = R

FB2

VS = ±8V, RL = 1k, AV = 50 ±6.6 ±7.0

VS = ±8V, RL = 300Ω, AV = 50, (Note 3) ±6.4 ±6.6

TA = 25°C, (Note 3)

= 100Ω from pin 8 to V

FB2

–

–

–55°C ≤ TA ≤ 125°C, (Note 3)

ICS

–

, RL = R

REF

High 3.6 4.0 V

OUT

V

Low 0.15 0.4

OUT

FB1

+ R

= 1k, CL ≤ 10pF, pin 5

FB2

LT1189M/C

0.8 1.5 mA

525 µA

= 1k, CL ≤ 10pF, pin 5 open.

LT1189M

525 µA

+ R

FB1

FB2

3

Page 4

LT1189

+

5V

–

V

= ±5V, V

S

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OS

∆VOS/∆T Input V

I

OS

I

B

CMRR Common-Mode Rejection Ratio VCM = –2.5V to 3.5V 80 105 dB

PSRR Power Supply Rejection Ratio VS = ±2.375V to ±8V 70 90 dB

V

OUT

G

E

I

S

I

S/D

5V

+

V

= +5V, V

S

open.

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OS

∆VOS/∆T Input V

I

OS

I

B

CMRR Common-Mode Rejection Ratio VCM = 2.0V to 3.5V 80 100 dB

V

OUT

I

S

I

S/D

Note 1: A heat sink may be required to keep the junction temperature below

absolute maximum when the output is shorted continuously.

Note 2: T

according to the following formulas:

P

D

Note 3: When R

= 300Ω is specified, then an additional 430Ω is added to the output such

R

L

that (R

Note 4: V

pair, and is input referred.

Note 5: V

pin 3) for which the output can respond.

LECTRICAL C CHARA TERIST

E

= 0V, R

REF

Input Offset Voltage Either Input 1.0 3.0 mV

(Note 4) SOIC Package 1.0 6.0 mV

Input Offset Current Either Input 0.2 1.5 µA

Input Bias Current Either Input ±0.5 ±3.5 µA

Input Voltage Range –2.5 3.5 V

Output Voltage Swing VS = ±5V, RL = 1k, AV = 50 ±3.7 ±4.0 V

Gain Error VO = ±1V, AV = 10, RL = 1k 1.0 3.5 %

Supply Current 13 17 mA

Shutdown Supply Current Pin 5 at V–, (Note 11) 0.8 1.5 mA

Shutdown Pin Current Pin 5 at V

LECTRICAL C CHARA TERIST

E

–

= 0V, V

S

Input Offset Voltage, (Note 4) Either Input 1.0 3.0 mV

Input Offset Current Either Input 0.2 1.5 µA

Input Bias Current Either Input ±0.5 ±3.5 µA

Input Voltage Range 2.0 3.5 V

Output Voltage Swing RL = 300Ω to Ground V

Supply Current 12 16 mA

Shutdown Supply Current Pin 5 at V, (Note 11) 0.8 1.5 mA

Shutdown Pin Current Pin 5 at V

is calculated from the ambient temperature TA and power dissipation

J

LT1189MJ8, LT1189CJ8: T

LT1189CN8: T

LT1189CS8: T

= 1k is specified, the load resistor is R

L

+ R

FB1

) in parallel with 430Ω is RL = 300Ω.

FB2

measured at the output (pin 6) is the contribution from both input

OS

is the maximum voltage between –VIN and +VIN (pin 2 and

IN LIM

= 900Ω from pins 6 to 8, R

FB1

Drift 5.0 µV/°C

OS

= 2.5V, R

REF

Drift 5.0 µV/°C

OS

= TA + (PD × 100°C/W)

J

= TA + (PD × 100°C/W)

J

= TA + (PD × 150°C/W)

J

= 900Ω from pins 6 to 8, R

FB1

FB2

VS = ±8V, RL = 1k, AV = 50 ±6.6 ±7.0

VS = ±8V, RL = 300Ω, AV = 50, (Note 3) ±6.4 ±6.6

(Note 3) V

+ R

FB1

, but when

FB2

ICS

0°C ≤ TA ≤ 70°C, (Note 3)

= 100Ω from pin 8 to ground, RL = R

–

ICS

0°C ≤ TA ≤ 70°C, (Note 3)

= 100Ω from pin 8 to V

FB2

–

Note 6: Slew rate is measured between ±1V on the output, with a V

±0.5V, A

V

Note 7: Full power bandwidth is calculated from the slew rate measurement:

FPBW = SR/2πVp.

Note 8: Settling time measurement techniques are shown in “Take the

Guesswork Out of Settling Time Measurements,” EDN, September 19, 1985.

Note 9: NTSC (3.58MHz).

Note 10: AC parameters are 100% tested on the ceramic and plastic DIP

packaged parts (J8 and N8 suffix) and are sample tested on every lot of the SO

packaged parts (S8 suffix).

Note 11: See Application section for shutdown at elevated temperatures. Do

not operate shutdown above T

REF

High 3.5 4.0 V

OUT

Low 0.15 0.4

OUT

= 10 and RL = 1k.

+ R

FB1

, RL = R

> 125°C.

J

= 1k, CL ≤ 10pF, pin 5 open.

FB2

LT1189C

525 µA

+ R

FB1

= 1k, CL ≤ 10pF, pin 5

FB2

LT1189C

525 µA

IN

step of

4

Page 5

LT1189

UW

Y

PICA

3.0

2.5

µ

2.0

1.5

1.0

0.5

INPUT BIAS CURRENT ( A)

0

–0.5

–5

200

√

180

160

140

120

100

80

60

40

20

EQUIVALENT INPUT NOISE VOLTAGE (nV/ Hz)

0

LPER

F

O

R

AT

CCHARA TERIST

E

C

ICS

Input Bias Current vs Common-Mode Voltage vs

Common-Mode Voltage Input Bias Current vs Temperature Temperature

+

VS = ±5V

–55°C

25°C

125°C

–3 0 2 4

–4 –2 1 3

–1 5

COMMON-MODE VOLTAGE (V)

LT1189 • TPC01

100

VS = ±5V

0

–100

I

–200

INPUT BIAS CURRENT (nA)

–300

–400

–50

OS

0 25 75 125

–25 50 100

TEMPERATURE (°C)

+I

B

–I

B

LT1189 • TPC02

V

–0.5

–1.0

–1.5

–2.0

2.0

1.5

COMMON-MODE RANGE (V)

1.0

0.5

–

V

–50 25 75 125

–25 50 100

V+ = 1.8V TO 9V

V+ = –1.8V TO –9V

0

TEMPERATURE (°C)

Equivalent Input Noise Voltage vs Equivalent Input Noise Current vs

Frequency Frequency Supply Current vs Supply Voltage

V = ±5V

S

T = 25°C

A

Ω

R = 0

S

10 1k 10k 100k

100

FREQUENCY (Hz)

LT1189 • TPC04

12

√

10

8

6

4

2

EQUIVALENT INPUT NOISE CURRENT (pA/ Hz)

0

10 1k 10k 100k

100

FREQUENCY (Hz)

VS = ±5V

= 25°C

T

A

= 100k

R

S

LT1189 • TPC05

16

14

12

SUPPLY CURRENT (mA)

10

8

246 10

0

±SUPPLY VOLTAGE (V)

–55°C

25°C

125°C

LT1189 • TPC03

8

LT1189 • TPC06

Shutdown Supply Current vs

Temperature Gain Error vs Temperature Open-Loop Gain vs Temperature

6.0

V = ±5V

S

5.0

V

= –V

+ 0.6V

S/D

4.0

3.0

2.0

1.0

SHUTDOWN SUPPLY CURRENT (mA)

0

–50

EE

V

S/D

V

= –V

EE

+ 0.2V

S/D

0 25 75 125

–25 50 100

TEMPERATURE (°C)

= –V

V

S/D

+ 0.4V

EE

= –V

EE

LT1189 • TPC07

–1.2

VS = ±5V

= ±1V

V

OUT

–1.4

= 10

A

V

= 1k

R

L

–1.6

–1.8

–2.0

GAIN ERROR (%)

–2.2

–2.4

–50

–25 25 75

0 50 100 125

TEMPERATURE (°C)

LT1189 • TPC08

16

VS = ±5V

14

= ±3V

V

O

12

10

8

6

4

OPEN-LOOP GAIN (kV/V)

2

0

–25 25 75

–50 0 50 100 125

TEMPERATURE (°C)

RL = 1k

RL = 500Ω

LT1189 • TPC09

5

Page 6

LT1189

FREQUENCY (Hz)

COMMON-MODE REJECTION RATIO (dB)

50

60

70

80

100k 10M 100M

LT1189 • TPC15

30

1M

40

90

VS = ±5V

T

A

= 25°C

R

L

= 1k

±SUPPLY VOLTAGE (V)

0

100

GAIN BANDWIDTH PRODUCT (MHz)

150

200

250

24 810

LT1189 • TPC12

6

TA = 25°C

TA = 125°C

TA = –55°C

AV = 20dB

±SUPPLY VOLTAGE (V)

OUTPUT SATURATION VOLTAGE (V)

V

+

LT1189 • TPC18

V

–

0.3

–0.8

–0.7

0.2

0246 108

–0.9

–1.0

0.4

0.5

0.1

–1.1

–55°C

125°C

25°C

–55°C

125°C

25°C

RL = 1k

±1.8V ≤ V

S

≤ ±9V

UW

Y

PICA

100

80

60

40

LPER

F

O

R

AT

CCHARA TERIST

E

C

ICS

Open-Loop Voltage Gain vs Gain Bandwidth Product vs

Gain, Phase vs Frequency Load Resistance Supply Voltage

PHASE

GAIN

VS = ±5V

= 25°C

T

A

= 1k

R

L

100

80

60

40

30

VS = ±5V

V

O

T

PHASE MARGIN (DEG)

A

20

= ±3V

= 25°C

20

VOLTAGE GAIN (dB)

0

–20

100k

1M 10M 100M

FREQUENCY (Hz)

LT1189 • TPC11

20

0

–20

10

OPEN-LOOP VOLTAGE GAIN (kV/V)

0

100

1k 10k

LOAD RESISTANCE (Ω)

LT1189• TPC10

Gain Bandwidth Product and Common-Mode Rejection Ratio

Phase Margin vs Temperature Output Impedance vs Frequency vs Frequency

250

200

GAIN BANDWIDTH

PRODUCT

150

GAIN BANDWIDTH PRODUCT (MHz)

100

–25 25 75

–50

PHASE MARGIN

0 50 100 125

TEMPERATURE (°C)

V = ±5V

S

R = 1k

L

= 20dB

A

V

LT1189 • TPC13

85

75

65

55

100

VS = ±5V

= 25°C

T

A

A

= 10

PHASE MARGIN (DEG)

V

Ω

10

1

OUTPUT IMPEDANCE ( )

0.1

1k

10k 100k 1M 10M 100M

FREQUENCY (Hz)

LT1189 • TPC14

Power Supply Rejection Ratio vs Output Short Circuit Current vs

Frequency Temperature ± Output Swing vs Supply Voltage

80

60

40

20

0

POWER SUPPLY REJECTION RATIO (dB)

–20

1k 100k 10M 100M

6

+PSRR

–PSRR

10k 1M

FREQUENCY (Hz)

VS = ±5V

= 25°C

T

A

V

RIPPLE

= ±300mV

LT1189 • TPC16

36

35

34

33

32

31

OUTPUT SHORT CIRCUIT CURRENT (mA)

30

–50

–25 50 100

0 25 75 125

TEMPERATURE (°C)

VS = ±5V

LT1189 • TPC17

Page 7

Y

PICA

LPER

F

O

R

AT

UW

CCHARA TERIST

E

C

LT1189

ICS

Output Voltage Swing vs

Load Resistance

5

VS = ±5V

3

1

–1

–3

OUTPUT VOLTAGE SWING (V)

–5

TA = –55°C

TA = 25°C

TA = –55°C

TA = 25°C

10

LOAD RESISTANCE (Ω)

Output Voltage Step vs

Settling Time, AV = 10

4

VS = ±5V

= 25°C

T

A

= 1k

R

L

2

0

–2

OUTPUT VOLTAGE STEP (V)

10mV

TA = 25°C

TA = 25°C

100 1000

LT1189 • TPC19

10mV

Slew Rate vs Temperature

300

–SLEW RATE

µ

250

SLEW RATE (V/ s)

VS = ±5V

= 1k

R

L

= ±2V

V

O

= 10

A

V

200

–50

–25 0 50 7525 100 125

TEMPERATURE (°C)

Harmonic Distortion vs

Output Level

0

VS = ±5V

= 25°C

T

A

–10

= 1k

R

L

f = 10MHz

= 10

A

V

–20

–30

–40

DISTORTION (dBc)

–50

+SLEW RATE

LT1189 • TPC20

HD

HD

3

2

–4

100

180 220 260 300

140 340

SETTLING TIME (ns)

Large-Signal Transient Reponse

AV = 10, RL = 1k, +SR = 223V/µs, –SR = 232V/µs

LT1189 • TPC21

LT1189 • TPC23

–60

0

12

OUTPUT VOLTAGE (V

P-P

Small-Signal Transient Reponse

AV = 10, RL = 1k, tr = 9.40ns

3

)

LT1189 • TPC22

4

LT1189 • TPC24

7

Page 8

LT1189

PPLICATI

A

U

O

S

I FOR ATIO

WU

U

The primary use of the LT1189 is in converting high speed

differential signals to a single-ended output. The LT1189

video difference amplifier has two uncommitted high input

impedance (+) and (–) inputs. The amplifier has another

set of inputs which can be used for reference and feedback. Additionally, this set of inputs give gain adjust, and

DC control to the differential amplifier. The voltage gain of

the LT1189 is set like a conventional operational amplifier.

Feedback is applied to pin 8, and it is optimized for gains

of 10 or greater. The amplifier can be operated singleended by connecting either the (+) or (–) inputs to the

+/REF (pin 1). The voltage gain is set by the resistors:

(RFB + RG)/RG.

Like the single-ended case, the differential voltage gain is

set by the external resistors: (RFB + RG)/RG. The maximum

input differential signal for which the output will respond

is approximately ±170mV.

S/D

+

V

5

3

V

IN

2

1

8

+

–

+/REF

–/FB

LT1189

V

R

7

6

V

OUT

4

–

FB

V

S/D

+

V

5

3

2

IN

1

8

+

–

+/REF

–/FB

LT1189

V

R

7

6

V

OUT

4

–

FB

Power Supply Bypassing

The LT1189 is quite tolerant of power supply bypassing.

In some applications a 0.1µF ceramic disc capacitor

placed 1/2 inch from the amplifier is all that is required. In

applications requiring good settling time, it is important to

use multiple bypass capacitors. A 0.1µF ceramic disc in

parallel with a 4.7µF tantalum is recommended.

Calculating the Output Offset Voltage

Both input stages contribute to the output offset voltage at

pin 6. The feedback correction forces balance in the input

stages by introducing an Input VOS at pin 8. The complete

expression for the output offset voltage is:

V

= ( VOS + IOS(RS) + IB(R

OUT

)) × (RFB + RG)/RG + IB(RFB)

REF

RS represents the input source resistance, typically 75Ω,

and R

DC reference voltage, for V

represents finite source impedance from the

REF

grounded, R

REF

= 0Ω the

REF

IOS is normally a small contributor and the expression

simplifies to:

V

= VOS(RFB + RG)/RG + IB(RFB)

OUT

If RFB is limited to 1k, the last term of the equation

contributes only 2mV since IB is less than 2µA.

V

IN DIFF

8

+

R

R

G

FB

AV= +

R

G

S/D

5

3

+

2

–

LT1189

1

V

+/REF

IN

8

–/FB

VO= (V

R

G

R

G

+

V

7

6

V

OUT

4

–

V

R

FB

+ VIN)

IN DIFF

V

V

IN

+

R

R

G

FB

R

G

IN DIFF

R

G

VO=

R

AV= –

G

S/D

5

3

+

2

–

LT1189

1

+/REF

8

–/FB

+

R

R

G

FB

(

R

G

V

V

R

V

(

+

7

4

–

FB

IN DIFF

+

R

R

G

FB

R

–

G

6

R

FB

(

R

G

LT1189 • AI01

2

–

R

S

Q1 Q2

RE

300

345µA

+

V

OUT

3

+

R

S

V

IN

(

1

REF

R

REF

Q3 Q4

RE

300

350µA

7V

8

4V

+

–

R

R

G

LT1189 • AI02

6

FB

Figure 1. Simplified Input Stage Schematic

Page 9

LT1189

PPLICATI

A

U

O

S

I FOR ATIO

WU

U

Instrumentation Amplifier Rejects High Voltage

Instrumentation amplifiers are often used to process

slowly varying outputs from transducers. With the LT1189

it is easy to make an instrumentation amplifier that can

respond to rapidly varying signals. Attenuation resistors

in front of the LT1189 allow very large common-mode

signals to be rejected while maintaining good frequency

response. The input common-mode and differential-mode

signals are reduced by 100:1, while the closed-loop gain

is set to be 100, thereby maintaining unity-gain input to

output. The unique topology allows for frequency response boost by adding 150pF to pin 8 as shown.

3.5MHz Instrumentation Amplifier Rejects 120V

10k*

V

IN

V

CM

120V

P-P

* 0.1% RESISTORS

WORST CASE CMRR = 48dB

Output of Instrumentation Amplifier with 1MHz Square Wave

10k*

Riding on 120V

100*

100*

150pF

100Ω

at the Input

P-P

5V

2

+

1

REF

LT1189

3

–

8

FB

–5V

10k

P-P

7

6

4

LT1189 • AI03

High Voltage Instrumentation Amplifier Response

20

DIFFERENTIAL-MODE RESPONSE

0

–20

VOLTAGE GAIN (dB)

–40

–60

COMMON-MODE RESPONSE

FREQUENCY (Hz)

LT1189 • AI05

100M10M1M100k

Operating with Low Closed-Loop Gain

The LT1189 has been optimized for closed-loop gains of

10 or greater. The amplifier can be operated at much lower

closed-loop gains with the aid of a capacitor CFB across

the feedback resistor, (feedback zero). This capacitor

lowers the closed-loop 3dB bandwidth. The bandwidth

cannot be made arbitrarily low because CFB is a short at

high frequency and the amplifier will appear configured

unity-gain. As an approximate guideline, make BW × A

VCL

= 200MHz. This expression expands to:

A

VCL

2

π

RC

()()

FB FB

200

=

MHz

or:

A

C

=

FB

200 2π

()()()

VCL

MHz R

FB

LT1189 • AI04

The effect of the feedback zero on the transient and

frequency response is shown for AV = 4.

9

Page 10

LT1189

PPLICATI

A

U

O

S

I FOR ATIO

WU

Closed-Loop Voltage Gain vs Frequency

30

20

10

0

VS = ±5V

= 25°C

T

A

= 4

A

–10

V

= 900Ω

R

CLOSED-LOOP VOLTAGE GAIN (dB)

–20

FB

R

G

= 300Ω

FREQUENCY (Hz)

CFB = 0pF

CFB = 5pF

100M10M1M100k

LT1189 • AI06

Small-Signal Transient Response

U

Reducing the Closed-Loop Bandwidth

Although it is possible to reduce the closed-loop bandwidth by using a feedback zero, instability can occur if the

bandwidth is made too low. An alternate technique is to do

differential filtering at the input of the amplifier. This

technique filters the differential input signal, and the

differential noise, but does not filter common-mode noise.

Common-mode noise is rejected by the LT1189’s CMRR.

10MHz Bandwidth Limited Amplifier

R1

110Ω

SIG

eN

D

eN

CM

C1

68pF

R2

110Ω

3

2

1

8

100Ω

+

–

REF

FB

5V

7

LT1189

4

–5V

909Ω

6

A

f

V

V

–3dB

OUT

= 10

V

OUT

1

=

2π(R1 + R2)C1

SIG + eN

=

FILTER

D

eN

CM

+

CMR

LT1189 • AI09

AV = 4, RFB = 910Ω, RG = 300Ω

Small-Signal Transient Response

AV = 4, RFB = 910Ω, RG = 300Ω, CFB = 5pF

LT1189 • AI07

LT1189 • AI08

Using the Shutdown Feature

The LT1189 has a unique feature that allows the amplifier

to be shutdown for conserving power, or for multiplexing

several amplifiers onto a common cable. The amplifier will

shutdown by taking pin 5 to V–. In shutdown, the amplifier

dissipates 15mW while maintaining a true high impedance

output state of about 20kΩ in parallel with the feedback

resistors. For MUX applications, the amplifiers may be

configured inverting, non-inverting, or differential. When

the output is loaded with as little as 1kΩ from the amplifier’s

feedback resistors, the amplifier shuts off in 600ns. This

shutoff can be under the control of HC CMOS operating

between 0V and –5V.

10

Page 11

LT1189

PPLICATI

A

1MHz Sine Wave Gated Off with Shutdown Pin

SHUTDOWN

V

OUT

AV = 10, RFB = 900Ω, RG = 100Ω

A

U

O

S

I FOR ATIO

WU

U

The ability to maintain shutoff is shown on the curve Shut

down Supply Current vs Temperature in the Typical Performance Characteristics section. At very high elevated

temperature it is important to hold the shutdown pin close

to the negative supply to keep the supply current from

increasing.

LT1189 • AI10

U

O

PPLICATITYPICAL

Differential Receiver MUX for Power Down Applications

CABLE 1

CABLE 2

15k

15k

1.5k

CMOS IN

CHANNEL SELECT

1k

15k

1.5k

15k

1.5k

1.5k

3

+

2

–

1

V

REF

DC

8

FB

1k

100Ω

74HC04 74HC04

1k

3

+

2

–

1

V

REF

DC

8

FB

100Ω

LT1189

5

5

LT1189

1k

5V

–5V

5V

–5V

7

6

4

V

OUT

–5V

7

6

4

1% RESISTORS WORST CASE CMRR = 28dB

TYPICALLY 35dB

LT1189 • TA03

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

11

Page 12

LT1189

+

–

OUT

V

BIAS

V

LT1189 • SS

BIAS

V

M

C

FF

C

+V+V

3

2

5

1

+/REF

S/D

6

*

V

7

+

V

4

–

* SUBSTRATE DIODE, DO NOT FORWARD BIAS

8

–/FB

E

W

A

W

SPL

I

IIFED S

CH

PACKAGEDESCRIPTI

0.290 – 0.320

(7.366 – 8.128)

J8 Package

8-Lead Hermetic DIP

0.008 – 0.018

(0.203 – 0.460)

0.385 ± 0.025

(9.779 ± 0.635)

0.300 – 0.320

(7.620 – 8.128)

TI

O

C

U

Dimensions in inches (millimeters) unless otherwise noted.

0.200

0.015 – 0.060

0.100 ± 0.010

(5.080)

MAX

0.125

3.175

MIN

0° – 15°

CORNER LEADS OPTION

(4 PLCS)

0.023 – 0.045

(0.58 – 1.14)

HALF LEAD

OPTION

0.045 – 0.065

(1.14 – 1.65)

FULL LEAD

OPTION

0.045 – 0.065

(1.14 – 1.65)

0.014 – 0.026

(0.360 – 0.660)

0.045 – 0.065

(1.143 – 1.651)

(0.381 – 1.524)

(2.540 ± 0.254)

0.130 ± 0.005

(3.302 ± 0.127)

0.005

(0.127)

MIN

0.025

(0.635)

RAD TYP

0.405

(10.287)

MAX

0.400

(10.160)

MAX

65

3

87

12

876

4

5

0.220 – 0.310

(5.588 – 7.874)

× 45°

0.008 – 0.010

(0.203 – 0.254)

0.065

(1.651)

TYP

0.045 ± 0.015

(1.143 ± 0.381)

0.100 ± 0.010

(2.540 ± 0.254)

0.053 – 0.069

(1.346 – 1.752)

0.014 – 0.019

(0.355 – 0.483)

0.125

(3.175)

MIN

0.018 ± 0.003

(0.457 ± 0.076)

(1.270)

0.004 – 0.010

(0.101 – 0.254)

0.050

BSC

0.020

(0.508)

MIN

0.228 – 0.244

(5.791 – 6.197)

1234

0.189 – 0.197

(4.801 – 5.004)

7

8

1

2

5

6

3

4

0.250 ± 0.010

(6.350 ± 0.254)

0.150 – 0.157

(3.810 – 3.988)

N8 Package

8-Lead Plastic DIP

S8 Package

8-Lead Plastic SOIC

0.009 – 0.015

(0.229 – 0.381)

+0.025

0.325

–0.015

+0.635

8.255

()

–0.381

0.010 – 0.020

(0.254 – 0.508)

0°– 8° TYP

0.016 – 0.050

0.406 – 1.270

Linear Technology Corporation

12

1630 McCarthy Blvd., Milpitas, CA 95035-7487

(408) 432-1900

●

FAX

: (408) 434-0507

●

TELEX

: 499-3977

LINEAR TECHNOLOGY CORPORATION 1993

BA/LT/GP 0293 10K REV 0

Loading...

Loading...