Page 1

Data Sheet

LRS1331

Stacked Chip

16M Flash Memory and 4M SRAM

FEATURES

• Flash Memory and SRAM

• Stacked Die Chip Scale Package

• 72-ball 8 mm × 11 mm CSP plastic package

• Power supply: 2.7 V to 3.6 V

• Operating temperature: -25°C to +85°C

•Flash Memory

– Access time (MAX.): 90 ns

– Operating current (MAX.)

(The current for F-V

– Read: 25 mA (t

CYCLE

pin and F-V

CC

= 200 ns)

CCW

pin):

– Word write: 57 mA

– Block erase: 42 mA

– Standby current (the current for F-V

(MAX. F-RP

≤ GND ± 0.2 V)

pin): 15 µA

CC

– Optimized array blocking architecture

– Two 4K-word boot blocks

– Six 4K-word parameter blocks

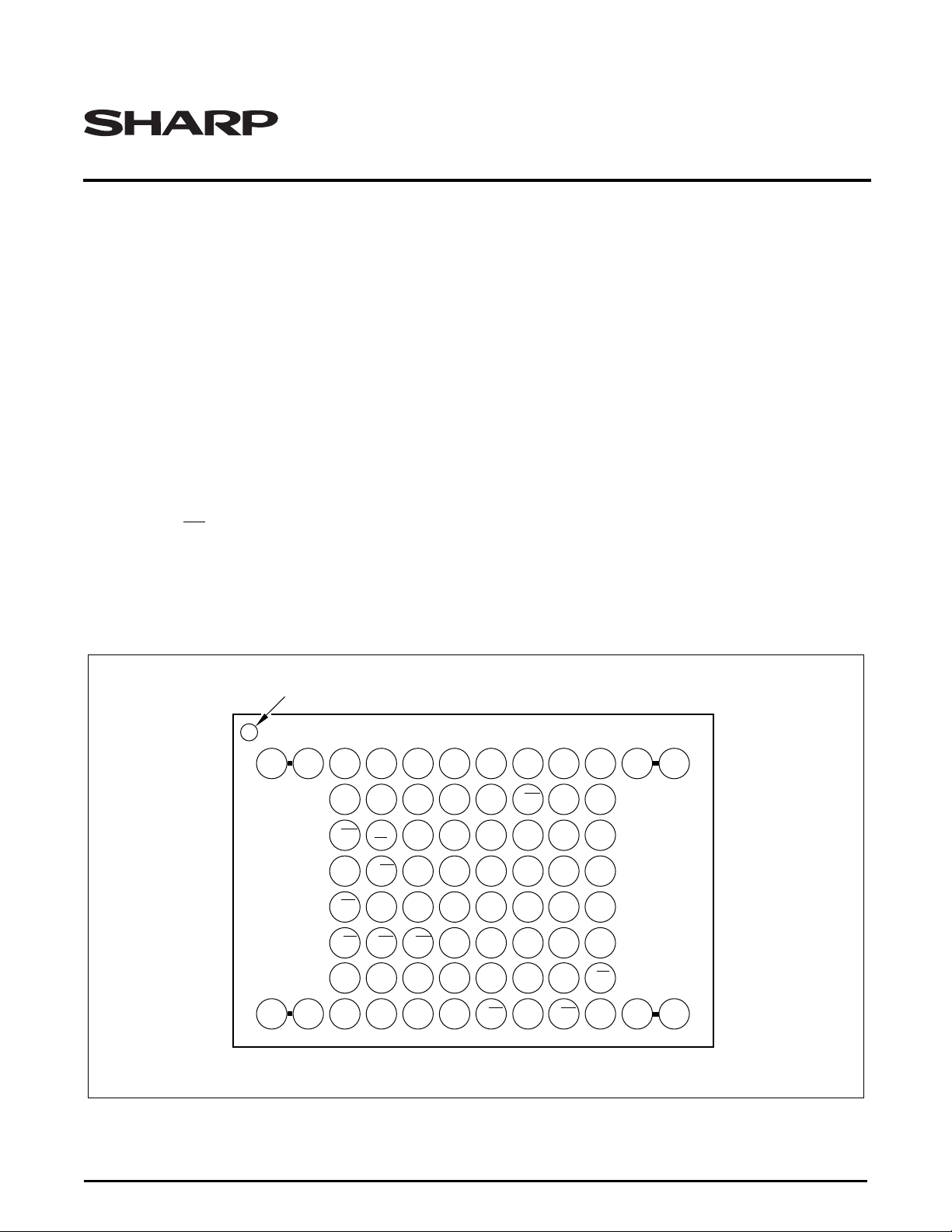

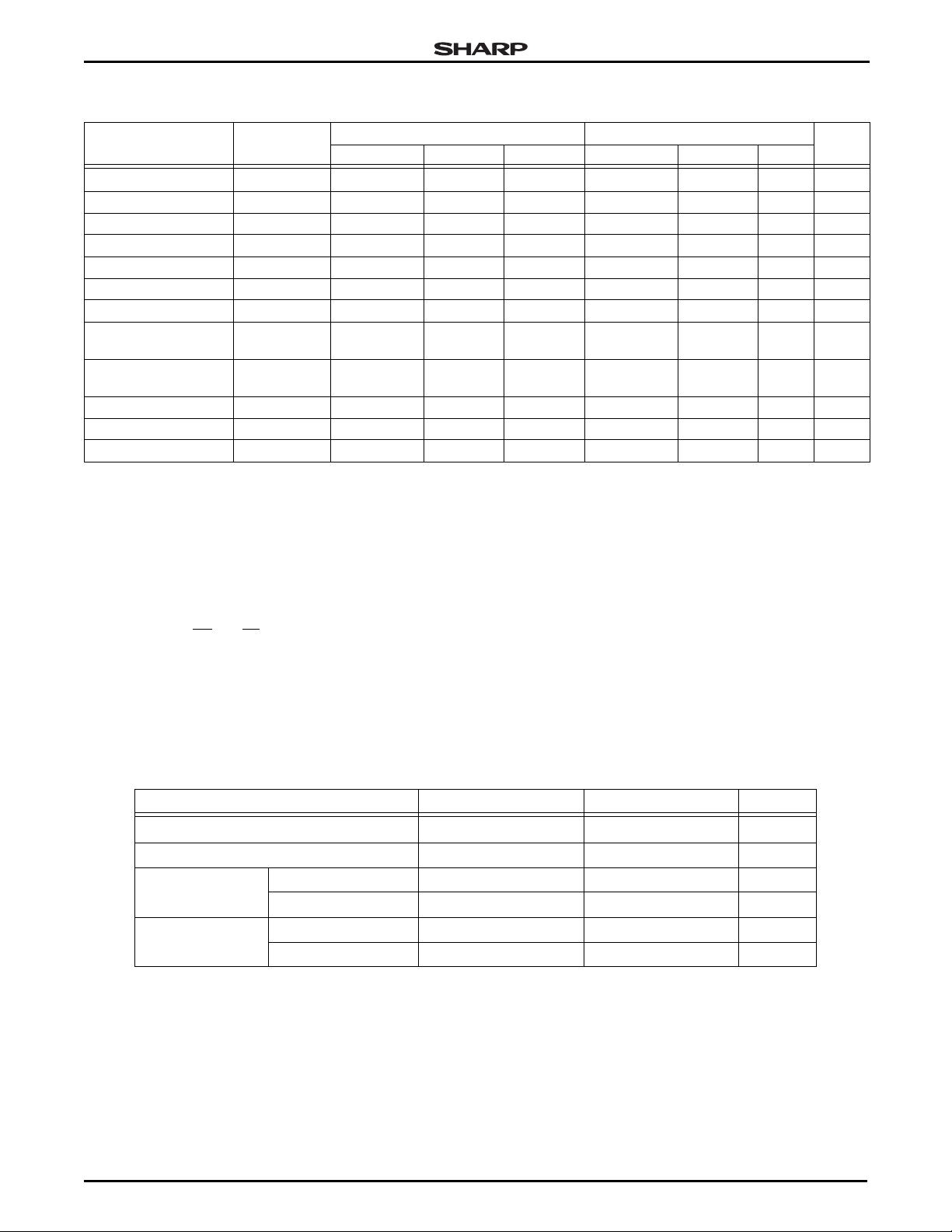

PIN CONFIGURATION

INDEX

– Thirty-one 32K-word main blocks

– Bottom boot location

– Extended cycling capability

– 100,000 block erase cycles

– Enhanced automated suspend options

– Word write suspend to read

– Block erase suspend to word write

– Block erase suspend to read

•SRAM

– Access time (MAX.): 85 ns

– Operating current: 45 mA (MAX.)

– Standby current: 15 µA (MAX.)

– Data retention current: 2 µA (MAX.)

DESCRIPTION

The LRS1331 is a combination memory organized as

1,048,576 × 16-bit flash memory and 262,144 × 16-bit

static RAM in one package.

TOP VIEW72-BALL FBGA

1234567

A

NC NC NC A

B

C

D

E

F

G

NC NC

H NC A5A4A

NOTE: All F-GND and S-GND pins are connected on the board.

Two NC pins at the corner are connected.

A11A

15

A

A8A

16

F-RY/

F-WE

GND

F-RP T

F-WP

F-VPPF-A19DQ11T

S-LB

S-UB

F-A18F-A17A7A6A3A

BY

10

T

1

2

S-OE

Figure 1. LRS1331 Pin Configuration

A

14

A

DQ

9

S-A17DQ

DQ

T

4

NC DQ

0

8

910

F-GND

A

12

13

DQ

S-WE

3

15

13

12

9

DQ

S-CE

DQ

DQ

F-GND

14

DQ

6

4

S-V

CC

2

DQ

10

2

DQ

8

0

A

2

1

F-OEF-CE

DQ

DQ

F-V

DQ

DQ

S-CE

11

12

NCNC

NC

7

5

CC

3

1

1

NCNC

NC

LRS1331-1

Data Sheet 1

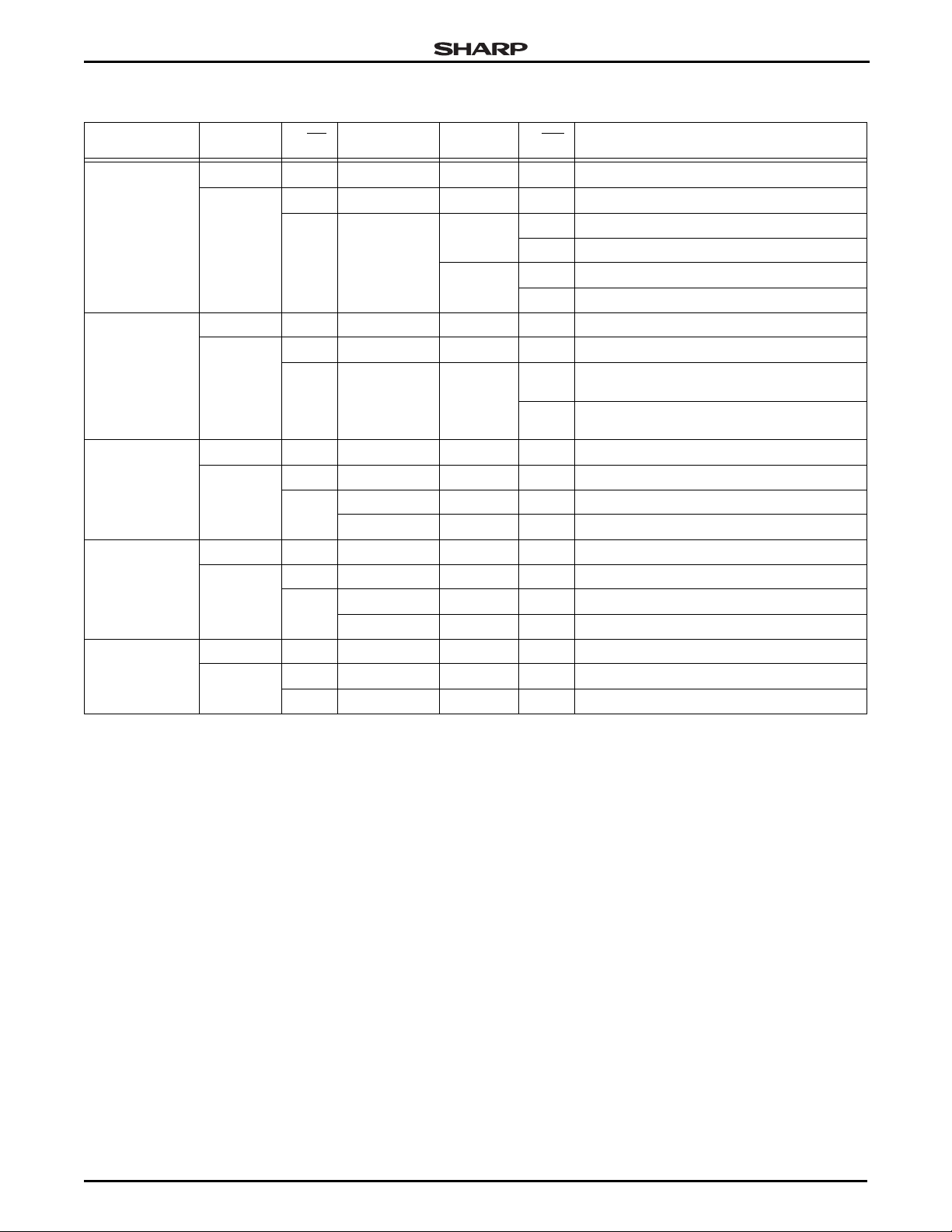

Page 2

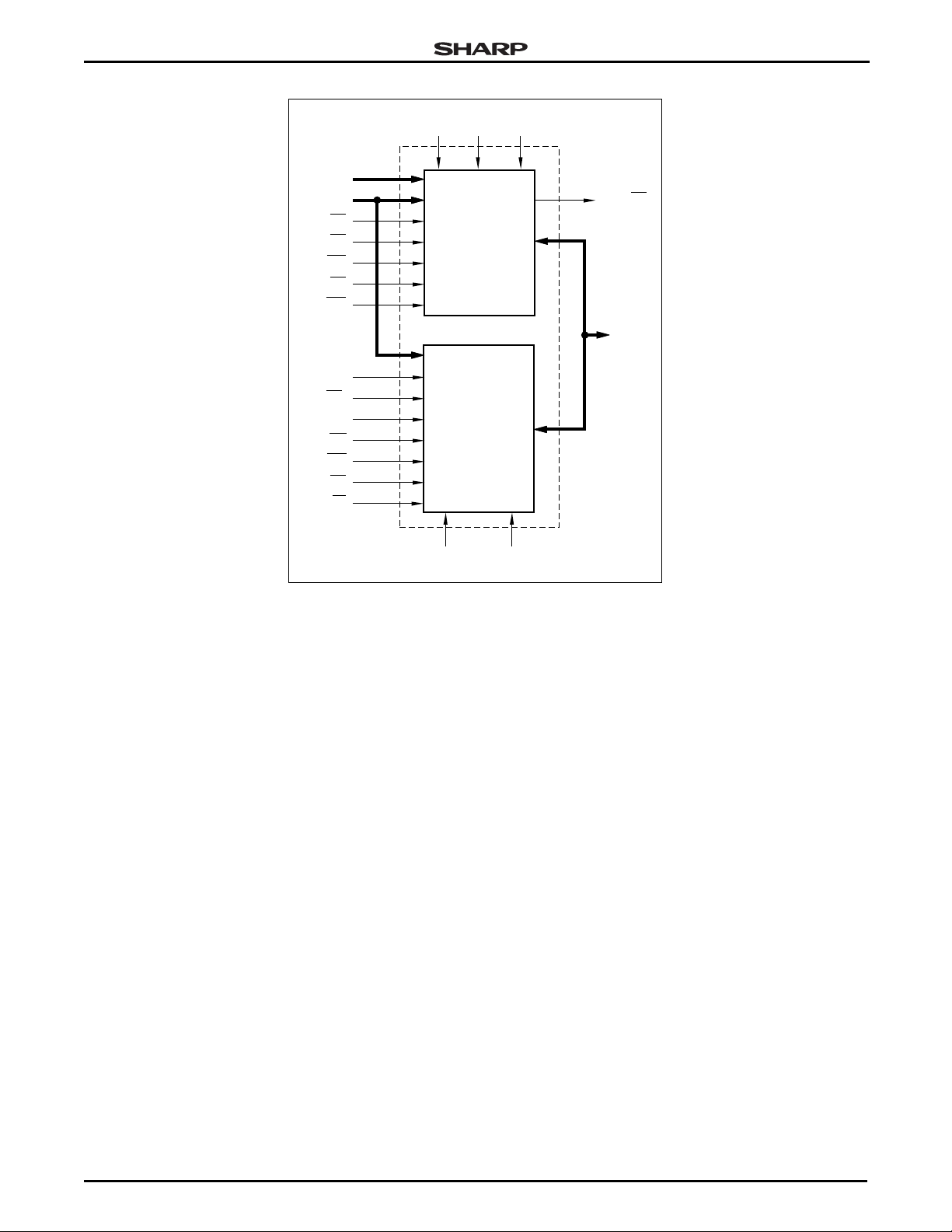

LRS1331 Stacked Chip (16M Flash & 4M SRAM)

F-V

PP

SRAM

F-GND

F-RY/BY

DQ

0

DQ

15

to

A

F-A

F-A

0

to A

17

19

F-CE

F-OE

F-WE

F-RP

F-WP

S-A

S-CE

S-CE

S-OE

S-WE

S-UB

S-LB

to

F-V

CC

16

16M (x16) BIT

FLASH MEMORY

17

1

2

4M (x16) BIT

S-GNDS-V

CC

Figure 2. LRS1331 Block Diagram

LRS1331-2

2 Data Sheet

Page 3

Stacked Chip (16M Flash & 4M SRAM) LRS1331

Table 1. Pin Descriptions

PIN DESCRIPTION TYPE

A

to A

0

16

to F-A

F-A

17

S-A

17

F-CE

, S-CE2Chip Enable Inputs (SRAM) Input

S-CE

1

F-WE

S-WE

F-OE

S-OE

S-LB

S-UB

Address Inputs (Common) Input

Address Inputs (Flash) Input

19

Address Input (SRAM) Input

Chip Enable Input (Flash) Input

Write Enable Input (Flash) Input

Write Enable Input (SRAM) Input

Output Enable Input (Flash) Input

Output Enable Input (SRAM) Input

SRAM Byte Enable Input (DQ0 to DQ7) Input

SRAM Byte Enable Input (DQ8 to DQ15) Input

Deep Power Down Input (Flash)

F-RP

F-WP

Block erase and Word Write: V

Read: V

Deep Power Down: V

IH

IL

Write Protect Input (Flash)

Two Boot Blocks Locked: V

IH

Input

Input

IL

Ready/Busy Output(Flash)

F-RY/BY

to DQ

DQ

0

F-V

S-V

CC

CC

During an Erase or Write operation: V

Block Erase and Word Write Suspend: HIGH-Z

Deep Power Down: V

Data Input and Outputs (Common) Input/Output

15

OH

Power Supply (Flash) Power

Power Supply (SRAM) Power

OL

Output

Write, Erase Power Supply (Flash)

F-V

PP

Block Erase and Word Write: F-V

All Blocks Locked: F-VPP < V

PPLK

PP

= V

PPLK

Power

F-GND Ground (Flash) Power

S-GND Ground (SRAM) Power

NC No Connection —

T

to T

1

5

Test Pins (Should be Open) —

Data Sheet 3

Page 4

LRS1331 Stacked Chip (16M Flash & 4M SRAM)

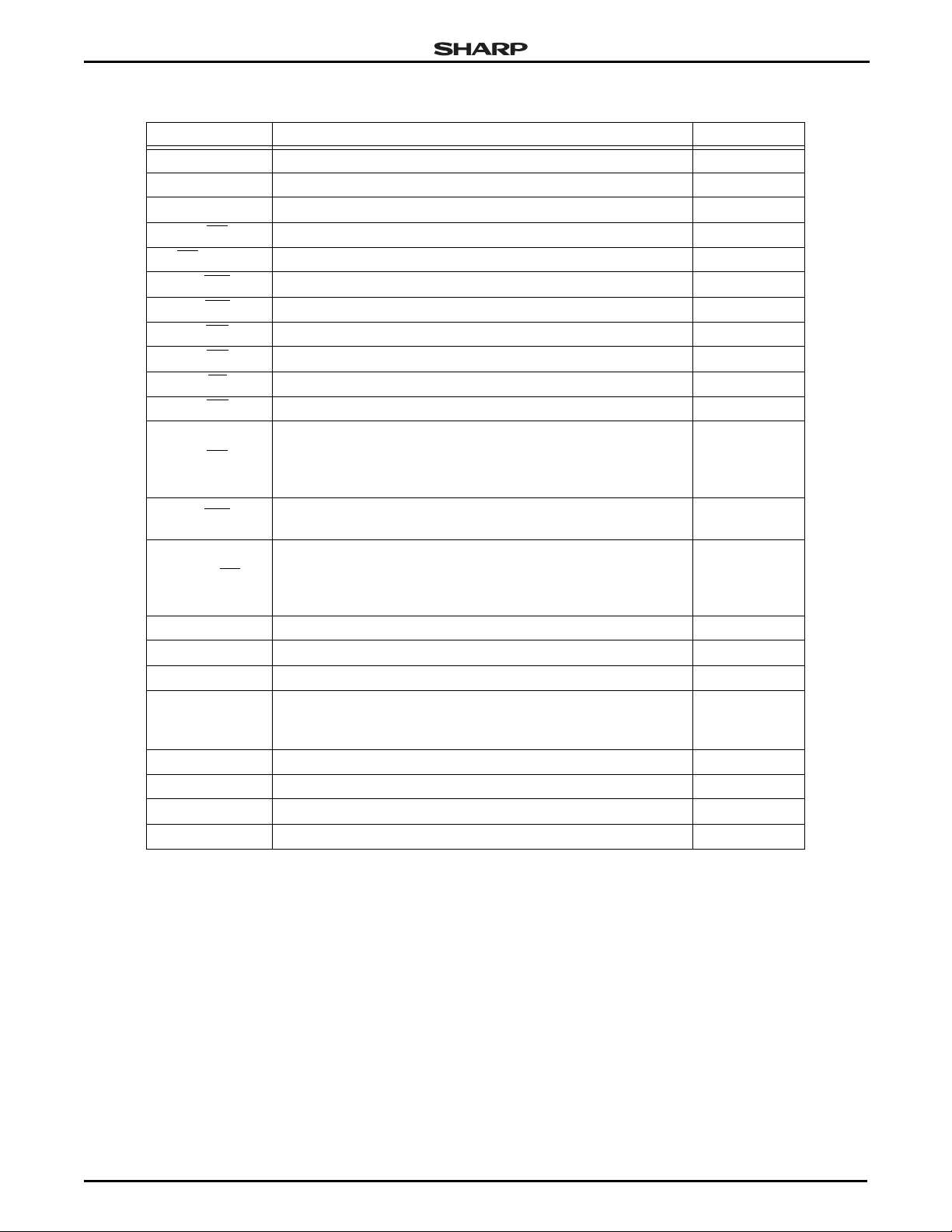

Table 2. Truth Table

FLASH SRAM F-CE

Read Standby L H L H

Output Disable Standby L H H H X X HIGH-Z 3

Write Standby L H H L X X D

F-RP F-OE F-WE S-CE1S-CE2S-OE S-WE S-LB S-UB

See Note 4

1

XX

See Note 4

DQ0 -

DQ

DQ8 DQ

7

D

OUT

IN

15

NOTES

2, 3, 5, 6

Read H H X X L H L H See Note 7

Standby

Reset

Output

Disable

Write H H X X L H L L

Read X L X X L H L H

Output

Disable

HHX X L H H HX X HIGH-Z

HHX X L H X X HH HIGH-Z

See Note 7

XLX X L H HHXX HIGH-Z

XLX X L H X XHH HIGH-Z

Write X L X X L H L L See Note 7

Standby Standby H H X X

Reset Standby X L X X X X HIGH-Z 3

NOTES:

1. L = V

, H = VIH, X = H or L. Refer to DC Characteristics.

IL

See Note 4

5. Command writes involving block erase or word write are reliably

2. Refer to the ‘Flash Memory Command Definition’ section for valid

address input and D

3. F-WP

set to VIL or VIH.

4. SRAM standby data. See Table 2a.

during a write operation.

IN

6. Never hold F-OE

7. S-LB

XX

executed when V

See Note 4

(2.7 V to 3.6 V) and F-VCC = 2.7 V to

CCWH

3.6 V. Block erase or word write with F-V

HIGH-Z 3

< V

CCW

CCWH

produce spurious results and should not be attempted.

LOW and F-WE LOW at the same timing.

, S-UB Control Mode. See Table 2b.

2, 3

(MIN.)

MODE

Standby

(SRAM)

Table 2a.

PINS

S-CE

S-CE

1

2

S-LB S-UB

HXXX

XLXX

XXHH

MODE

(SRAM)

Read/Write

Table 2b.

PINS

S-LB

LLD

LHD

HLHIGH-ZD

S-UB DQ0 - DQ7DQ8 - DQ

OUT/DIN

OUT/DIN

D

OUT/DIN

HIGH-Z

OUT/DIN

15

4 Data Sheet

Page 5

Stacked Chip (16M Flash & 4M SRAM) LRS1331

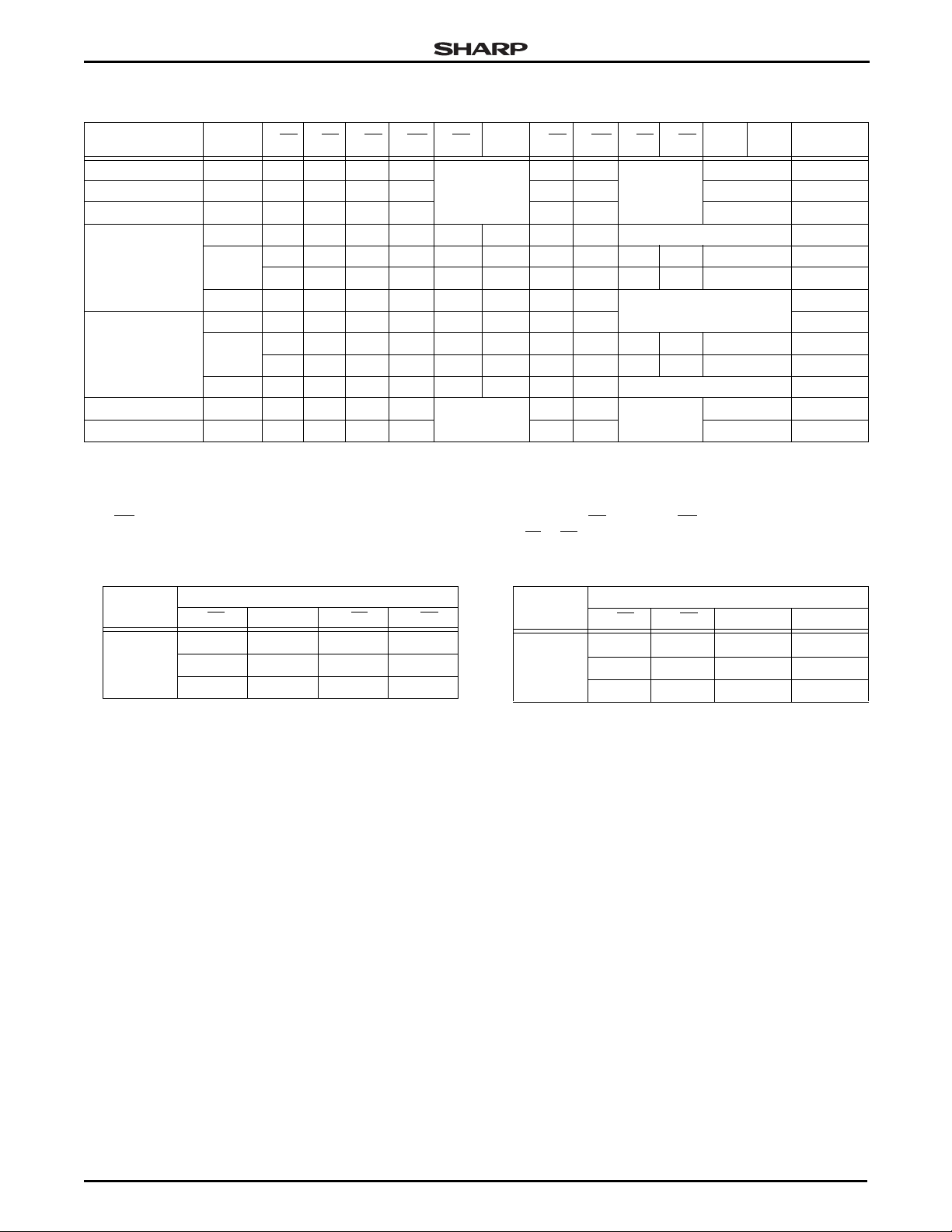

Table 3. Command Definition for Flash Memory

COMMAND

Read Array/Reset 1 Write XA FFH

Read Identifier Codes

Read Status Register 2 Write XA 70H Read XA SRD

Clear Status Register 1 Write XA 50H

Block Erase 2 Write BA 20H Write BA D0H 5

Full Chip Erase 2 Write XA 30H Write XA D0H

Word Write 2 Write WA 40H or 10H Write WA WD 5

Block Erase and Word

Write Suspend

Block Erase and

Write Resume

Set Block Lock-Bits 2 Write BA 60H Write BA 01H 6

Clear Block Lock-Bits 2 Write XA 60H Write XA D0H 6, 7

Set Permanent Lock-Bits 2 Write XA 60H Write XA F1H

NOTES:

1. Commands other than those shown in table are reserved by SHARP for future device

implementations and should not be used.

2. BUS operations are defined in Table 2.

3. XA = Any valid address within the device;

IA = Identifier code address;

BA = Address within the block being erased;

WA = Address of memory location to be written;

SRD = Data read from status register;

WD = Data to be written at location WA. Data is latched on the

rising edge of F-WE

ID = Data read from identifier codes.

4. See Table 4 for Identifier Codes.

5. See Table 5 for Write Protection Alternatives.

6. If the permanent lock-bit is set, Set Block Lock-Bit and Clear Block Lock-Bits commands cannot be done.

7. The clear block lock-bits operation simultaneously clears all block lock-bits.

BUS CYCLES

REQUIRED

≥

2 Write XA 90H Read IA ID 4

1WriteXAB0H 5

1WriteXAD0H 5

or F-CE (whichever goes HIGH first);

OPERATION

FIRST BUS CYCLE SECOND BUS CYCLE

2

ADDRESS

3

DATA

3

OPERATION2ADDRESS3DATA

1

NOTES

3

Table 4. Identifier Codes

CODES ADDRESS (A0 - A19) DATA (DQ0 - DQ7)1NOTES

Manufacture Code 00000H B0H

Device Code 00001H E9H

Block Lock

Configuration

Permanent Lock

Configuration

NOTES:

- DQ15 outputs 00H in word mode. DQ1 - DQ7 are reserved for future use.

1. DQ

8

2. BA selects the specific block lock configuration code to be read. See Figure 3

for the device identifier code memory map.

Block is Unlocked BA + 2 DQ

Block is Locked BA + 2 DQ

Device is Unlocked 00003H DQ

Device is Locked 00003H DQ

= 0 2

0

= 1 2

0

= 0

0

= 1

0

Data Sheet 5

Page 6

LRS1331 Stacked Chip (16M Flash & 4M SRAM)

Table 5. Write Protection Alternatives

OPERATION F-V

Block Erase or

Word Write

Full Chip Erase

Set Block

Lock-Bit

Clear Block

Lock-Bit

Set Permanent

Lock-Bit

≤ V

> V

≤ V

> V

≤ V

> V

≤ V

> V

≤ V

> V

CCW

CCWLK

CCWLK

CCWLK

CCWLK

CCWLK

CCWLK

CCWLK

CCWLK

CCWLK

CCWLK

F-RP

PERMANENT

LOCK-BIT

XX XX

V

IL

V

IH

XXX

X

XX XX

V

IL

V

IH

XXX

XX

XX XX

V

IL

XXX

0XX

V

IH

1XX

XX XX

V

IL

XXX

0XX

V

IH

1XX

XX XX

V

IL

V

IH

XXX

XXX

BLOCK

LOCK-BIT

0

1

F-WP

V

IL

V

IH

V

IL

V

IH

V

IL

V

IH

All blocks locked

All blocks locked

Two boot blocks locked

Block Erase and Word Write enabled

Block Erase and Word Write disabled

Block Erase and Word Write disabled

All blocks locked

All blocks locked

All unlocked blocks are erased. Two boot

blocks and locked blocks are not erased

All unlocked blocks are erased. Locked blocks

are not erased

Set block lock-bit disabled

Set block lock-bit disabled

Set block lock-bit enabled

Set block lock-bit disabled

Clear block lock-bits disabled

Clear block lock-bits disabled

Clear block lock-bits enabled

Clear block lock-bits disabled

Set permanent lock-bit disabled

Set permanent lock-bit disabled

Set permanent lock-bit enabled

EFFECT

6 Data Sheet

Page 7

Stacked Chip (16M Flash & 4M SRAM) LRS1331

Table 6. Status Register Definition

WSMS BESS ECBLBS WBWSLBS VCCWS WBWSS DPS R

76543210

SR.7 = Write State Machine Status (WSMS)

1 = Ready

0 = Busy

SR.6 = Erase Suspend Status (BESS)

1 = Block Erase Suspended

0 = Block Erase in Progress/Completed

SR.5 = Erase and Clear Block

Lock-Bits Status (

ECBLBS

)

1 = Error in Block Erase, Bank Erase or

Clear Block Lock-Bits

0 = Successful Block Erase, Bank Erase or

Clear Block Lock-Bits

SR.4 = Word/Byte Write and Set Lock-Bit

Status (WBWSLBS)

1 = Error in Word/Byte Write or Set

Block/Permanent Lock-Bit

0 = Successful Word/Byte Write or Set

Block/Permanent Lock-Bit

SR.3 = V

1 = V

0 = V

Status (VCCWS)

CCW

LOW Detect, Operation Abort

CCW

Okay

CCW

SR.2 = Word/Byte Write Suspend Status (WBWSS)

1 = Word/Byte Write Suspended

0 = Word/Byte Write in Progress/Completed

NOTES:

1. Check SR.7 to determine block erase, bank erase, word/byte

write or lock-bit configuration completion. SR.6 - SR.0 are invalid

while SR.7 = 0.

2. If both SR.5 and SR.4 are ‘1’s after a block erase, bank erase or

lock-bit configuration attempt, an improper command sequence

was entered.

3. SR.3 does not provide a continuous indication of F-V

The WSM interrogates and indicates the F-V

block erase, bank erase, word/byte write or lock-bit configuration

command sequences. SR.3 is not guaranteed to report accurate

feedback only when F-V

4. SR.1 does not provide a continuous indication of permanent and

block lock-bit and F-WP

nent lock-bit, block lock-bit and F-WP

erase, word/byte write or lock-bit configuration command

sequences. It informs the system, depending on the attempted

operation, if the block lock-bit is set, permanent lock-bit is set and/

is VIL. Reading the block lock and permanent lock confi-

or F-WP

gruation codes after writing the Read Identifier codes command

indicates permanent and block lock-bit status..

5. SR.0 is reserved for future use and should be masked out when

polling the status register.

≠ F-V

CCW

values. The WSM interrogates the perma-

.

CCWH

only after block erase, bank

level only after

CCW

CCW

level.

SR.1 = Device Protect Status (DPS)

1 = Block Lock-Bits, Permanent Lock-Bits

and/or F-WP

Lock Detected, Operation Abort

0 = Unlock

SR.0 = Reserved for future enhancements (R)

Data Sheet 7

Page 8

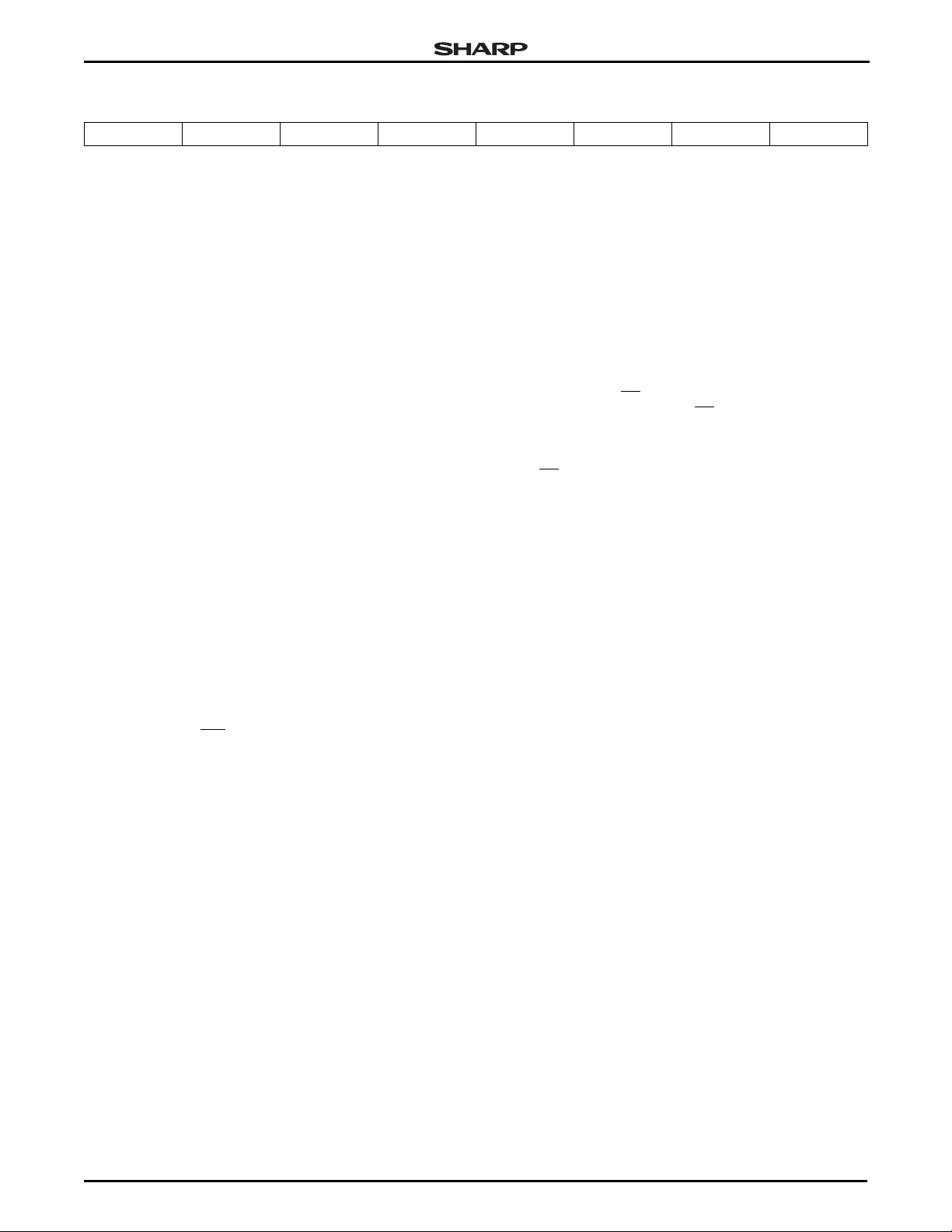

LRS1331 Stacked Chip (16M Flash & 4M SRAM)

MEMORY MAP

[A0 - A19]

FFFFF

F8000

F7FFF

F0000

EFFFF

E8000

E7FFF

E0000

DFFFF

D8000

D7FFF

D0000

CFFFF

C8000

C7FFF

C0000

BFFFF

B8000

B7FFF

B0000

AFFFF

A8000

A7FFF

A0000

9FFFF

98000

97FFF

90000

8FFFF

88000

87FFF

80000

7FFFF

78000

77FFF

70000

6FFFF

68000

67FFF

60000

5FFFF

58000

57FFF

50000

4FFFF

48000

47FFF

40000

3FFFF

38000

37FFF

30000

2FFFF

28000

27FFF

20000

1FFFF

18000

17FFF

10000

0FFFF

08000

07FFF

07000

06FFF

06000

05FFF

05000

04FFF

04000

03FFF

03000

02FFF

02000

01FFF

01000

00FFF

00000

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

32K-WORD MAIN BLOCK

4K-WORD PARAMETER BOOT BLOCK

4K-WORD PARAMETER BOOT BLOCK

4K-WORD PARAMETER BOOT BLOCK

4K-WORD PARAMETER BOOT BLOCK

4K-WORD PARAMETER BOOT BLOCK

4K-WORD PARAMETER BOOT BLOCK

4K-WORD BOOT BLOCK

4K-WORD BOOT BLOCK

BOTTOM BOOT

Figure 3. Memory Map for Flash Memory

30

2932K-WORD MAIN BLOCK

2832K-WORD MAIN BLOCK

2732K-WORD MAIN BLOCK

2632K-WORD MAIN BLOCK

2532K-WORD MAIN BLOCK

2432K-WORD MAIN BLOCK

2332K-WORD MAIN BLOCK

2232K-WORD MAIN BLOCK

2132K-WORD MAIN BLOCK

2032K-WORD MAIN BLOCK

1932K-WORD MAIN BLOCK

18 32K-WORD MAIN BLOCK

1732K-WORD MAIN BLOCK

1632K-WORD MAIN BLOCK

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

5

4

3

2

1

0

1

0

LRS1331-3

8 Data Sheet

Page 9

Stacked Chip (16M Flash & 4M SRAM) LRS1331

ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL RATINGS UNIT NOTES

Supply voltage V

Input voltage V

Operating temperature T

Storage temperature T

F-V

NOTES:

1. The maximum applicable voltage on any pins with respect to GND.

2. Except F-V

3. -2.0 V undershoot is allowed when the pulse width is less than 20 ns.

voltage F-V

CCW

CC

, F-V

CCW

.

CC

IN

OPR

STG

CCW

-0.2 to +4.6 V 1

-0.2 to VCC +0.3 V 1, 2, 3

-25 to +85 °C

-65 to +125 °C

-0.5 to +4.6 V 1, 3

RECOMMENDED DC OPERATING CONDITIONS

TA = -25°C to +85°C

PARAMETER SYMBOL MIN. TYP. MAX. UNIT NOTES

Supply voltage V

Input voltage

NOTES:

is the lower one of S-VCC and F-VCC.

1. V

CC

2. -2.0 V undershoot is allowed when the pulse width is less than 20 ns.

CC

V

IH

V

IL

2.7 3.0 3.6 V

2.2 VCC + 0.2 V 1

-0.3 0.6 V 2

PIN CAPACITANCE

TA = 25°C, f = 1 MHz

PARAMETER SYMBOL CONDITION MIN. TYP. MAX. UNIT

Input capacitance* C

I/O capacitance* C

NOTE: *

Sampled by not 100% tested.

IN

I/O

VIN = 0 V 20 pF

V

= 0 V 22 pF

I/O

Data Sheet 9

Page 10

LRS1331 Stacked Chip (16M Flash & 4M SRAM)

DC CHARACTERISTICS

TA = -25°C to + 85°C, VCC = 2.7 V to 3.6 V

1

PARAMETER SYMBOL CONDITION MIN. TYP.

Input leakage current I

Output leakage current I

VIN = VCC or GND -1.5 +1.5 µA

LI

V

LO

= VCC or GND -1.5 +1.5 µA

OUT

F-CE = F-RP = F-VCC ± 0.2 V

= F-VCC ± 0.2 V

F-WP

CCS

or F-GND ± 0.2 V

F-CE

= F-RP = V

F-CE = GND ± 0.2 V 2 15 µA 2, 3

F-RP = F-GND ± 0.2 V,

CCD

I

(F-RY/BY) = 0 mA

OUT

CMOS input, F-CE = F-GND,

f = 5 MHz, I

CCR

TTL input, F-CE

F-V

Standby Current I

Auto Power-Save Current I

Reset/Power-Down Current I

CC

Read Current I

CCAS

f = 5 MHz, I

Word Write or Set Lock-Bit Current I

F-V

Block Erase, Full Chip Erase or

Clear Block Lock-BIts Current

Word Write Block Erase

Suspend Current

Standby or Read Current

Auto Power-Save Current I

Reset/Power-Down Current I

CCW

Word Write or Set Lock-Bit Current I

Block Erase, Full Chip Erase or

Clear Block Lock-Bits Current

Word Write or Block Erase

Suspend Current

I

I

CCWS

I

CCES

I

CCWS

I

CCWR

CCWAS

CCWD

CCWW

I

CCWE

I

CCWWS

I

CCWES

Standby Current

S-V

CC

Operation Current

Input LOW Voltage V

Input HIGH Voltage V

Output LOW Voltage V

Output HIGH Voltage (CMOS) V

Lockout during Normal Operations V

F-V

CCW

during Block Erase, Bank Erase, W ord

F-V

CCW

Write or Lock-Bit Configuration Operations

F-V

Lockout Voltage V

CC

CCWLK

V

I

I

I

CCWH

F-V

CCW

CCE

F-V

CCW

CCW

F-CE = V

F-VPP ≤ F-V

> F-V

F-V

PP

F-CE = GND ± 0.2 V 0.1 5 µA 2, 3

F-RP = F-GND ± 0.2 V 0.1 5 µA 2

F-V

CCW

F-V

CCW

F-V

CCW

S-CE1, S-CE2 ≥ S-VCC - 0.2 V

I

SB

or S-CE

S-CE1 = VIH or S-CE2 = V

SB1

S-CE1 = VIL, S-CE2 = VIH, VIN = VIL or

CC1

V

, t

IH

CYCLE

S-CE1 = 0.2 V, S-CE2 = S-VCC - 0.2 V,

= S-VCC - 0.2 V, or 0.2 V

V

CC2

OLIOL

OH1IOH

LKO

IN

t

CYCLE

IL

IH

= 0.5 mA 0.4 V 4

= -0.5 mA 2.2 V 4

NOTES:

1. Reference values at V

2. CMOS inputs are either V

are either V

3. Automatic Power Savings (APS) feature is placed automatically

or VIH.

IL

= 3.0 V and TA = +25°C.

CC

± 0.2 V or GND ± 0.2 V. TTL inputs

CC

power save mode that addresses not switching more than 300 ns

while read mode.

OUT

OUT

= V

CCWH

= V

CCWH

IH

CC

CC

= V

CCWH

= V

CCWH

= V

CCWH

≤ 0.2 V

2

= MIN., I

= 1 µs, I

F-WP = VIH or V

IH,

IL

= 0 mA

= F-GND,

= 0 mA

IL

= 0 mA

I/O

= 0 mA

I/O

-0.3 0.6 V

2.2

2.7 3.6 V

2.0 V

4. Includes F-RY/BY

.

5. Block erases and word writes are inhibited when F-V

and not guaranteed in the range between V

(MIN.), and above V

V

CCWH

CCWH

MAX. UNIT NOTES

215µA2

0.2 2 mA

215µA2

15 25 mA 2

30 mA 2

517mA

417mA

16mA

±2 ±15 µA 2

10 200 µA

12 40 mA

825mA

10 200 µA

15 µA

3mA

45 mA

8mA

V

+

CC

0.2

V

1.5 V 5

≤

V

CCW

CCWLK

(MAX.) and

CCWLK

(MAX.).

10 Data Sheet

Page 11

Stacked Chip (16M Flash & 4M SRAM) LRS1331

FLASH MEMORY AC CHARACTERISTICS

AC Test Conditions

PARAMETER CONDITION

Input pulse level 0 V to 2.7 V

Input rise and fall time 10 ns

Input and Output timing reference level 1.35 V

Output load 1TTL + C

(50 pF)

L

Read Cycle

TA = -25°C to +85°C, VCC = 2.7 V to 3.6 V

PARAMETER SYMBOL MIN. MAX. UNIT

Read Cycle Time t

Address to Output Delay t

to Output Delay* t

F-CE

F-RP

HIGH to Output Delay t

F-OE

to Output Delay* t

to Output in LOW Z t

F-CE

F-CE

HIGH to Output in HIGH-Z t

F-OE

to Output in LOW Z t

HIGH to Output in HIGH-Z t

F-OE

Output Hold from Address, F-CE

or F-OE change,

whichever occurs first

*F-OE

NOTE:

may be delayed up to t

ELQV

- t

after the falling edge of F-OE without impact on t

GLQV

AVAV

AVQV

ELQV

PHQV

GLQV

ELQX

EHQZ

GLQX

GHQZ

t

OH

90 ns

90 ns

90 ns

600 ns

40 ns

0ns

40 ns

0ns

15 ns

0ns

.

ELQV

Data Sheet 11

Page 12

LRS1331 Stacked Chip (16M Flash & 4M SRAM)

Write Cycle (F-WE Controlled)

1

TA = -25°C to +85°C, VCC = 2.7 V to 3.6 V

PARAMETER SYMBOL MIN. MAX. UNIT NOTES

Write Cycle Time t

HIGH Recovery to F-WE going to LOW t

F-RP

F-CE

Setup to F-WE going LOW t

F-WE

Pulse Width t

V

F-WP

F-V

Address Setup to F-WE

Data Setup to F-WE

Data Hold from F-WE

Address Hold from F-WE

F-CE

F-WE

F-WE

Setup to F-WE going HIGH t

IH

Setup to F-WE going HIGH t

CCW

going HIGH t

going HIGH t

HIGH t

HIGH t

Hold from F-WE HIGH t

Pulse Width HIGH t

HIGH to F-RY/BY going LOW t

Write Recovery before Read t

F-V

F-WP

Hold from Valid SRD, F-RY/BY HIGH Z t

CCW

VIH Hold from Valid SRD, F-RY/BY HIGH t

AVAV

PHWL

ELWL

WLWH

SHWH

VPWH

AVWH

DVWH

WHDX

WHAX

WHEH

WHWL

WHRL

WHGL

QVVL

QVSL

90 ns

1µs

10 ns

50 ns

100 ns

100 ns

50 ns

50 ns 2

0ns2

0ns

10 ns

30 ns

100 ns

0ns

0ns

0ns

NOTES:

1. Read timing characteristics during block erase and word write operations are the same as

during read-only operations. Refer to AC Characteristics for Read Cycle.

2. Refer to the ‘Flash Memory Command Definition’ section for valid A

and DIN for block erase or word write.

IN

12 Data Sheet

Page 13

Stacked Chip (16M Flash & 4M SRAM) LRS1331

Write Cycle (F-CE Controlled)

1

TA = -25°C to +85°C, VCC = 2.7 V to 3.6 V

PARAMETER SYMBOL MIN. MAX. UNIT NOTES

Write Cycle Time t

HIGH Recovery to F-CE going to LOW t

F-RP

Setup to F-CE going LOW t

F-WE

Pulse Width t

F-CE

V

F-WP

F-V

Address Setup to F-CE

Data Setup to F-CE

Data Hold from F-CE

Address Hold from F-CE

F-WE

F-CE

F-CE

Write Recovery before Read t

F-V

F-WP

Setup to F-CE going HIGH t

IH

Setup to F-CE going HIGH t

CCW

going HIGH t

going HIGH t

HIGH t

HIGH t

Hold from F-CE HIGH t

Pulse Width HIGH t

HIGH to F-RY/BY going LOW t

Hold from Valid SRD, F-RY/BY HIGH Z t

CCW

VIH Hold from Valid SRD, F-RY/BY HIGH t

AVAV

PHEL

WLEL

ELEH

SHEH

VPEH

AVEH

DVEH

EHDX

EHAX

EHWH

EHEL

EHRL

EHGL

QVVL

QVSL

90 ns

1µs

0ns

60 ns

100 ns

100 ns

50 ns

50 ns 2

0ns2

0ns

0ns

20 ns

100 ns

0ns

0ns

0ns

NOTES:

1. In system where F-CE

hold, and inactive F-WE

2. Refer to the ‘Flash Memory Command Definition’ section for valid A

defines the pulse width (within a F-WE timing waveform), all setup,

times should be measured relative to the F-CE waveform.

Block Erase and Word Write Performance

TA = -25°C to +85°C, VCC = 2.7 V to 3.6 V

SYMBOL PARAMETER

Word Write Time 32K-word Block 33 200 µs 3

t

WHQV1

t

EHQV1

t

WHQV2

t

EHQV2

t

WHQV3

t

EHQV3

t

WHQV4

t

EHQV4

t

WHRZ1

t

EHRZ1

t

WHRZ2

t

EHRZ2

Word Write Time 4K-word Block 36 200 µs 3

Block Write Time 32K-word Block 1.1 2.4 s 3

Block Write Time 4K-word Block 0.15 0.3 s 3

Block Erase Time 32K-word Block 1.2 6 s 3

Block Erase Time 4K-word Bock 0.6 5 s 3

Full Chip Erase Time 42 210 s 3

Set Lock-Bit Time 27.6 200 µs 3

Clear Block Lock-Bits Time 0.64 5 s 3

Word Write Suspend Latency Time to Read 6.0 15 µs

Erase Suspend Latency Time to Read 16.0 30 µs

and DIN for block erase or word write.

IN

V

= 2.7 V to 3.6 V

CCW

MIN. TYP.

1

MAX.

2

UNIT NOTES

NOTES:

1. Reference values at T

2. Sampled, but not 100% tested.

3. Excludes system-level overhead.

= +25°C and VCC = 3.0 V, VPP = 3.0 V.

A

Data Sheet 13

Page 14

LRS1331 Stacked Chip (16M Flash & 4M SRAM)

FLASH MEMORY AC CHARACTERISTICS TIMING DIAGRAMS

ADDRESS

F-CE

F-OE

F-WE

DQ

Standby

Device

Address Selection

t

GLQV

t

ELQV

t

GLQX

t

ELQX

Address Stable

t

AVAV

Data Valid

Valid Output

t

t

t

OH

EHQZ

GHQZ

HIGH ZHIGH Z

F-V

F-RP

CC

t

AVQV

t

PHQV

Figure 4. Read Cycle Timing Diagram

LRS1331-4

14 Data Sheet

Page 15

Stacked Chip (16M Flash & 4M SRAM) LRS1331

21 3 4 5 6

ADDRESS

F-CE

F-OE

F-WE

DQ

F-RY/BY

HIGH-Z

t

PHWL

t

ELWL

A

t

AVAV

t

WLWH

t

DVWH

IN

t

WHEH

D

IN

t

WHWL

t

WHDX

t

AVWH

A

IN

t

WHAX

t

WHGL

t

EHQV1, 2, 3, 4

D

IN

t

WHRL

Data

Valid

SRD

D

IN

F-WP

F-RP

V

CCWH

F-V

CCW

V

CCWLK

V

IL

NOTES:

1. V

power-up and standby.

CC

2. Write block erase or word write setup.

3. Write block erase confirm or valid address and data.

4. Automated erase or program delay.

5. Read status register data.

6. Write Read Array command.

Figure 5. Write Cycle Timing Diagram (F-WE Controlled)

t

SHWH

t

VPWH

t

QVVL

t

QVSL

LRS1331-5

Data Sheet 15

Page 16

LRS1331 Stacked Chip (16M Flash & 4M SRAM)

21 3 4 5 6

ADDRESS

F-WE

F-OE

F-CE

DQ

F-RY/BY

HIGH-Z

t

PHEL

t

WLEL

A

t

AVAV

t

ELEH

t

DVEH

IN

t

EHWH

D

A

IN

t

AVEH

t

EHAX

t

EHGL

t

EHEL

t

EHDX

t

SHEH

D

IN

IN

t

EHRL

t

EHQV1, 2, 3, 4

Data

Valid

SRD

t

QVSL

D

IN

F-WP

F-RP

V

CCWH

V

CCW

CCWLK

V

IL

F-V

NOTES:

power-up and standby.

1. V

CC

2. Write block erase or word write setup.

3. Write block erase confirm or valid address and data.

4. Automated erase or program delay.

5. Read status register data.

6. Write Read Array command.

Figure 6. Write Cycle Timing Diagram (F-CE Controlled)

t

VPEH

t

QVVL

LRS1331-6

16 Data Sheet

Page 17

Stacked Chip (16M Flash & 4M SRAM) LRS1331

RESET OPERATIONS

TA = -25°C to +85°C, VCC = 2.7 V to 3.6 V

PARAMETER SYMBOL MIN. MAX. UNIT NOTES

Pulse LOW Time (if F-RP is tied to VCC, this

F-RP

specification is not applicable).

F-RP

LOW to Reset during Block Erase or Word Write t

2.7 V to F-RP HIGH t

F-V

CC

t

PLPH

PLRZ

VPH

100 ns

20 µs 1, 2

100 ns 3

NOTES:

1. If F-RP

2. A reset time t

3. When the device power-up, holding F-RP

is asserted while a block erase or word write operation is not executing,

the reset will complete with 100 ns.

is required from F-RY/BY going HIGH Z, or F-RP going HIGH until outputs are valid.

PHQV

in predefined range and also has been stable there.

HIGH Z

F-RY/BY (R)

V

OL

V

F-RP (P)

F-RY/BY (R)

F-RP (P)

V

HIGH Z

V

OL

V

V

IH

IL

IH

IL

LOW minimum 100 ns is required after VCC has been

t

PLPH

A. Reset During Read Array Mode

t

PLRZ

t

PLPH

B. Reset During Block Erase or Word Byte Write

CC

2.7 V

V

V

V

IL

IH

IL

t

VPH

F-V

F-RP (P)

C. F-RP Rising Timing

1331-7

Figure 7. AC Waveform for Reset Operation

Data Sheet 17

Page 18

LRS1331 Stacked Chip (16M Flash & 4M SRAM)

SRAM AC ELECTRICAL CHARACTERISTICS

AC Test Conditions

PARAMETER CONDITION

Input pulse level 0.6 V to 2.2 V

Input rise and fall time 5 ns

Input and Output timing reference level 1.5 V

Output load* 1TTL + C

*Including scope and jig capacitance.

NOTE:

(30 pF)

L

Read Cycle

TA = -25°C to +85°C, VCC = 2.7 V to 3.6 V

PARAMETER SYMBOL MIN. MAX. UNIT

Read Cycle Time t

Address Access Time t

S-CE

Chip Enable Access Time

S-CE

1

2

Output Enable to Output Valid t

Output hold from address change t

S-CE

, S-CE2 LOW to Output Active*

S-CE

1

LOW to Output Active* t

S-OE

or S-LB LOW to Output in HIGH Impedance* t

S-UB

, S-CE2 HIGH to Output in

S-CE

1

HIGH Impedance*

HIGH to Output in HIGH Impedance* t

S-OE

or S-LB HIGH to Output Active* t

S-UB

*Active output to HIGH impedance and HIGH impedance to output active

NOTE:

tests specified for a ±200 mV transition from steady state levels into the test load.

S-CE

S-CE

S-CE

1

2

1

2

RC

AA

t

ACE1

t

ACE2

OE

OH

t

LZ1

t

LZ2

OLZ

BLZ

t

HZ1

H

HZ2

OHZ

BHZ

85 ns

85 ns

85 ns

85 ns

45 ns

10 ns

10 ns

10 ns

5ns

5ns

025ns

025ns

025ns

025ns

Write Cycle

TA = -25°C to +85°C, VCC = 2.7 V to 3.6 V

PARAMETER SYMBOL MIN. MAX. UNIT

Write Cycle Time t

Chip Enable to End of Write t

Address Valid to End of Write t

Address Setup Time t

Write Pulse Width t

Write Recovery Time t

Input Data Setup Time t

Input Data Hold Time t

HIGH to Output Active* t

S-WE

LOW to Output in HIGH Impedance* t

S-WE

*Active output to HIGH impedance and HIGH impedance to output active

NOTE:

tests specified for a ±200 mV transition from steady state levels into the test load.

WC

CW

AW

AS

WP

WR

DW

DH

OW

WZ

18 Data Sheet

85 ns

70 ns

70 ns

0ns

60 ns

0ns

35 ns

0ns

5ns

025ns

Page 19

Stacked Chip (16M Flash & 4M SRAM) LRS1331

SRAM AC CHARACTERISTICS TIMING DIAGRAMS

t

RC

ADDRESS

t

AA

t

ACE

S-CE

1

S-CE

2

S-UB, S-LB

S-OE

D

OUT

NOTE: S-WE is HIGH for Read Cycle.

t

LZ

t

BE

t

BLZ

t

OE

t

OLZ

Data Valid

Figure 8. Read Cycle Timing Diagram

t

HZ

t

HZ

t

BHZ

t

OHZ

t

OH

1331-8

Data Sheet 19

Page 20

LRS1331 Stacked Chip (16M Flash & 4M SRAM)

t

WC

ADDRESS

t

AW

t

CW

(NOTE 2)

S-CE

1

t

WR

S-CE

2

t

BW

(NOTE 3)

S-UB, S-LB

t

AS

(NOTE 4)

(NOTE 1)

S-WE

t

WZ

(NOTE 7) (NOTE 8)

D

OUT

(NOTE 6)

D

IN

NOTES:

1. A write occurs during the overlap of a LOW S-CE

A write begins at the latest transition among S-CE

and

S-WE going LOW. A write ends at the earliest transition among S-CE1 going HIGH,

S-CE2 going LOW and S-WE going HIGH. tWP is measured from the beginning of

write to the end of write.

2. t

is measured from the later of S-CE1 going LOW or S-CE2 going HIGH to the end

CW

, a HIGH S-CE2 and a LOW S-WE,

1

going LOW, S-CE2 going HIGH

1

of write.

3. t

is measured from the time of going LOW S-UB or LOW S-LB to the end of write.

BW

is measured from the address valid to the beginning of write.

4. t

AS

5. t

is measured from the end of write to the address change. tWR applied in case a

WR

write ends as S-CE

going HIGH, S-CE2 going LOW or S-WE going HIGH.

1

6. During this period, DQ pins are in the output state, therefore the input signals of

opposite phase to the outputs must not be applied.

7. If S-CE

goes LOW or S-CE2 goes HIGH simultaneously with S-WE going LOW or

1

after S-WE going LOW, the outputs remain in HIGH impedance state.

8. If S-CE

goes HIGH or S-CE2 goes LOW simultaneously with S-WE going HIGH or

1

S-WE going HIGH, the outputs remain in HIGH impedance state.

Figure 9. Write Cycle Timing Diagram (S-WE Controlled)

t

WP

t

DW

t

WR

(NOTE 5)

t

OW

t

DH

Data Valid

1331-9

20 Data Sheet

Page 21

Stacked Chip (16M Flash & 4M SRAM) LRS1331

t

WC

ADDRESS

t

AW

(NOTE 2)

(NOTE 3)

t

WP

(NOTE 1)

t

CW

t

BW

t

WR

t

WR

(NOTE 5)

S-CE

S-CE

S-UB, S-LB

t

AS

(NOTE 4)

1

2

S-WE

D

OUT

D

IN

HIGH IMPEDANCE

(NOTE 6)

NOTES:

1. A write occurs during the overlap of a LOW S-CE

A write begins at the latest transition among S-CE

and

S-WE going LOW. A write ends at the earliest transition among S-CE1 going HIGH,

S-CE2 going LOW and S-WE going HIGH. tWP is measured from the beginning of

write to the end of write.

2. t

is measured from the later of S-CE1 going LOW or S-CE2 going HIGH to the end

CW

of write.

3. t

is measured from the time of going LOW S-UB or LOW S-LB to the end of write.

BW

4. t

is measured from the address valid to the beginning of write.

AS

is measured from the end of write to the address change. tWR applied in case a

5. t

WR

write ends as S-CE

6. During this period, DQ pins are in the output state, therefore the input signals of

opposite phase to the outputs must not be applied.

going HIGH, S-CE2 going LOW or S-WE going HIGH.

1

, a HIGH S-CE2 and a LOW S-WE,

1

going LOW, S-CE2 going HIGH

1

Figure 10. Write Cycle Timing Diagram (S-CE Controlled)

t

DW

Data Valid

t

DH

1331-10

Data Sheet 21

Page 22

LRS1331 Stacked Chip (16M Flash & 4M SRAM)

t

WC

ADDRESS

t

AW

S-OE

t

CW

(NOTE 2)

S-CE

1

t

WR

(NOTE 5)

S-CE

2

t

AS

(NOTE 4)

t

BW

(NOTE 3)

t

WR

(NOTE 5)

S-UB, S-LB

t

WP

(NOTE 1)

S-WE

D

OUT

D

IN

HIGH IMPEDANCE

NOTES:

1. A write occurs during the overlap of a LOW S-CE1, a HIGH S-CE2 and a LOW S-WE,

A write begins at the latest transition among S-CE

and

S-WE going LOW. A write ends at the earliest transition among S-CE1 going HIGH,

S-CE2 going LOW and S-WE going HIGH. tWP is measured from the beginning of

write to the end of write.

2. t

is measured from the later of S-CE1 going LOW or S-CE2 going HIGH to the end

CW

going LOW, S-CE2 going HIGH

1

of write.

is measured from the time of going LOW S-UB or LOW S-LB to the end of write.

3. t

BW

4. t

is measured from the address valid to the beginning of write.

AS

5. t

is measured from the end of write to the address change. t

WR

as S-CE1 going HIGH, S-CE2 going LOW or S-WE going HIGH.

applied in case a write ends

WR

Figure 11. Write Cycle Timing Diagram (S-UB, S-LB Control)

t

DW

Data Valid

t

DH

1331-11

22 Data Sheet

Page 23

Stacked Chip (16M Flash & 4M SRAM) LRS1331

SRAM DATA RETENTION CHARACTERISTICS

TA = -25°C to +85°C

PARAMETER SYMBOL CONDITIONS MIN. TYP.1MAX. UNIT NOTES

Data Retention Supply Voltage V

Data Retention Supply Current I

Chip Enable Setup Time t

Chip Enable Hold Time t

CCDR

CCDR

CDR

R

S-CE2 ≤ 0.2 V or

S-CE

≥ V

1

V

= 1.2 V, S-CE2 ≤ 0.2 V or

CCDR

S-CE

≥ V

1

CCDR

CCDR

- 0.2 V

- 0.2 V

13.6V2

5µA 2

0ns

t

RC

ms

NOTES:

1. Reference value at T

2. S-CE

≥ VCC - 0.2 V, S-CE2 ≥ VCC - 0.2 V (S-CE1 controlled) or S-CE2 ≤ 0.2 V (S-CE2 controlled).

1

S-V

CC

= 25°C, S-VCC = 3.0 V.

A

2.7 V

t

CDR

2.2 V

V

CCDR

S-CE

1

0 V

NOTE: To control the data retention mode at S-CE

V

CCDR

and V

- 0.2 V, or 0 V and 0.2 V, and during the data retention mode.

CCDR

Figure 12. Data Retention Timing Diagram (S-CE1 Controlled)

Data Retention Mode

S-CE1 ≥

, fix the input level of S-CE2 between

1

V

CCDR

- 0.2 V

t

R

1331-12

Data Retention Mode

S-V

CC

2.7 V

S-CE

t

2

V

CCDR

CDR

t

R

0.6 V

S-CE2 ≤ 0.2 V

0 V

1331-13

Figure 13. Data Retention Timing Diagram (S-CE

Controlled)

2

Data Sheet 23

Page 24

LRS1331 Stacked Chip (16M Flash & 4M SRAM)

GENERAL DESIGN GUIDELINES

Supply Power

Maximum difference (between F-VCC and S-VCC) of

the voltage is less than 0.3 V.

Power Supply and Chip Enable of Flash

Memory and SRAM

S-CE1 should not be LOW and S-CE2 should not be

HIGH when F-CE

If the two memories are active together, they may

not operate normally because of interference noises or

data collision on DQ bus.

Both F-V

recommended supply voltage at the same time except

SRAM data retention mode.

is LOW simultaneously.

and S-VCC need to be applied by the

CC

Power Up Sequence

When turning on Flash memory power supply, keep

F-RP

LOW. After F-VCC reaches over 2.7 V, keep F-RP

LOW for more than 100 ns.

Device Decoupling

The power supply needs to be designed carefully

because one of the SRAM and the Flash Memory is in

standby mode when the other is active. A careful

decoupling of power supplies is necessary between

SRAM and Flash Memory. Note peak current caused

by transition of control signals (F-CE

, S-CE1, S-CE2).

FLASH MEMORY DATA PROTECTION

Noises having a level exceeding the limit specified in

the specification may be generated under specific

operating conditions on some systems.

Such noises, when induced onto F-WE

power supply may be interpreted as false commands,

causing undesired memory updating.

To protect the data store in the flash memory against

unwanted overwriting, systems operating with the flash

memory should have the following write protect

designs, as appropriate:

signal or

Protecting Data in Specific Block

By setting a F-WP to LOW, only the boot block can

be protected against overwriting.

Parameter and main blocks with F-WP

locked.

System program, etc., can be locked by storing them

in the book block.

For further information on setting/resetting of block

bit, and controlling of F-WP

specification, see the Command Definitions section.

and F-RP, refer to the

cannot be

Data Protection Through F-V

When the level of F-V

(lockout voltage), write operation on the flash memory

is disabled. All blocks are locked and the data in the

blocks are completely write protected.

For the lockout voltage refer to the ‘DC Characteristics’ section.

is lower than F-V

CCW

CCW

CCWK

Data Protection During Voltage Transition

DATA PROTECTION THROUGH F-RP

When the F-RP is kept LOW during power up and

power down sequence, write operation on the flash

memory is disabled, write protecting all blocks.

For details of F-RP

ory AC Electrical Characteristics’ section.

control refer to the ‘Flash Mem-

DESIGN CONSIDERATIONS

Power Supply Decoupling

To avoid a bad effect on the system by flash memory

power switching characteristics, each device should

have a 0.1 µF ceramic capacitor connected between its

V

and GND and between its V

CC

inductance capacitors should be placed as close as

possible to package leads.

V

that reside in the target system requires that the printed

circuit board designer pay attention to the V

Supply trace. Use similar trace widths and layout considerations given to the V

Trace on Printed Circuit Boards

CCW

Updating the memory contents of flash memories

power bus.

CC

and GND. LOW

CCW

CCW

Power

The Inhibition of Overwrite Operation

Please do not execute reprogramming ‘0’ for the bit

which has already been programmed ‘0’. Overwrite operation may generate unerasable bit. In case of reprogramming ‘0’ to the data which has been programmed ‘1’.

• Program ‘0’ for the bit in which you want to change

data from ‘1’ to ‘0’.

• Program ‘1’ for the bit which has already been pro-

grammed ‘0’.

For example, changing data from

‘1011110110111101’ to ‘1010110110111100’ requires

‘1110111111111110’ programming.

Power Supply

Block erase, full chip erase, word write and lock-bit

configuration with an invalid V

istics’) produce spurious results and should not be

attempted. Device operations at invalid V

product spurious results and should not be attempted.

(see ‘DC Character-

CCW

CC

voltage

24 Data Sheet

Page 25

Stacked Chip (16M Flash & 4M SRAM) LRS1331

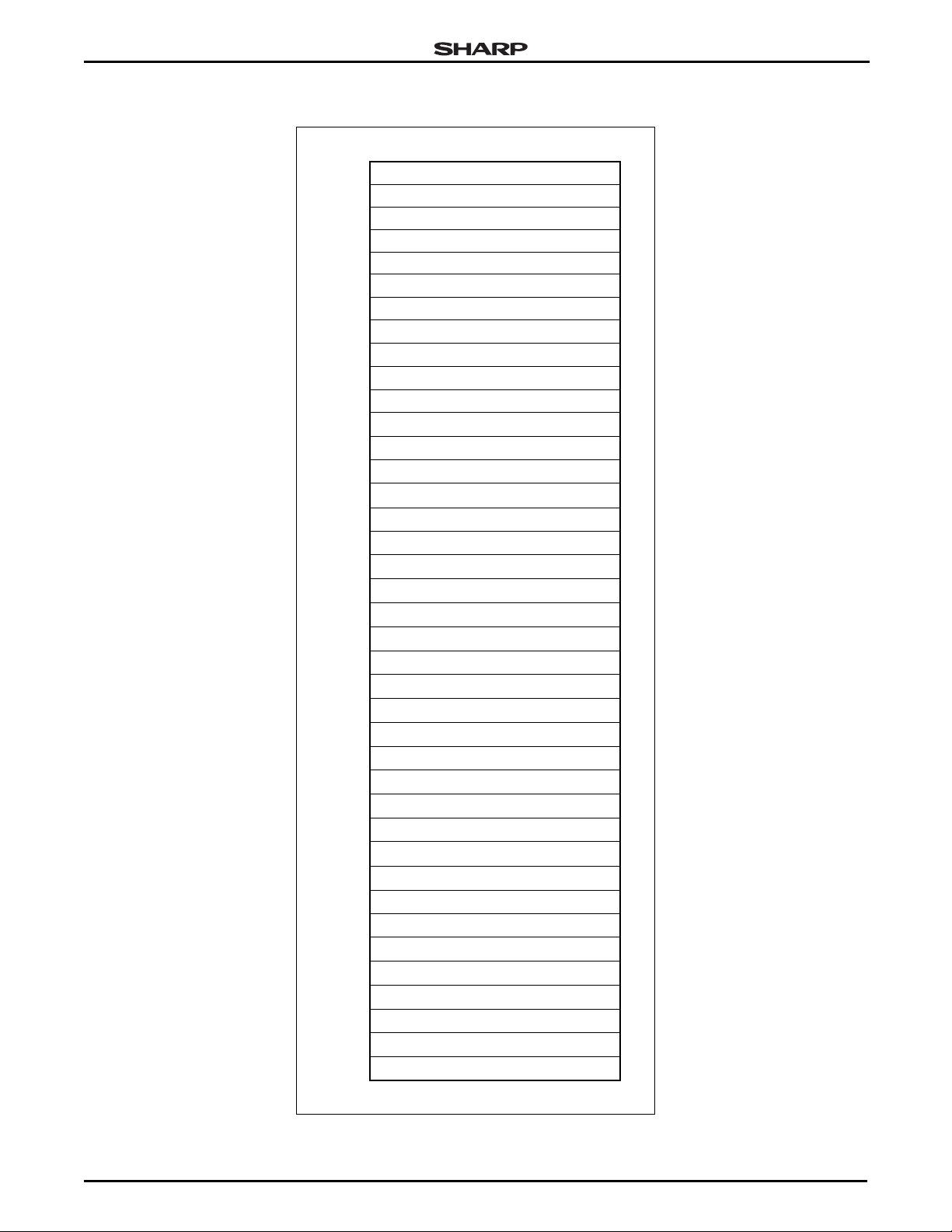

OUTLINE DIMENSIONS

FBGA072-P-0811

B

TOP VIEW

SIDE VIEW

S

A

0.10 S

0.10 S

INDEX

11.0

+0.2

-0

+0.2

-0

8.0

(See Detail)

0.40 TYP.

DETAIL

1.1 TYP.

0.8 TYP.

H

BOTTOM VIEW

D

NOTE: Dimensions are in mm.

G

F

E

D

C

B

A

12345678

0.4 TYP.

C

9101112

φ 0.45 ±0.05

φ 0.30

φ 0.15

1.2 TYP.

0.8 TYP.

M

SSAB

M

1.4 MAX.

0.35 ±0.05

0.4 TYP.

CD

72FBGA

Data Sheet 25

Page 26

Stacked Chip (16M Flash & 4M SRAM) LRS1331

LIFE SUPPORT POLICY

SHARP components should not be used in medical devices with life support functions or in safety equipment (or similiar applications where

component failure would result in loss of life or physical harm) without the written approval of an officer of the SHARP Corporation.

LIMITED WARRANTY

SHARP warrants to its Customer that the Products will be free from defects in material and workmanship under normal use and service for a

period of one year from the date of invoice. Customer's exclusive remedy for breach of this warranty is that SHARP will either (i) repair or

replace, at its option, any Product which fails during the warranty period because of such defect (if Customer promptly reported the failure to

SHARP in writing) or, (ii) if SHARP is unable to repair or replace, refund the purchase price of the Product upon its return to SHARP. This

warranty does not apply to any Product which has been subjected to misuse, abnormal service or handling, or which has been altered or

modified in design or construction, or which has been serviced or repaired by anyone other than Sharp. The warranties set forth herein are in

lieu of, and exclusive of, all other warranties, express or implied. ALL EXPRESS AND IMPLIED WARRANTIES, INCLUDING THE

WARRANTIES OF MERCHANTABILITY, FITNESS FOR USE AND FITNESS FOR A PARTICULAR PURPOSE, ARE SPECIFICALLY

EXCLUDED. In no event will Sharp be liable, or in any way responsible, for any incidental or consequential economic or property damage.

The above warranty is also extended to Customers of Sharp authorized distributors with the following exception: reports of failures of Products

during the warranty period and return of Products that were purchased from an authorized distributor must be made through the distributor.

In case Sharp is unable to repair or replace such Products, refunds will be issued to the distributor in the amount of distributor cost.

SHARP reserves the right to make changes in specifications at any time and without notice. SHARP does not assume any responsibility

for the use of any circuitry described; no circuit patent licenses are implied.

NORTH AMERICA

SHARP Microelectronics

of the Americas

5700 NW Pacific Rim Blvd.

Camas, WA 98607, U.S.A.

Phone: (360) 834-2500

Telex: 49608472 (SHARPCAM)

Facsimile: (360) 834-8903

EUROPE

SHARP Electronics (Europe) GmbH

Microelectronics Division

Sonninstraße 3

20097 Hamburg, Germany

Phone: (49) 40 2376-2286

Facsimile: (49) 40 2376-2232

http://www.sharpmed.com

ASIA

SHARP Corporation

Integrated Circuits Group

2613-1 Ichinomoto-Cho

Tenri-City, Nara, 632, Japan

Phone: +81-743-65-1321

Facsimile: +81-743-65-1532

http://www.sharp.co.jp

http://www.sharpsma.com

©1999 by SHARP Corporation Reference Code SMA99087

Loading...

Loading...