Datasheet LMS8117AMPX-3.3, LMS8117AMP-ADJ, LMS8117AMP-1.8, LMS8117ADTX-ADJ, LMS8117ADTX-3.3 Datasheet (NSC)

...Page 1

LMS8117A

1A Low-Dropout Linear Regulator

General Description

The LMS8117Ais a series of low dropout voltage regulators

with a dropout of 1.2V at 1A of load current. It has the same

pin-out as National Semiconductor’s industry standard

LM317.

The LMS8117A is available in an adjustable version, which

can set the output voltage from 1.25V to 13.8V with only two

external resistors. In addition, it is also available in two fixed

voltages, 1.8V and 3.3V.

The LMS8117Aoffers currentlimiting and thermal shutdown.

Its circuit includes a zener trimmed bandgap reference to

assure output voltage accuracy to within

±

1%.

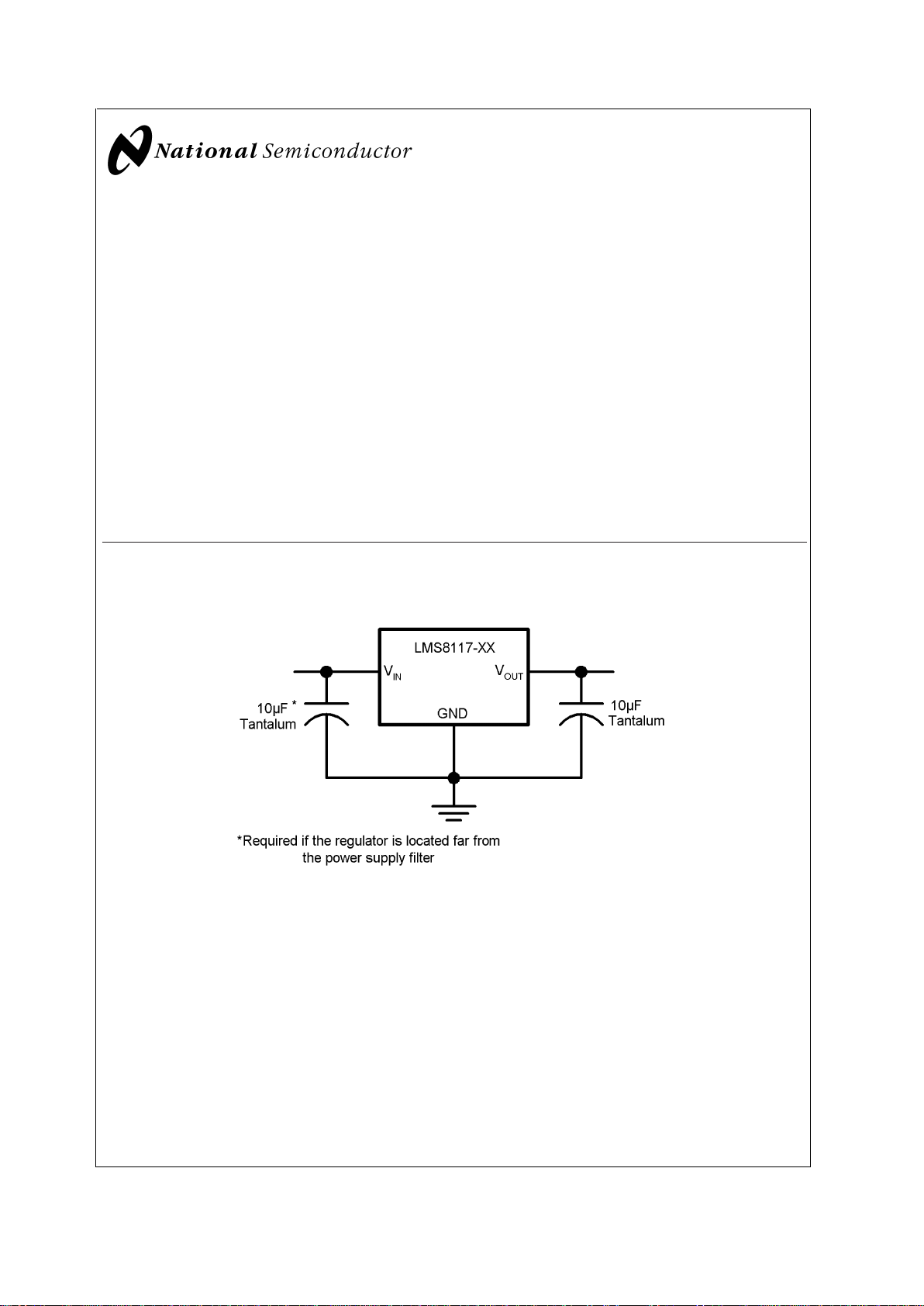

The LMS8117A series is available in SOT-223 and TO-252

D-PAK packages. A minimum of 10µF tantalum capacitor is

required at the output to improve the transient response and

stability.

Features

n Available in 1.8V, 3.3V, and Adjustable Versions

n Space Saving SOT-223 and TO-252 Packages

n Current Limiting and Thermal Protection

n Output Current 1A

n Temperature Range 0˚C to 125˚C

n Line Regulation 0.2% (Max)

n Load Regulation 0.4% (Max)

Applications

n Post Regulator for Switching DC/DC Converter

n High Efficiency Linear Regulators

n Battery Charger

n Battery Powered Instrumentation

Typical Application

Fixed Output Regulator

DS101196-28

July 2001

LMS8117A 1A Low-Dropout Linear Regulator

© 2001 National Semiconductor Corporation DS101196 www.national.com

Page 2

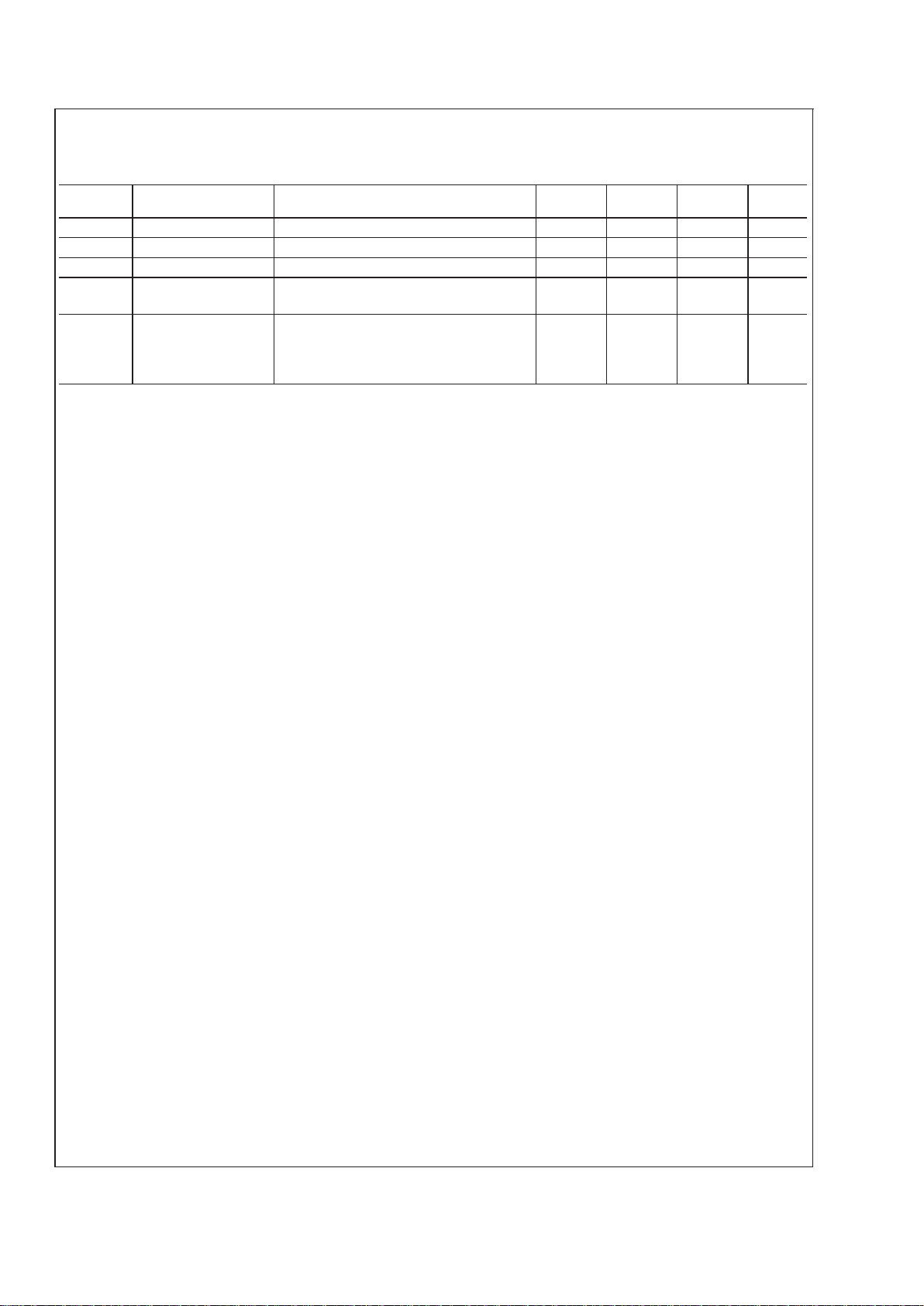

Ordering Information

Package

Temperature Range

(T

J

)

Packaging Marking Transport Media

NSC

Drawing

0˚C to +125˚C

3-lead

SOT-223

LMS8117AMP-ADJ LS0A 1k Tape and Reel MP04A

LMS8117AMPX-ADJ LS0A 2k Tape and Reel

LMS8117AMP-1.8 LS00 1k Tape and Reel

LMS8117AMPX-1.8 LS00 2k Tape and Reel

LMS8117AMP-3.3 LS01 1k Tape and Reel

LMS8117AMPX-3.3 LS01 2k Tape and Reel

3-lead TO-252 LMS8117ADT-ADJ LMS8117ADT-ADJ Rails TD03B

LMS8117ADTX-ADJ LMS8117ADT-ADJ 2.5k Tape and Reel

LMS8117ADT-1.8 LMS8117ADT-1.8 Rails

LMS8117ADTX-1.8 LMS8117ADT-1.8 2.5k Tape and Reel

LMS8117ADT-3.3 LMS8117ADT-3.3 Rails

LMS8117ADTX-3.3 LMS8117ADT-3.3 2.5k Tape and Reel

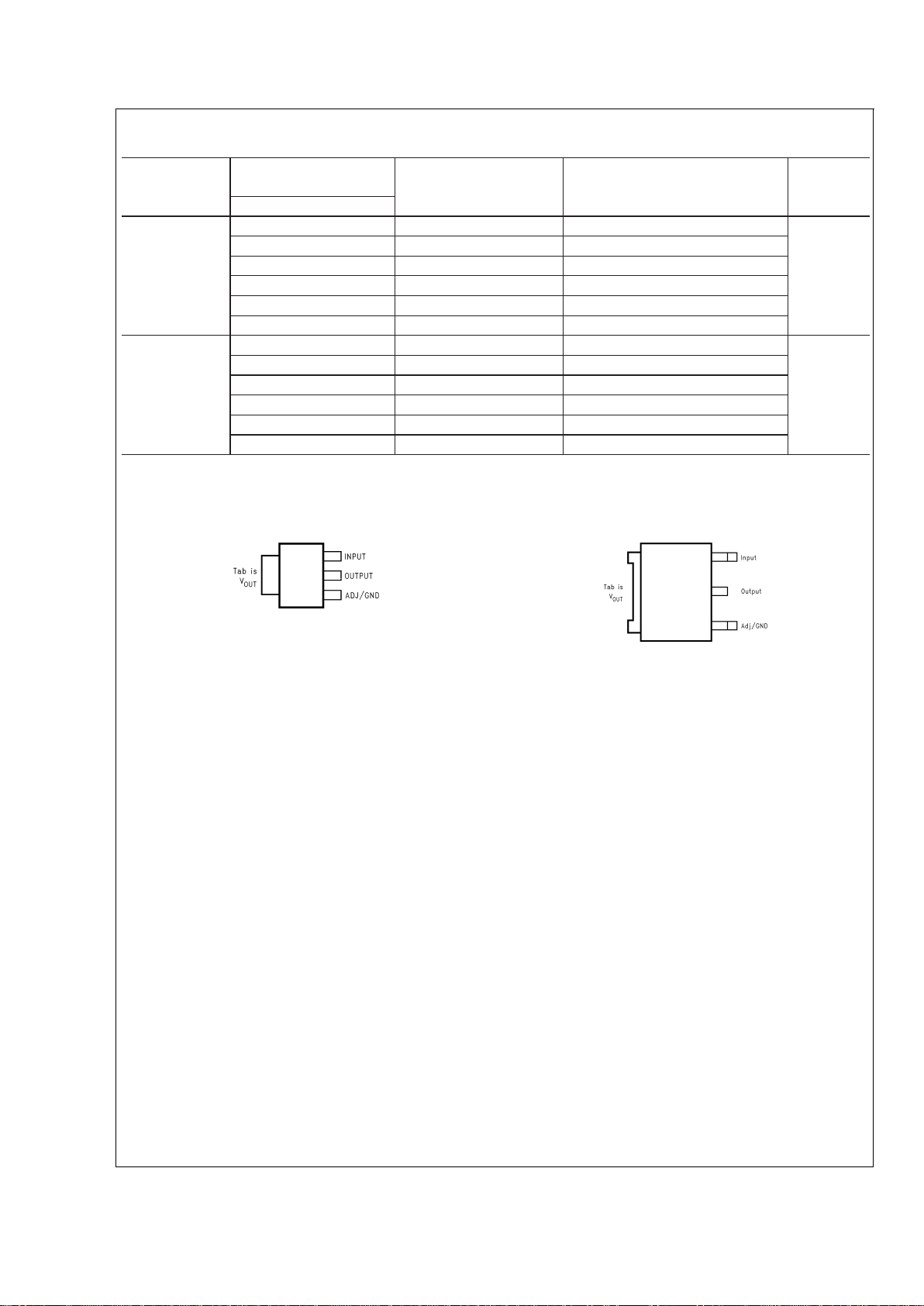

Connection Diagrams

SOT-223

DS101196-99

Top View

TO-252

DS101196-38

Top View

LMS8117A

www.national.com 2

Page 3

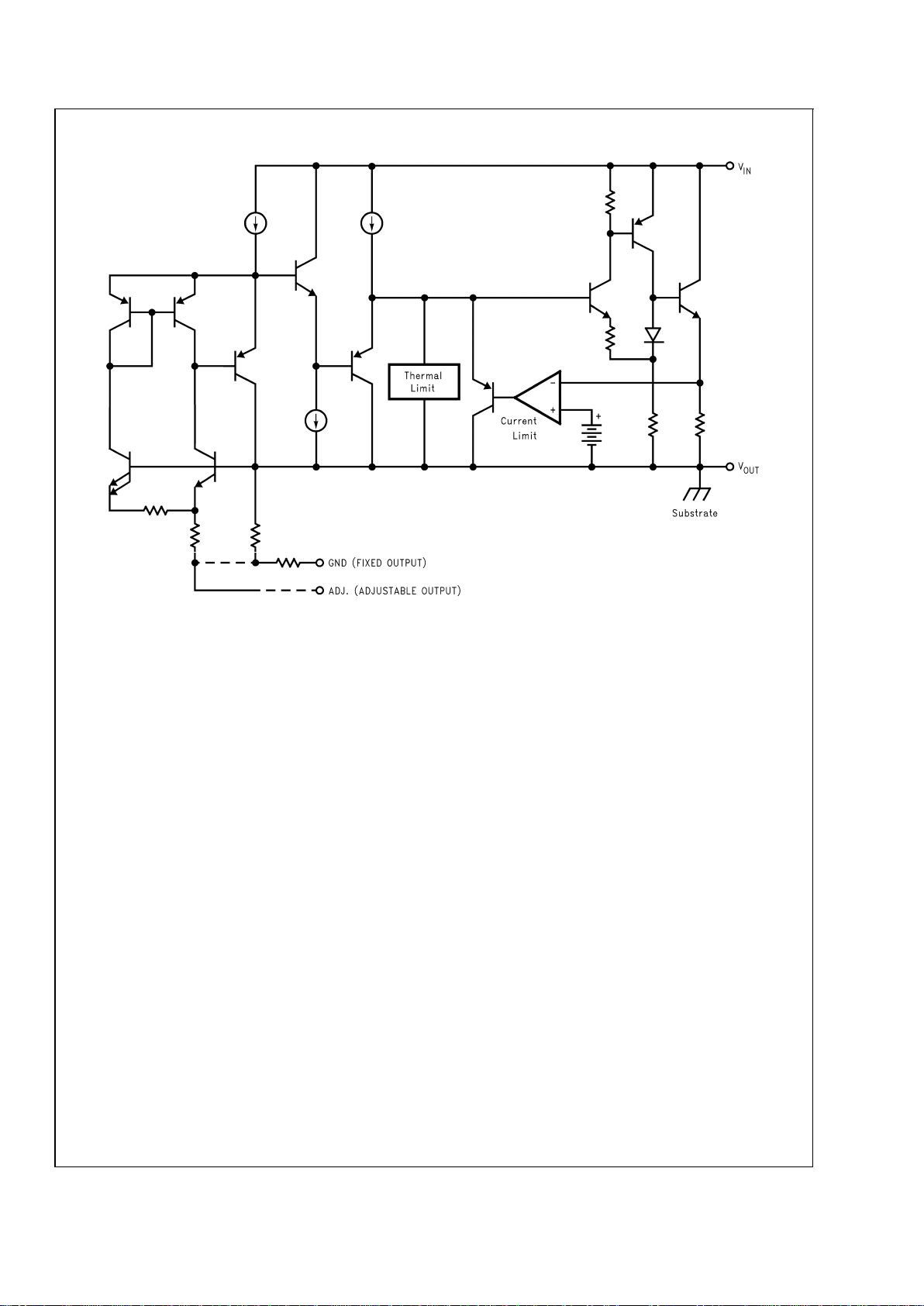

Block Diagram

DS101196-1

LMS8117A

www.national.com3

Page 4

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Maximum Input Voltage (V

IN

to GND)

LMS8117A-ADJ, LMS8117A-1.8,

LMS8117A-3.3 20V

Power Dissipation (Note 2) Internally Limited

Junction Temperature (T

J

)

(Note 2)

150˚C

Storage Temperature Range -65˚C to 150˚C

Soldering Information

Infrared (20 sec) 235˚C

ESD Tolerance (Note 3) 2000V

Operating Ratings (Note 1)

Input Voltage (V

IN

to GND)

LMS8117A-ADJ, LMS8117A-1.8,

LMS8117A-3.3 15V

Junction Temperature Range

(T

J

)(Note 2)

0˚C to 125˚C

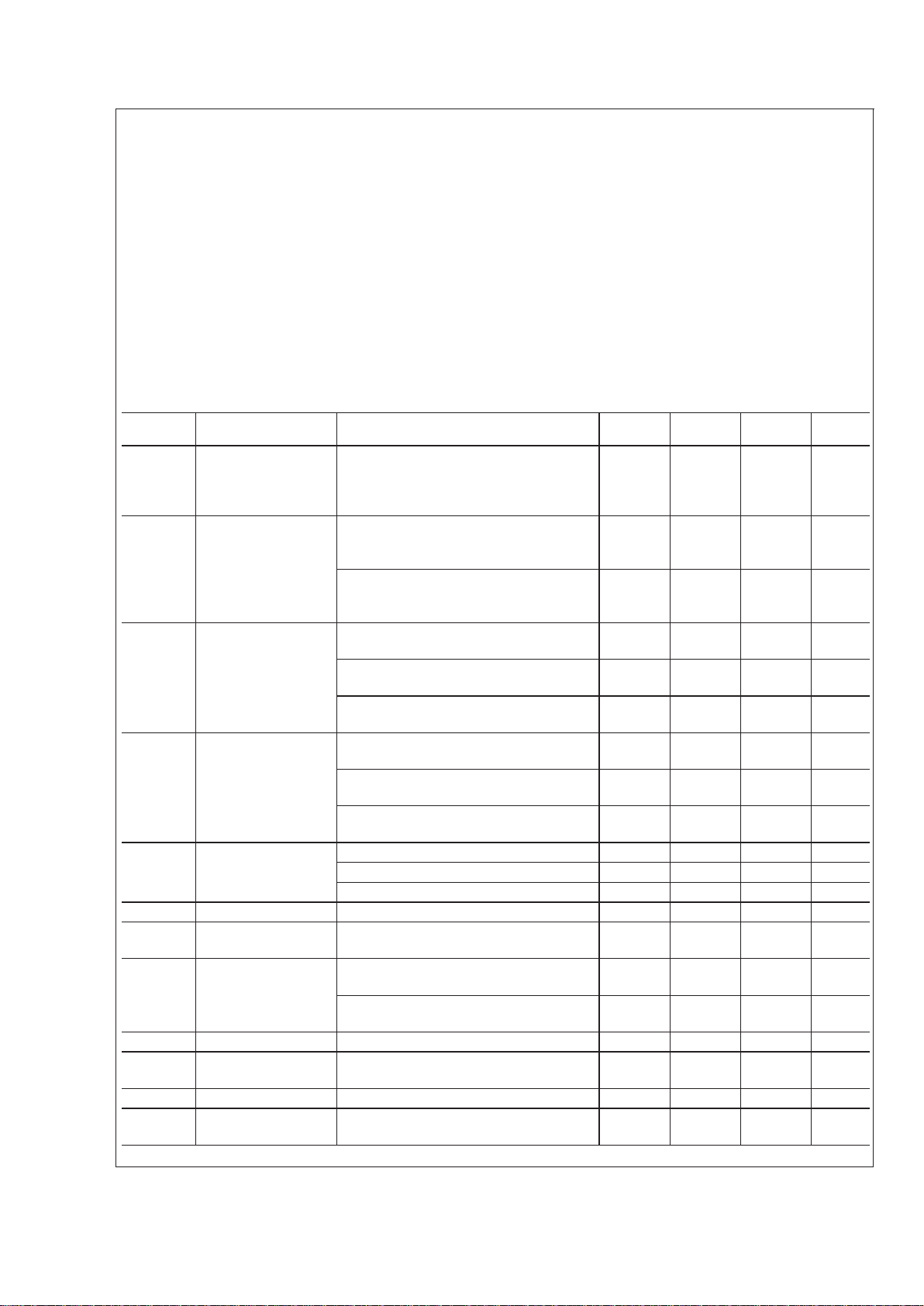

Electrical Characteristics

Typicals and limits appearing in normal type apply for TJ= 25˚C. Limits appearing in Boldface type apply over the entire junction temperature range for operation, 0˚C to 125˚C.

Symbol Parameter Conditions

Min

(Note 5)

Typ

(Note 4)

Max

(Note 5)

Units

V

REF

Reference Voltage LMS8117A-ADJ

I

OUT

= 10mA, VIN-V

OUT

= 2V, TJ= 25˚C

10mA ≤ I

OUT

≤ 1A, 1.4V ≤ VIN-V

OUT

≤

10V

1.238

1.225

1.250

1.250

1.262

1.270

V

V

V

OUT

Output Voltage LMS8117A-1.8

I

OUT

= 10mA, VIN= 3.8V, TJ= 25˚C

0 ≤ I

OUT

≤ 1A, 3.2V ≤ VIN≤ 10V

1.782

1.746

1.800

1.800

1.818

1.854

V

V

LMS8117A-3.3

I

OUT

= 10mA, VIN=5VTJ= 25˚C

0 ≤ I

OUT

≤ 1A, 4.75V ≤ VIN≤ 10V

3.267

3.235

3.300

3.300

3.333

3.365

V

V

∆V

OUT

Line Regulation

(Note 6)

LMS8117A-ADJ

I

OUT

= 10mA, 1.5V ≤ VIN-V

OUT

≤ 13.75V 0.035 0.2 %

LMS8117A-1.8

I

OUT

= 0mA, 3.2V ≤ VIN≤ 10V

1 6 mV

LMS8117A-3.3

I

OUT

= 0mA, 4.75V ≤ VIN≤ 15V 1 6 mV

∆V

OUT

Load Regulation

(Note 6)

LMS8117A-ADJ

V

IN-VOUT

= 3V, 10mA ≤ I

OUT

≤ 1A 0.2 0.4 %

LMS8117A-1.8

V

IN

= 3.2V, 0 ≤ I

OUT

≤ 1A 1 10 mV

LMS8117A-3.3

V

IN

= 4.75V, 0 ≤ I

OUT

≤ 1A 1 10 mV

V

IN-VOUT

Dropout Voltage

(Note 7)

I

OUT

= 100mA 1.1 1.15 V

I

OUT

= 500mA 1.15 1.2 V

I

OUT

= 1A 1.2 1.25 V

I

LIMIT

Current Limit VIN-V

OUT

= 5V, TJ= 25˚C 1.0 1.4 1.9 A

Minimum Load

Current (Note 8)

LMS8117A-ADJ

V

IN

= 15V 1.7 5 mA

Quiescent Current LMS8117A-1.8

V

IN

≤ 15V

5 10 mA

LMS8117A-3.3

V

IN

≤ 15V 5 10 mA

Thermal Regulation T

A

= 25˚C, 30ms Pulse 0.01 0.1 %/W

Ripple Regulation f

RIPPLE

= 120Hz, VIN-V

OUT

=3V

V

RIPPLE

=1V

PP

60 75 dB

Adjust Pin Current 60 120 µA

Adjust Pin Current

Change

10mA ≤ I

OUT

≤ 1A,

1.4V ≤ V

IN-VOUT

≤ 10V 0.2 5 µA

LMS8117A

www.national.com 4

Page 5

Electrical Characteristics (Continued)

Typicals and limits appearing in normal type apply for TJ= 25˚C. Limits appearing in Boldface type apply over the entire junction temperature range for operation, 0˚C to 125˚C.

Symbol Parameter Conditions

Min

(Note 5)

Typ

(Note 4)

Max

(Note 5)

Units

Temperature Stability 0.5 %

Long Term Stability T

A

= 125˚C, 1000Hrs 0.3 %

RMS Output Noise (% of V

OUT

), 10Hz ≤ f ≤ 10kHz 0.003 %

Thermal Resistance

Junction-to-Case

3-Lead SOT-223

3-Lead TO-252

15.0

10

˚C/W

˚C/W

Thermal Resistance

Junction-to-Ambient

(No heat sink;

No air flow)

3-Lead SOT-223

3-Lead TO-252 (Note 9)

136

92

˚C/W

˚C/W

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is

intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

Note 2: The maximum power dissipation is a function of T

J(MAX)

, θJA, and TA. The maximum allowable power dissipation at any ambient temperature is

P

D

=(T

J(MAX)–TA

)/θJA. All numbers apply for packages soldered directly into a PC board.

Note 3: For testing purposes, ESD was applied using human body model, 1.5kΩ in series with 100pF.

Note 4: Typical Values represent the most likely parametric norm.

Note 5: All limits are guaranteed by testing or statistical analysis.

Note 6: Load and line regulation are measured at constant junction room temperature.

Note 7: The dropout voltage is the input/output differential at which the circuit ceases to regulate against further reduction in input voltage. It is measured when the

output voltage has dropped 100mV from the nominal value obtained at V

IN=VOUT

+1.5V.

Note 8: The minimum output current required to maintain regulation.

Note 9: Minimum pad size of 0.038in

2

LMS8117A

www.national.com5

Page 6

Typical Performance Characteristics

Dropout Voltage (VIN-V

OUT

)

DS101196-22

Short-Circuit Current

DS101196-23

Load Regulation

DS101196-24

LMS8117A-ADJ Ripple Rejection vs. Current

DS101196-6

LMS8117A-ADJ Ripple Rejection

DS101196-7

Temperature Stability

DS101196-25

LMS8117A

www.national.com 6

Page 7

Typical Performance Characteristics (Continued)

Adjust Pin Current

DS101196-26

LMS8117A-1.8 Load Transient Response

DS101196-8

LMS8117A-3.3 Load Transient Response

DS101196-9

LMS8117A-1.8 Line Transient Response

DS101196-10

LMS8117A-3.3 Line Transient Response

DS101196-11

LMS8117A

www.national.com7

Page 8

APPLICATION NOTE

1.0 External Capacitors/Stability

1.1 Input Bypass Capacitor

An input capacitor is recommended. A 10µF tantalum on the

input is a suitable input bypassing for almost all applications.

1.2 Adjust Terminal Bypass Capacitor

The adjust terminal can be bypassed to ground with a bypass capacitor (C

ADJ

) to improve ripple rejection. This bypass capacitor prevents ripple from being amplified as the

output voltage is increased. At any ripple frequency, the

impedance of the C

ADJ

should be less than R1 toprevent the

ripple from being amplified:

1/(2π*f

RIPPLE*CADJ

)<R1

The R1 is the resistor between the output and the adjust pin.

Its value is normally in the range of 100-200Ω. For example,

with R1 = 124Ω and f

RIPPLE

= 120Hz, the C

ADJ

should be

>

11µF.

1.3 Output Capacitor

The output capacitor is critical in maintaining regulator stability, and must meet the required conditions for both minimum amount of capacitance and ESR (Equivalent Series

Resistance). The minimum output capacitance required by

the LMS8117A is 10µF, if a tantalum capacitor is used. Any

increase of the output capacitance will merely improve the

loop stability and transient response. The ESR of the output

capacitor should be greater than 0.5Ω and less than 5Ω.In

the case of the adjustable regulator, when the C

ADJ

is used,

a larger output capacitance (22µf tantalum) is required.

2.0 Output Voltage

The LMS8117A adjustable version develops a 1.25V reference voltage, V

REF

, between the output and the adjust ter-

minal. As shown in

Figure 1

, this voltage is applied across

resistor R1 to generate a constant current I1. The current

I

ADJ

from the adjust terminal could introduce error to the

output. Butsince it is very small (60µA) compared with the I1

and very constant with line and load changes, the error can

be ignored. The constant current I1 then flows through the

output set resistor R2 and sets the output voltage to the

desired level.

For fixed voltage devices, R1 and R2 are integrated inside

the devices.

3.0 Load Regulation

The LMS8117A regulates the voltage that appears between

its output and ground pins, or between its output and adjust

pins. In some cases, line resistances can introduce errors to

the voltage across the load. To obtain the best load regulation, a few precautions are needed.

Figure 2

, shows a typical application using a fixed output

regulator. The Rt1 and Rt2 are the line resistances. It is

obvious that the V

LOAD

is less than the V

OUT

by the sum of

the voltage drops along the line resistances. In this case, the

load regulation seen at the R

LOAD

would be degraded from

the data sheet specification. To improve this, the load should

be tied directly to the output terminal on the positive side and

directly tied to the ground terminal on the negative side.

When the adjustable regulator is used (

Figure 3

), the best

performance is obtained with the positive side of the resistor

R1 tied directly to the output terminal of the regulator rather

than near the load.This eliminatesline drops from appearing

effectively in series with the reference and degrading regulation. For example, a 5V regulator with 0.05Ω resistance

between the regulator and load will have a load regulation

due to line resistance of 0.05Ω xI

L

. If R1 (=125Ω) is con-

nected near the load, the effective line resistance will be

0.05Ω (1+R2/R1) or in this case, it is 4 times worse. In

addition, the ground side of the resistor R2 can be returned

near the ground of the load to provide remote ground sensing and improve load regulation.

DS101196-17

FIGURE 1. Basic Adjustable Regulator

DS101196-18

FIGURE 2. Typical Application using Fixed Output

Regulator

LMS8117A

www.national.com 8

Page 9

APPLICATION NOTE (Continued)

4.0 Protection Diodes

Under normal operation, the LMS8117A regulators do not

need any protection diode. With the adjustable device, the

internal resistance between the adjust and output terminals

limits the current. No diode is needed to divert the current

around the regulator even with capacitor on the adjust terminal. The adjust pin can take a transient signal of

±

25V with

respect to the output voltage without damaging the device.

When a output capacitor is connected to a regulator and the

input is shorted toground, the output capacitor will discharge

into the output of the regulator. The discharge current depends on the value of the capacitor,the output voltage of the

regulator, and rate of decrease of V

IN

. In the LMS8117A

regulators, the internal diode between the output and input

pins can withstand microsecond surge currents of 10A to

20A. With an extremely large output capacitor (≥1000 µF),

and with input instantaneously shorted to ground, the regulator could be damaged.

In this case, an external diode is recommended between the

output and input pins to protect the regulator, as shown in

Figure 4

.

5.0 Heatsink Requirements

When an integrated circuit operates with an appreciable

current, itsjunction temperature is elevated. It is important to

quantify its thermal limits in order to achieve acceptable

performance and reliability. This limit is determined by summing the individual parts consisting of a series of temperature rises from the semiconductor junction to the operating

environment. A one-dimensional steady-state model of conduction heat transfer is demonstrated in

Figure 5

. The heat

generated at the device junction flows through the die to the

die attach pad, through the lead frame to the surrounding

case material, to the printed circuit board, and eventually to

the ambient environment. Below is a list of variables that

may affect the thermal resistance and in turn the need for a

heatsink.

R

θJC

(Component Vari-

ables)

R

θCA

(Application Vari-

ables)

Leadframe Size &

Material

Mounting Pad Size,

Material, & Location

No. of Conduction Pins Placement of Mounting

Pad

Die Size PCB Size & Material

Die Attach Material Traces Length & Width

Molding Compound Size

and Material

Adjacent Heat Sources

Volume of Air

Ambient Temperatue

Shape of Mounting Pad

The LMS8117Aregulators haveinternal thermal shutdown to

protect the device from over-heating. Under all possible

operating conditions, the junction temperature of the

LMS8117A must be within the range of 0˚C to 125˚C. A

heatsink may be requireddepending on the maximum power

dissipation and maximum ambient temperature of the application. To determine if a heatsink is needed, the power

dissipated by the regulator, P

D

, must be calculated:

I

IN=IL+IG

PD=(VIN-V

OUT)IL+VINIG

DS101196-19

FIGURE 3. Best Load Regulation using Adjustable

Output Regulator

DS101196-15

FIGURE 4. Regulator with Protection Diode

DS101196-37

FIGURE 5. Cross-sectional view of Integrated Circuit

Mounted on a printed circuit board. Note that the case

temperature is measured at the point where the leads

contact with the mounting pad surface

LMS8117A

www.national.com9

Page 10

APPLICATION NOTE (Continued)

Figure 6

shows the voltages and currents which are present

in the circuit.

The next parameter which must be calculated is the maximum allowable temperature rise, T

R

(max):

T

R

(max)=TJ(max)-TA(max)

where T

J

(max) is the maximum allowable junction tempera-

ture (125˚C), and T

A

(max) is the maximum ambient tem-

perature which will be encountered in the application.

Using the calculated values for T

R

(max) and PD, the maximum allowable value for the junction-to-ambient thermal

resistance (θ

JA

) can be calculated:

θ

JA=TR

(max)/P

D

If the maximum allowable value for θJAis found to be

≥136˚C/W for SOT-223 package or ≥92˚C/W for TO-252

package, noheatsink is needed since the package alone will

dissipate enough heat to satisfy these requirements. If the

calculated value for θ

JA

falls below these limits, a heatsink is

required.

As a design aid,

Table 1

shows the value of the θJAof

SOT-223and TO-252for different heatsink area. The copper

patterns that we used to measure these θ

JA

s are shown at

the end of the Application Notes Section.

Figure 7

and

Figure

8

reflects the same test results as what are in the

Table 1

.

Figure 9

and

Figure 10

shows the maximum allowable power

dissipation vs. ambient temperature for the SOT-223 and

TO-252 device.

Figure 11

and

Figure 12

shows the maxi-

mum allowable power dissipation vs. copper area (in

2

) for

the SOT-223 and TO-252 devices. Please see AN1028 for

power enhancement techniques to be used with SOT-223

and TO-252 packages.

TABLE 1. θ

JA

Different Heatsink Area

Layout Copper Area Thermal Resistance

Top Side (in

2

)* Bottom Side (in2)(θ

JA

,˚C/W) SOT-223 (θJA,˚C/W) TO-252

1 0.0123 0 136 103

2 0.066 0 123 87

3 0.3 0 84 60

4 0.53 0 75 54

5 0.76 0 69 52

61 0 66 47

7 0 0.2 115 84

8 0 0.4 98 70

9 0 0.6 89 63

10 0 0.8 82 57

11 0 1 79 57

12 0.066 0.066 125 89

13 0.175 0.175 93 72

14 0.284 0.284 83 61

15 0.392 0.392 75 55

16 0.5 0.5 70 53

*Tab of device attached to topside copper

DS101196-16

FIGURE 6. Power Dissipation Diagram

LMS8117A

www.national.com 10

Page 11

APPLICATION NOTE (Continued)

DS101196-13

FIGURE 7. θJAvs. 1oz Copper Area for SOT-223

DS101196-34

FIGURE 8. θJAvs. 2oz Copper Area for TO-252

DS101196-12

FIGURE 9. Maximum Allowable Power Dissipation vs.

Ambient Temperature for SOT-223

DS101196-36

FIGURE 10. Maximum Allowable Power Dissipation vs.

Ambient Temperature for TO-252

DS101196-14

FIGURE 11. Maximum Allowable Power Dissipation vs.

1oz Copper Area for SOT-223

DS101196-35

FIGURE 12. Maximum Allowable Power Dissipation vs.

2oz Copper Area for TO-252

LMS8117A

www.national.com11

Page 12

APPLICATION NOTE (Continued)

DS101196-20

FIGURE 13. Top View of the Thermal Test Pattern in Actual Scale

LMS8117A

www.national.com 12

Page 13

APPLICATION NOTE (Continued)

DS101196-21

FIGURE 14. Bottom View of the Thermal Test Pattern in Actual Scale

LMS8117A

www.national.com13

Page 14

Typical Application Circuits

DS101196-29

1.25V to 10V Adjustable Regulator with Improved Ripple Rejection

DS101196-27

5V Logic Regulator with Electronic Shutdown*

LMS8117A

www.national.com 14

Page 15

Physical Dimensions inches (millimeters) unless otherwise noted

3-Lead SOT-223

NS Package Number MP04A

LMS8117A

www.national.com15

Page 16

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL

COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or

systems which, (a) are intended for surgical implant

into the body, or (b) support or sustain life, and

whose failure to perform when properly used in

accordance with instructions for use provided in the

labeling, can be reasonably expected to result in a

significant injury to the user.

2. A critical component is any component of a life

support device or system whose failure to perform

can be reasonably expected to cause the failure of

the life support device or system, or to affect its

safety or effectiveness.

National Semiconductor

Corporation

Americas

Email: support@nsc.com

National Semiconductor

Europe

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor

Asia Pacific Customer

Response Group

Tel: 65-2544466

Fax: 65-2504466

Email: ap.support@nsc.com

National Semiconductor

Japan Ltd.

Tel: 81-3-5639-7560

Fax: 81-3-5639-7507

www.national.com

3-Lead TO-252

NS Package Number TD03B

LMS8117A 1A Low-Dropout Linear Regulator

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

Loading...

Loading...