Page 1

LM9833 48-Bit Color, 1200dpi USB Image Scanner

General Description

The LM9833 is a complete USB image scanner system on a single IC. The LM9833 provides all the functions (image sen sor

control, illumination control, analog front end, pixel processing

function image data buffer/DRAM controller, microstepping

motor controller, and USB interface) necessary to crea te a high

performance color scann er. The LM9833 scans imag es in 48 bit

color/16 bit gray, and has output data formats for 48 and 24bit

color/16 and 8 bit gray. The LM9833 su pp orts sensors with pixel

counts of up to 16384 pixels x 3 colors (1200 dpi x 13.6 inches).

The LM9833’s low operating and suspend mode supply currents

allow design of USB bus- powe re d scan ne rs. T he only a dditional

active components required are an external 4Mbit or 16Mbit

DRAM for data bufferi ng and power transistors fo r the stepper

motor.

Applications

•

Color Flatbed Document Scanners

•

Color Sheetfed Document Scanners

Key Specifications

•

Analog to Digital Converter Resolution 16 Bits

•

Maximum Pixel Conversion Rate 6MHz

•

A4 Color 150dpi scan time <10 seconds

•

A4 Color 300dpi scan time <40 seconds

•

A4 Color 600dpi scan time <160 seconds

•

Supply Voltage

- LM9833 +4.75V to +5.25V

- LM9833 DRAM I/O +2.85 to +5.25V

•

Maximum Operating Current Consumption 136mA

•

Maximum Suspend Current Consumption 175µA

Features

• 16 bit ADC digitizes at up to 6Mpixels/s (2M RGB pixels/sec).

• Digital Pixel Processing provid es 1200, 800, 600, 400, 300,

200, 150, and 100dpi horizontal resolution from a 1200dpi

sensor and 600, 400, 300, 200, 150, 100, 75, and 50dpi

horizontal resolution from a 600dpi sensor.

• Provides 50-2400dpi vertical resolution in 1 dpi increments.

• Pixel rate error correction for gain (shading) and offset errors.

• Supports 4 or 16Mbit external DRAMs.

• Multiple CCD clocking rates allows matching of CCD clock to

scan resolution and pixel depth for maximum scan speed.

• Stepper motor control ti ghtly coupled with imag e data buffer

management to maximize data transfer efficiency.

• PWM stepper motor current control allows microsteppi ng for

the price of fullstepping.

• USB interface f or Plug and P lay o peration on U SB-equipp ed

computers.

• Serial EEPROM option for custom Vendor and Product IDs.

• Support for USB bus-powered operation.

• Pixel depths of 1, 2, or 4 bits are packed into bytes for faster

scans of line art and low pixel depth images.

• Supports 3 channel CCDs and 1 channel CIS sensors.

• 3 (R, G, and B) 12-bit, u ser-programmable gam ma cor rect ion

tables.

• Compatible with a wide range of color linear CCDs and

Contact Image Sensors (CIS).

• Operates with 48MHz external crystal.

• Internal bandgap voltage reference.

• 100 pin TQFP package

LM9833 48-Bit Color 1200dpi USB Image Scanner

October 2001

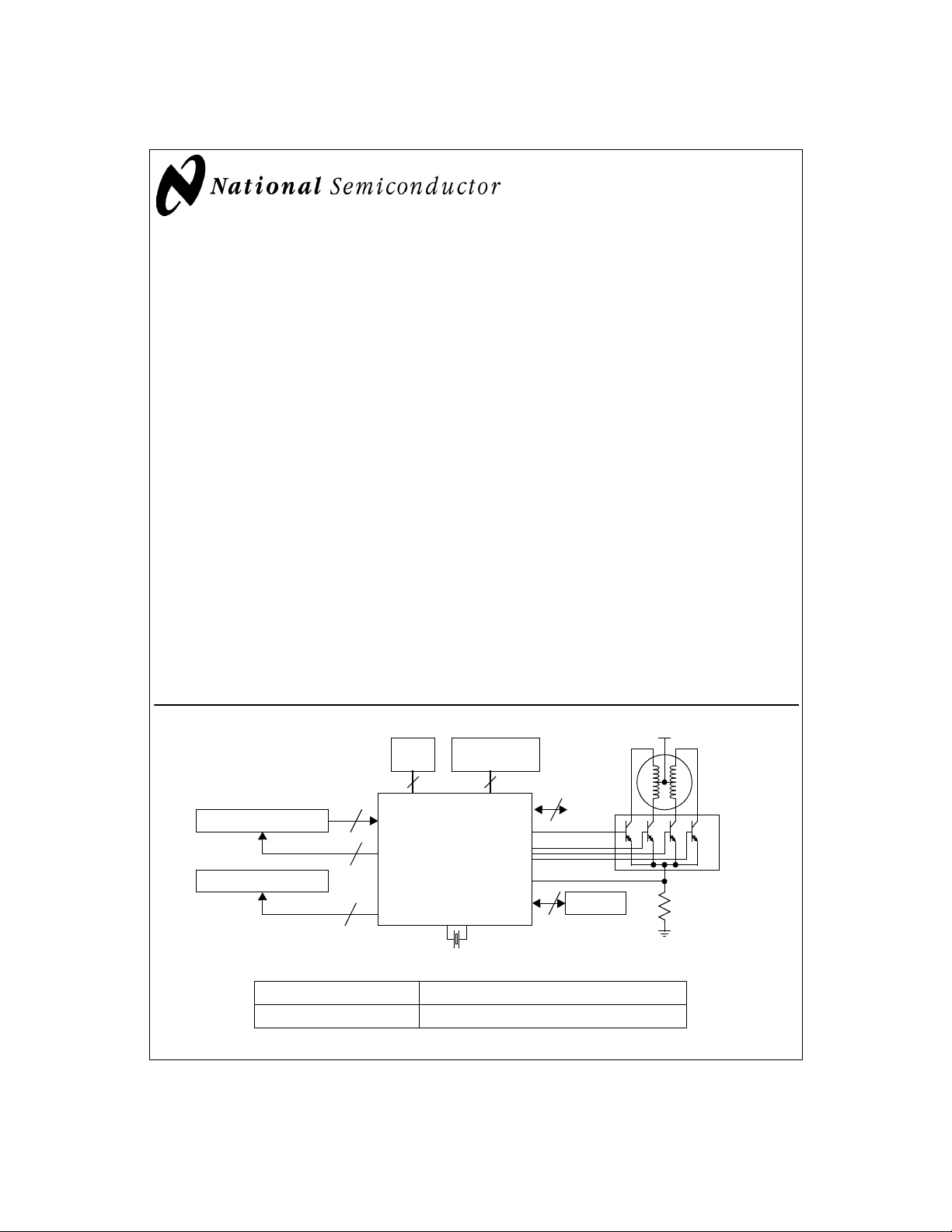

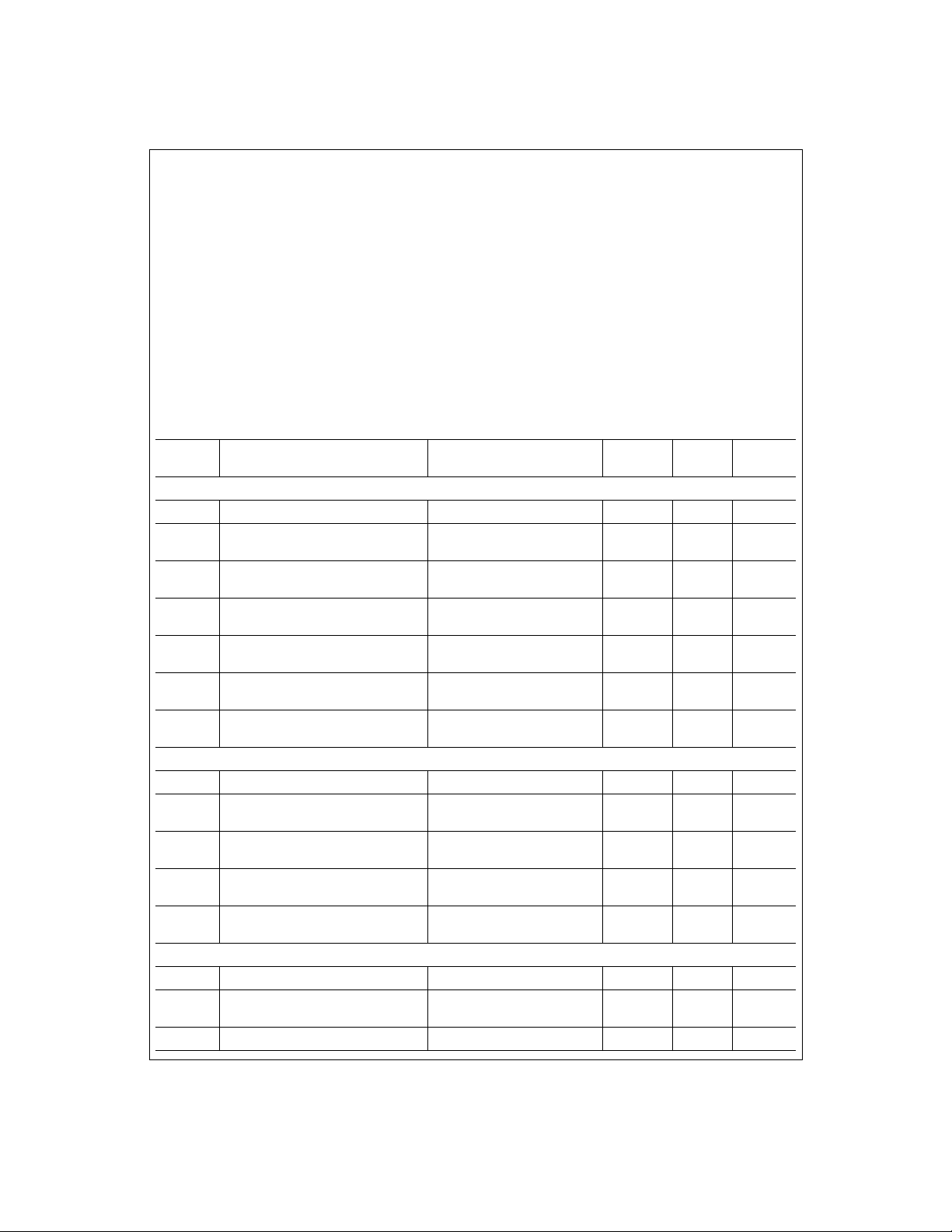

LM9833 Scanner System Block Diagram

USB

Port

2

2-6

1-3

1-3

LM9833CCVJD

CCD/CIS

Illumination

Ordering Information

Commercial (0°C ≤ TA ≤ +70°C) Package

LM9833CCVJ D VJD100A 100 Pin Thin Quad Flatpac

©2000 National Semiconductor Corporation

Serial

EEPROM

2

8MISC

I/O

30

DRAM

48MHz Crystal

1 www.national.com

+12V

Stepper

Motor

Power

Transistors

Page 2

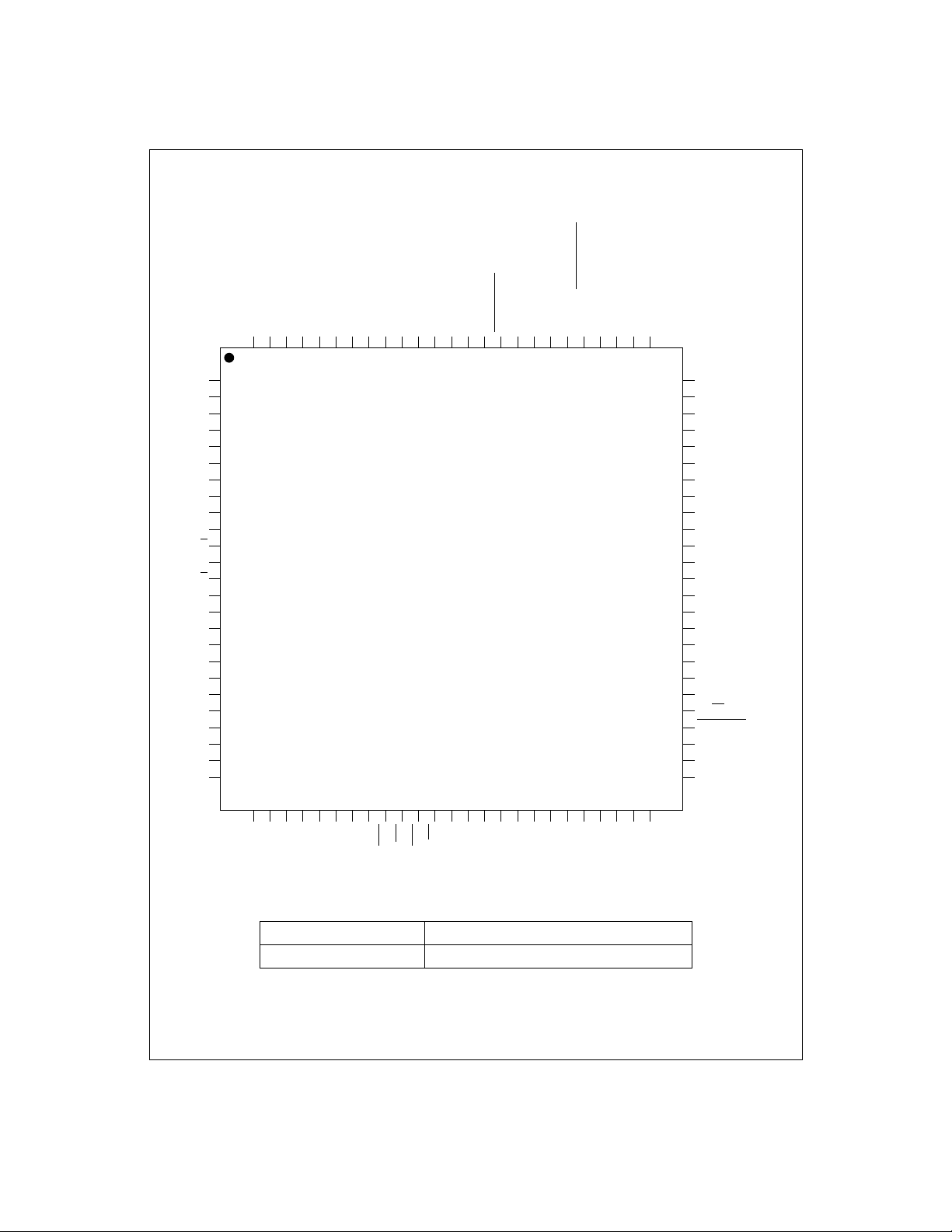

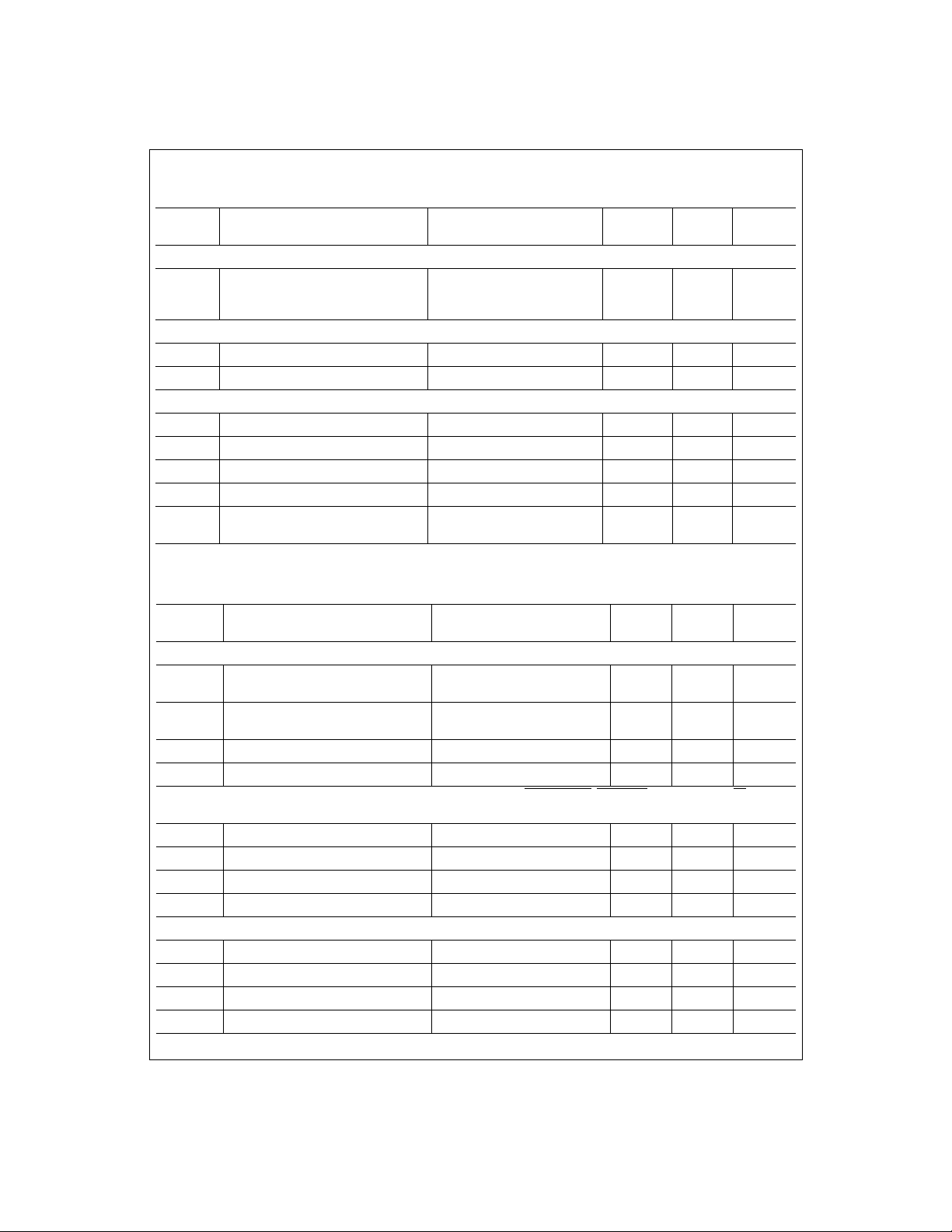

Connection Diagram

LM9833

V

BANDGAP

V

REF LO

V

REF MID

V

REF HI

AGND

V

DGND

OS

OS

OS

D0

D15

DRAM

D1

D14

D2

D13

D3

D12

D4

D11

AGND VADGND VDTEST SENSEGND SENSEA SENSEB NC CMODE RESET NC NC DGND VDBUS POWR D+ D- V

REGULATOR

DGND ACTIVE/SUSPENDED CP2 CP1 RS ø2

100999897969594939291908988878685848382818079787776

1

2

3

R

4

5

G

6

7

B

8

V

9

A

A

10

A

11

B

12

B

13

14

LM9833CCVJD

15

16

17

18

19

20

21

22

23

24

25

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

ø1

TR2

TR1

MISC I/O 6

MISC I/O 5

MISC I/O 4

DGND

V

MISC I/O 3

MISC I/O 2

MISC I/O 1

D

PAPER SENSE 1

PAPER SENSE 2

V

D

DGND

LAMP

B

LAMP

G

LAMP

R

DGND

V

D

24/48

CRYSTAL/EXT CLK

CRYSTAL IN

CRYSTAL OUT

SCL

26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

D5

D6

D9

D10

Ordering Information

Commercial (0°C ≤ TA ≤ +70°C) Package

LM9833CCVJD VJD100A 100 Pin Thin Quad Flatpac

DRAM

V

D7

DGND

D8

A9A8A0A7A1

RD

WR

RAS

CAS

A6A2A5A3A4

DRAM

DGND

V

SDA

2 www.national.com

Page 3

Pin Descriptions

USB Interface

D+, D- Digital I/O. USB Interface signals

BUS POWER

ACTIVE/

SUSPENDED

SDA Digital I/O. Serial Data to/from external

SCL Digital Output. Serial Clock Output to externa l

Digital Input. Tie low for bus powered systems, tie high for external power.

Digital Output. Low in Suspend mode. High in

operational mode. Used to control external

regulators, other components.

EEPROM.

EEPROM.

Analog

OSR,

OS

,

G

OS

B

V

REF LO

V

REF MID

V

REF HI

V

BANDGAP

Analog Inputs. The se inpu ts (for Re d, Green ,

and Blue) should be tied to the sensor ’s output signal through DC bloc king capacitors. If

unused, tie to ground through DC blocking

capacitors.

Analog Output/Input . Bypass to AGND with a

0.047µF monolithic capacitor. Do not put a

DC load on this pin.

Analog Output/Input . Bypass to AGND with a

0.047µF monolithic capacitor. Do not put a

DC load on this pin.

Analog Output/Input . Bypass to AGND with a

0.047µF monolithic capacitor. Do not put a

DC load on this pin.

Analog Output. Bypass to AGND with a

0.047µF monolithic capacitor. Do not put a

DC load on this pin.

DRAM

D0 (LSB) -D15

(MSB)

RD

WR

A0-A9 Digital Outputs. Addre ss pins for up to 1M x

RAS

CAS

Digital Inputs/Outp uts. This is the 16 bit data

path between the external DRAM and the

LM9833.

Digital Output. Read signal to external DRAM.

Digital Output. Write signal to external DRAM.

16 external DRAM.

Digital Output. Row Address Strobe signal.

Digital Output. Column Address Strobe sig-

nal.

Scanner Support I/O

PAPER

SENSE 1-2

MISC I/O 1-6 Digital Inputs/Outputs. Programmable, used

Digital Inputs. P rogrammable, u sed for sensing home position, paper, front panel

switches, etc.

for front panel switches, status LEDs, etc. A t

power-on and in Susp end Mode, MISC I/Os

1-3 are inputs and MISC I/Os 4-6 are outputs.

Stepper Motor

A, B, A, B Digital Outputs. Pulses to stepper motor drive

SENSE

A

SENSE

B

SENSE

GND

circuitry.

,

Analog Inputs. Current sensing for stepper

motor’s PWM current control.

Analog Input. Ground sen se input for stepper

motor’s PWM current control.

Sensor Control

ø1 Digital Output. CCD/CIS clock signal phase 1.

ø2 Digital Output. CCD/CIS clock signal phase 2.

RS Digital Output. Reset pulse for the CCD/CIS.

CP1 Digital Output. Clamp pulse for the CCD/CIS.

CP2 Digital Output. Clamp pulse for the CCD/CIS.

TR1, TR2 Digital Outputs. Transfer pulses for the

,

LAMP

R

LAMP

,

G

LAMP

B

CCD/CIS.

Digital Outputs. Us ed to control R, G, and B

LEDs of single output CIS, as well as brightness of CCFL. The CDS signal can be se en

on LAMP

7).

in a test mode (see registe r 5E, bi t

B

Master Clock Generation

CRYSTAL IN Digital Input. Used with CRYSTAL OUT and

CRYSTAL

OUT

CRYSTAL

EXT CLOCK

24/48

an external 48MHz crystal to form a crystal

oscillator.

Digital Output. Used with CRYST AL IN and an

external 48MHz crystal to form a crystal oscillator.

/

Digital Input. Tie to DGND for operati on with

an external crystal. Pull up to V

CRYSTAL OUT with an external TTL or

CMOS clock source.

Digital Input. Tie to DGND for operation with a

48MHz crystal or exter nal clo ck. P ull up to V

for operation with a 2 4M H z crystal o r e xter na l

clock. NOTE: Operation at 24MHz is not guaranteed - always use a 48MHz crystal.

to drive

D

Miscellaneous

V

REGULATOR

RESET Digital input. Take high to force device into

TEST Analog Output.

CMODE Digital Input. Test mode, always tie high.

Digital Output. This is the regu late d 3.3 V supply (generated from V

transceiver. It should be us ed as th e termina l

voltage for the 1.5k D+ pullup resistor, and

bypassed to DGND with a 0.047µF monolithic

capacitor.

Power On Reset state, low to exit reset state.

) that powers the USB

D

LM9833

D

3 www.national.com

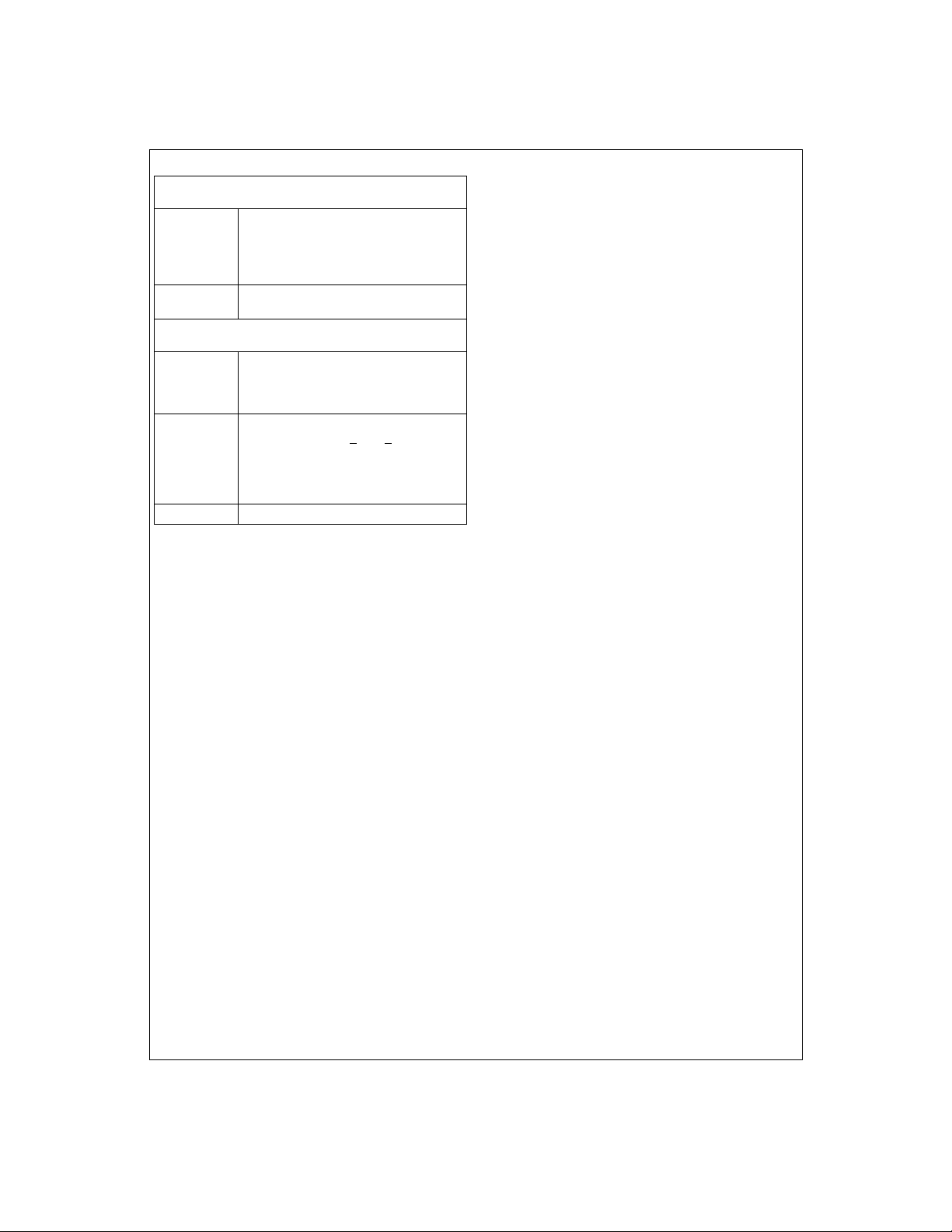

Page 4

Pin Descriptions

Analog Power Supplies (4 pins)

LM9833

VA (2) This is the positive supply pin for the analog

AGND (2) This is the ground retu rn for the analog sup-

supply. It should be connected to a voltage

source of +5V and bypassed to AGND with a

0.1µF monolithic capacitor in parallel with a

10µF tantalum capacitor.

ply.

(Continued)

Digital Power Supplies (17 pins)

VD (5) This is the positive su pply pin for the digital

V

(3) This is the positiv e supply pin for the digital

DRAM

DGND (9) This is the ground return for V

supply. It should be connected to a voltage

source of +5V and bypassed to DGND with a

0.1µF monolithic capacitor.

supply for the LM9833’s external DRAM I/O. It

also powers th e A, B , A

outputs. It should be conne cted to a 3 or 5V

supply and bypassed to the closest DGND pin

with a 0.1µF monolithic capacitor.

, and B stepper motor

and V

D

DRAM

.

4 www.national.com

Page 5

LM9833

DRAM

(Notes 1 & 2)

)

+

+0.3V

Operating Ratings

Operating Temperature Range T

LM9833CCVJD 0°C≤T

V

Supply Voltage +4.75V to +5.25V

A

V

Supply Voltage +4.75V to +5.25V

D

V

Supply Voltage +2.85V ≤ V

DRAM

|V

| ≤ 100mV

A-VD

Input Voltage Range -0.05V to V

Absolute Maximum Ratings

Positive Supply Voltage (V+=VA=VD=V

With Respect to GND=AGND=DGND 6.5V

Voltage On Any Input or Output Pin -0.3V to V

Input Current at any pin (Note 3) ±25mA

Package Input Current (Note 3) ±50mA

Package Dissipation at T

ESD Susceptibility (Note 5)

Human Body Model 2000 V

= 25°C (Note 4)

A

Machine Model 250 V

Soldering Information

Infrared, 10 seconds (Note 6) 235°C

Storage Temperature -65°C to +150°

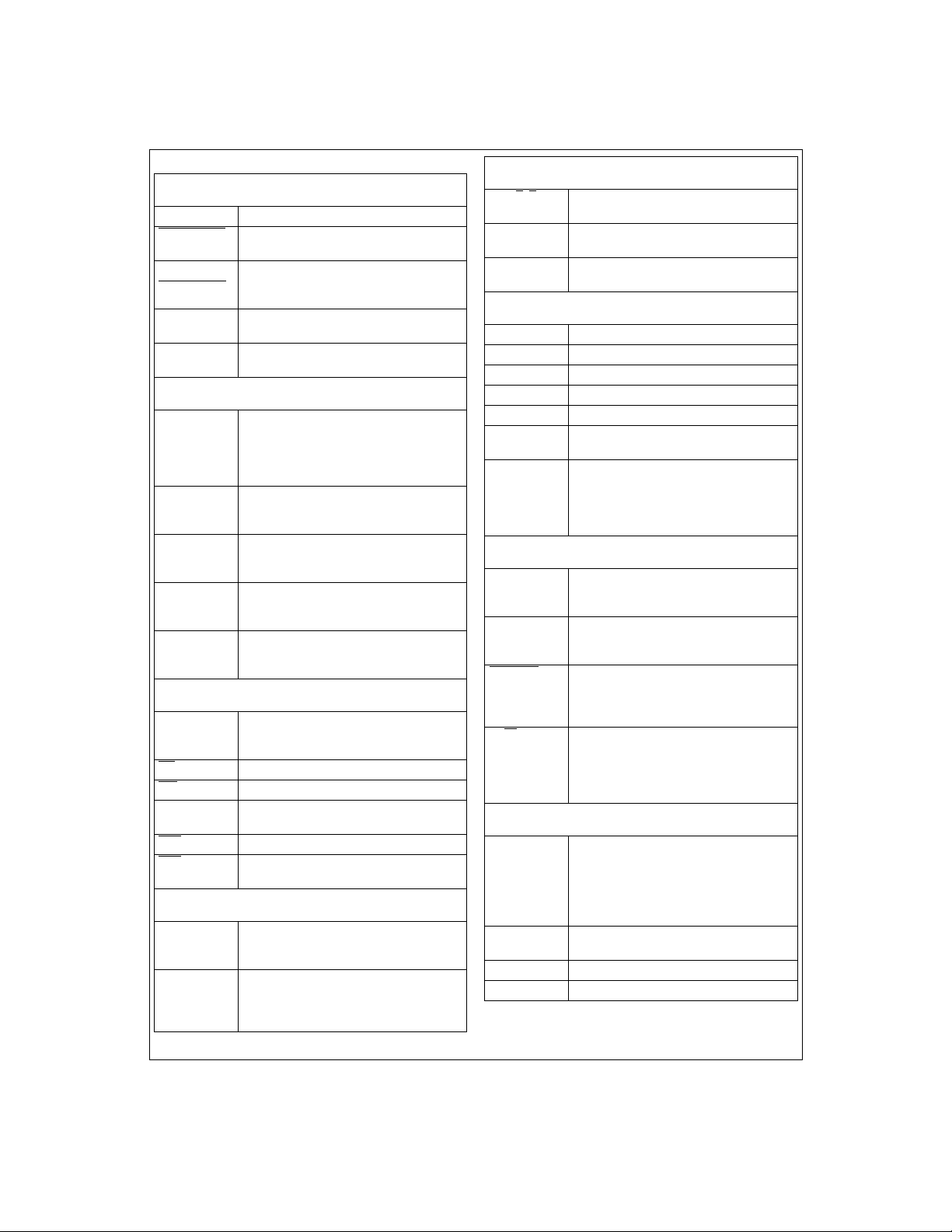

Electrical Characteristics

The following specifications apply for AGND=DGND=0V, VA=VD=V

100%, unless otherwise noted. Boldface limits apply for T

A=TJ=TMIN

Symbol Parameter Conditions

Full Channel Characteristics (in units of 12 bit LSBs unless otherwise noted)

Resolution with No Missing Codes 16 12 bits (min)

DNL

INL

V

OS1

V

OS2

V

OS3

Differential Non-Linear ity

(Note 14)

Integral Non-Lineari ty Error

(Notes 11 & 14)

Analog Channel Gain Constant

C

(ADC Codes/V), referred to 16 bi ts.

Pre-Boost Analog Channel Offset Error 26

Pre-PGA Analog Channel Offset Error -30

Post-PGA Analog Channel Offset Error -26

Bias Current = 80%,

V

DRAM

Bias Current = 80%,

V

DRAM

Includes voltage reference

variation, gain setting = 1

Coarse Color Balance PGA Characteristics (Configuration Registers 3B, 3C, and 3D)

Monotonicity 5 bits (min)

(Minimum PGA Gain) PGA Setting = 0 0.93

G

0

(Maximum PGA Gain) PGA Setting = 31 3.00

G

31

x3 Boost Gain

x3 Boost Setting On

(bit B5 of Gain Register is set)

Gain Error at any gain (Note 13) 0.3

Static Offset DAC Characteristics (Configuration Registers 38, 39, and 3A)

Monotonicity 6 bits (min)

Offset DAC LSB size PGA gain = 1 9

Offset DAC Adjustment Range PGA gain = 1 ±278 ±256 mV (min)

DRAM

=3.3V

=3.3V

=+5.0VDC, f

to T

CRYSTAL IN

; all other limits TA=TJ=25°C. (Notes 8, 9, & 10)

MAX

(Notes 1 & 2)

MIN≤TA≤TMAX

≤+70°C

A

≤ V

DRAM

+100mV

D

+

+ 0.05V

= 48MHz, Analog Bias Current =

Typical

(Note 9)

-0.45

+0.75

-2.3

+1.7

32768

2.94

Limits

(Note 10)

-0.9

+2.4

-8.5

+7.5

29648

37200

-34

+76

-80

+31

-75

+26

0.90

0.96

2.95

3.10

2.85

3.04

-0.6

+0.9

6

12

Units

(Limits)

LSB (min)

LSB (max)

LSB (min)

LSB (max)

LSB (min)

LSB (max)

mV (min)

mV (max)

mV (min)

mV (max)

mV (min)

mV (max)

V/V (min)

V/V (max)

V/V (min)

V/V (max)

V/V (min)

V/V (max)

% (min)

% (max)

mV (min)

mV (max)

5 www.national.com

Page 6

Electrical Characteristics

The following specifications apply for AGND=DGND=0V, V

100%, unless otherwise noted. Boldface limits apply for T

LM9833

(Continued)

A=VD=VDRAM

A=TJ=TMIN

=+5.0VDC, f

to T

CRYSTAL IN

; all other limits TA=TJ=25°C. (Notes 8, 9, & 10)

MAX

Symbol Parameter Conditions

CCD/CIS Source Requiremen ts for Full Spec ified Accura cy and Dynamic Range (Note 12)

V

CCDPEAK

Sensor’s Maximum Outp ut Sig nal

Amplitude before LM9833 Analog Front

End Saturation

Gain = 0.933

Gain = 3.0

Gain = 9.0

Analog Input Characteristics

Average OS

OS

R

, OSG, OSB Input Current CDS Enabled, OS = 3.5V

R

, OSG, OSB Input Current CDS Disabled, OS = 3.5V

DC

DC

Internal Voltage Reference Characteristics

V

BANDGAP

V

REF LO

V

REF MID

V

REF HI

V

REGULA-

TOR

Voltage Reference Output Voltage 1.23 V

Negative Reference Output Voltage V

Midpoint Reference Output Voltage VA/2.0 V

Positive Reference Output Voltage

USB I/O Voltage Regulator 3.3 V

DC and Logic Electrical Characteristics

The following specifications apply for AGND=DGND=0V, VA=VD=V

f

CRYSTAL IN

= 48MHz. Boldface limits apply for TA=TJ=T

MIN

to T

Symbol Parameter Conditions

Digital Input Characteristics for D0-D15 (DRAM Interface)

V

V

V

C

Logical “1” Input Voltage

IN(1)

Logical “0” Input Voltage

IN(0)

Input Leakage Current ±0.1 µA

I

IN

Input Capacitance 5 pF

IN

V

V

V

DRAM

DRAM

DRAM

DRAM

Digital Input Characteristics for PAPER SENSE 1-2, MISC I/O 1-6, SDA, BUS POWER

CMODE

V

V

C

Logical “1” Input Voltage VD=5.25V 2.0 V (min)

IN(1)

Logical “0” Input Voltage VD=4.75V 0.8 V (ma x)

IN(0)

Input Leakage Current ±0.1 µA

I

IN

Input Capacitance 5 pF

IN

Digital Input Characteristics for D+, D-

V

V

C

Logical “1” Input Voltage VD=5.25V 2.0 V (min)

IN(1)

Logical “0” Input Voltage VD=4.75V 0.8 V (ma x)

IN(0)

Input Leakage Current ±0.1 µA

I

IN

Input Capacitance 5 pF

IN

=+5.0VDC unless otherwise noted,

DRAM

; all other limits TA=TJ=25°C. (Notes 8, 9, & 10)

MAX

=5.25V

=3.6V

=4.75V

=2.85V

= 48MHz, Analog Bias Current =

Typical

(Note 9)

1.9

0.6

0.19

Limits

(Note 10)

Units

(Limits)

V

V

V

±3 nA

±26 ±30 µA (max)

-1.0 V

REF MID

V

+1.0 V

REF MID

Typical

(Note 9)

Limits

(Note 10)

2.0

2.0

0.8

0.8

Units

(Limits)

V (min)

V (min)

V (max)

V (max)

, CRYSTAL/EXT CLOCK, 24/48, RESET,

6 www.national.com

Page 7

A=VD=VDRAM

to T

MIN

MAX

(Continued)

=+5.0VDC unless otherwise noted,

; all other limits TA=TJ=25°C. (Notes 8, 9, & 10)

DC and Logic Electrical Characteristics

The following specifications apply for AGND=DGND=0V, V

f

CRYSTAL IN

= 48MHz. Boldface limits apply for TA=TJ=T

Symbol Parameter Conditions

Digital Output Characteristics for D0-D15, A0-A9, RD

V

OUT(1)

V

OUT(0)

Digital Output Characteristics for A, B, A

V

OUT(1)

V

OUT(0)

Logical “1” Output Voltage

Logical “0” Output Voltage

, B

Logical “1” Output Voltage

Logical “0” Output Voltage

, WR, RAS, CAS (DRAM Interface)

V

V

V

V

V

V

V

V

DRAM

DRAM

DRAM

DRAM

DRAM

DRAM

DRAM

DRAM

=4.75V, I

=2.85V, I

=4.75V, I

=2.85V, I

=4.75V, I

=2.85V, I

=4.75V, I

=2.85V, I

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

=-4mA

=-4mA

=4mA

=4mA

=-10mA

=-10mA

=4mA

=4mA

Digital Output Characteristics for MISC I/O 1-6, TR1, TR2, ø1, ø2, RS, CP1, CP2, LAMP

V

V

OUT(1)

OUT(0)

Logical “1” Output Voltage VD=4.75V, I

Logical “0” Output Voltage VD=4.75V, I

=-4mA 2.4 V (min)

OUT

=4mA 0.4 V (ma x)

OUT

Digital Output Characteristics for D+, D-

V

V

OUT(1)

OUT(0)

Logical “1” Output Voltage VD=4.75V, I

Logical “0” Output Voltage VD=4.75V, I

=-1mA 2.4 V (min)

OUT

=3mA 0.4 V (ma x)

OUT

CRYSTAL IN, CRYSTAL OUT Characteristics

XTAL

XTAL

CRYSTAL OUT Bias Level (Offset) 0.8 V

OUT DC

CRYSTAL OUT Amplitude f

OUT AC

= 48MHz 0.8 V

CRYSTAL

Power Supply Characteristics (Note 14)

I

A

I

D

I

DRAM

I

SUSPEND

Analog Supply Current

(V

pins)

A

Digital Supply Current

(V

pins)

D

DRAM Supply Current

(V

pins)

DRAM

Total Suspend Current (IA+ID+I

DRAM

Operating (Bias Current = 80%) 65 91 mA (max)

Operating (Bias Current = 80%) 35 41 mA (max)

Operating, V

Operating, V

DRAM

DRAM

= 5V

= 3V

)19175 µA (max)

Typical

(Note 9)

, LAMPG, LAMP

R

2

1

Limits

(Note 10)

2.4

2.4

0.4

0.4

2.4

2.4

0.4

0.4

B

8

5

LM9833

Units

(Limits)

V (min)

V (min)

V (max)

V (max)

V (min)

V (min)

V (max)

V (max)

P-P

mA (max)

mA (max)

7 www.national.com

Page 8

AC Electrical Characteristics

The following specifications apply for AGND=DGND=0V, VA=VD=V

LM9833

f

CRYSTAL IN

C

= 48MHz, MCLK DIVIDER = 1.0 (unless otherwise noted), f

(databus loading) = 20pF/pin. Boldface limits apply for TA=TJ=T

L

Symbol Parameter Conditions

DRAM Timing (Figure 1)

=5.0V

V

t

RD SETUP

t

RD HOLD

t

WR SETUP

t

WR HOLD

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional ,

but do not guara nt ee specific perform ance limits. For g uaranteed specifications and test conditions, see the Electrical Chara cteristics. The gua ranteed specificat ions apply

only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND =AGND=DGND = 0V, unless otherw is e specified.

Note 3: When the input voltage (V

maximum package input current rating limits the number of pins that can simultaneously safely exceed the power supplies with an input current of 25mA to two.

Note 4: The maximum power dissipation must be derated at elevated temperatures and is dictated by T

able power dissipation at any temperature is P

.

is 53°C/W

Note 5: Human body model, 100pF capacitor disch arged through a 1.5 k Ω resistor. Machine model, 200pF capacitor discharged through a 0Ω resistor.

Note 6: See AN-450 “Surface Mounting Methods and Their Effect on Product Reliability” or the section titled “Surface Mount” found in any National Semiconductor Linear

Data Book for other m et hods of soldering su rf ac e mount devices.

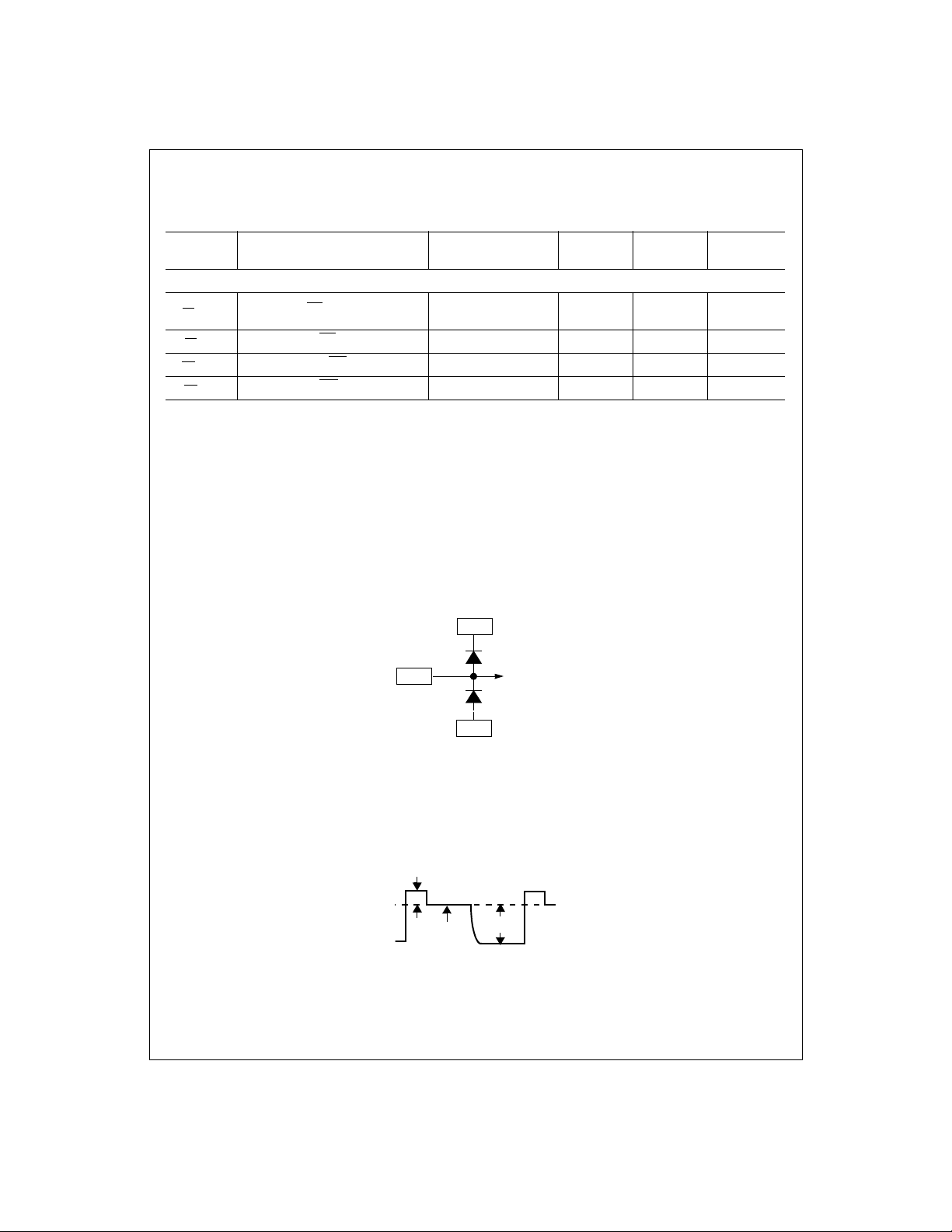

Note 7: Two diodes clamp the OS analog inputs to

impedance of the sensor, prevents damage to th e LM9833 from tra ns ients during power-up.

Data valid to RD rising edge

Data valid after RD rising edge 0 ns (min)

Data valid before WR falling edge 5 ns (min)

Data valid after WR rising edge 10 ns (min)

) at any pin exceeds the power supplies (VIN<GND or VIN>VA or VD), the current at that pin should be limited to 25mA. The 50mA

IN

= (TJmax - TA) / ΘJA. TJmax = 150°C for this device. The typical thermal resistance (ΘJA) of this part when board mounted

D

AGND

and VA as shown below. This input protection, in combination with the external clamp capacitor and the output

V

DRAM

DRAM

=3.3V

VA

=+5.0VDC unless otherwise noted,

DRAM

MIN

MCLK

to T

= f

CRYSTAL IN

MAX

/MCLK DIVIDER, f

; all other limits TA=TJ=25°C. (Notes 8, 9, & 10)

Typical

(Note 9)

max, ΘJA and the ambient temperature, TA. The maximum allow-

J

Limits

(Note 10)

26

35

ADC CLK

= f

MCLK

Units

(Limits)

ns (min)

ns (min)

/8,

OS Input

To Internal

Circuitry

AGND

Note 8: For best performance, it is required that all supply pins be powered from the same power supply with separate bypass capacitors at each supply pin.

Note 9: Typicals are at T

Note 10: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 11: Integral linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line that best fits the actual transfer function o f the ADC.

Note 12: V

a white (full scale) image wi th r es pect to the reference level, V

correctable range of pixel-to-pixel V

LM9833 can correct for using its internal PGA.

Note 13: PGA Gain Error is the maximum difference between the measured gain for any PGA code and the ideal gain calculated by using the formula

Gain

Note 14: DNL, INL, and Pow er Supply Current are s pecified at the 80% Bi as Current Setting (R egister 9). This is the ma ximum recomme nded Bias Curren t setting , and

gives the best analog performance as we ll as lower power consu m pt ion for USB-bus powered applications.

is defined as the CCD OS voltage for the reference pe ri od foll o wing the r eset feedthrough pulse. V

REF

V

G0X

--- -

PGA

V

=25°C, f

J=TA

WHITE

PGA code

-------------- ------------ -+=XG

where .

32

= 48MHz, and repre s ent most likely parametric norm.

CRYSTAL IN

is defined as the peak positive deviation above V

. V

REF

variation is defined as the maximum variation in V

–()

31G0

RFT

CCD Output Signal

V

RFT

V

REF

32

------=

31

V

is defined as the peak CCD pixel output voltage for

WHITE

of the reset feedthrough pulse. The maximum

(due to PRNU, light source intensity variation, optics, etc.) that the

WHITE

WHITE

REF

8 www.national.com

Page 9

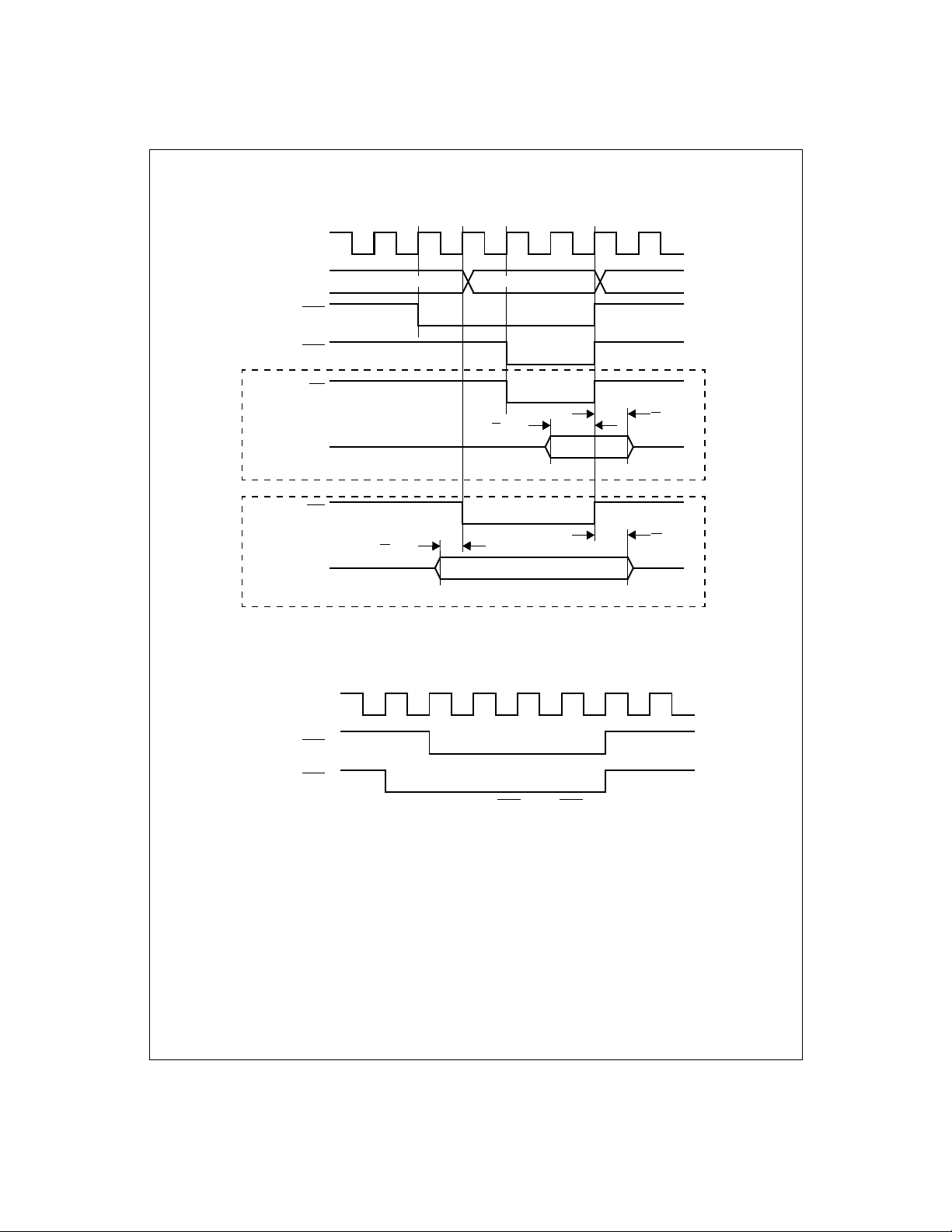

Timi ng Diagra ms

LM9833

48MHz Internal Clock

(t

= 20.83ns)

PERIOD

A0-A9 Row Address

RAS

CAS

RD

Read Operation

WR

Write Operation

01234560

n

Column Address

t

RD SETUP

n

Row Address

t

RD HOLD

n+1

DataD0-D15

t

t

WR SETUP

WR HOLD

DataD0-D15

Figure 1: DRAM Read and Write

48MHz Internal Clock

(t

= 20.83ns)

PERIOD

RAS

CAS

01234560

Figure 2: DRAM Refresh (CAS

before RAS)

9 www.national.com

Page 10

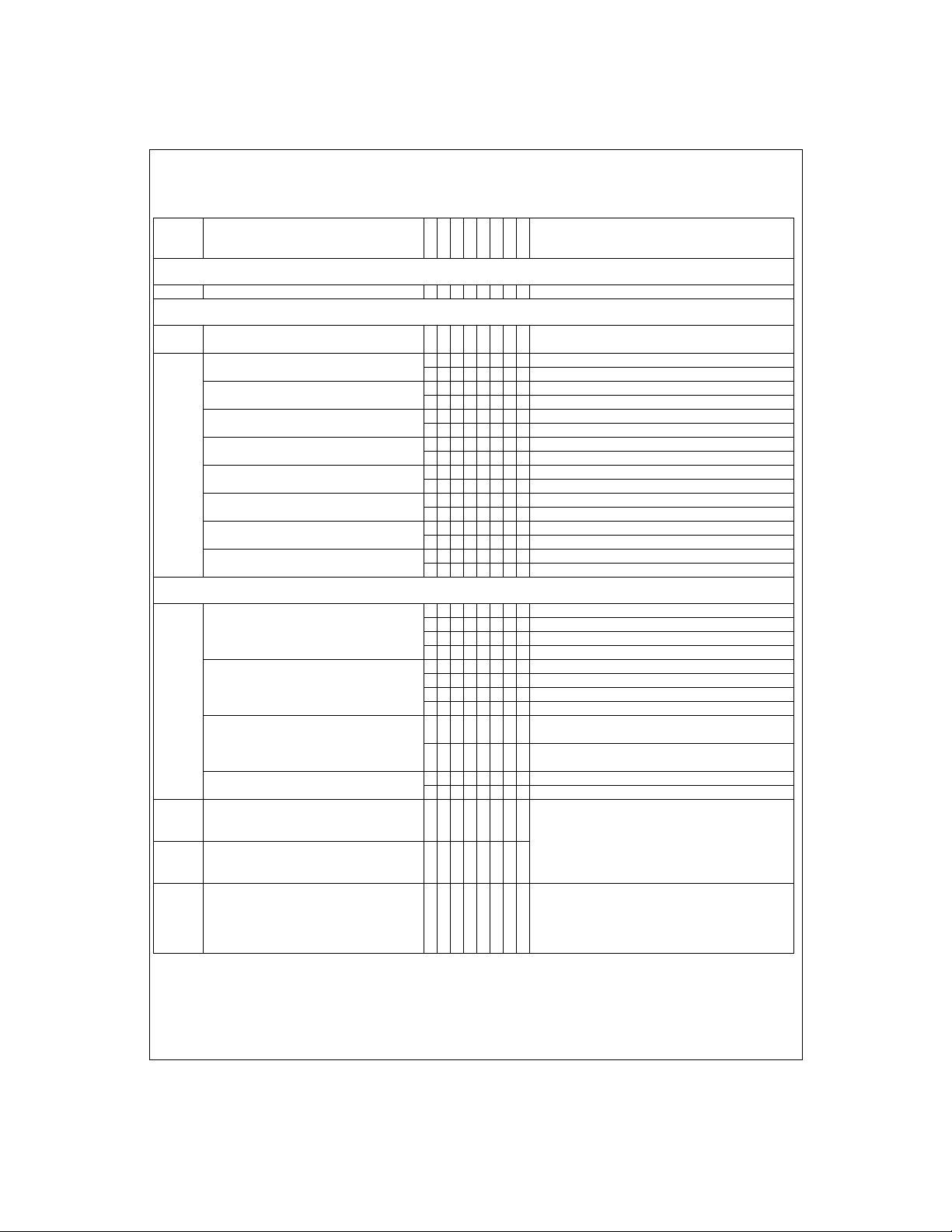

Register Listing

Registers in bold boxes are reset to that value on power-up. All register addresses are in hexadecimal. All other numbers are

LM9833

decimal unless otherwise noted.

Address Function

IMAGE BUFFER (READ ONLY)

00 Pixel (Image) Data nnnnnnnnOne byte of image data.

STATUS REGISTERS (READ ONLY)

01 Image Data Available In Buffer nnnnnnnn

PAPER SENSE 1 State

read clears bit if edge sensitive input.

PAPER SENSE 2 State

read clears bit if edge sensitive input.

MISC I/O 1 State

read clears bit if edge sensitive input.

MISC I/O 2 State

read clears bit if edge sensitive input.

02

MISC I/O 3 State

read clears bit if edge sensitive input.

MISC I/O 4 State

read clears bit if edge sensitive input.

MISC I/O 5 State

read clears bit if edge sensitive input.

MISC I/O 6 State

read clears bit if edge sensitive input.

DATAPORT REGISTERS

DataPort T arget

DataPort T arget Color

03

Pause (Read Only)

This bit indicates whether or not the scanner

is currently paused due to a buffer full

condition.

DRAM Test

04 DataPort Address - MSB

05 DataPort Address - LSB aaaaaaaa

06 DataPort nnnnnnnn

D7D6D5D4D3D2D1D

0False

1True

0False

1True

0False

1True

0False

1True

0Normal State

1 The scanner is currently in the pause/reverse cycle.

0 Normal Operation

1 DRAM Test mode

R

/Waaaaaa

0

n*2 (256k x 16 DRAM) or n*8 (1M x 16 DRAM)

kilobytes of image data is available

0False

1True

0False

1True

0False

1True

0False

1True

0 0 Offset Coefficient Data

0 1 Gain Coefficient Data

1 0 Gamma Lookup Table

11N/A

00 Red

01 Green

10 Blue

11 N/A

Address of location to be read/written to.

a = 0 to 4095 for gamma tables,

0 to 16383 for Offset and Gain Coefficient Data

Addresses greater than these are illegal.

Bit D6 of register 4 indicates whether next operation

will be a Read (D6=1) or a Write (D6=0).

Data to be read from or written to the address of the

currently selected Dataport Target. The DataPort

Address is automatically incremented whenever one

(gamma data) or two (Gain/Offset Data) bytes are

read from or written to this register.

Value

10 www.national.com

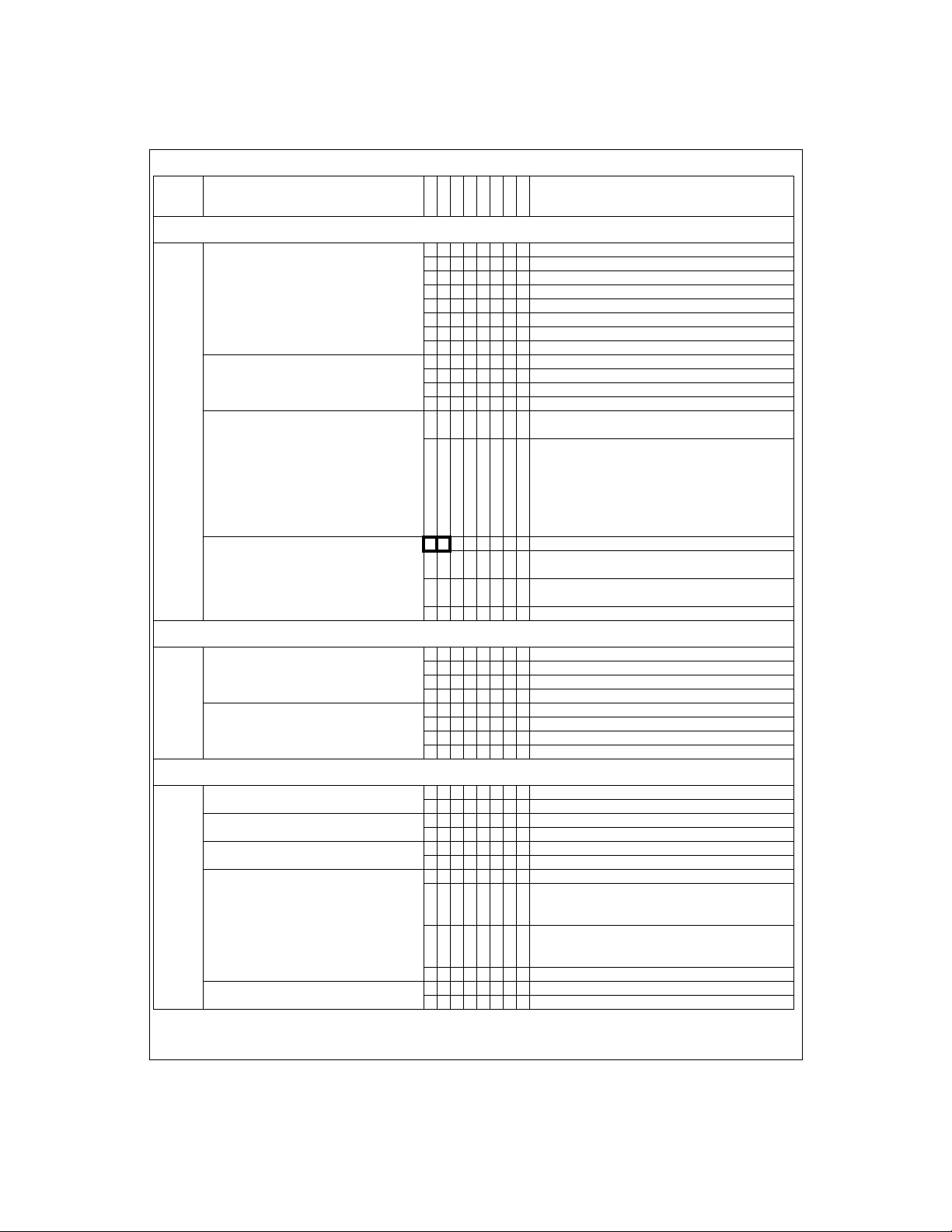

Page 11

MCLK

(Continued)

/8

Register Listing

Address Function

COMMAND REGISTER

Command Register

This register is used to start and end a scan.

It is also used to home the sensor in a

flatbed scanner or eject the image in a

sheetfed scanner. Note: Always make sure

the Command Reg i st er i s in the idle s tat e

(=0) before issuing a new command.

07

Standby

When this bit is set the entire chip enters a

low power state.

Warning: A Standby command will stop

DRAM refresh.

Soft Reset

Write a 1 then a 0 to reset the LM9833’s

state machines.

Warning: A Reset will stop DRAM refresh.

MASTER CLOCK DIVIDER

MCLK Divider

This register sets the master clock frequency

for the entire scanner.

08

f

= 48MHz/MCLK_Divider

MCLK

f

= f

ADC

D7D6D5D4D3D2D1D

0 Normal Operation.

1 Low Power Standby Mode.

0 Normal Operation.

1

000000÷1.0

000001÷1.5

000110÷4

aaaaaa÷ ((aaaaaa/2)+1)

111110÷32.0

111111÷32.5

0

Idle - Stops motor (A, B, A

000

completes current line of data (if scanning).

Note: CCD/CIS clocks continue clocking.

High Speed Forward - Moves motor forward at a

001

speed determined by the Fast Feed Step Size

(registers 48 and 49).

High Speed Reverse - Moves motor backward at a

010

speed determined by the Fast Feed Step Size

(registers 48 and 49).

Start Scan - Resets the LM9833’s data pointers and

011

starts an image scan.

Programmed High Speed Forward - Moves motor

forward at a speed determined by the Fast Feed Step

101

Size (registers 48 and 49) for the number of lines

programmed in registers 4A and 4B.

Programmed High Speed Reverse - Moves motor

backward at a speed determined by the Fast Feed

110

Step Size (registers 48 and 49) for the number of lines

programmed in registers 4A and 4B.

Resets the LM9833. See section 10.2 Soft Reset for

instructions on using this bit.

LM9833

Value

, B = 0),

11 www.national.com

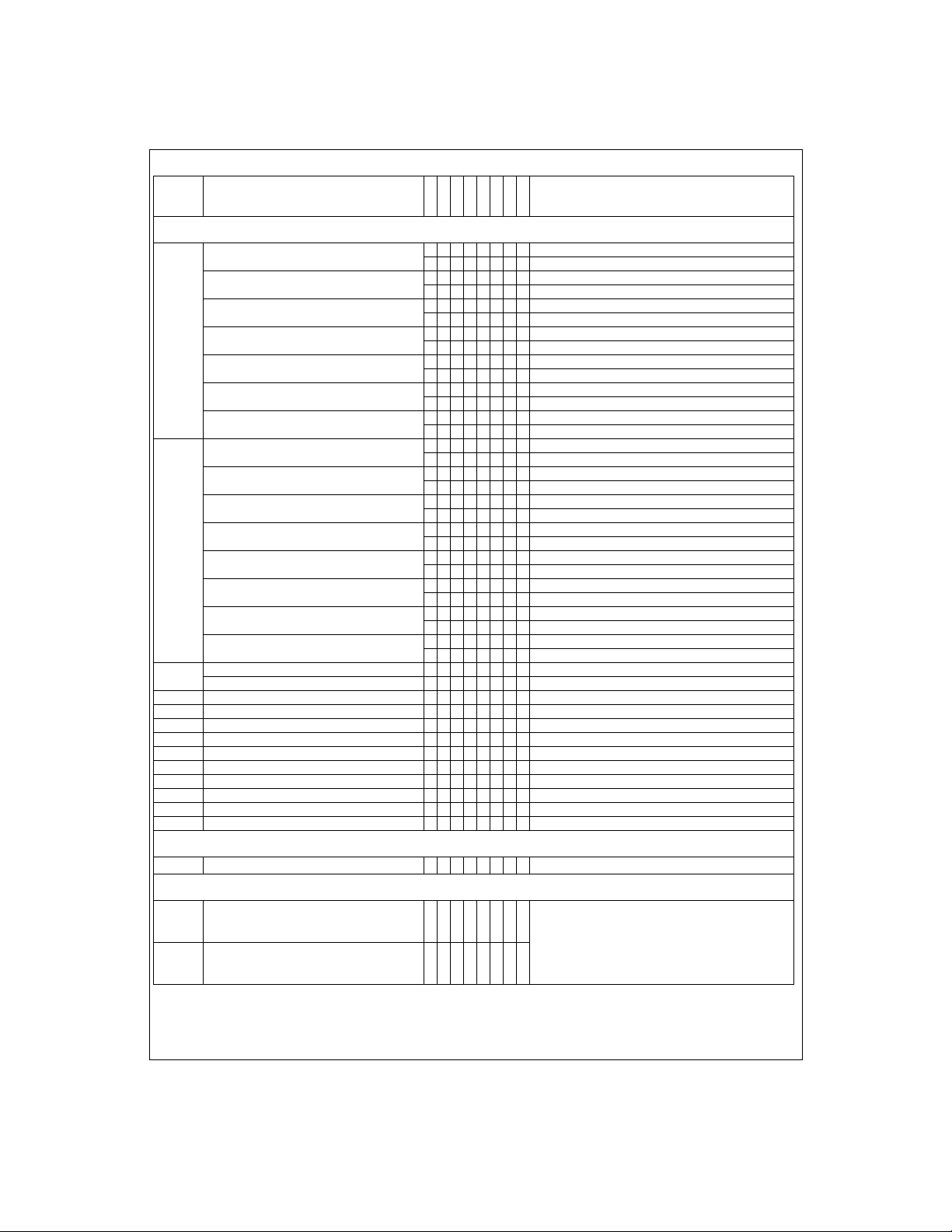

Page 12

Register Listing

Address Function

LM9833

HORIZONTAL RESOLUTION AND DATAMODE SETTINGS

Horizontal DPI Divider

This register determines the horizontal

resolution of the scan.

Scan resolution = Optical resolution divided

by the Horizontal_DPI_Divider.

Pixel Packing

This register determines how many bits in

each byte of data are transmitted to the host

when DataMode = 0

DataMode

09

When DataMode = 0, the pixel data is fully

processed, going through the Offset,

Shading, Horizontal DPI Adjust, Gamma,

and Pixel Packing blocks.

When DataMode = 1, 16 bit da ta is ext racte d

following the Shading Multiplier stage.

Gamma and any other post processing must

be done by th e host.

Analog Bias Current (Percent of Nominal)

The recommended setting is 80% for best

performance. Lower settings will reduce

power consumption further but may degrade

ADC INL and DNL performance.

TURBO AND PREVIEW MODE SETTINGS

Turbo/Preview Mode Select

0A

Turbo/Preview Mode Speed

SENSOR CONFIGURATION

Input Signal Polarity

CDS On/Off

Standard/Even-Odd Sensor

0B

CIS TR1 Timing Mode

Fake Optical Black Pixels

(for Dyna-type CIS sensors)

(Continued)

D7D6D5D4D3D2D1D

0 0 1 bit/pixel (1 bit grayscale/3 bit color)

0 1 2 bits/pixel (2 bit grayscale/6 bit color)

1 0 4 bits/pixel (4 bit grayscale/12 bit color)

1 1 8 bits/pixel (8 bit grayscale/24 bit color)

0

1

0 0 100% (analog supply current = ~81mA)

0 1 80% (analog supply current = ~65mA)

1 0 70% (analog supply current = ~57mA)

1 1 50% (analog supply current = ~41mA)

0 0 Off - use standard CCD Timing

01

10

11 N/A

0 Off: Normal operation

1 On: RS pulse held high for entire Optical Black period

0

000÷1

001÷1.5

010÷2

011÷3

100÷4

101÷6

110÷8

111÷12

1, 2, 4, or 8 bit image data,

as determined by the Pixel Size setting.

16 bit image data - sent in 2 bytes, MSB first:

15 14 13 12 11 10 09 08 - 07 06 05 04 03 02 01 00

0 0 Normal Operation

0 1 Preview Mode (for CCD Sensors)

1 0 Turbo Mode (for CIS Sensors)

11 N/A

00 x2

0 1 x3 (3 Channel Pixel Rate Mode Only)

1 0 x4 (3 Channel Pixel Rate Mode Only)

1 1 x6 (3 Channel Pixel Rate Mode Only)

0 Negative (Most CCD Sensors and Toshiba CIS)

1 Positive (Most CIS Sensors)

0 CDS Off

1 CDS On

0 Standard (1 pixels per Ø period)

1 Even/Odd (2 pixels per Ø period)

CIS TR1 Timing Mode 1:

TR1 pulse = exactly one Ø clock,

starting at rising edge of Ø1

CIS TR1 Timing Mode 2:

TR1 pulse = exactly one Ø clock,

TR1 centered around Ø1 high.

Value

12 www.national.com

Page 13

Register Listing

Address Function

SENSOR CONTROL SETTINGS

Ø1 Polarity

Ø2 Polarity

RS Polarity

0C

CP1 Polarity

CP2 Polarity

TR1 Polarity

TR2 Polarity

Ø1 Active/Off

Ø2 Active/Off

RS Active/Off

CP1 Active/Off

0D

CP2 Active/Off

TR1 Active/Off

TR2 Active/Off

Number of TR Pulses

TR Pulse Duration nnnnn+1 pixel periods (1-16)

0E

TR-Ø1 Guardband Duration n n n n n pixel periods (0-15)

0F Optical Black Clamp Start nnnnn

10 Optical Black Clamp End nnnnn

11 Reset Pulse Start nnnnn

12 Reset Pulse Stop nnnnn

13 CP1 Pulse Start nnnnn

14 CP1 Pulse Stop nnnnn

15 CP2 Pulse Start nnnnn

16 CP2 Pulse Stop nnnnn

17 Reference Sample Position nnnnn

18 Signal Sample Position nnnnn

INTEGRATION TIME ADJUST

19 Integration Time Adjustment Function nnnnnnn

STEPPER PHASE CORRECTION

1A TR to Stepper Phase Correction - MSB nnnnnn

1B TR to Stepper Phase Correction - LSB nnnnnnnn

(Continued)

D7D6D5D4D3D2D1D

0 Positive

1 Negative

0 Positive

1 Negative

0 Positive

1 Negative

0 Positive

1 Negative

0Off

1Active

0Off

1Active

0Off

1Active

0Off

1Active

01 TR Pulse

12 TR Pulses

0

0 Positive

1 Negative

0 Positive

1 Negative

0 Positive

1 Negative

0Off

1Active

0Off

1Active

0Off

1Active

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

t

= n*t

READOUT

First step of scan occurs n pixels (1 - 16383) after first

TR pulse. This register can be used to set the phase

between the TR pulses and the stepper motor pulses.

NOTE: a setting of n = 0 creates the maximum delay

(16384) pixels, which will increase scan time. If this

function is not used, this register should be set to 1.

Value

, n = 1 to 127. n=0 turns off function.

INT

LM9833

13 www.national.com

Page 14

Register Listing

Address Function

LM9833

(Continued)

D7D6D5D4D3D2D1D

0

Value

SENSOR PIXEL CONFIGURATION

1C Optical Black Pixels Start nnnnnnnnn pixels (0 - 255)

1D Optical Black Pixels End nnnnnnnnn pixels (0 - 255)

1E Active Pixels Start - MSB nnnnnnn pixels (0 - 16383)

1F Active Pixels Start - LSB nnnnnnnn

20 Line End - MSB nnnnnn

21 Line End - LSB nnnnnnnn

Set to the same value as register Data Pixels Sta rt.

n pixels (0 - 16383)

This selects the pixel count at which the current line is

ended and the next line begins. This determines the

integration time of one line.

PIXEL DATA RANGE TO PROCESS

22 Data Pixels Start - MSB nnnnnn

n pixels (Active Pixel s Sta rt - 16383)

This selects the start of the range of pixels transmitted

to the PC and determines the pixel location where

23 Data Pixels Start - LSB nnnnnnnn

offset and shading correction begins (pixel 0 in the

DataPort). This value must be >= Active Pixels Start

24 Data Pixels End - MSB nnnnnnn pixels (Data Pixels Start - [Line End - 20])

25 Data Pixels End - LSB nnnnnnnn

This selects the end of the range of pixels transmitted

to the PC. This value must be <= [Line End - 20]

COLOR MODE SETTINGS

0003 Channel Pixel Rate Color

AFE Operation

3 Channel or 1 Channel

0013 Channel Line Rate Color

1001 Channel Grayscale

1011 Channel Color

1 Channel Grayscale Input Source

(1 Channel Color always uses the

26

Blue Channel as the input)

TR

(=TR1) position

RED

(3 Channel Line Rate Mode only)

TR

(=TR2) position

GREEN

(3 Channel Line Rate Mode only)

TR

(=CP2) position

BLUE

(3 Channel Line Rate Mode only)

3 Channel Line Rate TR

(3 Channel Line Rate Mode only)

3 Channel Line Rate TR

(3 Channel Line Rate Mode only)

27

3 Channel Line Rate TR

(3 Channel Line Rate Mode only)

Triple TR output

RED

GREEN

BLUE

drop

drop

drop

0 0 Red Channel

0 1 Green Channel

1 0 Blue Channel

11 N/A

0 1st TR pulse position (inside Ø1 high)

1 2nd TR pulse position (inside Ø1 low)

0 1st TR pulse position (inside Ø1 high)

1 2nd TR pulse position (inside Ø1 low)

0 1st TR pulse position (inside Ø1 high)

1 2nd TR pulse position (inside Ø1 low)

0 0 Do not drop any TR

01Drop 1 TR

10Drop 2 TR

11N/A

RED

RED

0 0 Do not drop any TR

0 1 Drop 1 TR

1 0 Drop 2 TR

11 N/A

GREEN

GREEN

0 0 Do not drop any TR

0 1 Drop 1 TR

1 0 Drop 2 TR

11 N/A

BLUE

BLUE

pulses

RED

pulse (double integration time)

pulses (triple integration time)

pulses

GREEN

pulse (double integration time)

pulses (triple integration time)

pulses

BLUE

pulse (double integration time)

pulses (triple integration time)

0 Normal operation

1 Outputs single TR pulse on TR1, TR2, and CP2 pins

RESERVED

28 Reserved 00000000Write 00 to this register

14 www.national.com

Page 15

Register Listing

Address Function

(Continued)

D7D6D5D4D3D2D1D

ILLUMINATION SETTINGS

Illumination Mode

Controls t he f u nc t io n of th e 3 L A MP o utp ut s :

LAMP

, LAMPG, and LAMP

R

B

Mode 0 is the Off/Reset state.

Mode 1 is typically used for CCFL lamps.

29

Mode 2 is for color scanning with tri-color

LEDs.

Mode 3 is for grayscale scanning with tricolor LEDs.

LAMP

for INT IME ADJ

B

2A LAMP

2C LAMP

2D LAMP

2E LAMP

2F LAMP

30 LAMP

31 LAMP

32 LAMP

33 LAMP

34 LAMP

35 LAMP

36 LAMP

37 LAMP

PWM - MSB (Illumination Mode 1) nnnnLAMPG output is a PWM pulse stream. Duty cycle is

G

PWM - LSB (Illumination Mode 1) nnnnnnnn

G

On - MSB nnnnnnn pixels (1 - 16384)

R

On - LSB nnnnnnnn

R

Off - MSB nnnnnnn pixels (1 - 16384)

R

Off - LSB nnnnnnnn

R

On - MSB nnnnnnn pixels (1 - 16384)

G

On - LSB nnnnnnnn

G

Off - MSB nnnnnnn pixels (1 - 16384)

G

Off - LSB nnnnnnnn

G

On - MSB nnnnnnn pixels (1 - 16384)

B

On - LSB nnnnnnnn

B

Off - MSB nnnnnnn pixels (1 - 16384)

B

Off - LSB nnnnnnnn

B

STATIC OFFSET AND GAIN SETTINGS FOR ANALOG FRONT END

38 Static Offset (Red)

39 Static Offset (Green)

3A Static Offset (Blue)

3B Static Gain (Red)

3C Static Gain (Green)

3D Static Gain (Blue)

0nnnnnOffset = +n*9.3mV, n = 0 to 31

1nnnnnOffset = -n*9.3mV, n = 0 to 31

0nnnnnOffset = +n*9.3mV, n = 0 to 31

1nnnnnOffset = -n*9.3mV, n = 0 to 31

0nnnnnOffset = +n*9.3mV, n = 0 to 31

1nnnnnOffset = -n*9.3mV, n = 0 to 31

0nnnnnGain = 0.93 + 0.067*n (V/V), n = 0 to 31

1nnnnnGain = 3(0.93 + 0.067*n) (V/V), n = 0 to 31

0nnnnnGain = 0.93 + 0.067*n (V/V), n = 0 to 31

1nnnnnGain = 3(0.93 + 0.067*n) (V/V), n = 0 to 31

0nnnnnGain = 0.93 + 0.067*n (V/V), n = 0 to 31

1nnnnnGain = 3(0.93 + 0.067*n) (V/V), n = 0 to 31

0

= LAMPG = LAMPB = 0V

LAMP

00

R

(Power-On/Reset Default)

Illumination Mode 1 - LAMP

every line, with their on and off points controlled by

the Pixel Counter settings. LAMP

continuous PWM pulse stream. (Figure 20)

01

LAMP

and/or LAMPB may be set to stay on or off at

R

all times by setting the LAMP Off or LAMP On settings

Value

and LAMPB turn on

R

G

(registers 2C-37) grea ter than the Line End value

(registers 20 and 21).

Illumination Mode 2 - LAMP

sequentially at the line rate, with their on and off

10

points controlled by Pixel Counter settings. (Figure

, LAMPG, LAMPB turn on

R

21)

Illumination Mode 3 - LAMP

11

every line, with their on and off points controlled by

, LAMPG, LAMPB turn on

R

the Pixel Counter settings. (Figures 22 and 23)

0LAMP

1

operates normally

B

LAMP

output is enabled during short integration

B

time, low during long integration time.

n/4095. Frequency = 48Mhz/4096 = 11.7kHz2B LAMP

This selects the pixel count at which the LAMP

output goes high (if programmed)

This selects the pixel count at which the LAMP

output goes low (if programmed)

This selects the pixel count at which the LAMP

output goes high (if programmed)

This selects the pixel count at which the LAMP

output goes low (if programmed)

This selects the pixel count at which the LAMP

output goes high (if programmed)

This selects the pixel count at which the LAMP

output goes low (if programmed)

Output is

LM9833

R

R

G

G

B

B

15 www.national.com

Page 16

Register Listing

Address Function

LM9833

DIGITAL PIXEL RATE OFFSET AND GAIN SETTINGS

3E Fixed Offset Coefficient - MSB nnnnnnnn

3F Fixed Offset Coefficient - LSB nnnnnnnn

40 Fixed Multiplier Coefficient - MSB nnnnnnnn

41 Fixed Multiplier Coefficient - LSB nnnnnnnn

DIGITAL PIXEL RATE OFFSET AND GAIN/DRAM SETTINGS

Shading Multiplier

Multiplier Coefficient Source

42

Offset Coefficient Source

Reserved 1 0 Set to 10

DRAM Size

(Continued)

D7D6D5D4D3D2D1D

0 256k x 16

11M x 16

0

Fixed Offset to use for calibration

Fixed Gain to use for calibration

0 Gain = [Multiplier Coefficent]/16384

1 Bypass Multiplier

0 Configuration Register 40 and 41 (Fixed)

1 External DRAM

0 Configuration Register 3E an d 3F (Fixed)

1 External DRAM

Value

16 www.national.com

Page 17

Register Listing

Address Function

STEPPER MOTOR CONTROL SETTINGS

n (Line Skipping)

43

Part of the “n out of m” function, consisting of

registers 43, 44, and 54 (bits 3-7).

m (Line Skipping)

44

Part of the “n out of m” function, consisting of

registers 43, 44, and 54 (bits 3-7).

Full/Microstepping

Current Sensing Phases

= 0 for fullstepping

= 1 for micros tepping

Stepper Motor Phase A Polarity

45

Stepper Motor Phase B Polarity

A, B, A

Swap A/A

(Reverses m otor directi on)

Fullstep During FastFeed at Start of Scan

46 Scanning Step Size - MSB nnnnnnnnThe step size of one microstep while scanning, in

48 Fast Feed Step Size - MSB nnnnnnThe step size of one microstep while fast feeding, in

4A Fullsteps to Skip at Start of Scan - MSB nnnnnnnWhen scan starts, paper is fed forward n full steps (0 -

4C Step Counter - MSB nnnnnnCounts n (0-16383) full steps. See register 58, bit 5

4E Pause scanning, stop/reverse motor nnnnnnnn

4F Resume scanning, start motor nnnnnnnn

50 Full steps to reverse when buffer is full nnnnnnnnn (0-255) full steps (0 = do not reverse)

Acceleration Profile (stopped) n n n (0,1, 2, or 8) f ull st ep t ime un i ts pa us e whi le s top pe d

Acceleration Profile (25%) n n n (0,1, 2, or 8) full steps at 25% speed

51

Acceleration Profile (50%) n n n (0,1, 2, or 8) full steps at 50% speed

Default Phase Difference - High Byte n n 18 bit word used to calculate when motor resumes

52 Default Phase Differen ce - Mid B yte nnnnnnnn

53 Default Phase Difference - Low Byte nnnnnnnn

Lines to Process After Pa us e/

Lines to Discard after Resum e

Line Skipping Phase

Part of the “n out of m” function, consisting of

54

registers 43, 44, and 54 (bits 3-7).

Line Skipping Color Phase Delay

Part of the “n out of m” function, consisting of

registers 43, 44, and 54 (bits 3-7).

(Continued)

, and B stepper motor status

with B/B

D7D6D5D4D3D2D1D

tttttttt

mmmmmmmm

0 A, B, A

1A, B, A

0 Default polarity

1 Reverse Polarity

0 Traditional Operation

1 Fullstep during fastfeed at start of scan

n n n n n lines, n = 0-15

0

n lines saved in DRAM for every m lines (register 44)

scanned, function bypassed if register value = 0.

n (lines saved per m lines scanned) = 256 - t

t = 256 - n

If t = 0 then function is bypassed.

n lines (register 43) saved in DRAM for every m lines

scanned. m = 1 to 255.

If m = 0 then function is bypassed.

0 Full Step Mode

1 Microstepping Mode

1 Phase - No microstepping, just kickstart/stop

0

functions

1 2 Phases - necessary for microstepping

0

Positive (A/B/A

Negative (A/B/A

WARNING: When idle, this setting leaves the motor

1

energized for unipolar motors, and will destroy bipolar

0

1

0 Red sensor data arrives before Green sensor

1 Blue sensor data arrives before Green sensor

motor drivers. Keep this bit set to a 0.

Positive (A/B/A

Negative (A/B/A

WARNING: When idle, this setting leaves the motor

energized for unipolar motors, and will destroy bipolar

motor drivers. Keep this bit set to a 0.

, and B output pins in Tri-State

, and B output pins active

units of pixel periods (minimum 2)47 Scanning Step Size - LSB nnnnnnnn

units of pixel periods (minimum 2)49 Fast Feed Step Size - LSB nnnnnnnn

32767) at highest speed. For “zooming” in flatbeds4B Fullsteps to Skip at Start of Scan - LSB nnnnnnnn

for more information.4D Step Counter - LSB nnnnnnnn

Pause scan when buffer is n*2 (16 x 256k) or

n*8 (16x1M) kbytes full

Resume scan when buffer is n*2 (16 x 256k) or

n*8 (16x1M) kbytes full

after reversing and stopping. 1 < n < 262143. 2 bits in

register 51 are the most significant bits of 18 bit word.

n (0-7) lines. This only applies if the motor doesn’t

nnn

reverse (reverse steps = 0)

Value

/B Output high = winding energized)

/B output low = winding energized)

/B Output high = winding energized)

/B output low = winding energized)

LM9833

17 www.national.com

Page 18

Register Listing

Address Function

LM9833

Kickstart steps (fullstepping mode) nnnMotor gets maximum current for first n (0-7) full steps

55

Hold Current Timeout nnnnn Full step time units (1-31) (do not set to 0)

56 Stepper Motor PWM Frequency nnnnnnnn

57 Stepper Motor PWM Set Duty Cycle nnnnnn= minimum of n/64 (default = 0)

PAPER SENSE SETTINGS

PAPER SENSE 1: Polarity

PAPER SENSE 1: Level/Edge sensitive

PAPER SENSE 1: Stop Scan, High Speed

Forward, and H igh Speed Reverse

Use this input for the home sensor in flatbed

scanners.

PAPER SENSE 2: Polarity

58

PAPER SENSE 2: Level/Edge sensitive

PAPER SENS E 2: Stop Scan and High

Speed Forward

(Continued)

D7D6D5D4D3D2D1D

0

1

0

1

0 A low input on PAPER SENSE 2 is True

1 A high input on PAPER SENSE 2 is True

0

1

0

1

0

=CRYST AL OUT/(256*n) (0 < n < 256)

=CRYSTAL OUT/(256*256) (n = 0)

0 A low input on PAPER SENSE 1 is True

1 A high input on PAPER SENSE 1 is True

Level sensitive: PAPER SENSE 1 State bit (in Status

Register) is set to a 1 if PAPER SENSE 1 is currently

True.

Edge sensitive: PAPER SENSE 1 State bit (in Status

Register) is set to a 1 if PAPER SENSE 1 has been

True since the last time the Status Register was read.

Transitions on PAPER SENSE 1 will not clear the

command register.

A False-to-True transition on P APER SENSE 1 will

clear the Command Register and stop the scan .

Level sensitive: PAPER SENSE 2 State bit (in Status

Register) is set to a 1 if PAPER SENSE 2 is currently

True.

Edge sensitive: PAPER SENSE 2 State bit (in Status

Register) is set to a 1 if PAPER SENSE 2 has been

True since the last time the Status Register was read.

The scan will automatically stop after scanning for the

number of fullsteps specified in the Step Counter

(registers 4C and 4D). (The fullsteps moved during

the “FastFeed At Start of scan period are not

counted.) If the value in the Step Counter is 0, the

scan can only be stopped by writing a 0 to register 07.

A False-to-True transition on P APER SENSE 2 will

stop a scan or a High Speed Forward command after

the number of fullsteps specified in the Step Counter

(registers 4C and 4D). It will not stop a High Speed

Reverse, and therefore should not be used as a home

position s ensor input.

Value

18 www.national.com

Page 19

Register Listing

Address Function

MISC I/O PIN SETTINGS

MISC I/O 1: Input or Output

MISC I/O 1: Polarity

(if configured as an input)

MISC I/O 1: Level/Edge sensitive

(if configured as an input)

MISC I/O 1: Output State

(if configured as an output)

Power On/USB Suspend Default: Input

59

MISC I/O 2: Input or Output

MISC I/O 2: Polarity

(if configured as an input)

MISC I/O 2: Level/Edge sensitive

(if configured as an input)

MISC I/O 2: Output State

(if configured as an output)

Power On/USB Suspend Default: Input

MISC I/O 3: Input or Output

MISC I/O 3: Polarity

(if configured as an input)

MISC I/O 3: Level/Edge sensitive

(if configured as an input)

MISC I/O 3: Output State

(if configured as an output)

Power On/USB Suspend Default: Input

5A

(NEW)

MISC I/O 4: Input or Output

MISC I/O 4: Polarity

(if configured as an input)

MISC I/O 4: Level/Edge sensitive

(if configured as an input)

MISC I/O 4: Output State

(if configured as an output)

Power On/USB Suspend Default: Output,

Logic High

(Continued)

D7D6D5D4D3D2D1D

0 The MISC I/O 2 pin is configured as an input.

1 The MISC I/O 2 pin is configured as an output.

0 A low input on MISC I/O 2 is True

1 A high input on MISC I/O 2 is True

0

1

0

1

0 The MISC I/O 4 pin is configured as an input.

1 The MISC I/O 4 pin is configured as an output.

0 A low input on MISC I/O 4 is True

1 A high input on MISC I/O 4 is True

0

1

0

1

0

0 The MISC I/O 1 pin is configured as an input.

1 The MISC I/O 1 pin is configured as an output.

0 A low input on MISC I/O 1 is True

1 A high input on MISC I/O 1 is True

Level sensitive: MISC I/O 1 State bit (in Status

0

Register) is set to a 1 if MISC I/O 1 is currently True.

Edge sensitive: MISC I/O 1 State bit (in Status

1

Register) is set to a 1 if MISC I/O 1 has been True

since the last time the Status Register was read.

0

1

0

1

The output of the MISC I/O 1 pin will be a logic low

(0V).

The output of the MISC I/O 1 pin will be a logic high

(5V).

Level sensitive: MISC I/O 2 State bit (in Status

Register) is set to a 1 if MISC I/O 2 is currently True.

Edge sensitive: MISC I/O 2 State bit (in Status

Register) is set to a 1 if MISC I/O 2 has been True

since the last time the Status Register was read.

The output of the MISC I/O 2 pin will be a logic low

(0V).

The output of the MISC I/O 2 pin will be a logic high

(5V).

0 The MISC I/O 3 pin is configured as an input.

1 The MISC I/O 3 pin is configured as an output.

0 A low input on MISC I/O 3 is True

1 A high input on MISC I/O 3 is True

Level sensitive: MISC I/O 3 State bit (in Status

0

Register) is set to a 1 if MISC I/O 3 is currently True.

Edge sensitive: MISC I/O 3 State bit (in Status

1

Register) is set to a 1 if MISC I/O 3 has been True

since the last time the Status Register was read.

The output of the MISC I/O 3 pin will be a logic low

(0V).

The output of the MISC I/O 3 pin will be a logic high

(5V).

Level sensitive: MISC I/O 4 State bit (in Status

Register) is set to a 1 if MISC I/O 4 is currently True.

Edge sensitive: MISC I/O 4 State bit (in Status

Register) is set to a 1 if MISC I/O 4 has been True

since the last time the Status Register was read.

The output of the MISC I/O 4 pin will be a logic low

(0V).

The output of the MISC I/O 4 pin will be a logic high

(5V).

Value

LM9833

19 www.national.com

Page 20

Register Listing

Address Function

LM9833

MISC I/O 5: Input or Output

MISC I/O 5: Polarity

(if configured as an input)

MISC I/O 5: Level/Edge sensitive

(if configured as an input)

MISC I/O 5: Output State

(if configured as an output)

Power On/USB Suspend Default: Output,

5B

Logic High

(NEW)

MISC I/O 6: Input or Output

MISC I/O 6: Polarity

(if configured as an input)

MISC I/O 6: Level/Edge sensitive

(if configured as an input)

MISC I/O 6: Output State

(if configured as an output)

Power On/USB Suspend Default: Output,

Logic Low

TEST MODE SETTINGS

5C ADC Output Code - MSB nnnnnnnnUsed to force the input to the HDPI Divider to a known

ADC Test Mode

Pixel Processing Input Select

5E

16 bit Counter Increment Select

(16 bit counter starts at 0, increments every

datapixel)

MCLK edge for AFE (Set this bit to 0)

CDS Signal

5F-68 Reserved 00000000Write 00 to these registers

69 Version Number 100

6A-7F Reserved 00000000Write 00 to these registers

(Continued)

D7D6D5D4D3D2D1D

0 The MISC I/O 6 pin is configured as an input.

1 The MISC I/O 6 pin is configured as an output.

0 A low input on MISC I/O 6 is True

1 A high input on MISC I/O 6 is True

0

1

0

1

0 0 Increments by 1

0 1 Increments by 4

1 0 Increments by 16

11 N/A

0 Rising

1 Falling

0 Normal Operation

1 CDS signal is output on LAMP

0

0 The MISC I/O 5 pin is configured as an input.

1 The MISC I/O 5 pin is configured as an output.

0 A low input on MISC I/O 5 is True

1 A high input on MISC I/O 5 is True

Level sensitive: MISC I/O 5 State bit (in Status

0

Register) is set to a 1 if MISC I/O 5 is currently True.

Edge sensitive: MISC I/O 5 State bit (in Status

1

Register) is set to a 1 if MISC I/O 5 has been True

since the last time the Status Register was read.

0

1

0 0 Normal Operation - ADC Output

0 1 Registers 5C and 5D

1 0 16 bit counter, reset at the start of every scan

1 1 16 bit counter, reset at the start of every line

The output of the MISC I/O 5 pin will be a logic low

(0V).

The output of the MISC I/O 5 pin will be a logic high

(5V).

Level sensitive: MISC I/O 6 State bit (in Status

Register) is set to a 1 if MISC I/O 6 is currently True.

Edge sensitive: MISC I/O 6 State bit (in Status

Register) is set to a 1 if MISC I/O 6 has been True

since the last time the Status Register was read.

The output of the MISC I/O 6 pin will be a logic low

(0V).

The output of the MISC I/O 6 pin will be a logic high

(5V).

value for digital tests5D ADC Output Code - LSB nnnnnnnn

0 0 Normal Operation

0 1 Bypass AFE, Normal ADC Operation

Bypass AFE, bypass ADC digital corre ction,

10

output uncorrected ADC MSB

Bypass AFE, bypass ADC digital corre ction,

11

output uncorrected ADC LSB

100 = LM9832 or LM9833

(011 = LM9831, 010 = LM9830)

Value

B

pin

20 www.national.com

Page 21

Applications Information

1.0 OVERVIEW

The LM9833 is a USB, 1200d pi, 16 bit (48 bit colo r) scanner- ona-chip. The LM9833 is an improved, 16 bit version of the

LM9831, providing all o f the L M9 831 ’s functionality while impr oving performance and adding several new features. See 12.0

CHANGES FROM THE LM9831 for a complete list of additions

and enhancements.

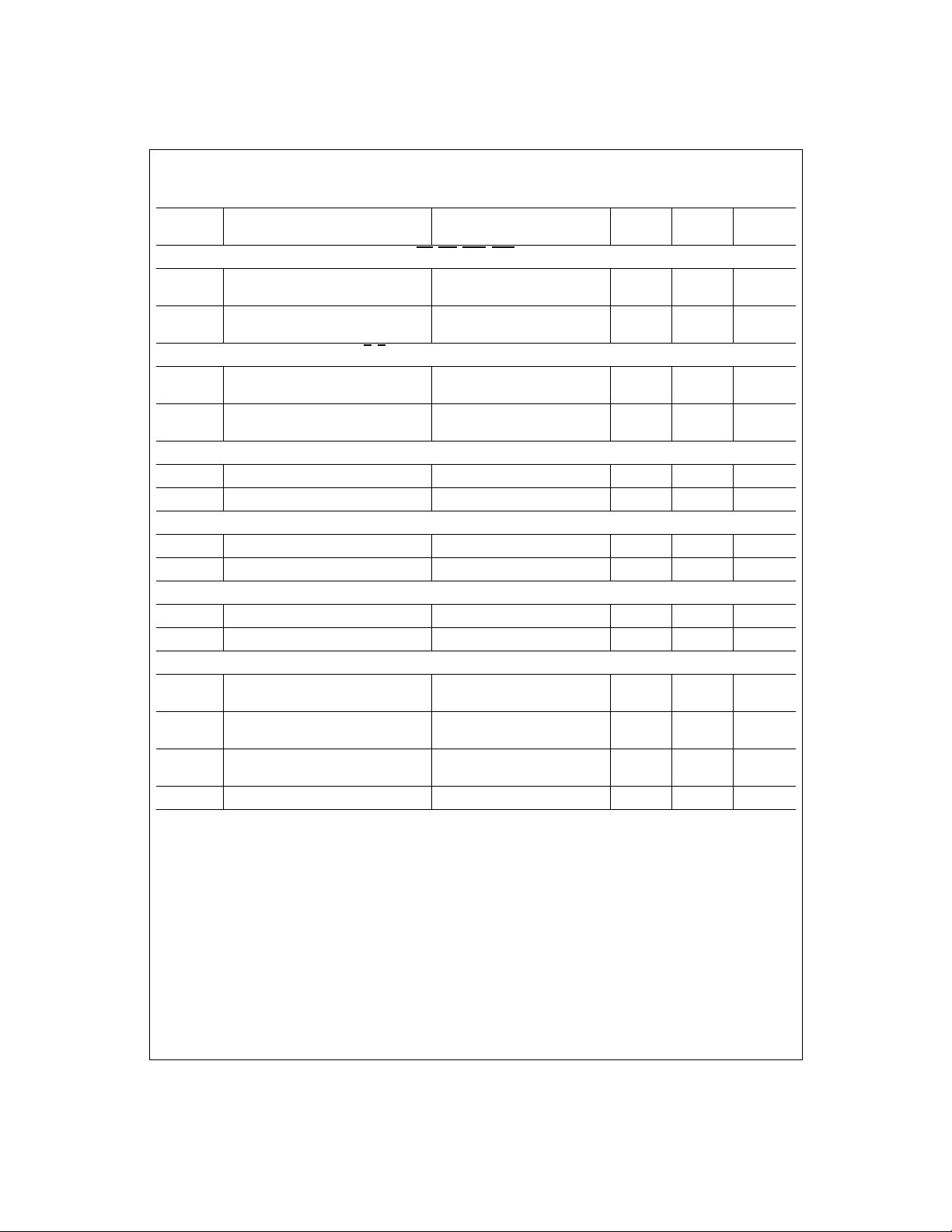

2.0 ANALOG SIGNAL PROCESSING

One channel of the LM9833’s analog front end is shown in Figure

3. The gain through each cha nnel can be set between 0.93V/V

and 9.0V/V using regi sters 3B, 3C , and 3D. Th e offset DAC p rovides up to ±278mV of offset correction using registers 38, 39,

and 3A. The offset DAC an d ga i n s tage s sh ould be adjusted during coarse calibration so that the input signal is a maximum of

1.9Vp-p at the ADC input.

3.0 DIGITA L SIGNAL PROCESSING

3.1 ADC

The digital pixel data comes from a 6MHz 16 bit pipelined ADC.

3.2 Pixel Processing Block

The Pixel Processing stage is used to digit ally re duce t he optica l

resolution of the sensor. The optical resolution can be reduced by

a factor of 1, 1.5, 2, 3, 4, 6 , 8, o r 1 2. For a 12 00 d pi (o ptica l) system, this would prod uce res olutions o f 1200 , 800, 6 00, 40 0, 300 ,

200, 150, and 100. A 600 dpi (optical) system would be cap able

of 600, 400, 300, 200, 150, 100, 75, and 50 dpi. (Resolution in the

vertical direction is controlled by the stepper motor speed.)

Horizontal resolution reduction is accomplished by averaging

adjacent pixels. Averaging produces better image quality and

reduces aliasing versus the traditional technique of simply discarding pixels to r educe resolutio n. For example , to get 100 dp i

from a 300dpi optical sensor, you would average 3 300dpi pixels:

p

++

pixel

100dpi

n-2pn-1pn

-------------------- ----------------------- -=

3

The number of pi xe ls co ming o ut of the Pixel Processing block is

equal to the integer portion of the number of pixels going in to the

Pixel Processing block divided by the “Divide By” setting, from the

table shown in Figure 4.

Pixels

IN

OUT

=

INT

------------------- ------

Divide By

Pixels

This equation also applies to the divide by 1.5 function.

Divide

By

DPI

(1200

DPI

system)

DPI

(800

DPI

system)

DPI

(600

DPI

system)

DPI

(300

DPI

system)

1 1200 800 600 300

1.5 800 533 400 200

2 600 400 300 150

3 400 267 200 100

4 300 200 150 75

6 200 133 100 50

8 150 100 75 37.5

12 100 67 50 25

Figure 4: Decrea sing Horizo nta l Resolutio n

If there are not enough pixe ls at the end of a line to fo rm a complete pixel, the last pixel will be eliminated . For example, if a line

is 35 pixels wide and the Horizontal DPI setting i s set to divide by

6, then the output of the Pixel Processing block will be 5 pixels

(the integer portion of 35/6). The last 5 pixels will be discarded,

since 6 pixels would be required to form a new pixel in this mode.

The output of this stage is sent to the Pixel Rate Offset Correction

Block.

3.3 Pixel Rate Offset Correction Block

Offset correction words for every pixel of the CCD are stored in

LM9833

Σ

+

V

DAC

OS1)GB

PGA

0.93V/V t o

3V/V

G

PGA

+ V

DAC

+ V

+

+

V

Σ

OS3

OS2)GPGA

+ V

16 Bit

ADC

OS3

D

OUT

)C

Gain Boost

1V/V or

3V/V

+

+

V

IN

G

Σ

+

V

OS1

B

D

OUT

= (((VIN + V

+

Σ

+

V

OS2

Offset

DAC

simplified, with all offsets = 0, this is:

D

= (VINGB + V

OUT

DAC)GPGA

C

C is a constant that combines the gain error thr ough th e AFE, ref erence voltage var ianc e, and ana log voltage

to digital code conversion into one constant. Ideally, C = 32768 codes/V.

Manufacturing tolerances widen the range of C. See Electrical Specifications.

Figure 3: Analog Front End (AFE) Model

21 www.national.com

Page 22

Applications Information

(Continued)

the external DRAM and accessed at the pixel rate . A digital subtractor subtracts the 16 bit offset word (corresponding to that

LM9833

pixel’ s offset error) from each pixel.

The subtractor saturates at 0, i.e. if the coefficient to be sub-

tracted is greater than the ADC output code, the result is an output of 0.

The offset words stored in DRAM are typically calculated by

scanning a black calibration strip at 16 bits, and storing the

results in the DRAM using the DataPort.

The offset correction equation is:

Pixel

PixelINcoefficient

=

OUT

–

3.6 Pixel Packing/Thresholding Block

Some scans require only one bit per pixel (“line art” mode), others

may need only 2 or 4 bits/ pixel. To increase scanning speed for

lower pixel depths, the LM9833 packs the desir ed MSBs of multiple pixels together into 1 16 bit word, increasing the transmission

speed to the host by a factor of 2, 4, 8, or 16. Figure 6 shows how

the pixels are packed together f or 8, 4, 2, an d 1 bit pixel depths.

In Figure 6, “b” indicates the bit position (b7 = the most significant

and b0 = the least significant bit) of the original 8 bit pixel data,

and p

indicates the original pixel sequence, i.e p0, p1, p2, p3...

n

If there are no t enough unpacked pixe ls at the end of a line to

complete the packed wor d for t ransmiss ion, tha t final wor d is not

sent. For exampl e, doing an 8 bit pixel rate scan with a HDPI

divider of 1 and an odd number of pixels will truncate the blue

component of the last pixel.

3.4 Pixel Rate Gain Correction Block

This is a digital multiplier that multiplies the outp ut word from the

subtractor by a 16 bit di gital correcti on coefficient corres ponding

to that pixel’s gain err or. The coefficients are stored in the external RAM and accessed at the pixel rate.

The multiplier saturate s at 65535, i.e. if the result of the m ultiplication is greater than 65535, the multiplier output is 65535.

The gain equation is:

coefficient

----------------- --------- -

Pixel

OUT

=

Pixel

⋅

IN

16384

Note that a c o ef f i ci en t of 0 r ep r es e nt s a g ai n of 0. O n t he LM98 3 0

and previous parts, a coe fficient of 0 re presented a gain o f 1. To

achieve a gain of 1, the coefficient should be set to 16384.

3.5 Gamma Correction Tables

There are 3 gamma loo kup tables for R, G, and B. The inp ut to

the table is the 12 MSBs ( most si gnifican t bit s) of th e 16 b it pixe l

data coming from t he previous st age (3.4 P ixel Rate Gain Cor-

rection Block). The output is the 8 bit gamma corrected pixel

data. The tables consume 12k words (4K bytes x 16 bits, only the

8 LSBs of each word is used) of the external DRAM. Each

gamma table (red, gre en, an d blu e) can b e loa ded with a ny a rbitrary user-defined transfer curve.

255

Pixel

Depth

bit15bit14bit13bit12bit11bit10bit9bit

8b7 p

4b7 p0b6 p0b5 p0b4 p0b7 p1b6 p1b5 p1b4 p

b6 p0b5 p0b4 p0b3 p0b2 p0b1 p0b0 p

0

2b7 p0b6 p0b7 p1b6 p1b7 p2b6 p2b7 p3b6 p

1b7 p0b7 p1b7 p2b7 p3b7 p4b7 p5b7 p6b7 p

bit 7 bit 6 bit 5 b it 4 bit 3 bit 2 bit 1 bit 0

8b7 p

4b7 p2b6 p2b5 p2b4 p2b7 p3b6 p3b5 p3b4 p

b6 p1b5 p1b4 p1b3 p1b2 p1b1 p1b0 p

1

2b7 p4b6 p4b7 p5b6 p5b7 p6b6 p6b7 p7b6 p

1b7 p8b7 p9b7 p10b7 p11b7 p12b7 p13b7 p14b7 p

8

0

1

3

7

1

3

7

15

Figure 6: Packing Multiple Pixels Into One Word

The gamma table in 3.5 Gamma Correct ion Tables allows the

user to set the threshol d of each transi tion for various l ine art or

reduced pixel depth modes.

3.7 16 Bit Output Mode

The LM9833 als o sup p or t s a 16 b i t o ut m o de . Th i s c a n be us ed t o

get very accurate data for calibration o r to scan a 16 gr ay/48 bit

color image. This mode i s set through regist er 9, bit 5. In the 16

bit output mode, the gamma and pixel packing stages are

bypassed, and the 16 bit da ta from the ADC is st ored in DRAM,

formatted as shown in Figure 7.

MSB 151413121110 9 8

b15 b14 b13 b12 b11 b10 b9 b8

LSB76543210

b7 b6 b5 b4 b3 b2 b1 b0

Figure 7: 16 Bit Output Mode Data Format

8 Bit Pixel Out

0

12MSBs of 16 bit Output

0 4095

Figure 5: Gamma Table

The gamma tables are loa ded thr ough th e da taport ( see 6.1 The

DataPort: Reading and Writing to Gamma, O ffset, and Gain

Memory). The DataPort selects which color (Red, Green or Blue)

gamma table will be read from or written to.

The memory reserved for the gamma table is used to store image

data in the 16 bit mode. After scanning in 16 bit mode, the

gamma table mus t be reloaded f or operation in 8, 4, 2, or 1 bi t

mode.

3.8 Line Buffer

The line buffer uses the external DR AM as a FIF O line buffer to

store the pixel data (wh ich is generated at a fi xed rate, synchronous to the CCD clocks) and send it back to the PC at an as ynchronous, unpredictable, and non-constant rate.

The LM9833 supports 2 sizes of DRAM, 2 56k x 16bit and 1M x

16bit. 216kbytes (108kwords) of the capacity of the DRAM is con-

22 www.national.com

Page 23

Applications Information

sumed by the offset and shading coefficients an d the gamma

tables. That leaves 296k bytes of m emory av ailabl e for line bu ffer

when using a 256k x 16 bit DRAM, or 1832kbytes of memor y

when using a 1M x 16 bit DRAM.

The line buffer is tightly co upled to th e stepper mo tor (4.0 Step-

per Motor Control ler ), and is res ponsibl e for stoppi ng the motor

before the buffer overflows and starting the motor again as the

buffer nears empty.

If the scanner is generating pixe l data faster than the PC can

acquire it, the line buffer will start to fill up. As the buffer nears

100% of its capacity, the scan must be paused before it starts

acquiring a line which will overflow the buffer. This Pause Threshold limit (register 4 E) is program mable in 2 kbyte (256k x 16 bi t

DRAM) or 8kbyte (1M x 16 bit DRAM) increme nts be twee n 0 and

255.

To maximize scanner perfo rmance and min imize pausing d ue to

buffer full conditions, the pause threshold should be set using this

formula:

Pause Threshold (kB) = Available_Memory - (Line_Length + 1)

where Available_Memory = 296kbytes (256k x 16b DRAM) or

1832kbytes (1M x 16 bit D RAM),

Line_Length = (Bytes/Line)/1024

INT

Bytes/Line 2 INT

Where C = 1 for “1 Channel Grayscale”, 3 for all other modes,

Data_Pixels = Data Pixels End (regi sters 24, 25) - Data Pixels

Start (registers 22, 23)

HDPI_Divider = Horizontal DPI divider = 1, 1.5, 2, 3, 4, 6, 8, or 12

B = Bits per Pixel = 16 (16 bit mode), 8, 4, 2, or 1

Register 4E value = Pause Thre shold (kB)/2 (256k x 16 DRA M)

or Pause Threshold (kB)/8 (1M x 16 DRAM)

When the Pause Thresho ld is reached the b uffer sends a com-

mand to the stepper motor controller to stop scanning. The

remainder of the line being processed will continue being processed and be sent to the buffer. If the Lines To Process After

Pause Scan Signal register (regis ter 54) is great er than 0, then

room for these additional lines nee ds to be added into the Pause

Threshold value calculation.

Note that the scanner software on th e host PC mu st set a Pause

Threshold value low eno ugh to ensure tha t any data that come s

after a pause request (the rest of the curre nt line and any sub sequent lines if register 54 bits 0-2 are greater than 0) will fit into the

DRAM buffer. If the Pause Threshold is set too high, the Line

Buffer may overflow, creating discontinuities in the scanned

image.

After a pause, the buffer will continue to transmit data to the PC

until it hits the Resume Threshold limit (register 4F), which is also

programmable in 2 kbyt e (256k x 16 bi t DRAM) or 8kb yte (1M x

16 bit DRAM) increments between 0 and 255. When the Resume

Threshold is reached, the Line Buffer sends the motor controller a

command to resume.

4.0 Stepper Motor Controller

The stepper motor controller sends a series of pulses to the step-

=

⋅

------------------- ------------------------------ ---------------------- -

(Continued)

Data Pixels

------------------- ---------------- -

HDPI_Divider

CB⋅⋅

16

per motor to move the pap er past the sensor (sheetfed) or the

sensor past the paper (flat bed). The speed at which the paper

moves relative to the sensor, combined with the i ntegration t ime

of the image sensor, determines the effective vertica l resolution

(Lines Per Inch, or LPI).

The stepper motor i s mo ved for w ard s a nd backwards by two signals, A and B, 90° out of ph ase with each other. The phase for

the forward direction is set in Configuration Register 45.

The A and B signals are e ither square waves (in F ull Step Mo de,

Figure 8), or a staircase approximation of a sine wave (in

Microstep mode, Figures 10 and 11).

A

A

1 full step = 4

microsteps

B

B

Figure 8: Stepper Motor Waveform - Full Stepping

The LM9833 always counts stepper motor steps in units of

microsteps. A full step is equal to four microsteps. Even when the

LM9833 is in Full Step Mode, it is counting in microsteps, and will

increment the stepper motor (generating a full step) every fo ur

microsteps.

The microstep Step Size is defined in units of time. These units of

time are pixel periods , as defined in the hor izontal pixel coun ter.

In the 3 Channel Pixel Rate input mode, the pixel period is the

f

/3 (= f

ADC

modes, the pixel period is eq ual to f

Size is stored in the Scanning S tep Size confi guration register

as a 14 bit value. During normal operation, the stepper motor is

advanced 1 microstep every Step Size pixel periods. The LPI can

be calculated as follows:

Where FSPI = the number of full steps required to move the

image one inch, pixels/l ine is the nu mber of pixel pe riods it takes

to scan one horizo ntal line (e quivalent to the value stor ed in the

Line End registers), StepSize is the number of pixel periods/microstep, and X = 3 for line rate and 1 for pixel rate modes.

Whenever the stepper motor has been moving and then comes to

a stop, the LM9833 waits for the time specified in the Hold Current Timeout register a nd th en de -asserts the A, B, A

puts to cut power t o the motor. When the stepper m otor is not

scanning or fast-feeding (Command = 00), A, B, A

asserted in all stepper modes.

There are two modes of stepper motor operation: fullstepping and

microstepping.

4.1 Full Step Mode

In Full Step Mode the out put is a pulse str eam, as shown i n Figure 8. The amplitude of the pul ses is controlled by the outp ut of

/24). In the 3 Channe l Line Rate and 1 channe l

MCLK

LPI 4FSPI

----------------- ------------------ -=

pixels/line X

ADC

StepSize

(= f

⋅

/8). The Step

MCLK

, and B are de-

, and B out-

LM9833

23 www.national.com

Page 24

Applications Information

the 2 bit DAC, shown in Figure 9.

(Continued)

LM9833

Scan Mode DAC Voltage

Starting from

a dead stop

Scanning 0.347V

Stopped

4.2 Microstep Mode

Microstepping is a techni que of driving the stepper motor with a

staircase approximation of a si ne wave, as shown in Figure 10 .

This technique maximizes the torque of a given motor, resulting in

a higher maximum speed. In additi on, it increases the reso lution

of the stepper motor. If a stepper motor moves 3.6° per full step,

microstepping can crea te positions inside the 3.6°: 1.8°, 0.9° , or

0.45°, for example. Th is increases the maximu m vertical resolution of the scan ner. Microstepping also results in q uieter motor

movement.

A

A

B

0.484V for number of steps specified

in Kickstart Steps register (0-7). If

register is 0 there is no Kickstart

current-movement begins at 0.347V.

0.133V for number of steps specified

in Hold Current Timeout register (1 -

31), 0V after time out.

Figure 9: Full Step Current Control

1 microstep

noise generated by the driver transistor turning on.

DAC A

A

A

DAC B

B

B

Figure 11: Stepper Motor Waveform - LM9833 Signals

Figure 12 shows the LM98 33’s DAC voltages. The peak current

through the stepper motor winding will be 0.484V/R

table index is increment ed every microstep (StepSize pixel periods).

Table

Index

000N/A

1100.195V

2100.347V

3100.448V

4100.484V

-0 0 0 N/A

-1 0 1 0.195V

-2 0 1 0.347V

-3 0 1 0.448V

-4 0 1 0.484V

Figure 12: Microstepping Current Control

A (B) A

(B)

DAC

Voltage

SENSE

. The

B

Figure 10: Bipolar Microstepping Waveform

The amplitude of the microstepped sine wave is controlled by the

output of the stepper m otor DAC (Figure 11). The current in the