Page 1

N

LM9831 42-Bit Color, 1200dpi USB Image Sc anner

General Description

The LM9831 is a complete USB image scanner system on a single IC. The LM9831 provides all the functions (image sensor

control, ill umination control, a nalog front end, pi xel processing

function image data buffer/DRAM controller, microstepping

motor cont rolle r, and USB i nterfac e) ne ces sary to create a high

performance color scanner. The LM9831 scans images in 42 bit

color/14 bit gray, and has output data formats for 24 bit color/8

bit gray. The LM9831 supports sensors with pixel counts of up to

16384 pixels x 3 colors (1200 dpi x 13.6 inches).

The LM9831’s low operating and suspend mode supply currents

allow design of USB bus-powered scanners. The only additional

active components required are an external 4Mbit or 16Mbit

DRAM for data buffering and power tra nsistors for the stepper

motor.

Applications

• Color Flatbed Document Scanners

• Color Sheetfed Document Scanners

Features

• 14 bit ADC digitizes at up to 6Mpixels/s (2M RGB pixels/sec).

• Digital Pixel Processing pr ovides 1200, 800, 600, 400, 300,

200, 150, and 100dpi horizontal resolution from a 1200dpi

sensor and 600, 400, 300, 200, 150, 100, 75, and 50dpi

horizontal resolution from a 600dpi sensor.

• Provides 50-2400dpi vertical resolution in 1 dpi increments.

• Pixel rate error correction for gain (shading) and offset errors.

• Supports 4 or 16Mbit external DRAMs.

• Multiple CCD clocking rates allows matching of CCD clock to

scan resolution and pixel depth for maximum scan speed.

• Stepper motor con trol tightly coupl ed with image data buffer

management to maximize data transfer efficiency.

• PWM stepper motor current c ontrol allows microst epping for

the price of fullstepping.

• USB interface for Plug and Play oper ation on USB- equipped

computers.

• Serial EEPROM option for custom Vendor and Product IDs.

• Support for USB bus-powered operation.

• Pixel depths o f 1, 2, or 4 bits are pac k ed into b yte s f or fas ter

scans of line art and low pixel depth images.

• Supports 3 channel CCDs and 1 channel CIS sensors.

• 3 (R, G, and B) 12-bit, user-programmable gamma correction

tables.

• Compatible with a wide range of color linear CCDs and

Contact Image Sensors (CIS).

• Operates with 48MHz external crystal.

• Internal bandgap voltage reference.

• 100 pin TQFP package

Key Specifications

• Analog to Digital Converter Resolution 14 Bits

• Maximum Pixel Conversion Rate 6MHz

• A4 Color 150dpi scan time <10 seconds

• A4 Color 300dpi scan time <40 seconds

• A4 Color 600dpi scan time <160 seconds

• Supply Voltage

- LM9831 +4.75V to +5.25V

- LM9831 DRAM I/O +2.85 to +5.25V

• Typical Operating Current Consumption 134mA

LM9831 42-Bit Color 1200dpi USB Image Scanner

October 1999

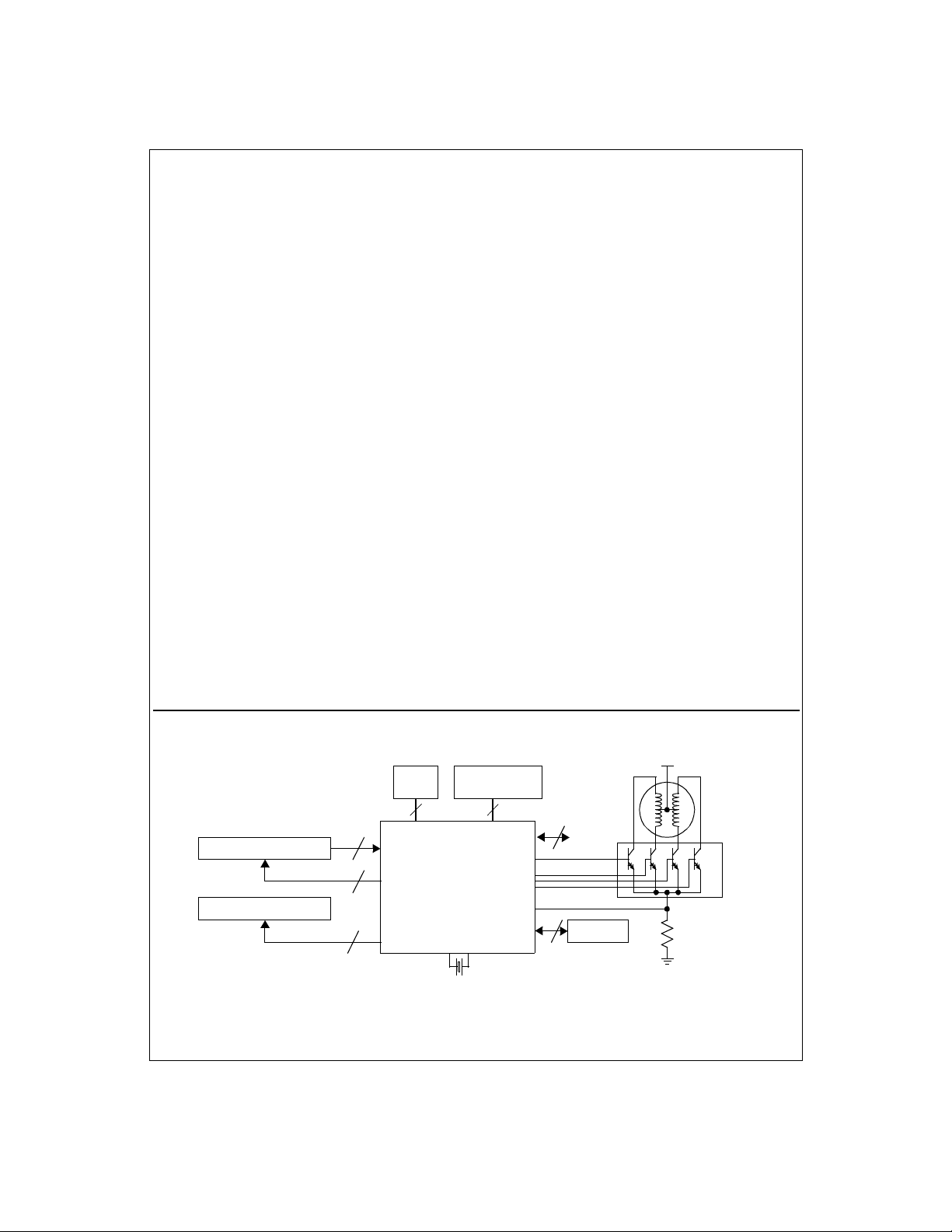

LM9831 Scanner System Block Diagram

USB

Port

2

2-6

1-3

1-3

LM9831CCVJD

CCD/CIS

Illumination

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

©1999 National Semiconductor Corporation

Optional Serial

EEPROM

2

8MISC

I/O

30

DRAM

48MHz Crystal

1 www.national.com

+24V

Stepper

Motor

Power

Transistors

Page 2

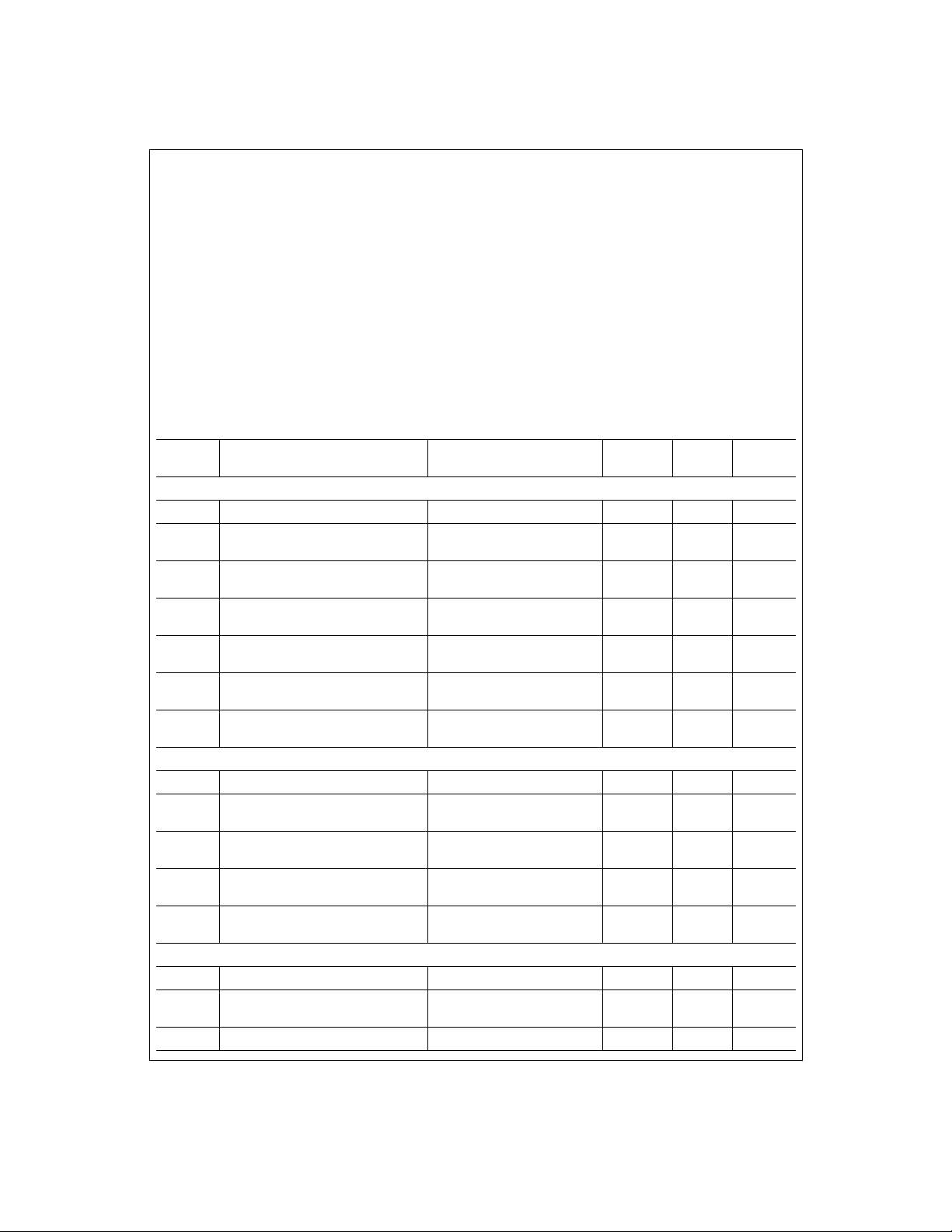

Absolute Maximum Ratings (Notes 1 & 2) Operating Ratings (Notes 1 & 2)

Positive Supply Voltage (V+=VA=VD=V

With Respect to GND=AGND=DGND 6.5V

Voltage On Any Input or Output Pin -0.3V to V

Input Current at any pin (Note 3) ±25mA

Package Input Current (Note 3) ±50mA

Package Dissipation at T

ESD Susceptibility (Note 5)

= 25°C (Note 4)

A

Human Body Model 2000 V

Machine Model 250 V

Soldering Information

Infrared, 10 seconds (Note 6) 235°C

Storage Temperature -65°C to +150°

DRAM

)

+

+0.3V

Operating Temperature Range T

LM9831VJD 0°C≤TA≤+70°C

Supply Voltage +4.75V to +5.25V

V

A

V

Supply Voltage +4.75V to +5.25V

D

Supply Voltage +2.85V ≤ V

V

DRAM

|V

| ≤ 100mV

A-VD

Input Voltage Range -0.05V to V

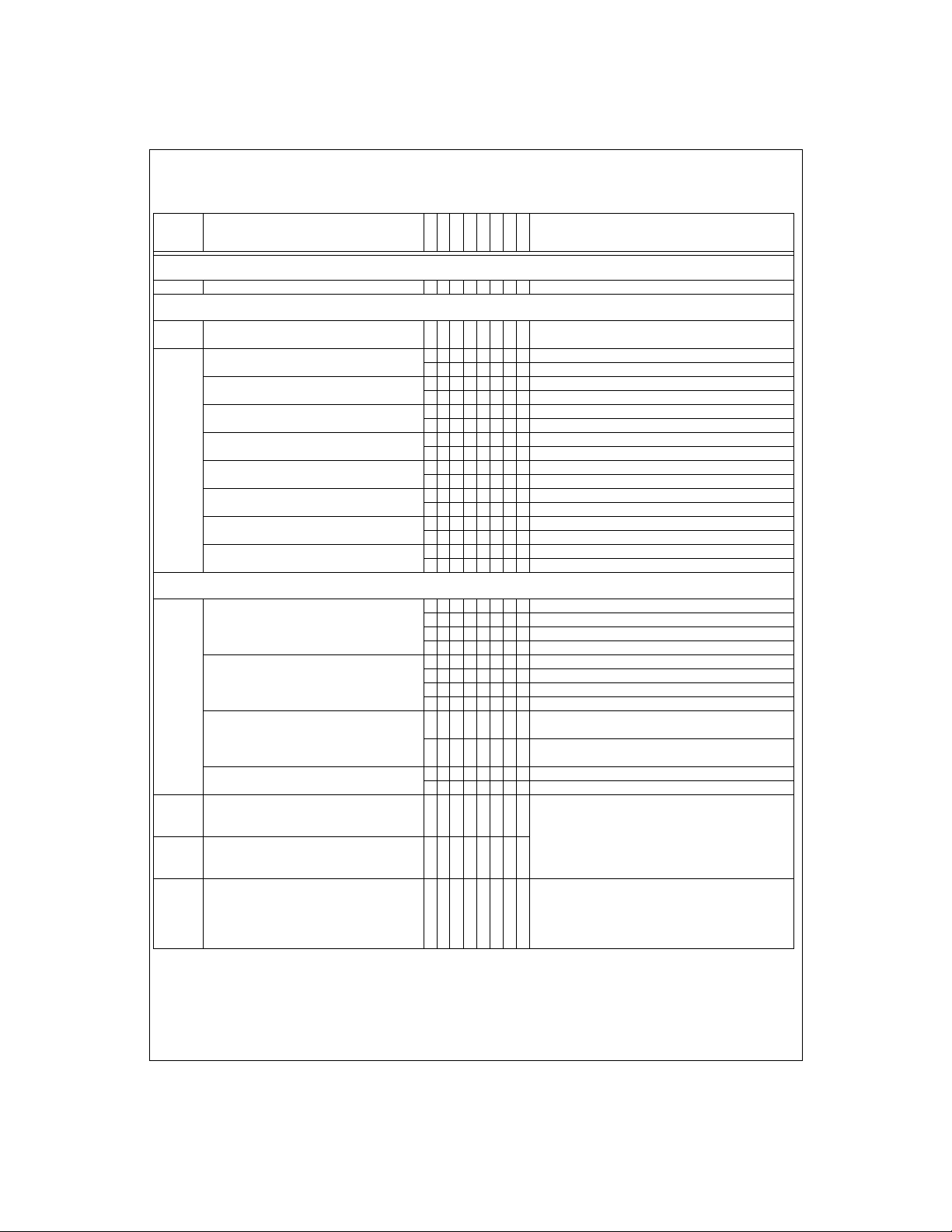

Electrical Characteristics

The following specifications apply for AGND=DGND=0V, VA=VD=V

f

CRYSTAL IN

= 48MHz.

Boldface limits apply for T

A=TJ=TMIN

to T

Symbol Parameter Conditions

Full Channel Characteristics (in units of 12 bit LSBs unless otherwise noted)

Resolution with No Missing Codes 14 12 bits (min)

DNL Differential Non-Linearity V

INL Integral Non-Linearity Error (Note 11) V

Analog Channel Gain Constant

C

(ADC Codes/V), referred to 14 bits.

V

V

V

Pre-Boost Analog Channel Offset Error 26

OS1

Pre-PGA Analog Channel Offset Error -30

OS2

Post-PGA Analog Channel Offset Error -26

OS3

DRAM

DRAM

Includes voltage reference

variation, gain setting = 1

Coarse Color Balance PGA Characteristics (Configuration Registers 3B, 3C, and 3D)

Monotonicity

G

(Minimum PGA Gain) PGA Setting = 0 0.93

0

G

(Maximum PGA Gain) PGA Setting = 31 3.00

31

x3 Boost Gain

x3 Boost Setting On

(bit B5 of Gain Register is set)

Gain Error at any gain (Note 13) 0.3

Static Offset DAC Characteristics (Configuration Registers 38, 39, and 3A)

Monotonicity

Offset DAC LSB size PGA gain = 1 9

Offset DAC Adjustment Range PGA gain = 1 ±278

=+5.0VDC,

DRAM

; all other limits TA=TJ=25°C. (Notes 8, 9, & 10)

MAX

Typical

(Note 9)

=3.3V

=3.3V

-0.47

+0.95

-3.2

+2.6

8192

2.94

DRAM

Limits

(Note 10)

-1

+2.4

-12.6

+7.3

7412

9300

-34

+76

-80

+31

-75

+26

5

0.90

0.96

2.95

3.05

2.85

3.04

-0.6

+0.9

6

6

12

±256

MIN≤TA≤TMAX

≤ VD+100mV

+

+ 0.05V

Units

(Limits)

LSB (min)

LSB (max)

LSB (min)

LSB (max)

LSB (min)

LSB (max)

mV (min)

mV (max)

mV (min)

mV (max)

mV (min)

mV (max)

bits (min)

V/V (min)

V/V (max)

V/V (min)

V/V (max)

V/V (min)

V/V (max)

% (min)

% (max)

bits (min)

mV (min)

mV (max)

mV (min)

2 www.national.com

Page 3

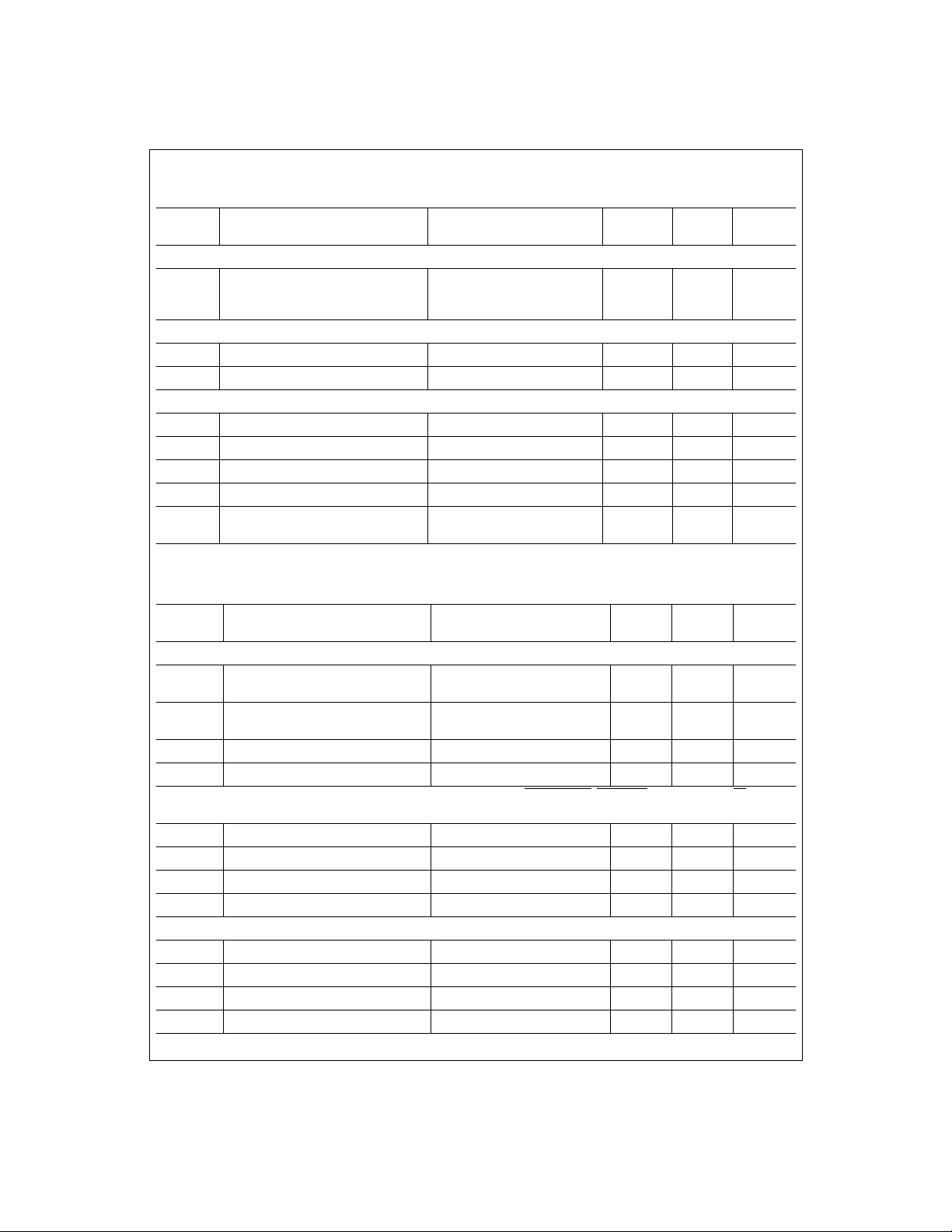

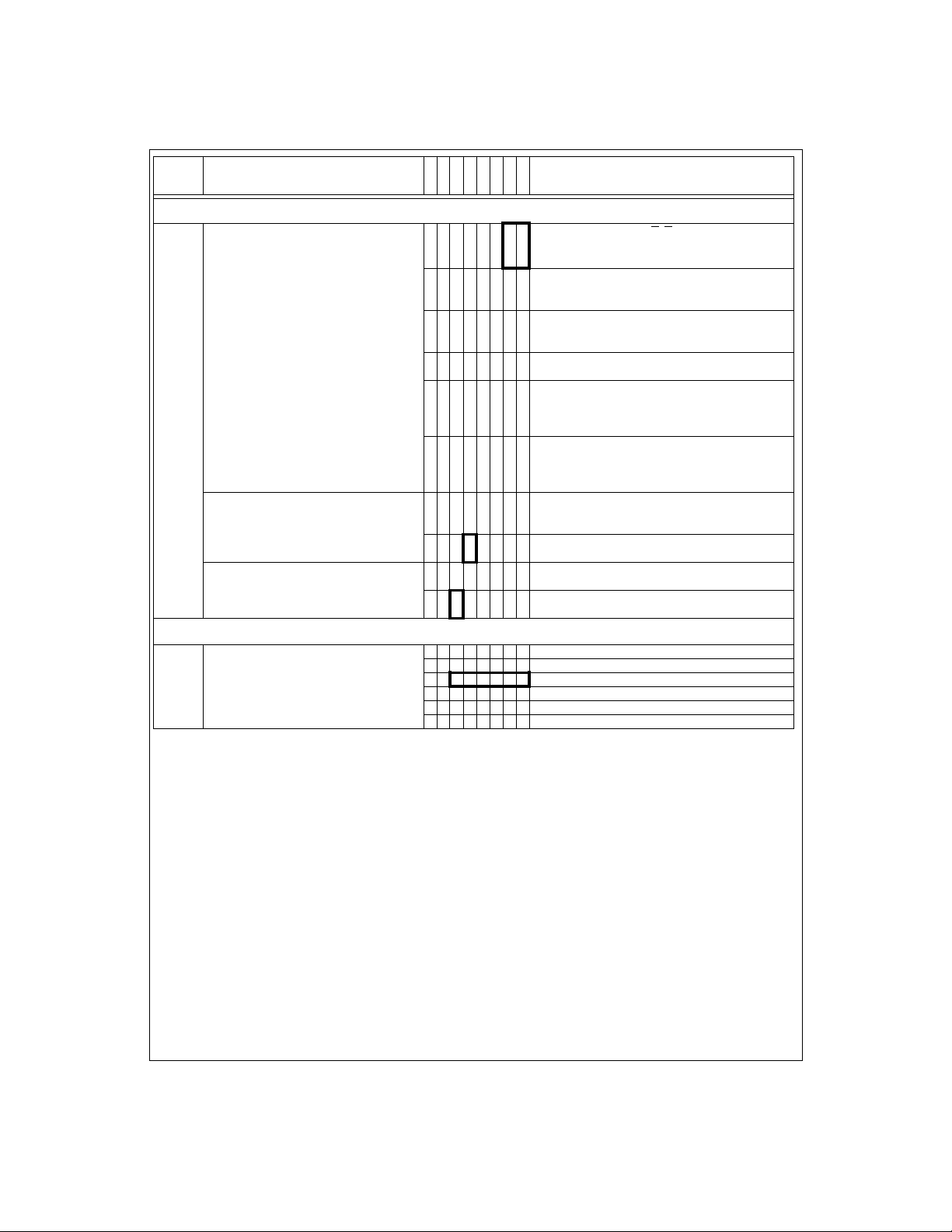

Electrical Characteristics

The following specifications apply for AGND=DGND=0V, V

f

CRYSTAL IN

= 48MHz.

Boldface limits apply for T

(Continued)

A=TJ=TMIN

A=VD=VDRAM

to T

=+5.0VDC,

; all other limits TA=TJ=25°C. (Notes 8, 9, & 10)

MAX

Symbol Parameter Conditions

CCD/CIS Source Requirements for Full Specified Accuracy and Dynamic Range (Note 12)

V

CCDPEAK

Sensor’s Maximum Output Signal

Amplitude before LM9831 Analog Front

End Saturation

Gain = 0.933

Gain = 3. 0

Gain = 9.0

Analog Input C haracteristics

Average OS

OS

R

, OSG, OSB Input Current CDS Enabled, OS = 3.5V

R

, OSG, OSB Input Current CDS Disabled, OS = 3.5V

DC

DC

Internal Voltage Reference Characteristics

V

BANDGAP

V

REF LO

V

REF MID

V

REF HI

V

REGULA-

TOR

Voltage Reference Output Voltage 1.23 V

Negative Reference Output Voltage

Midpoint Reference Output Voltage

Positive Reference Output Voltage

USB I/O Voltage Regulator

DC and Logic Electrical Characteristics

The following specifications apply for AGND=DGND=0V, VA=VD=V

f

CRYSTAL IN

= 48MHz.

Boldface limits apply for T

A=TJ=TMIN

to T

Symbol Parameter Conditions

Digital Input Characteristics for D0-D15 (DRAM Interface)

V

V

V

C

Logical “1” Input Voltage

IN(1)

Logical “0” Input Voltage

IN(0)

I

Input Leakage Current ±0.1 µA

IN

Input Capacitance 5 pF

IN

V

V

V

DRAM

DRAM

DRAM

DRAM

Digital Input Characteristics for PAPER SENSE 1-2, MISC I/O 1-6, SDA, BUS POWER

CMODE

V

V

C

Logical “1” Input Voltage VD=5.25V

IN(1)

Logical “0” Input Voltage VD=4.75V

IN(0)

I

Input Leakage Current ±0.1 µA

IN

Input Capacitance 5 pF

IN

Digital Input Characteristics for D+, D-

V

V

C

Logical “1” Input Voltage VD=5.25V

IN(1)

Logical “0” Input Voltage VD=4.75V

IN(0)

I

Input Leakage Current ±0.1 µA

IN

Input Capacitance 5 pF

IN

=+5.0VDC unless otherwise noted,

DRAM

; all other limits TA=TJ=25°C. (Notes 8, 9, & 10)

MAX

=5.25V

=3.6V

=4.75V

=2.85V

, CRY STAL/EXT CLOCK, 24/48, RESET,

Typical

(Note 9)

Limits

(Note 10)

1.9

0.6

0.19

±3 nA

±26

-1.0 V

V

REF MID

/2.0 V

V

A

+1.0 V

V

REF MID

3.4

Typica l

(Note 9)

±30

Limits

(Note 10)

2.0

2.0

0.8

0.8

2.0

0.8

2.0

0.8

Units

(Limits)

V

V

V

µA (max)

V

Units

(Limits)

V (min)

V (min)

V (max)

V (max)

V (min)

V (max)

V (min)

V (max)

3 www.national.com

Page 4

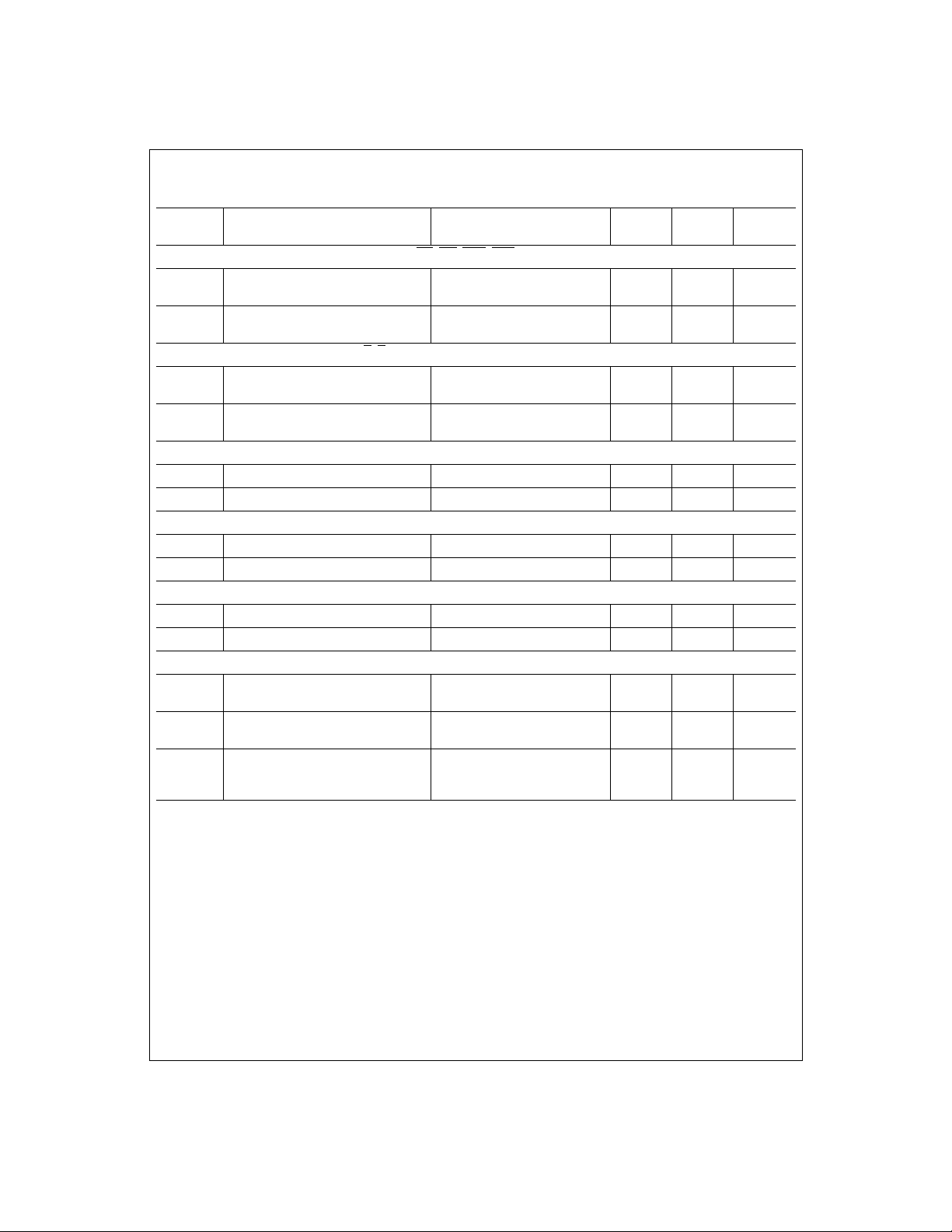

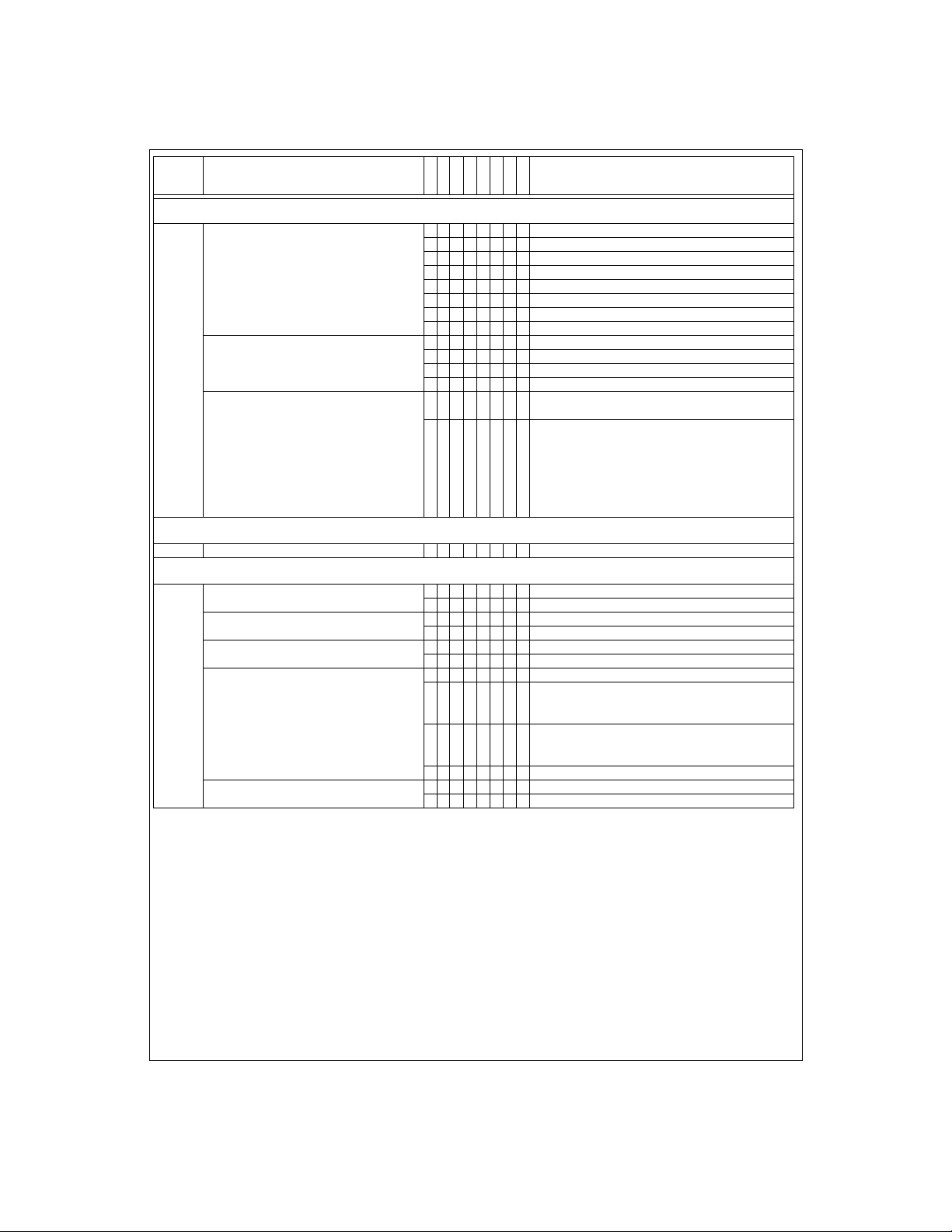

DC and Logic Electrical Characteristics

The following specifications apply for AGND=DGND=0V, V

f

CRYSTAL IN

= 48MHz.

Boldface limits apply for T

A=TJ=TMIN

(Continued)

A=VD=VDRAM

to T

=+5.0VDC unless otherwise noted,

; all other limits TA=TJ=25°C. (Notes 8, 9, & 10)

MAX

Symbol Parameter Conditions

Digital Output Characteristics for D0-D15, A0-A9, RD

V

OUT(1)

V

OUT(0)

Digital Output Characteristics for A, B, A

V

OUT(1)

V

OUT(0)

Logical “1” Output Voltage

Logical “0” Output Voltage

, B

Logical “1” Output Voltage

Logical “0” Output Voltage

, WR, RAS, CAS (DRAM Interface)

V

V

V

V

V

V

V

V

DRAM

DRAM

DRAM

DRAM

DRAM

DRAM

DRAM

DRAM

=4.75V, I

=2.85V, I

=4.75V, I

=2.85V, I

=4.75V, I

=2.85V, I

=4.75V, I

=2.85V, I

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

=-4mA

=-4mA

=4mA

=4mA

=-10mA

=-10mA

=4mA

=4mA

Digital Output Characteristics for MISC I/O 1-6, TR1, TR2, ø1, ø2, RS, CP1, CP2, LAMP

V

V

OUT(1)

OUT(0)

Logical “1” Output Voltage VD=4.75V, I

Logical “0” Output Voltage VD=4.75V, I

OUT

OUT

=-4mA

=4mA

Digital Output Characteristics for D+, D-

V

V

OUT(1)

OUT(0)

Logical “1” Output Voltage VD=4.75V, I

Logical “0” Output Voltage VD=4.75V, I

OUT

OUT

=-1mA

=3mA

CRYSTAL IN, CRYSTAL OUT Characteristics

XTAL

XTAL

CRYSTAL OUT Bias Level (Offset) 0.8 V

OUT DC

CRYSTAL OUT Amplitude f

OUT AC

= 48MHz 0.8 V

CRYST AL

Power Supply Cha racteristics

I

I

I

DRAM

Analog Supply Current

A

(V

A

Digital Supply Current

D

(V

D

DRAM Supply Current

(V

DRAM

pins)

pins)

pins)

Operating

Suspend

Operating

Suspend (including I

Operating, V

Operating, V

Suspend

DRAM

DRAM

DRAM

= 5V

= 3V

)

Typica l

(Note 9)

, LAMPG, LAMP

R

87

1

37

14

10

5

14

Limits

(Note 10)

2.4

2.4

0.4

0.4

2.4

2.4

0.4

0.4

B

2.4

0.4

2.4

0.4

137

50

21

14

Units

(Limits)

V (min)

V (min)

V (max)

V (max)

V (min)

V (min)

V (max)

V (max)

V (min)

V (max)

V (min)

V (max)

P-P

mA (max)

µA (max)

mA (max)

µA (max)

mA (max)

mA (max)

µA (max)

4 www.national.com

Page 5

AC Electrical Ch ar acterist ic s

The following specifications apply for AGND=DGND=0V, VA=VD=V

f

CRYSTAL IN

C

= 48MHz, MCLK DIVIDER = 1.0 (unless otherwise noted), f

(databus loading) = 20pF/pin.

L

Boldface limits apply for T

A=TJ=TMIN

Symbol Parameter Conditions

DRAM Timing (Figure 1)

V

=5.0V

t

RD SETUP

t

RD HOLD

t

WR SETUP

t

WR HOLD

Note 1:

Absolute Maximum Ratings indicat e limits beyond which damage to the device may occur. Operating Ratings indicat e conditions for which the device is functional,

but do not guarantee specific performance limits. For guaranteed speci fications and test conditions, see the Elec trical Characteristics. The guaranteed specifications apply

only for the test cond itions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2:

All voltages are measured with respect to GND=AGND=DGND =0V, unless otherwise specified.

Note 3:

When the input voltage (V

maximum package input current rating limits the number of pins that can simultaneously safely exceed the power supplies with an input c urrent of 25mA to two.

Note 4:

The maximum power dissipati on must be derated at elevated temperatures and is dictated by T

able power dissipation at any temperature is P

.

is 53°C/W

Note 5:

Human body model, 100pF capacitor discharged through a 1.5kΩ resistor. Machine model, 200pF capacitor discharged through a 0Ω resistor.

Note 6:

See AN-45 0 “Sur fa ce M oun tin g Met hod s a nd T hei r E ffect o n Pro duct Reliab ility” o r the sectio n titled “Su rfa ce Mount” found in any N ational Semiconductor Linear

Data Book for other methods of soldering surface mount devices.

Note 7:

Two diodes clamp the OS analog inputs to

impedance of the sensor, prevents damage to the LM9831 from transients during power-up.

Data valid to RD rising edge

Data valid after RD rising edge

Data valid before WR falling edge

Data valid after WR rising edge

) at any pin exceeds the power supplies (VIN<GND or VIN>VA or VD), the current at that pin should be limited to 25mA. The 50mA

IN

= (TJmax - TA) /

D

AGND

and VA as shown below. This input protection, in combination with the external clamp capacitor and the output

DRAM

V

=3.3V

DRAM

Θ

. TJmax = 150°C for this device. The typical thermal resistance (

JA

VA

=+5.0VDC unless otherwise noted,

DRAM

MCLK

to T

= f

CRYSTAL IN

MAX

/MCLK DIVIDER, f

; all other limits TA=TJ=25°C. (Notes 8, 9, & 10)

Typical

(Note 9)

Θ

max,

and the ambient temperature, TA. The maximum allow-

J

JA

= f

ADC CLK

Limits

(Note 10)

26

35

0

5

10

Θ

) of this part when board mounted

JA

Units

(Limits)

ns (min)

ns (min)

ns (min)

ns (min)

ns (min)

MCLK

/8,

OS Input

To Internal

Circuitry

AGND

Note 8:

For best performance, it is required that all supply pins be powered from the same power supply with separate bypass capaci tors at each supply pin.

Note 9:

Typicals are at T

Note 10:

Tested limits are guaranteed to National's AOQ L (Average Outgoing Quality Level).

Note 11:

Integr al linearity error is def ined as the devi ation of the analog value, expressed in LSBs, from the straight line that best fits the actual transfer function of the ADC.

Note 12:

V

is defined as the CCD OS voltage for the reference period following the reset feedthrough pulse. V

REF

a white (full scale) image with respect to the reference level, V

correctable range of pixel-to-pixel V

LM9831 can correct for using its internal PGA.

Note 13:

PGA Gain Error is the maximum difference between the measured gain for any PGA code and the ideal gain calculated by using the formula

V

--- -

PGA

V

G0X

Gain

=25°C, f

J=TA

WHITE

PGA code

--------------- ----------- -+=XG

where .

32

= 48MHz, and represent most likely parametric norm.

CRYSTAL IN

.

is defined as the peak positive deviation above V

V

REF

variation is defined as the maximum variation in V

–

()

31G0

RFT

V

RFT

V

32

----- -=

31

CCD Output Signal

V

REF

WHITE

is defined as the peak CCD pixel output voltage for

WHITE

of the reset feedthrough pulse. The maximum

(due to PRNU, light source intensity variation, optics, etc.) that the

WHITE

REF

5 www.national.com

Page 6

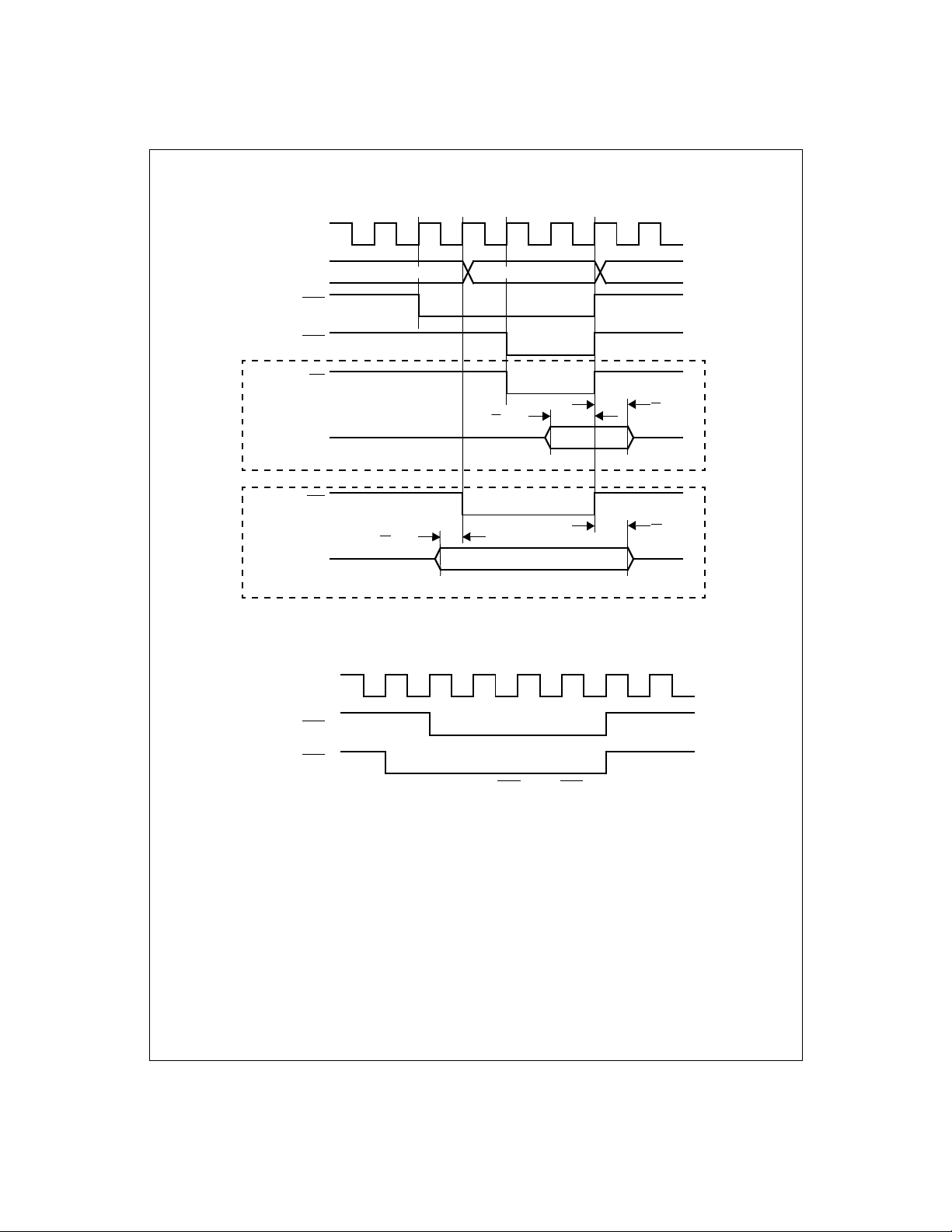

Timing Diagrams

48MHz Internal Clock

(t

= 20.83ns)

PERIOD

A0-A9 Row Address

RAS

CAS

RD

Read Operation

WR

Write Operation

01234560

n

Column Address

t

RD SETUP

n

Row Address

t

RD HOLD

n+1

DataD0-D15

t

t

WR SETUP

WR HOLD

DataD0-D15

Figure 1: DRAM Read and Write

48MHz Internal Clock

(t

= 20.83ns)

PERIOD

RAS

CAS

01234560

Figure 2: DRAM Refresh (CAS

before RAS)

6 www.national.com

Page 7

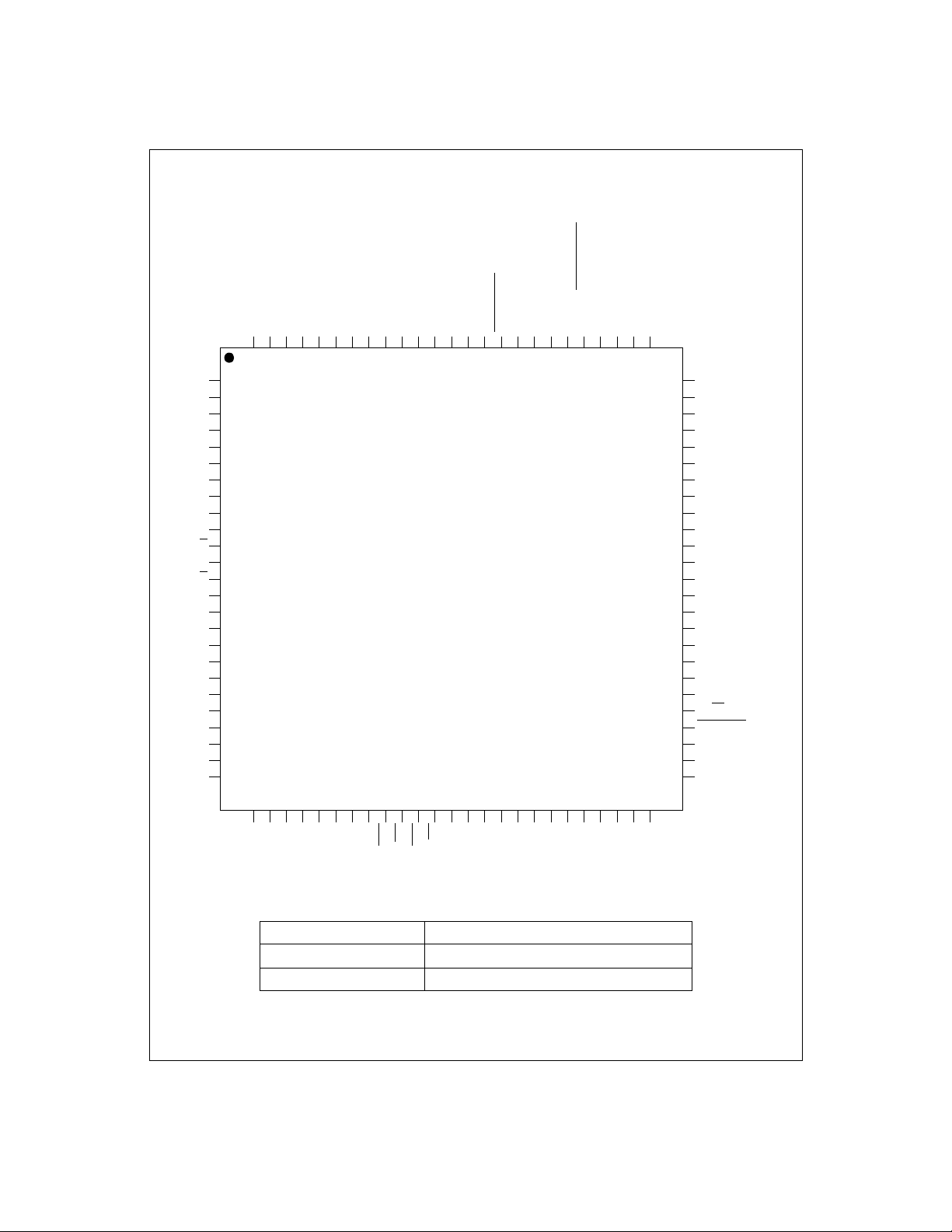

Connection Diagram

V

BANDGAP

V

REF LO

V

REF MID

V

REF HI

AGND

V

DGND

OS

OS

OS

V

D0

D15

DRAM

D1

D14

D2

D13

D3

D12

D4

D11

AGND VADGND VDTEST SENSEGND SENSEA SENSEB NC CMODE RESET NC NC DGND VDBUS POWR D+ D- V

10099 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76

1

2

3

R

4

5

G

6

7

B

8

9

A

A

10

A

11

B

12

B

13

14

LM9831VJD

15

16

17

18

19

20

21

22

23

24

25

26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

REGULATOR

DGND ACTIVE/SUSPENDED CP2 CP1 RS ø2

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

ø1

TR2

TR1

MISC I/O 6

MISC I/O 5

MISC I/O 4

DGND

V

MISC I/O 3

MISC I/O 2

MISC I/O 1

D

PAPER SENSE 1

PAPER SENSE 2

V

D

DGND

LAMP

B

LAMP

G

LAMP

R

DGND

V

D

24/48

CRYSTAL

CRYSTAL IN

/EXT

CRYSTAL OUT

SCL

CLK

D5

D6

D9

D10

Ordering Information

Commercial (0°C ≤ TA ≤ +70°C) Package

LM9831CCVJD VJD100A 100 Pin Thin Quad Flatpac

LM9831CCVJDX VJD100A 100 Pin Thin Quad Flatpac, Tape and Reel

D7

D8

WR

DRAM

DGND

V

CAS

A9A8A0A7A1

RD

RAS

A6A2A5A3A4

DRAM

DGND

V

SDA

7 www.national.com

Page 8

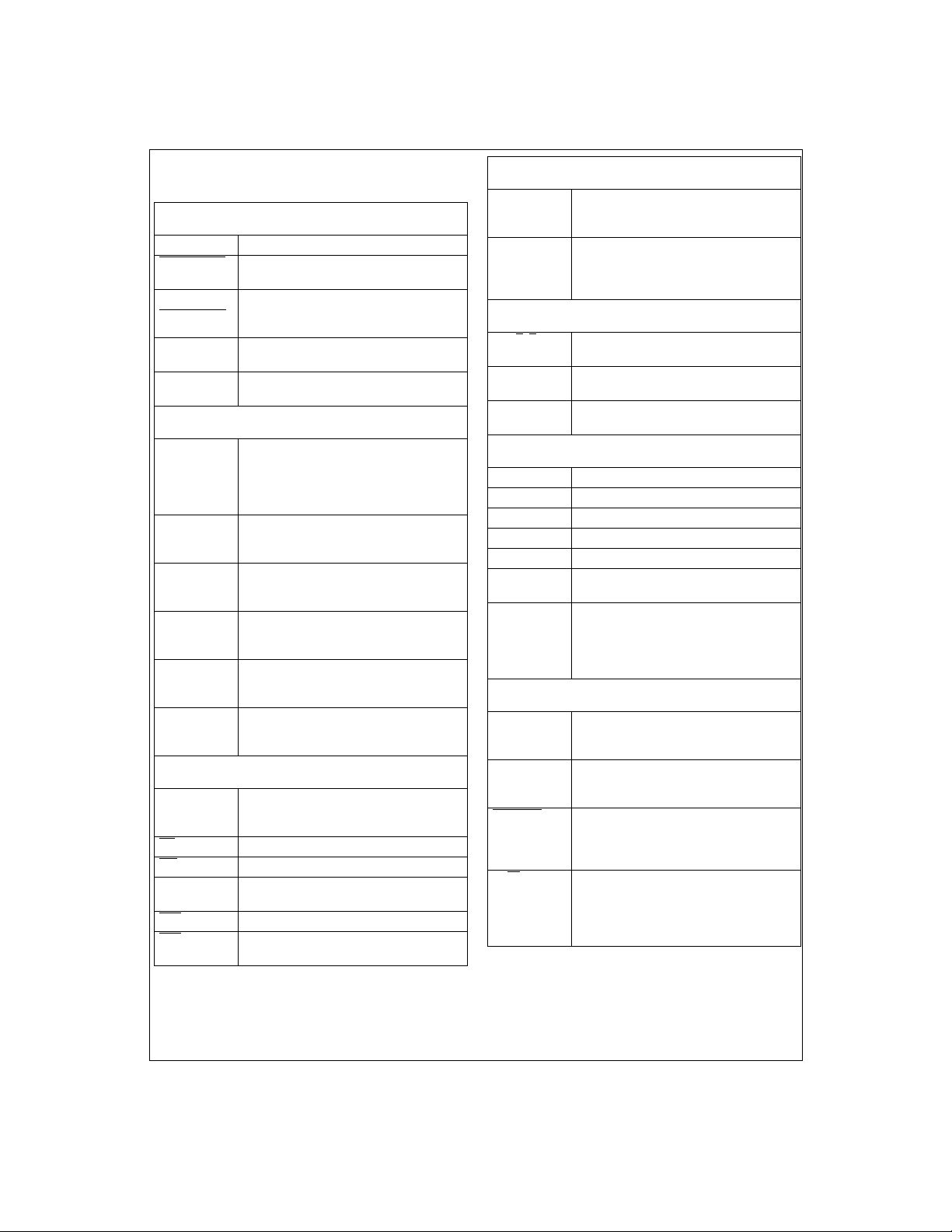

Pin Descriptions

g

USB Interface

D+, D- Digital I/O. USB Interface signals

BUS POWER

ACTIVE/

SUSPENDED

SDA Digital I/O. Serial Data to/from external

SCL Digital Output. Serial Clock Output to external

Digital Input. Tie low for bus powered systems, tie high for external power.

Digital Output. Low in Suspend mode. High in

operational mode. Used to control external

regulators, other components.

EEPROM.

EEPROM.

Analo

OSR,

OS

,

G

OS

B

V

REF LO

V

REF MID

V

REF HI

V

BANDGAP

V

REGULATOR

Analog Inputs. These i nputs (for Red, Green,

and Blue) should be tied to the sensor’s output signal th rough DC blocking capacitors. If

unused, tie to ground through DC blocking

capacitors.

Analog Output/Input. Bypass to AGND with a

0.047µF monolithic capacitor. Do not put a

DC load on this pin.

Analog Output/Input. Bypass to AGND with a

0.047µF monolithic capacitor. Do not put a

DC load on this pin.

Analog Output/Input. Bypass to AGND with a

0.047µF monolithic capacitor. Do not put a

DC load on this pin.

Analog Output. Bypass to AGND with a

0.047µF monolithic capacitor. Do not put a

DC load on this pin.

Analog Output. Bypass to AGND with a

0.047µF monolithi c capacitor. Used as terminal voltage for 1.5k D+ pullup resistor.

DRAM

D0 (LSB) -D15

(MSB)

RD

WR

A0-A9 Di gital Outputs. Address pins for up to 1M x

RAS

CAS

Digital Inputs/Outputs. This is the 16 bit data

path between the external DRAM and the

LM9831.

Digital Output. Read signal to external DRAM.

Digital Output. Write signal to external DRAM.

16 external DRAM.

Digital Output. Row Address Strobe signal.

Digital Output. Column Address Strobe sig-

nal.

Scanner Support I/O

PAPER

SENSE 1-2

MISC I/O 1-6 Digital Inputs/Outputs. Programmable, used

Digital Inputs. Programm able, used for sensing home position, paper, front panel

switches, etc.

for front panel switches, status LE Ds, etc. At

power-on and in Suspend Mode, MISC I/Os

1-3 are inputs and MISC I/Os 4-6 are outputs.

Stepper Motor

A, B, A, B Digital Outputs. Pulses to stepper motor drive

SENSE

A

SENSE

B

SENSE

GND

circuitry.

,

Analog Inputs. Current sensing for stepper

motor’s PWM current co ntrol.

Analog Input. G round se nse input for s tepper

motor’s PWM current co ntrol.

Sensor Control

ø1 Digital Output. CCD/CIS clock signal phase 1.

ø2 Digital Output. CCD/CIS clock signal phase 2.

RS Digital Output. Reset pulse for the CCD/CIS.

CP1 Digital Output. Clamp pulse for the CCD/CIS.

CP2 Digital Output. Clamp pulse for the CCD/CIS.

TR1, TR2 Digital Outputs. Transfer pulses for the

,

LAMP

R

LAMP

,

G

LAMP

B

CCD/CIS.

Digital Output s. Used to cont rol R, G, and B

LEDs of single output CIS, as wel l as brightness of CCFL. The CDS signal can b e seen

on LAMP

7).

in a test mode (see register 5E, bit

B

Master Clock Generation

CRYSTAL IN Digital Input. Used with CRYSTAL OUT and

CRYSTAL

OUT

CRYSTAL

EXT CL OCK

24/48

an external 48MHz crystal to form a crystal

oscillator.

Digital Output. Used with CRYSTAL IN and an

external 48MHz crystal to form a crystal oscillator.

/

Digital Input. Tie to DGND for operation wi th

an external crystal. Pull up to V

CRYSTAL OUT with an external TTL or

CMOS clock source.

Digital Input. Tie to DGND for operation with a

48MHz crystal or external clock. Pull up to V

for operation with a 24MHz crystal or external

clock. NOTE: Operation at 24MHz is not guaranteed - always use a 48MHz crystal.

to drive

D

D

8 www.national.com

Page 9

Miscellaneous

RESET Digital input. Ta ke high to force device into

TEST Analog Output.

CMODE Digital Input. Test mode, always tie high.

Power On Reset state, low to exit reset state.

Analog Power Supplies (4 pins)

VA (2) This is the positive supply pin for the analog

AGND (2) This is the ground r eturn for the analog sup -

supply. It should be connected to a v oltage

source of +5V and bypassed to AGND with a

0.1µF monolithic capacitor in parallel with a

10µF tantalum capacitor.

ply.

Digital Power Supplies (17 pins)

VD (5) This is the positive supply pin for the digital

(3) This is the po sitive supply pi n for the digital

V

DRAM

DGND (9) This is the ground return for V

supply. It should be connected to a v oltage

source of +5V and by passed to D GND wi th a

0.1µF monolithic capacitor.

supply for the LM9831’s external DRAM I/O. It

also powers the A, B, A

outputs. It should be connected to a 3 or 5V

supply and bypassed to the closest DGND pin

with a 0.1µF monolithic capacitor.

, and B stepper motor

and V

D

DRAM

.

9 www.national.com

Page 10

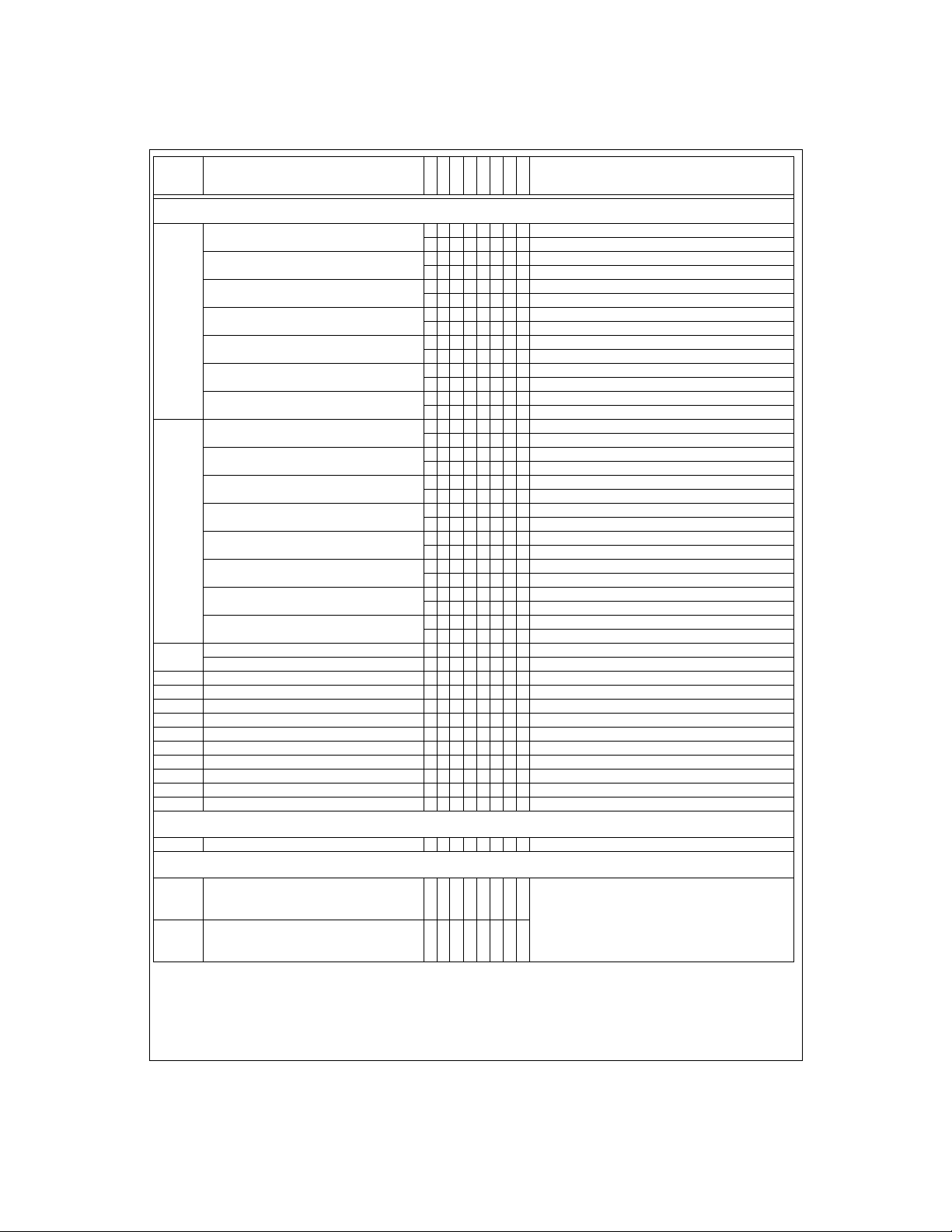

LM9831 Register Listing

Registers in bold boxes are reset to that value on power-up. All register addresses are in hexadecimal. All other numbers are

decimal unless otherwise noted.

Address Function

IMAGE BUFFER (READ ONLY)

00

Pixel (Image) D ata

STATUS REGISTERS (READ ONLY)

01

Image Data Available In Buffer

PAPER SENSE 1 State

read clears bit if edge sensitive input.

PAPER SENSE 2 State

read clears bit if edge sensitive input.

MISC I/O 1 State

read clears bit if edge sensitive input.

MISC I/O 2 State

read clears bit if edge sensitive input.

02

MISC I/O 3 State

read clears bit if edge sensitive input.

MISC I/O 4 State

read clears bit if edge sensitive input.

MISC I/O 5 State

read clears bit if edge sensitive input.

MISC I/O 6 State

read clears bit if edge sensitive input.

DATAPORT REGISTERS

DataPort Target

DataPort Targ et Color

03

Pause (Read Only)

This bit indicates whether or not the scanner

is currently paused due to a buffer full

condition.

DRAM Test

04

DataPort Address - MSB

05

DataPort Address - LSB

06

nnnnnnnn

DataPort

D7D6D5D4D3D2D1D

n n n n n n n n One byte of image data.

nnnnnnnn

0False

1True

0False

1True

0False

1True

0False

1True

0 Normal State

1 The scanner is currently in the pause/reverse cycle.

0 Normal Operation

1 DRAM Test mode

R

/Waaaaaa

aaaaaaaa

0

n*2 (256k x 16 DRAM) or n*8 (1M x 16 DRAM)

kilobytes of image data is available

0False

1True

0False

1True

0False

1True

0False

1True

0 0 Offset Coefficient Data

0 1 Gain Coefficient Data

1 0 Gamma Lookup Table

11N/A

00 Red

0 1 Green

10 Blue

11 N/A

Address of location to be read/written to.

a = 0 to 4095 for gamma tables,

0 to 16383 for Offset and Gain Coefficient Data

Addresses greater than these are illegal.

Bit D6 of register 4 indicates whether next operation

will be a Read (D6=1) or a Write (D6=0)

Data to be read from or written to the address of the

currently selected Dataport Target. The DataPort

Address is automatically incremented whenever one

(gamma data) or two (Gain/Offset Data) bytes are

read from or written to this register.

Value

.

10 www.national.com

Page 11

Address Function

COMMAND REGISTER

Command Register

This register is used to start and end a scan.

It is also used to home the sensor in a

flatbed scanner or eject the image in a

sheetfed scanner.

Note: Always make sure

the Command Register is in the idle state

(=0) before issuing a new command.

07

Standby

When this bit is set the entire chip enters a

low power state.

Warning: A Standby command will stop

DRAM refresh.

Reset

Write a 1 then a 0 to reset the LM9831’s

state machines.

Warning: A Reset will stop DRAM refresh.

MASTER CLOCK DIVIDER

MCLK Divider

This register sets the master clock frequency

for the entire scanner.

08

f

= 48MHz/MCLK_Divider

MCLK

f

= f

MCLK

/8

ADC

D7D6D5D4D3D2D1D

0

Idle - Stops motor (A, B, A

000

completes current line of data (if scanning).

Note: CCD/CIS clocks continue clocking.

High Speed Forward - Moves motor forward at a

001

speed determined by the Fast Feed Step Size

(registers 48 and 49).

High Speed Reverse - Moves motor backward at a

010

speed determined by the Fast Feed Step Size

(registers 48 and 49).

Start Scan - Resets the LM9831’s data pointers and

011

starts an image scan.

Programmed High Speed Forward - Moves motor

forward at a speed determined by the Fast Feed Step

101

Size (registers 48 and 49) for the number of lines

programmed in registers 4A and 4B.

Programmed High Speed Reverse - Moves motor

backward at a speed determined by the Fast Feed

110

Step Size (registers 48 and 49) for the number of lines

programmed in registers 4A and 4B.

0 Normal Operation

1 Low Power Standby Mode

0 Normal Operation

1 Resets the LM9831

000000÷1.0

000001÷1.5

000110÷4

a a a a a a ÷ ((aaaaaa/2)+1)

111110÷32.0

111111÷32.5

Value

, B = 0),

11 www.national.com

Page 12

Address Function

HORIZONTAL RESOLUTION AND DA TAMODE SETTINGS

Horizontal DPI Divider

This register determines the horizontal

resolution of the scan.

Scan resolution = Optical resolution divided

by the Horizontal_DPI_Divider.

Pixel Packing

This register determines how many bits in

09

each byte of data are transmitted to the host

when DataMode = 0

DataMode

When DataMode = 0, the pixel data is fully

processed, going through the Offset,

Shading, Horizontal DPI Adjust, Gamma,

and Pixel Packing blocks.

When DataMode = 1, 14 bit data is extracted

following the Shading Multiplier stage.

Gamma and any other post processing must

be done by the host.

RESERVED

0A Reserved 0 0 0 0 0 0 0 0 Write 00 to this register

SENSOR CONFIGURATION

Input Signal Polarity

CDS On/Off

Standard/Even-Odd Senso r

0B

CIS TR1 Timing Mode

Fake Optical Black Pixels

(for Dyna-type CIS sensors)

D7D6D5D4D3D2D1D

0 0 1 bit/pixel (1 bit grayscale/3 bit color)

0 1 2 bits/pixel (2 bit grayscale/6 bit color)

1 0 4 bits/pixel (4 bit grayscale/12 bit color)

1 1 8 bits/pixel (8 bit grayscale/24 bit color)

0

1

0 0 Off - use standard CCD Timing

01

10

11 N/A

0 Off: Normal operation

1 On: RS pulse held high for entire Optical Black period

0

000÷1

001÷1.5

010÷2

011÷3

100÷4

101÷6

110÷8

111÷12

1, 2, 4, or 8 bit image data,

as determined by the Pixel Size setting.

14 bit image data - sent in 2 bytes, MSB first:

First Byte: 13 12 11 10 09 08 07 06

Second Byte: 05 04 03 02 01 00 XX XX

(XX: bits set to 0)

0 Negative (Most CCD Sensors and Toshiba CIS)

1 Positive (Most CIS Sensors)

0 CDS Off

1 CDS On

0 Standard (1 pixels per Ø period)

1 Even/Odd (2 pixels per Ø period)

CIS TR1 Timing Mode 1:

TR1 pulse = exactly one Ø clock,

starting at rising edge of Ø1

CIS TR1 Timing Mode 2:

TR1 pulse = exactly one Ø clock,

TR1 centered around Ø1 high.

Value

12 www.national.com

Page 13

Address Function

SENSOR CONTROL SETTINGS

Ø1 Polarity

Ø2 Polarity

RS Polarity

0C

CP1 Polarity

CP2 Polarity

TR1 Polarity

TR2 Polarity

Ø1 Active/Off

Ø2 Active/Off

RS Active/Off

CP1 Active/Off

0D

CP2 Active/Off

TR1 Active/Off

TR2 Active/Off

Number of TR Pulses

TR Pulse Duration

0E

TR-Ø1 Guardband Duration

0F

Optical Black Clamp Start

10

Optical Black Clamp End

11

Rese t Pulse Start

12

Reset Pulse Stop

13

CP1 Pulse Start

14

CP1 Pulse Stop

15

CP2 Pulse Start

16

CP2 Pulse Stop

17

Reference Sample Position

18

Signal Sample Position

INTEGRATION TIME ADJUST

19

Integration Time Adjustment Function

STEPPER PHASE CORRECTION

1A

TR to Stepper Phase Correction - MSB

1B

TR to Stepper Phase Correctio n - LSB

D7D6D5D4D3D2D1D

0

Value

0Positive

1 Negative

0Positive

1 Negative

0Positive

1 Negative

0Positive

1 Negative

0Positive

1 Negative

0Positive

1 Negative

0Positive

1 Negative

0Off

1Active

0Off

1Active

0Off

1Active

0Off

1Active

0Off

1Active

0Off

1Active

0Off

1Active

01 TR Pulse

12 TR Pulses

n n n n n+1 pixel periods (1-16)

n n n n n pixel periods (0-15)

nnnnn

nnnnn

nnnnn

nnnnn

nnnnn

nnnnn

nnnnn

nnnnn

nnnnn

nnnnn

nnnnnnnt

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

= n*t

READOUT

, n = 1 to 127. n=0 turns off function.

INT

First step of scan occurs n pixels (1 - 16383) after first

nnnnnn

TR pulse. This register can be used to set the phase

between the TR pulses and the stepper motor pulses.

NOTE: a setting of n = 0 creates the maximum delay

nnnnnnnn

(16384) pixels, which will increase scan time. If this

function is not used, this register should be set to 1.

13 www.national.com

Page 14

Address Function

D7D6D5D4D3D2D1D

0

SENSOR PIXEL CONFIGURATION

1C

Optical Black Pixels Start

1D

Optical Black Pixels End

1E

Active Pixels Start - MSB

1F

Active Pixels Start - LSB

20

Line End - MSB

21

Line End - LSB

n n n n n n n n n pixels (0 - 255)

n n n n n n n n n pixels (0 - 255)

n n n n n n n pixels (0 - 16383)

nnnnnnnn

nnnnnn

nnnnnnnn

Set to the same value as register

n pixels (0 - 16383)

This selects the pixel count at which the current line is

ended and the next line begins. This determines the

integration time of one line.

PIXEL DATA RANGE TO PROCESS

n pixels (

22

Data Pixels S tart - MSB

nnnnnn

Active Pixels Start

This selects the start of the range of pixels transmitted

to the PC and determines the pixel location where

23

Data Pixels S tart - LSB

nnnnnnnn

offset and shading correction begins (pixel 0 in the

DataPort). This value must be >=

24

Data Pixels End - MSB

25

Data Pixels End - LSB

nnnnnnn pixels (

nnnnnnnn

Data Pixels Start

This selects the end of the range of pixels transmitted

to the PC. This value must be <= [

COLOR MODE SETTINGS

0 0 0 3 Channel Pixel Rate Color

AFE Operation

3 Channel or 1 Channel

0 0 1 3 Channel Line Rate Color

1 0 0 1 Channel Grayscale

1 0 1 1 Channel Color

1 Channel Grayscale Input Source

(1 Channel Color always uses the

26

Blue Channel as the input)

TR

(=TR1) position

RED

(3 Channel Line Rate Mode only)

TR

(=TR2) position

GREEN

(3 Channel Line Rate Mode only)

TR

(=CP2) position

BLUE

(3 Channel Line Rate Mode only)

0 0 Red Channel

0 1 Green Channel

1 0 B lue Channe l

11 N/A

0 1st TR pulse position (inside Ø1 high)

1 2nd TR pulse position (inside Ø1 low)

0 1st TR pulse position (inside Ø1 high)

1 2nd TR pulse position (inside Ø1 low)

0 1st TR pulse position (inside Ø1 high)

1 2nd TR pulse position (inside Ø1 low)

0 0 Do not drop any TR

3 Channel Line R ate TR

(3 Channel Line Rate Mode only)

RED

drop

0 1 Drop 1 TR

1 0 Drop 2 TR

11N/A

RED

RED

0 0 Do not drop any TR

3 Channel Line R ate TR

(3 Channel Line Rate Mode only)

27

GREEN

drop

0 1 Drop 1 TR

1 0 Drop 2 TR

11 N/A

GREEN

GREEN

0 0 Do not drop any TR

3 Channel Line R ate TR

(3 Channel Line Rate Mode only)

BLUE

drop

Triple TR output

0 1 Drop 1 TR

1 0 Drop 2 TR

11 N/A

BLUE

BLUE

0 Normal operation

1 Outputs single TR pulse on TR1, TR2, and CP2 pins

RESERVED

28 Reserved 0 0 0 0 0 0 0 0 Write 00 to this register

Value

Data Pixels Start

- 16383)

Active Pixels Start

- [

Line End

- 20])

Line End

pulses

RED

pulse (double integration time)

pulses (triple integration time)

pulses

GREEN

pulse (double integration time)

pulses (triple integration time)

pulses

BLUE

pulse (double integration time)

pulses (triple integration time)

.

- 20]

14 www.national.com

Page 15

Address Function

D7D6D5D4D3D2D1D

ILLUMINATION SETTINGS

Illumination Mode

Controls the function of the 3 LAMP outputs:

, LAMPG, and LAMP

LAMP

R

B

Mode 0 is the Off/Reset state.

Mode 1 is typically used for CCFL lamps.

29

Mode 2 is for color scanning with tri-color

LEDs.

Mode 3 is for grayscale scanning with tricolor LEDs.

2A

2C

2D

2E

2F

30

31

32

33

34

35

36

37

LAMP

LAMP

LAMP

LAMP

LAMP

LAMP

LAMP

LAMP

LAMP

LAMP

LAMP

LAMP

LAMP

LAMP

PWM - MSB

G

PWM - LSB

G

On - MSB

R

On - LSB

R

Off - MSB

R

Off - LSB

R

On - MSB

G

On - LSB

G

Off - MSB

G

Off - LSB

G

On - MSB

B

On - LSB

B

Off - MSB

B

Off - LSB

B

(Illumination Mode 1) n n n n LAMP

(Illumination Mode 1) n n n n n n n n

n n n n n n n pixels (1 - 16384)

nnnnnnnn

n n n n n n n pixels (1 - 16384)

nnnnnnnn

n n n n n n n pixels (1 - 16384)

nnnnnnnn

n n n n n n n pixels (1 - 16384)

nnnnnnnn

n n n n n n n pixels (1 - 16384)

nnnnnnnn

n n n n n n n pixels (1 - 16384)

nnnnnnnn

STATIC OFFSET AND GAIN SETTINGS FOR ANALOG FRONT END

38

Static Offset (Red)

39

Static Offset (Green)

3A

Static Offset (Blue)

3B

Static Gain (Red)

3C

Static Gain (Green)

3D

Static Gain (Blue)

0 n n n n n Offset = +n*9.3mV, n = 0 to 31

1 n n n n n Offset = -n*9.3mV, n = 0 to 31

0 n n n n n Offset = +n*9.3mV, n = 0 to 31

1 n n n n n Offset = -n*9.3mV, n = 0 to 31

0 n n n n n Offset = +n*9.3mV, n = 0 to 31

1 n n n n n Offset = -n*9.3mV, n = 0 to 31

0 n n n n n Gain = 0.93 + 0.067*n (V/V), n = 0 to 31

1 n n n n n Gain = 3(0.93 + 0.067*n) (V/V), n = 0 to 31

0 n n n n n Gain = 0.93 + 0.067*n (V/V), n = 0 to 31

1 n n n n n Gain = 3(0.93 + 0.067*n) (V/V), n = 0 to 31

0 n n n n n Gain = 0.93 + 0.067*n (V/V), n = 0 to 31

1 n n n n n Gain = 3(0.93 + 0.067*n) (V/V), n = 0 to 31

0

= LAMPG = LAMPB = 0V

LAMP

00

R

(Power-On/Reset Default)

Illuminati on Mode 1 - LAMP

every line, with their on and off points controlled by

the Pixel Counter settings. LAMP

continuous PWM pulse stream. (Figure 20)

01

LAMP

and/or LAMPB may be set to stay on or off at

R

all times by setting the LAMP Off or LAMP On settings

Value

and LAMPB turn on

R

Output is

G

(registers 2C-37) greater than the Line End value

(registers 20 and 21).

Illumination Mode 2 - LAMP

sequentially at the line rate, with their on and off

10

points controlled by Pixel Counter settings. (Figure

, LAMPG, LAMPB turn on

R

21)

Illumination Mode 3 - LAMP

11

every line, with their on and off points controlled by

, LAMPG, LAMPB turn on

R

the Pixel Counter settings. (Figures 22 and 23)

output is a PWM pulse stream. Duty cycle is

G

n/4095. Frequency = 48Mhz/4096 = 11.7kHz2B

This selects the pixel count at which the LAMP

output goes high (if programmed)

This selects the pixel count at which the LAMP

output goes low (if programmed)

This selects the pixel count at which the LAMP

output goes high (if programmed)

This selects the pixel count at which the LAMP

output goes low (if programmed)

This selects the pixel count at which the LAMP

output goes high (if programmed)

This selects the pixel count at which the LAMP

output goes low (if programmed)

R

R

G

G

B

B

15 www.national.com

Page 16

Address Function

DIGITAL PIXEL RATE OFFSET AND GAIN SETTINGS

3E

Fixed Offset Coefficient - MSB

3F

Fixed Offset Coefficient - LSB

40

Fixed Multiplier Coefficient - MSB

41

Fixed Multiplier Coefficient - LSB

DIGITAL PIXEL RATE OFFSET AND GAIN/DRAM SETTINGS

Shading Multiplier

Multiplier Coefficient Source

42

Offset Coefficient Source

Reserved

DRAM Size

D7D6D5D4D3D2D1D

nnnnnnnn

nnnnnn00

nnnnnnnn

nnnnnnnn

0

Fixed Offset to use for calibration

Fixed Gain to use for calibration

0 Gain = [Multiplier Coefficent]/16384

1 Bypass Multiplier

0 Configuration Register 40 and 41 (Fixed)

1 External DRAM

0 Configuration Register 3E and 3F (Fixed)

1 External DRAM

1 0 Set to 10

0 256k x 16

11M x 16

Value

16 www.national.com

Page 17

Address Function

STEPPER MOTOR CONTROL SETTINGS

n (Line Skipping)

43

Part of the “n out of m” function, consisting of

registers 43, 44, and 54 (bits 3-7).

m (Line Skipping)

44

Part of the “n out of m” function, consisting of

registers 43, 44, and 54 (bits 3-7).

Full/Microstepping

Current Sensing Phases

= 0 for fullstepping

= 1 fo r microstepping

Stepper Motor Phase A Polarity

45

Stepper Motor Phase B Polarity

A, B, A

, and B stepper motor status

46

Scanning Step Size - MSB

Scanning Step Size - LSB

48

Fast Feed Step Size - MSB

Fast Feed Step Size - LSB

4A

Fullsteps to Skip at Start of Scan - MSB

Fullsteps to Skip at Start of Scan - LSB

Fullsteps to Scan after PAPER SENSE 2

4C

trips -MSB

Fullsteps to Scan after PAPER SENSE 2

trips -LSB

4E

Pause scanning, stop/reverse motor

4F

Resume scanning, start motor

50

Full steps to reverse when buffer is full

Accelerati on Profile (stopped)

Acceleration Profile (25%)

51

Acceleration Profile (50%)

Default Phase Difference - High Byte

52

Default Phase Difference - Mid Byte

53

Default Phase Difference - Low Byte

Lines to Process After Pause/

Lines to Discard after Resume

Line Skipping Phase

Part of the “n out of m” function, consisting of

54

registers 43, 44, and 54 (bits 3-7).

Line Skipping Color Phase Delay

Part of the “n out of m” function, consisting of

registers 43, 44, and 54 (bits 3-7).

Kickstart steps

55

Hold Current Timeout

56

Stepper Motor PWM Frequency

57

Stepper Motor PWM Set Duty Cycle

(fullstepping mode) n n n Motor gets maximum current for first n (0-7) full steps

D7D6D5D4D3D2D1D

tttttttt

mmmmmmmm

0

1A, B, A

n n n n n n n n The step size of one microstep while scanning, in

nnnnnnnn

n n n n n n The step size of one microstep while fast feeding, in

nnnnnnnn

n n n n n n n When scan starts, paper is fed forward n full steps (0 -

nnnnnnnn

nnnnnnnn

nnnnnnnn

nnnnnnnn

n n n n n n n (0-63) full steps (0 = do not reverse)

n n n (0-3) full steps at 25% speed

n n n (0-3) full steps at 50% speed

nnnnnnnn

nnnnnnnn

n n n n n lines, n = 0-15

n n n n n Full step time units (1-31) (do not set to 0)

nnnnnnnn

n n n n n n = minimum of n/64 (default = 0)

17 www.national.com

0

n lines saved in DRAM for every m lines (register 44)

scanned, function bypassed if register value = 0.

n (lines saved per m lines scanned) = 256 - t

t = 256 - n

If t = 0 then function is bypassed.

n lines (register 43) saved in DRAM for every m lines

scanned. m = 1 to 255.

If m = 0 then function is bypassed.

0 Full Step Mode

1 Microstepping Mode

1 Phase - No microstepping, just kickstart/stop

0

functions

1 2 Phases - necessary for microstepping

0

Positive (A/B/A

Negative (A/B/A

WARNING: When idle, this setting leaves the motor

1

energized for unipolar motors, and will destroy bipolar

motor drivers. Keep this bit set to a 0.

0

1

n n n n Adds a delay of n (0-4095) full steps between when

n n n (0-3) full step time units pause while stopped

0 Red sensor data arrives before Green sensor

1 Blue sensor data arrives before Green sensor

Positive (A/B/A

Negative (A/B/A

WARNING: When idle, this setting leaves the motor

energized for unipolar motors, and will destroy bipolar

motor drivers. Keep this bit set to a 0.

A, B, A

, and B output pins in Tri-State

, and B output pins active

units of pixel periods (minimum 2)47

units of pixel periods (minimum 2)49

32767) at highest speed. For “zooming” in flatbeds4B

PAPER SENSE 2 trips and when the scanning bit is

reset, terminating the scan/motor movement4D

Pause scan when buffer is n*2 (16 x 256k) or

n*8 (16x1M) kbytes full

Resume scan when buffer is n*2 (16 x 256k) or

n*8 (16x1M) kbytes full

n n 18 bit word used to calculate when motor resumes

after reversing and stopping. 1 < n < 262143. 2 bits in

register 51 are the most significant bits of 18 bit word.

n (0-7) lines. This only applies if the motor doesn’t

nnn

reverse (reverse steps = 0)

=CRYSTAL OUT/(256*n) (0 < n < 256)

=CRYSTAL OUT/(256*256) (n = 0)

Value

/B Output high = winding energized)

/B output low = winding energized)

/B Output high = winding energized)

/B output low = winding energized)

Page 18

Address Function

PAPER SENSE SETTINGS

PAPER SENSE 1: Polarity

PAPER SENSE 1: Level/Edge sensitive

PAPER SENSE 1: Stop Scan

58

PAPER SENSE 2: Polarity

PAPER SENSE 2: Level/Edge sensitive

PAPER SENSE 2: Stop Scan

MISC I/O PIN SETTINGS

MISC I/O 1: Input or Output

MISC I/O 1: Polarity

(if configured as an input)

MISC I/O 1: Level/Edge sensitive

(if configured as an input)

MISC I/O 1: Output State

(if configured as an output)

Power On/USB Suspend Default: Input

59

MISC I/O 2: Input or Output

MISC I/O 2: Polarity

(if configured as an input)

MISC I/O 2: Level/Edge sensitive

(if configured as an input)

MISC I/O 2: Output State

(if configured as an output)

Power On/USB Suspend Default: Input

D7D6D5D4D3D2D1D

0

1

0

1

0 The MISC I/O 2 pin is configured as an input.

1 The MISC I/O 2 pin is configured as an output.

0 A low input on MISC I/O 2 is True

1 A high input on MISC I/O 2 is True

0

1

0

1

0

0 A low input on PAPER SENSE 1 is True

1 A high input on PAPER SENSE 1 is True

Level sensitive: PAPER SENSE 1 State bit (in Status

0

Register) is set to a 1 if PAPER SENSE 1 is currently

True.

Edge sensitive: PAPER SENSE 1 State bit (in Status

1

Register) is set to a 1 if PAPER SENSE 1 has been

True since the last time the Status Register was read.

Transitions on PAPER SENSE 1 will not clear the

0

scanning bit.

A False - to - True transition on PAPER SENSE 1 will

1

0 A low input on PAPER SENSE 2 is True

1 A high input on PAPER SENSE 2 is True

0

1

clear the Command Register and stop the scan.

Level sensitive: PAPER SENSE 2 State bit (in Status

Register) is set to a 1 if PAPER SENSE 2 is currently

True.

Edge sensitive: PAPER SENSE 2 State bit (in Status

Register) is set to a 1 if PAPER SENSE 2 has been

True since the last time the Status Register was read.

Transitions on PAPER SENSE 2 will not clear the

scanning bit.

A False - to - True transition on PAPER SENSE 2 will

clear the Command Register and stop the scan (after

the number of lines specified in the

after PAPER SENSE 2 trips

0 The MISC I/O 1 pin is configured as an input.

1 The MISC I/O 1 pin is configured as an output.

0 A low input on MISC I/O 1 is True

1 A high input on MISC I/O 1 is True

Level sensitive: MISC I/O 1 State bit (in Status

0

Register) is set to a 1 if MISC I/O 1 is currently True.

Edge sensitive: MISC I/O 1 State bit (in Status

1

Register) is set to a 1 if MISC I/O 1 has been True

since the last time the Status Register was read.

The output of the MISC I/O 1 pin will be a logic low

(0V).

The output of the MISC I/O 1 pin will be a logic high

(5V).

Level sensitive: MISC I/O 2 State bit (in Status

Register) is set to a 1 if MISC I/O 2 is currently True.

Edge sensitive: MISC I/O 2 State bit (in Status

Register) is set to a 1 if MISC I/O 2 has been True

since the last time the Status Register was read.

The output of the MISC I/O 2 pin will be a logic low

(0V).

The output of the MISC I/O 2 pin will be a logic high

(5V).

Value

Lines to Scan

register).

18 www.national.com

Page 19

Address Function

MISC I/O 3: Input or Output

MISC I/O 3: Polarity

(if configured as an input)

MISC I/O 3: Level/Edge sensitive

(if configured as an input)

MISC I/O 3: Output State

(if configured as an output)

Power On/USB Suspend Default: Input

5A

(NEW)

MISC I/O 4: Input or Output

MISC I/O 4: Polarity

(if configured as an input)

MISC I/O 4: Level/Edge sensitive

(if configured as an input)

MISC I/O 4: Output State

(if configured as an output)

Power On/USB Suspend Default: Output,

Logic High

MISC I/O 5: Input or Output

MISC I/O 5: Polarity

(if configured as an input)

MISC I/O 5: Level/Edge sensitive

(if configured as an input)

MISC I/O 5: Output State

(if configured as an output)

Power On/USB Suspend Default: Output,

5B

Logic High

(NEW)

MISC I/O 6: Input or Output

MISC I/O 6: Polarity

(if configured as an input)

MISC I/O 6: Level/Edge sensitive

(if configured as an input)

MISC I/O 6: Output State

(if configured as an output)

Power On/USB Suspend Default: Output,

Logic Low

D7D6D5D4D3D2D1D

0 The MISC I/O 4 pin is configured as an input.

1 The MISC I/O 4 pin is configured as an output.

0 A low input on MISC I/O 4 is True

1 A high input on MISC I/O 4 is True

0

1

0

1

0 The MISC I/O 6 pin is configured as an input.

1 The MISC I/O 6 pin is configured as an output.

0 A low input on MISC I/O 6 is True

1 A high input on MISC I/O 6 is True

0

1

0

1

0

0 The MISC I/O 3 pin is configured as an input.

1 The MISC I/O 3 pin is configured as an output.

0 A low input on MISC I/O 3 is True

1 A high input on MISC I/O 3 is True

Level sensitive: MISC I/O 3 State bit (in Status

0

Register) is set to a 1 if MISC I/O 3 is currently True.

Edge sensitive: MISC I/O 3 State bit (in Status

1

Register) is set to a 1 if MISC I/O 3 has been True

since the last time the Status Register was read.

0

1

0

1

The output of the MISC I/O 3 pin will be a logic low

(0V).

The output of the MISC I/O 3 pin will be a logic high

(5V).

Level sensitive: MISC I/O 4 State bit (in Status

Register) is set to a 1 if MISC I/O 4 is currently True.

Edge sensitive: MISC I/O 4 State bit (in Status

Register) is set to a 1 if MISC I/O 4 has been True

since the last time the Status Register was read.

The output of the MISC I/O 4 pin will be a logic low

(0V).

The output of the MISC I/O 4 pin will be a logic high

(5V).

0 The MISC I/O 5 pin is configured as an input.

1 The MISC I/O 5 pin is configured as an output.

0 A low input on MISC I/O 5 is True

1 A high input on MISC I/O 5 is True

Level sensitive: MISC I/O 5 State bit (in Status

0

Register) is set to a 1 if MISC I/O 5 is currently True.

Edge sensitive: MISC I/O 5 State bit (in Status

1

Register) is set to a 1 if MISC I/O 5 has been True

since the last time the Status Register was read.

The output of the MISC I/O 5 pin will be a logic low

(0V).

The output of the MISC I/O 5 pin will be a logic high

(5V).

Level sensitive: MISC I/O 6 State bit (in Status

Register) is set to a 1 if MISC I/O 6 is currently True.

Edge sensitive: MISC I/O 6 State bit (in Status

Register) is set to a 1 if MISC I/O 6 has been True

since the last time the Status Register was read.

The output of the MISC I/O 6 pin will be a logic low

(0V).

The output of the MISC I/O 6 pin will be a logic high

(5V).

Value

19 www.national.com

Page 20

Address Function

TEST MODE SETTINGS

5C

ADC Output Code - MSB

ADC Output Code - LSB

ADC Test Mode

Pixel Processing Input Select

5E

16 bit Counter Increment Select

(16 bit counter starts at 0, increments every

datapixel)

MCLK edge for AFE (Set this bit to 0)

CDS Signal

5F-7F

Reserved

D7D6D5D4D3D2D1D

0

Value

n n n n n n n n Used to force the input to the HDPI Divider to a known

nnnnnnnn

value for digital tests5D

0 0 Normal Operation

0 1 Bypass AFE, Normal ADC Operation

Bypass AFE, bypass ADC digital correction,

10

output uncorrected ADC MSB

Bypass AFE, bypass ADC digital correction,

11

output uncorrected ADC LSB

0 0 Normal Operation - ADC Output

0 1 Registers 5C and 5D

1 0 16 bit counter, reset at the start of every scan

1 1 16 bit counter, reset at the start of every line

0 0 Increments by 1

0 1 Increments by 4

1 0 Increments by 16

11 N/A

0 Rising

1 Falling

0 Normal Operation

1 CDS signal is output on LAMP

0 0 0 0 0 0 0 0 Write 00 to these registers

B

pin

20 www.national.com

Page 21

Applications Information

1.0 OVERVIEW

The LM9831 i s a U SB, 12 00dpi , 14 bi t (42 bi t c olor) s c anner- ona-chip.

2.0 ANALOG SIGNAL PROCESSING

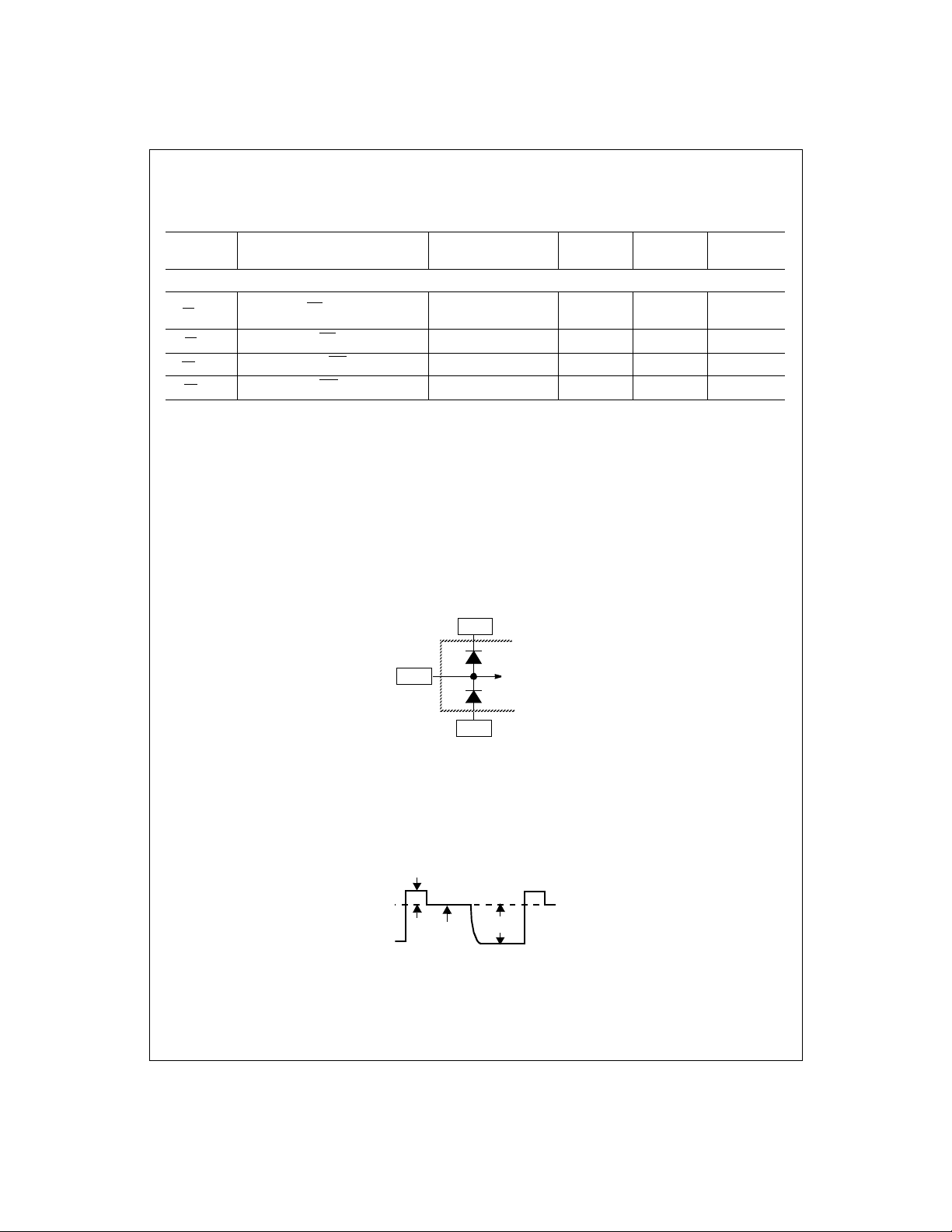

One channel of the LM9831’s analog front end is shown in Figure

3. The gain through each channel can be set between 0.93V/V

and 9.0V/V us ing r egi sters 3 B, 3C, a nd 3 D. T he offset DAC provides up to ±278mV of offset correction using regi sters 38, 39,

and 3A. The offset DAC and gain stages shoul d be adjusted dur ing coarse calibr ation so that the input signal is a maximum of

1.9Vp-p at the ADC input.

3.0 DIGITAL SIGNAL PROCESSING

3.1 ADC

The digital pixel d ata comes fr om a 6MHz 1 4 bit pipelined A DC.

The output data is formatted as a 16 bit word. The pixel data is in

the upper 14 bits, and the lower two bits are set to 0.

3.2 Pixel Processing Block

The Pixel Proce ssing stage i s used to dig ital ly reduc e the opti cal

resolution of the sensor. The optical resolution can be reduced by

a factor of 1, 1.5, 2, 3, 4, 6, 8, or 12. For a 1200 dpi (optical) system, this would p roduce resol uti ons of 1200 , 800, 600, 4 00, 300,

200, 150, and 100. A 600 dpi (o ptical) system woul d be capable

of 600, 400, 300, 200, 150, 100, 75, and 50 dpi. (Resolution in the

vertical direction is controlled by the stepper motor speed.)

Horizontal resolution reduction is accomplished by averaging

adjacent pixels. Averaging produces better image quality and

reduces aliasing v ersus the traditional technique of s imply discarding pix els to r educe r esolution. For example, t o get 100 dpi

from a 300dpi optical sensor, you would average 3 300dpi pixels:

p

++

pixel

100dpi

n-2pn-1pn

----------------- -------------------------- -=

3

The number of pixels coming out of the Pixel Processing block is

equal to the integer portion of the number of pixels going in to the

Pixel Processing block divided by the “Divide By” setting, from the

table shown in Figure 4.

Pixels

IN

Pixels

OUT

------------------- ------

INT

=

Divide By

This equation also applies to the divide by 1.5 function.

Divide

By

DPI

(1200

DPI

system)

DPI

(800

DPI

system)

DPI

(600

DPI

system)

DPI

(300

DPI

system)

1 1200 800 600 300

1.5 800 533 400 200

2 600 400 300 150

3 400 267 200 100

4 300 200 150 75

6 200 133 100 50

8 150 100 75 37.5

12 100 67 50 25

Figure 4:

Decreasing Horizontal Resolution

If there are not en ough pixel s a t the end of a line to for m a co mplete pixel, the l ast pixel will b e el iminated . F or ex ampl e, if a l ine

is 35 pixels wide and the Horizontal DPI setting is set to divide by

6, then the outpu t of the Pixel Processin g block will be 5 pixe ls

(the integer portio n of 35/6). The last 5 pixels will be discarded,

since 6 pixels would be required to form a new pixel in this mode.

The output of this stage is sent to the Pixel Rate Offset Correction

Block.

3.3 Pixel Rate Offset Correction Block

Offset correction words for every pixel of the CCD are stored in

the external DRAM and acces sed at the pixel rate . A digital s ubtractor subtracts the 16 bit offset word (corresponding to that

pixel’s offset error) from each pixel.

Gain Boost

1V/V or

3V/V

+

+

V

IN

G

Σ

+

V

OS1

B

D

OUT

= (((VIN + V

+

Σ

+

V

OS2

Offset

DAC

simplified, with all offsets = 0, this is:

D

OUT

PGA

0.93V/V to

3V/V

G

Σ

+

V

DAC

+ V

OS1)GB

= (VINGB + V

PGA

+ V

DAC

DAC)GPGA

+

Σ

+

V

OS3

OS2)GPGA

+ V

14 Bit

ADC

OS3

D

OUT

)C

C

C is a constant that combines the gain error through the AFE, reference voltage variance, and analog voltage

to digital code conversion into one constant. Ideally, C = 8192 codes/V (16384codes/1.9V).

Manufacturing tolerances widen the range of C. See Electrical Specifications.

Figure 3: Analog Front End (AFE) Model

21 www.national.com

Page 22

The subtractor saturates at 0, i.e. if the coefficient to be subtracted is gre ater than the ADC ou tput c ode, the r esul t is an output of 0.

The offset words stored in DRAM are typically calculated by

scanning a black calibration strip at 14 bits, and storing the

results in the DRAM using the DataPort.

The offset subtractor onl y uses the upper 14 bits of the 16 bit

word. When scanni ng in 14 bit mode , a pixel is transmitted as a

16 bit word, with the upper 14 bits containing the image data. The

2 LSBs of the image data and the offset correction word shoul d

be 00.

The offset correction equation is:

Pixel

PixelINcoefficient

OUT

–=

3.6 Pixel Packing/Thresholding Block

Some scans require only one bit per pixel (“line art” mode), others

may need only 2 or 4 bits/pixel. To increase scanning speed for

lower pixel depths, the LM9831 packs the desired MSBs of multiple pixels together into 1 16 bit word, increasing the transmission

speed to the host by a factor of 2, 4, 8, or 16. Figure 6 shows how

the pixels are packed together for 8, 4, 2, and 1 bit pixel depths.

In Figure 6, “b” indicates the bit position (b7 = the most significant

and b0 = the l east sign ificant b it) of t he origi nal 8 bi t pixel data,

and p

indicates the original pixel sequence, i.e p0, p1, p2, p3...

n

If there are not enough unpa cked pixels at the end of a line to

complete the pac ked wor d for tr ans miss ion, that fi nal word is no t

sent. For example, doing an 8 bit pixel rate s can with a HDPI

divider of 1 and an o dd number of pixels will tr uncate the blue

component of the last pixel.

3.4 Pixel Rate Gain Correction Block

This is a digital mul ti plier that m ultipl ies the output wor d from th e

subtractor by a 16 bi t digital correc tion coefficient c orrespondin g

to that pixel’s gain error. The coefficients are stored in the external RAM and accessed at the pixel rate.

The multiplier satu rates at 16383, i .e. if the result of the multipl ication is greater than 16383, the multiplier output is 16383.

The gain equation is:

coefficient

Pixel

OUT

Pixel

⋅=

IN

------------------ -------- 16384

Note that a coefficient of 0 represents a gain of 0. On the LM9830

and previous par ts, a co efficient of 0 r epres ente d a gai n o f 1. To

achieve a gain of 1, the coefficient should be set to 16384.

3.5 Gamm a Correction Tables

There are 3 gamma l ookup tabl es for R, G, an d B. The input t o

the table is the 12 MSBs (mos t signi ficant b its) of the 14 bit pi xel

data coming from the prev ious stag e (

rection Block

). The output is the 8 bit gamma correc ted pixel

3.4 Pixel R ate Gain Cor-

data. The tables consume 12k words (4K bytes x 16 bits, only the

8 LSBs of each word is used) of the external DRAM. Each

gamma table (red, gr een , and b lue) c an be loaded with any arbitrary user-defined transfer curve.

255

8 Bit Pixel Out

0

0 4095

The gamma tables ar e lo aded throu gh the da tapor t (see

12MSBs of 14 bit Output

Figure 5:

Gamma Table

6.1 The

DataPort: Reading and Writing to Gamma, Offset, and Gain

). The DataPort selects which color (Red, Green or Blue)

Memory

gamma table will be read from or written to.

Pixel

Depth

bit15bit14bit13bit12bit11bit10bit9bit

8 b7 p

4 b7 p0b6 p0b5 p0b4 p0b7 p1b6 p1b5 p1b4 p

b6 p0b5 p0b4 p0b3 p0b2 p0b1 p0b0 p

0

2 b7 p0b6 p0b7 p1b6 p1b7 p2b6 p2b7 p3b6 p

1 b7 p0b7 p1b7 p2b7 p3b7 p4b7 p5b7 p6b7 p

8

0

1

3

7

bit7bit6bit5bit4bit3bit2bit1bit

0

8 b7 p

4 b7 p2b6 p2b5 p2b4 p2b7 p3b6 p3b5 p3b4 p

2 b7 p4b6 p4b7 p5b6 p5b7 p6b6 p6b7 p7b6 p

1 b7 p8b7 p9b7 p10b7 p11b7 p12b7 p13b7 p14b7 p

Figure 6:

The gamma table in

b6 p1b5 p1b4 p1b3 p1b2 p1b1 p1b0 p

1

Packing Multiple Pixels Into One Word

3.5 Gamma Correction Tables

1

3

7

15

allows the

user to set the threshol d of each tran sition for vario us line art or

reduced pixel depth modes.

3.7 14 Bit Output Mode

For calibration purposes, it is useful to get the 14 bit data from the

ADC. This mode is set thr oug h register 9, bit 5. In th e 14 bit output mode, the gamma and pixel packi ng stages are bypas sed,

and the 14 bit data from the ADC is stored in DRAM, formatted as

shown in Figure 7.

MSB 151413121110 9 8

b13 b12 b11 b10 b9 b8 b7 b6

LSB76543210

b5 b4 b3 b2 b1 b0 0 0

Figure 7:

14 Bit Output Mode Data Format

The 14 bit data is stored as a 16 bit word, with the 2 least significant bits of the 16 bit word set to 0.

3.8 Line Buffer

The line buffer use s the external DRAM as a FIF O line bu ffer to

store the pixel data (whi ch is gener ated at a fixed rate, s ynchronous to the CCD clocks) and send it back to the PC at an asynchronous, unpredictable, and non-constant rate.

The LM9831 s upports 2 sizes of DRA M, 256k x 16bit and 1M x

16bit. 216kbytes (108kwords) of the capacity of the DRAM is consumed by the offset and shading coefficients and the gamma

22 www.national.com

Page 23

tables. That leave s 296kby tes of mem ory av ailabl e for line buffer

4

FSPI

StepSize

pixels/line

X

⋅

------------------ ------------------

=

when using a 256k x 16 bit DRAM, or 1832kbyte s of memory

when using a 1M x 16 bit DRAM.

The line buffer is tig htly coupl ed to the stepper motor (

per Motor Con tro ller

), and is responsible for stopping the motor

4.0 Step-

before the buffer overflow s and starting the motor again as the

buffer nears empty.

If the scanner i s generating pixel data faster t han the PC can

acquire it, the line buffer will start to fill up. As the buffer nears

100% of its capacity, the scan must be paused before it starts

acquiring a line which will overflow the buffer. This Pause Threshold limit (register 4E) is programmable in 2 kbyte (256k x 16 bi t

DRAM) or 8kbyte (1M x 16 bit DRAM) increments between 0 and

255.

To maximize scanner performance and mini mize pausi ng due to

buffer full conditions, the pause threshold should be set using this

formula:

Pause Threshold (kB) = Available_Memory - (Line_Length + 1)

where Available_Memory = 296kbytes (256k x 16b DRAM) or

1832kbytes (1M x 16 bit DRAM),

Line_Length = (Bytes/Line)/102 4

Data Pixels

------------------- ---------------- -

Bytes/Line 2 INT

=

⋅

INT

HDPI_Divider

-------------------- --------------------------------- ------------------ -

CB⋅⋅

16

Where C = 1 for “1 Channel Grayscale”, 3 for all other modes,

Data_Pixels = Data Pixels End (register s 24, 25) - Data Pixels

Start (registers 22, 23)

HDPI_Divider = Horizontal DPI divider = 1, 1.5, 2, 3, 4, 6, 8, or 12

B = Bits per Pixel = 16 (14 bit mode), 8, 4, 2, or 1

Register 4E value = Pause Threshold (kB)/2 (256k x 16 DRAM)

or Pause Threshold (kB)/8 (1M x 16 DRAM)

When the Pause Thr eshold is reached t he buffer sends a c om-

mand to the stepper motor controller to stop scanning. The

remainder of the l ine being processed will c ontinue being processed and be sent to the buffer. If the Lines To Process After

Pause Scan Sig nal register (reg ister 54) is grea ter than 0, then

room for these additio nal lines needs to be adde d into the Pause

Threshold value calculation.

Note that the scanner software on the host PC must set a Pause

Threshold value lo w enough to ens ure that any data that comes

after a pause request (the r es t of the current l ine and any subs equent lines if register 54 bits 0-2 are greater than 0) will fit into the

DRAM buffer. If the Pause Thres hold is set too high, the Lin e

Buffer may overflow, creating discontinuities in the scanned

image.

After a pause, the buffer wi ll continue to tra nsmit data to the P C

until it hits the Resume Threshold limit (register 4F), which is also

programmable in 2 kbyte (256 k x 16 bit DRAM ) or 8kbyte (1M x

16 bit DRAM) increments between 0 and 255. When the Resume

Threshold is reached, the Line Buffer sends the motor controller a

command to resume.

4.0 Stepper Motor Controlle r

The stepper motor controller sends a series of pulses to the stepper motor to move the pa per past the sensor (sheetfe d) or the

sensor past the paper (flatbed). T he speed at which the paper

moves relative to th e sensor, combined wi th the integr ation time

of the image sen sor, determines the effective ve rtical resolution

(Lines Per Inch, or LPI).

The stepper motor is moved forwards and bac kwards by two signals, A and B, 90° out of p hase with each other. The phas e for

the forward direction is set in Configuration Register 45.

The A and B sig nals a re ei ther s quarewav es (in Full S tep Mode ,

Figure 8), or a staircase approximation of a sine wave (in

Microstep mode, Figures 10 and 11).

A

A

1 full step = 4

microsteps

B

B

Figure 8:

Stepper Motor Waveform - Full Stepping

The LM9831 always counts stepper motor steps in units of

microsteps. A full step is equal to four microsteps. Even when the

LM9831 is in Full Step Mode, it is counting in microsteps, and will

increment the s tepper motor (gener ating a full step ) every four

microsteps.

The microstep Step Size is defined in units of time. These units of

time are pixel period s, as defined i n the horizontal pi xel counter.

In the 3 Channel Pixel Rate input mode, the pixel period is the

f

/3 (= f

ADC

modes, the pix el period is equa l to f

Size is stored i n the

/24). In the 3 Channel Line Rate and 1 channel

MCLK

Scanning Step Size

(= f

ADC

/8). The Step

MCLK

configuration register

as a 14 bit v alue. Duri ng normal operation, the stepp er motor is

advanced 1 microstep every Step Size pixel periods. The LPI can

be calculated as follows:

Where FSPI = the number of full steps required to move the

image one inch, pixel s/lin e is the numb er of pixel pe riods it tak es

to scan one horiz ontal line (equivalent to the val ue stored in the

Line End

registers), StepSize is the number of pixel peri-

ods/microstep, and X = 3 for line rate and 1 for pixel rate modes.

Whenever the stepper motor has been moving and then comes to

a stop, the LM983 1 waits for the tim e specifi ed in the H old Current Timeout register and then de -asser ts the A, B, A

, and B outputs to cut power to the motor. When the steppe r motor is not

scanning or fast-feeding (Command = 00), A, B, A

, and B are de-

asserted in all stepper modes.

There are two modes of stepper motor operation: fullstepping and

microstepping.

4.1 Full Step Mode

In Full Step Mo de th e ou tput is a pulse s tream, as s hown i n Fi gure 8. The a mplitude of th e pulses is controll ed by the out put of

23 www.national.com

Page 24

the 2 bit DAC, shown in Figure 9.

noise generated by the driver transistor turning on.

Scan Mode DAC Voltage

0.465V for number of steps specified

Starting from

a dead stop

in Kickstart Steps register (0-7). If

register is 0 there is no Kickstart

current-movement begins at 0.325V.

Scanning 0.325V

0.110V for number of steps specified

Stopped

in Hold Current Timeout register (1 -

31), 0V after time out.

Figure 9:

Full Step Current Control

4.2 Microstep Mode

Microstepping is a tec hnique of dr iving th e steppe r motor with a

staircase approx imation of a sine wave, as s hown in Figure 10.

This technique maximizes the torque of a given motor, resulting in

a higher maximum spe ed. In addition, it in creases the resol ution

of the stepper moto r. If a steppe r motor m oves 3 .6° per ful l step ,

microstepping can create pos itions insi de the 3.6° : 1.8°, 0.9° , or

0.45°, for examp le. This increases the maximu m vertic al resolution of the sc anner. Microstepping also res ults in quieter motor

movement.

A

A

1 microstep

B

DAC

A

A

DAC

B

B

Figure 11:

Stepper Motor Waveform - LM9831 Signals

Figure 12 sho ws the LM 9831’s DAC v oltages. T he peak c urrent

through the ste pper motor winding w ill be 0.465V/R

table index is incremen ted every mi crostep (StepSize pi xel peri-

SENSE

. The

ods).

Table

Index

A (B) A

(B)

DAC

Voltage

000N/A

1 1 0 0.175V

2 1 0 0.325V

3 1 0 0.425V

4 1 0 0.465V

-0 0 0 N/A

-1 0 1 0.175V

-2 0 1 0.325V

-3 0 1 0.425V

-4 0 1 0.465V

Figure 12:

Microstepping Current Control

B

Figure 10:

Bipolar Microstepping Waveform

The amplitude of the microstepped sine wave is controlled by the

output of t he stepper motor D AC (Figur e 11). The current in th e

stepper motor winding is measured as a voltage across the sense

resistor, and the transistor drive signals are pulse widt h modulated (PWM) to force the average current thr ough the winding

equal to V

PWM, and Register 57 controls the minimum time the driver is on

DAC/RSENSE

. Register 56 controls the frequen cy of th e

every period. Re gister 57 shoul d be s et as sh ort as p ossib le, th e

driver only needs to be on lon g enough to mask any transien t

4.3 Pause Behavior - Non-Reversing Mode

When the

Full Steps to Reverse When Buffer is Full

register is

0, the stepper motor sim ply stop s movin g when the P ause si gnal

is received, as shown in Figur e 13. The line of data currently

being processed (section “a” in Figure 13) will continue to be processed and stor ed in DRAM. Additional lines ma y be digitized

and stored as well, depending on the number programmed in the

Lines to Process After Pause Scan Signal

regi ster (Figure 14).

This value is different for different scanner designs and should be

empirically set to the val ue that minimizes the spatial dis tortion

created by the motor slowing down and stopping.

TR

abcd

Microstep

Pulse

Pause

Scanning

Signal

Figure 13:

Stepper Motor Stopping

24 www.national.com

Page 25

Value Ad ditional Lines to Store in DRAM

0 0(a only)

1 1 (a and b)