Page 1

N

LM9830 36-Bit Color Document Scanner

General Description

The LM9830 is a complete docu ment s canner syst em on a single IC. The LM9830 provides all the functions (CCD control, illumination control, analog front end, pixel processing function

image data buffer/SRAM controller, microstepping motor controller, and EPP parallel por t interface) necessar y to create a high

performance color scanne r. The LM9830 scans images i n 36 bit

color, and has output data formats for 36 bits, 30 bits, and 24

bits.

The only additional a ctive components requ ired are an exter nal

SRAM for data buffering and power transist ors for the stepper

motor. Parallel port pass-through requires two additional

TTL/CMOS logic ICs.

Applications

•

Color Flatbed Document Scanners

•

Color Sheetfed Document Scanners

Features

• Scans at up to 6Mpixels/s (2M RGB pixels/sec).

• Digital Pixel Processing provides 300, 200, 150, 10 0, 75, and

50 dpi horizontal resolution from 300dpi sensor, and 600, 400,

300, 200, 150, 100, 75, an d 50 dpi hor izontal resol ution from

a 600dpi sensor.

• Provides 50-600dpi vertical resolution in 1 dpi increments.

• Pixel rate error correction for gain (shading) and offset errors.

• Output formats inclu de 12 bit linear, 10 bit linear with shad ing

and offset, or 8 bit gamma corrected, all with 12 bit accuracy.

• Multiple CCD clocking rates allows matching of CCD clock to

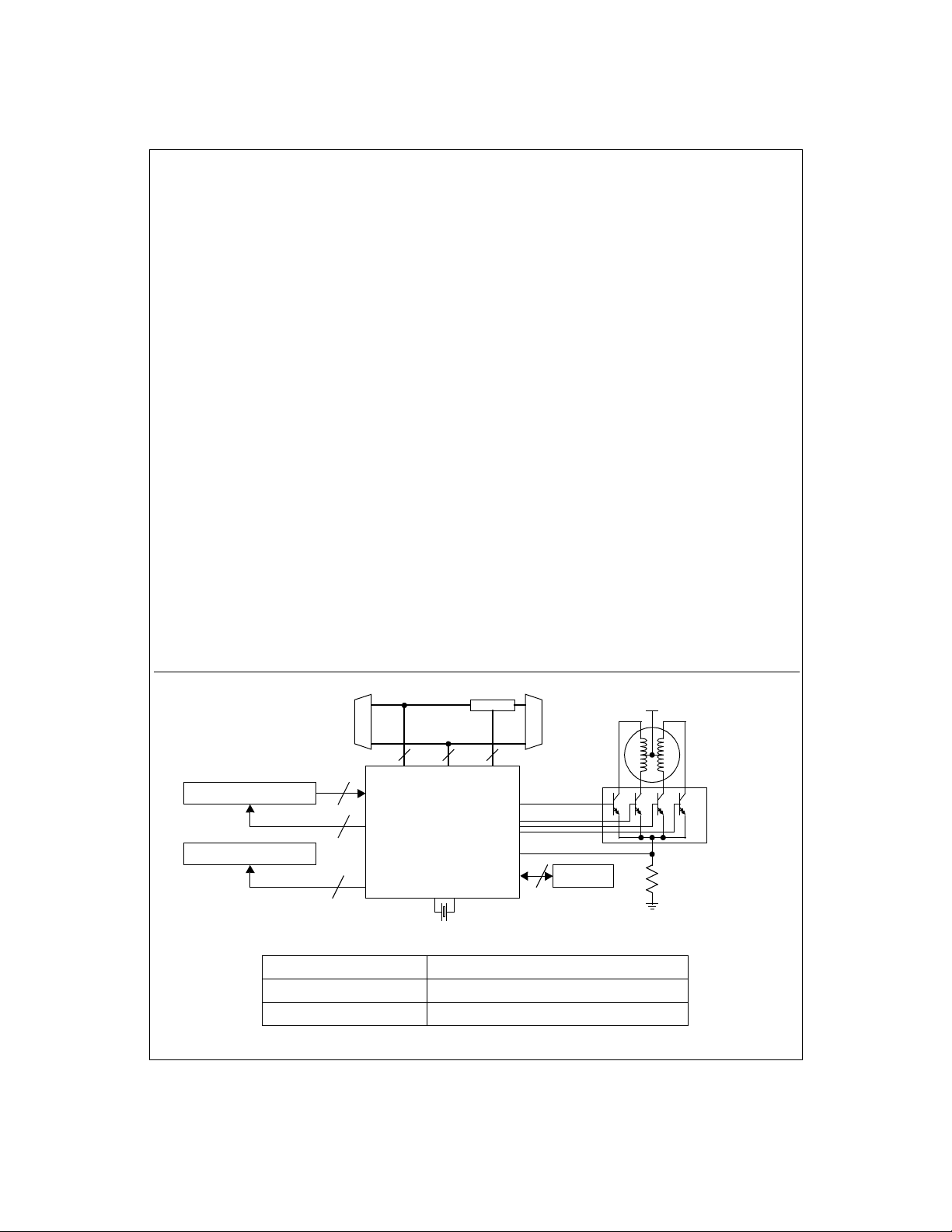

Scanner Block Diagram

To

Computer

CCD/CIS

2-6

Illumination

1-3

DB25

9 28

1-3

LM9830VJD

scan resolution and pixel depth for maximum scan speed.

• Stepper motor control tightly coupled with buffer management

to maximize data transfer efficiency.

• PWM stepper motor curr ent control allows microsteppi ng for

the price of fullstepping.

• Supports 64k, 128k, or 25 6k x8 external SRAMs.

• Parallel Port interface suppor ts EPP, PS2 (bidirection al), or

SPP (nibble) modes of operation.

• Pixel depths of 1, 2, or 4 bits are packed into bytes for faster

scans of line art and low pixel depth images.

• Supports 1 and 3 channel CIS and CCD devices.

• 3 (R, G, and B) user-programmable gamma correction tables.

• Able to transmit an arbitrary range of pixels to speed up

scanning of smaller items (business cards, etc. ) by zooming

in on a subset of CCD pixels.

• Compatible with a wide range of color linear CCDs and

Contact Image Sensors (CIS)

• Internal bandgap voltage reference.

• 100 pin TQFP package

Key Specifications

•

Analog to Digital Converter Resolution 12 Bits

•

Maximum Pixel Conversion Rate 6MHz

•

A4 Color 150dpi scan (typical, EPP Interface) <10 seconds

•

A4 Color 300dpi scan (typical, EPP Interface) <40 seconds

•

A4 Color 600dpi scan (typical, EPP Interface) <160 seconds

•

Supply Voltage +5V±10%

•

Power Dissipation (typical) 350mW

Buffer

DB25

Printer

28

To

SRAM

+24V

November 1998

Stepper

Motor

Power

Transistors

LM9830 36-Bit Color Document Scanner

Ordering Information

Commercial (0°C ≤ TA ≤ +70°C) Package

LM9830VJD VJD100A 100 Pin Thin Quad Flatpac

LM9830VJDX VJD100A 100 Pin Thin Quad Flatpac, Tape & Reel

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

©1998 National Semiconductor Corporation

1

http://www.national.com

Page 2

(

)

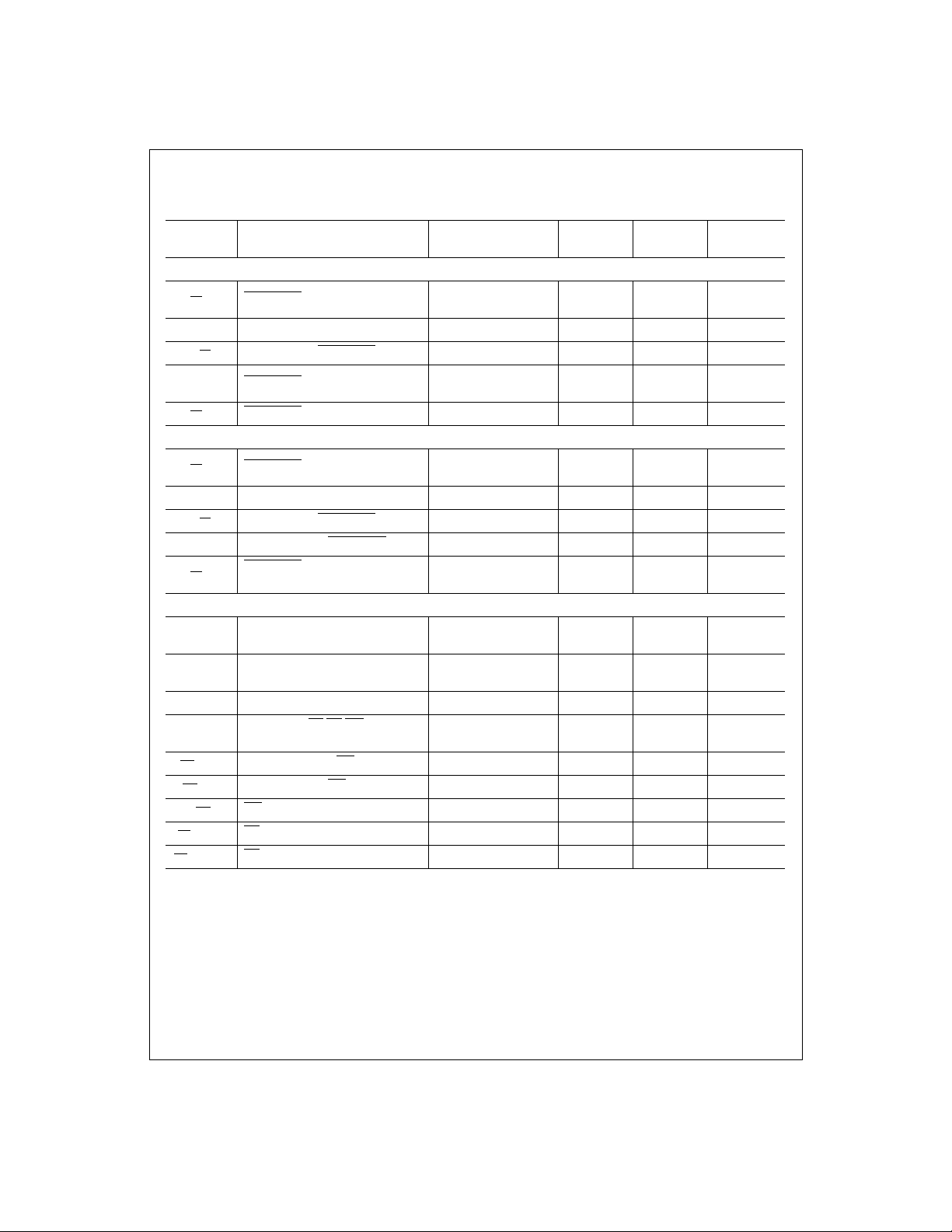

Absolute Maximum Ratings

Positive Supply V oltage (V+=VA=VD=V

With Respect to

GND=AGND=DGND=DGND

V oltage On Any Input or Output Pin -0.3V to V

=DGND

I/O

DI/O=VSRAM

SRAM

(Notes 1 & 2)

)

+

+0.3V

Input Current at any pin (Note 3) ±25mA

Package Input Current (Note 3) ±50mA

Package Dissipation at T

ESD Susceptibility (Note 5)

= 25°C (Note 4)

A

Human Body Model 1000V

Operating Ratings

Operating Temperature Range T

LM9830VJD 0°C≤T

6.5V

V

Supply Voltage +4.5V to +5.5V

A

V

Supply Voltage +4.5V to +5.5V

D

V

Supply Voltage +4.5V to +5.5V

DI/O

|V

|, |VA-V

A-VD

|V

D-VSRAM

Input Voltage Range -0.05V to V

DI/O

|, |V

DI/O-VSRAM

|, |VA-V

Soldering Information

Infrared, 10 seconds (Note 6) 235°C

Storage T emperature -65°C to +150°

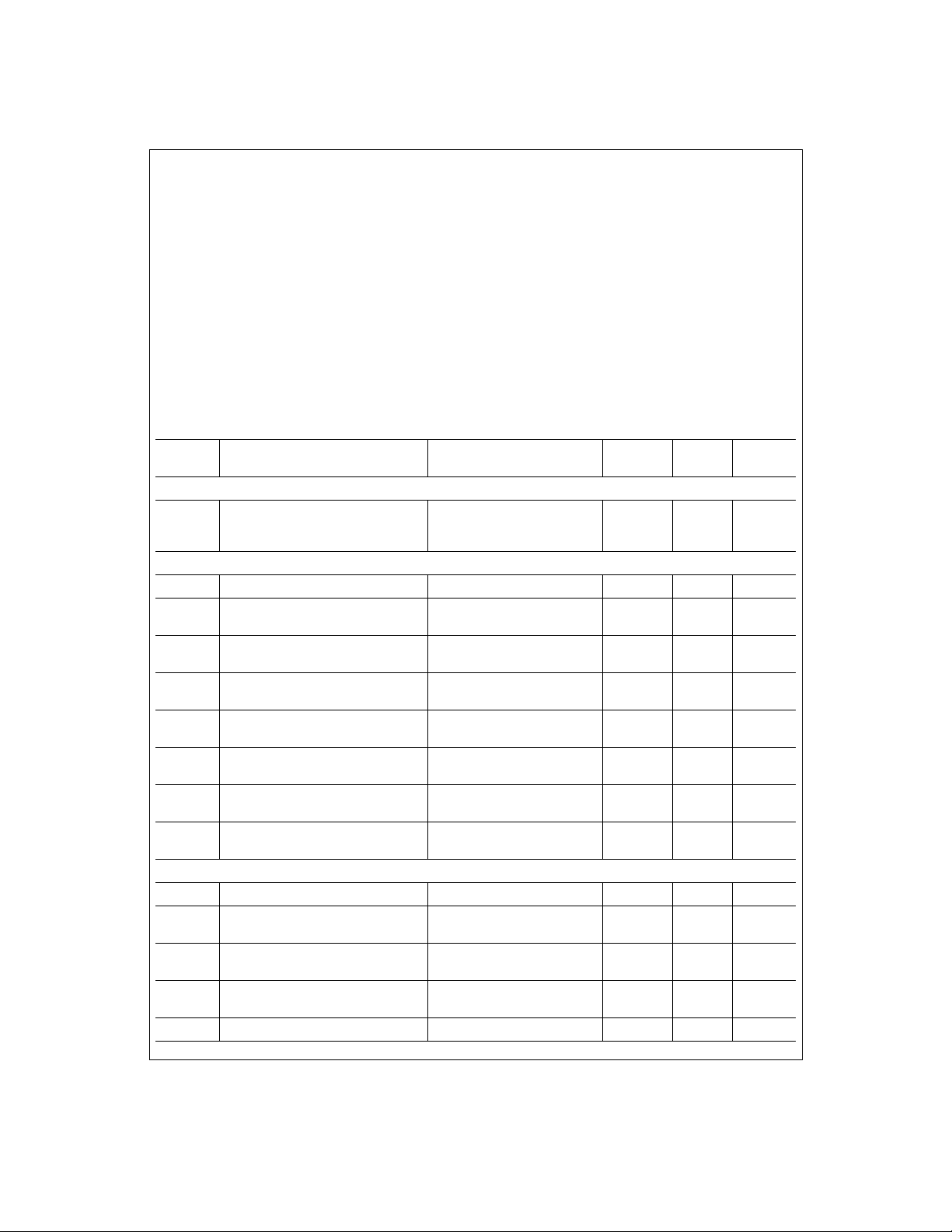

Electrical Characteristics

The following specifications apply for AGND=DGND=DGND

f

CRYSTAL IN

= 50MHz. Boldface limits apply for T

A=TJ=TMIN

Symbol Parameter Conditions

CCD/CIS Source Requirements for Full Specified Accuracy and Dynamic Range

Sensor’s Maximum Output Signal

V

OS

Amplitude before LM9830 Analog Front

PEAK

End Saturation

Full Channel Characteristics

Resolution with No Missing Codes 12 bits (min)

INL Integral Non-Linearity Error

(Note 11)

DNL Differential Non-Linearity

Analog Channel Gain Constant

C

(ADC Codes/V)

V

V

V

V

Pre-Boost Analog Channel Offset Error,

OS1

CCD Mode

Pre-Boost Analog Channel Offset Error,

OS1

CIS Mode

Pre-PGA Analog Channel Offset Error -30

OS2

Post-PGA Analog Channel Offset Error -21

OS3

Coarse Color Balance PGA Characteristics (Configuration Registers 3B, 3C, and 3D)

Monotonicity 5 bits (min)

(Minimum PGA Gain) PGA Setting = 0 0.93

G

0

(Maximum PGA Gain) PGA Setting = 31 3.05

G

31

x3 Boost Gain

Gain Error at any gain

(Note 13)

I/O

to T

=DGND

MAX

=0V, VA=VD=V

SRAM

; all other limits TA=TJ=25°C. (Notes 7, 8, & 12)

Gain = 0.933

Gain = 3.0

Gain = 9.0

Includes voltage reference

variation, gain setting = 1

x3 Boost Setting On

(bit B5 of Gain Register is set)

Note 12

(Notes 1 & 2)

|, |VD-V

SRAM

|,

DI/O=VSRAM

Typical

(Note 9)

|,

DI/O

=+5.0VDC,

Limits

(Note 10)

2.1

0.65

0.21

-1.1

+4.6

-0.5

+0.7

2048

4

12

-7

+10

-0.9

+2.0

1863

2129

-21

+34

-15

+38

-58

+8

-59

+14

.90

.96

2.98

3.15

2.99

2.86

3.08

±0.2 ±1.6 % (max)

≤

T

MIN

A

≤

100mV

+

+ 0.05V

LSB (min)

LSB (max)

LSB (min)

LSB (max)

LSB (min)

LSB (max)

mV (min)

mV (max)

mV (min)

mV (max)

mV (min)

mV (max)

mV (min)

mV (max)

V/V (min)

V/V (max)

V/V (min)

V/V (max)

V/V (min)

V/V (max)

≤

T

A

MAX

≤

+70°C

Units

(Limits)

V

V

V

2

http://www.national.com

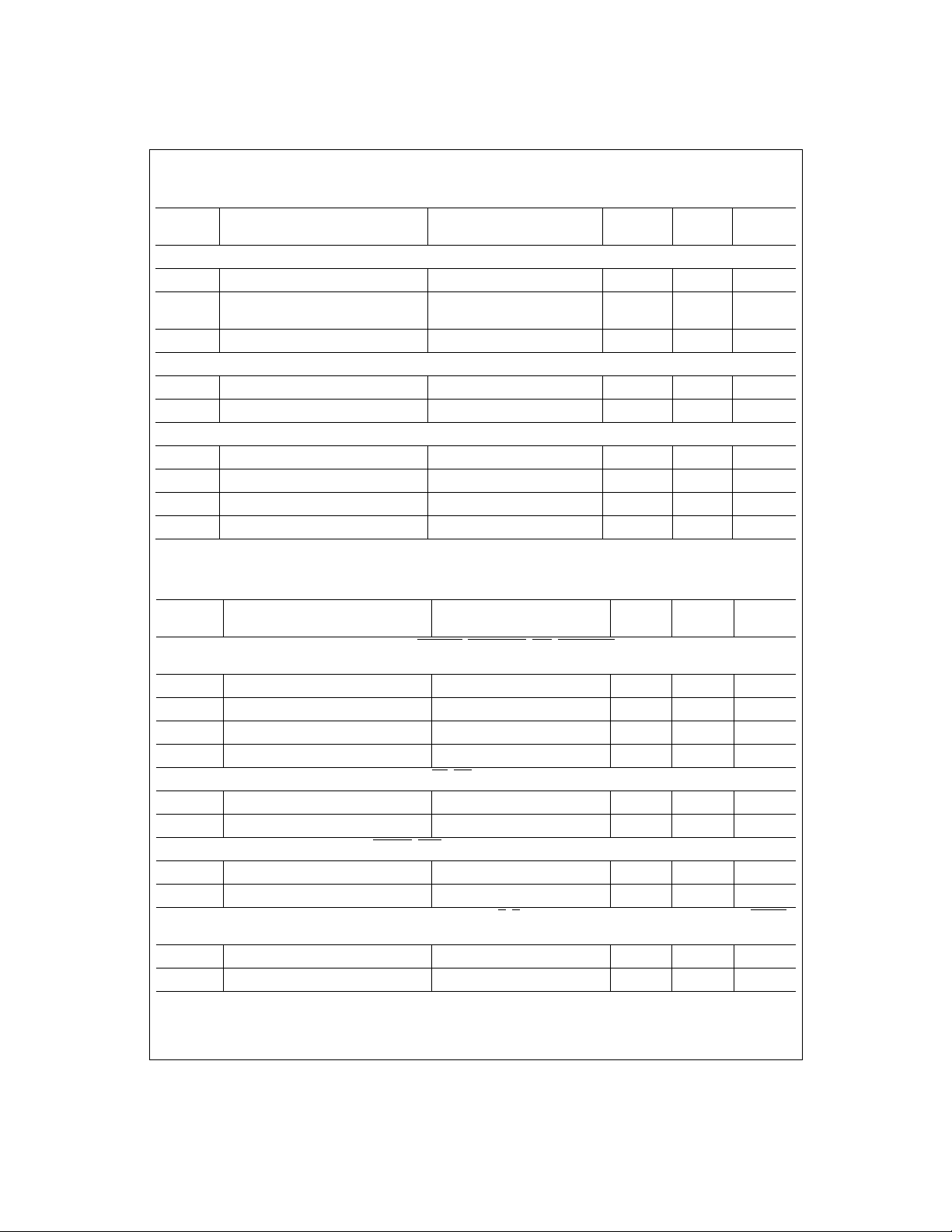

Page 3

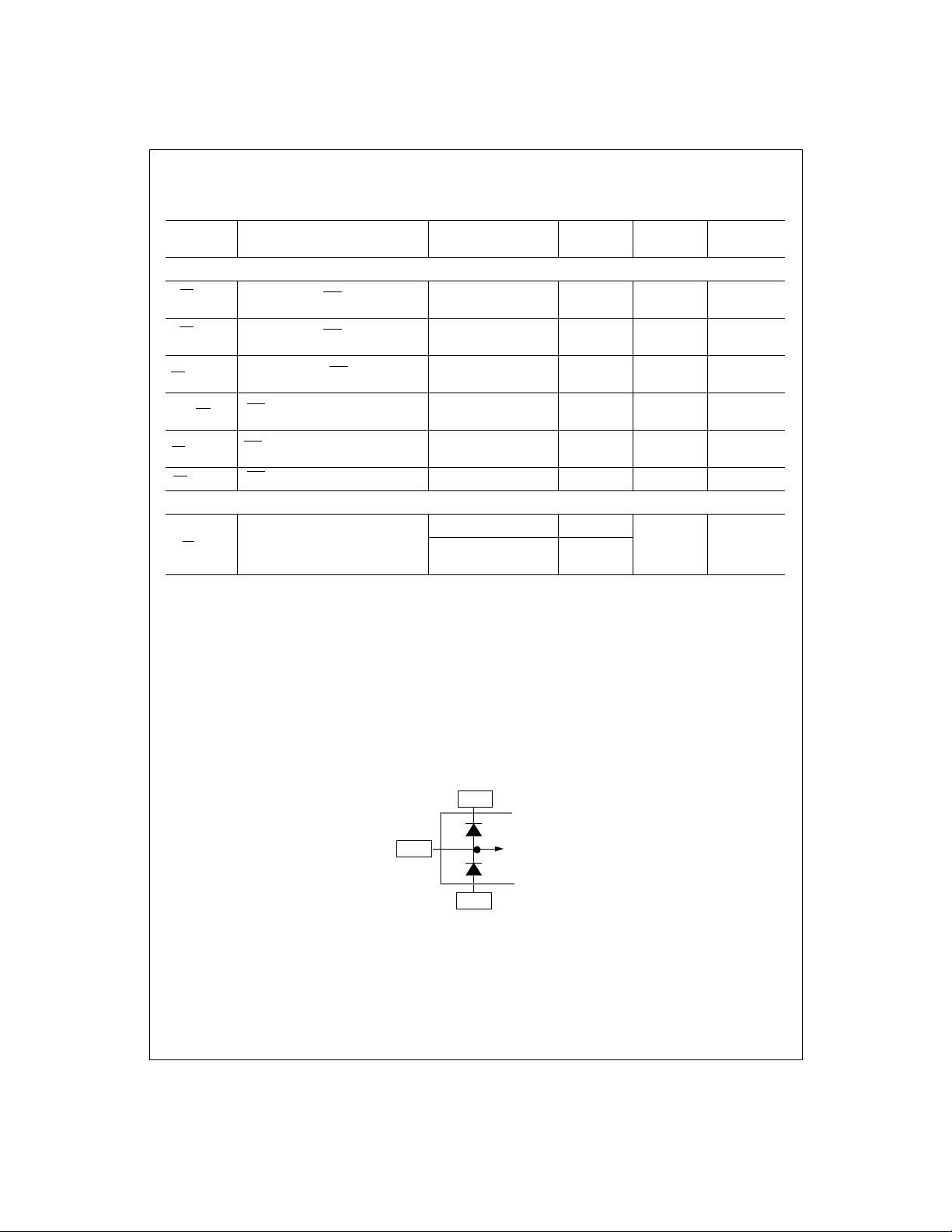

Electrical Characteristics

The following specifications apply for AGND=DGND=DGND

f

CRYSTAL IN

= 50MHz.

Boldface limits apply for T

(Continued)

A=TJ=TMIN

I/O

to T

=DGND

MAX

=0V, VA=VD=V

SRAM

; all other limits TA=TJ=25°C. (Notes 7, 8, & 12)

Symbol Parameter Conditions

Static Offset DAC Characteristics (Configuration Registers 38, 39, and 3A)

Monotonicity

Offset DAC LSB size PGA gain = 1 9.3

Offset DAC Adjustment Range PGA gain = 1 ±290

Analog Input Characteristics

Average OS

OS

R

, OSG, OSB Input Current CDS Enabled, OS = 3.5V

R

, OSG, OSB Input Current

CDS Disabled,

OS = 3.5V

Internal Voltage Reference Characteristics

V

BANDGAP

V

REF LO

V

REF MID

V

Voltage Reference Output Voltage 1.2 V

Negative Reference Output Voltage

Midpoint Reference Output Voltage

Positive Reference Output Voltage

REF HI

DC and Logic Electrical Characteristics

The following specifications apply for AGND=DGND=DGND

f

CRYSTAL IN

= 50MHz.

Boldface limits apply for T

A=TJ=TMIN

Symbol Parameter Conditions

Digital Input Characteristics for DB0-DB7, D0-D7, STROBE

#1, MISC I/O #2, CMODE

V

V

C

Logical “1” Input Voltage V

IN(1)

Logical “0” Input Voltage V

IN(0)

Input Leakage Current ±500 nA

I

IN

Input Capacitance 5 pF

IN

Digital Output Characteristics for DB0-DB7, A0-A17, RD

V

V

OUT(1)

OUT(0)

Logical “1” Output Voltage V

Logical “0” Output Voltage V

Digital Output Characteristics for D0-D7, ERROR

V

V

OUT(1)

OUT(0)

Logical “1” Output Voltage V

Logical “0” Output Voltage V

Digital Output Charact er ist ics for MI SC I/O #1 , M IS C I /O #2, A, B, A

LAMP

, LAMPG, LAMP

V

V

R

OUT(1)

OUT(0)

Logical “1” Output Voltage V

Logical “0” Output Voltage V

B

I/O

to T

=DGND

MAX

=0V, VA=VD=V

SRAM

; all other limits TA=TJ=25°C. (Notes 7 & 8)

, AUTOFEED, INIT, SELECT IN, PSENSE#1, PSENSE#2, MISC I/O

=5.5V

DI/O

=4.5V

DI/O

, WR (SRAM Interface)

DI/O

DI/O

=4.5V, I

=5.5V, I

OUT

OUT

=-4mA

=8mA

, ACK, BUSY, PE, SELECT (Parallel Port Interface)

DI/O

DI/O

=4.5V, I

=5.5V, I

OUT

OUT

=-4mA

=14mA

, B, TR1, TR2, ø1, ø2, RS, CP1, CP 2, TRI STATE, LATCH,

DI/O

DI/O

=4.5V, I

=5.5V, I

OUT

OUT

=-4mA

=8mA

DC

DC

DI/O=VSRAM

=+5.0VDC,

Typical

(Note 9)

(Note 10)

±80 nA

±24

V

-1.0 V

REF MID

V

/2.0 V

A

V

+1.0 V

REF MID

DI/O=VSRAM

=+5.0VDC,

Typical

(Note 9)

(Note 10)

Limits

6

5.8

12.7

±270

±30

Limits

2.0

0.8

2.4

0.4

2.4

0.4

2.4

0.4

Units

(Limits)

bits (min)

mV (min)

mV (max)

mV (min)

µA (max)

Units

(Limits)

V (min)

V (max)

V (min)

V (max)

V (min)

V (max)

V (min)

V (max)

3

http://www.national.com

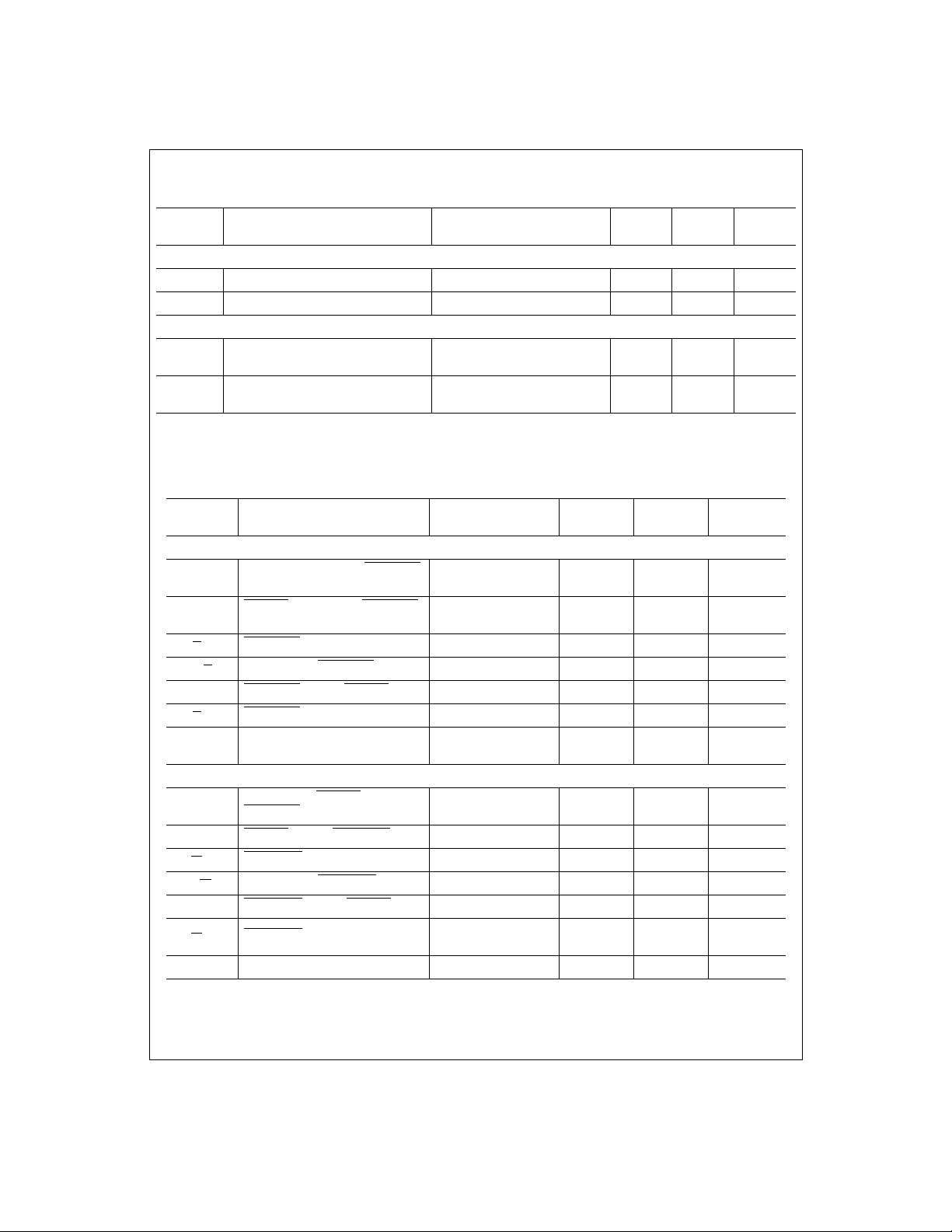

Page 4

DC and Logic Electrical Characteristics

The following specifications apply for AGND=DGND=DGND

f

CRYSTAL IN

= 50MHz.

Boldface limits apply for T

A=TJ=TMIN

Symbol Parameter Conditions

CRYSTAL IN, CRYSTAL OUT Characteristics

XTAL

XTAL

CRYSTAL OUT Bias Level (Offset) 0.8 V

OUT DC

CRYSTAL OUT Amplitude f

OUT AC

Power Supply Characteristics

Analog Supply Current

I

A

(V

pins)

A

I

D I/O

Digital I/O Supply Current

(V

, VD, and V

D I/O

SRAM

pins)

=DGND

I/O

to T

CRYSTAL

SRAM

; all other limits TA=TJ=25°C. (Notes 7 & 8)

MAX

= 50MHz 0.8 V

Operating

Standby

Operating

Standby

AC Electrical Characteristics

The following specifications apply for AGND=DGND=DGND

f

CRYSTAL IN

C

= 50MHz, MCLK DIVIDER = 1.0 (unless otherwise noted), f

(databus loading) = 20pF/pin.

L

Boldface limits apply for T

Symbol Parameter Conditions

Parallel Port Address Write (Figure 1)

t

SETUP1

t

SETUP2

t

SI-B1

t

B-SI

t

HOLD1

t

SI-B2

t

HOLD2

D0-D7 (Address) valid to SELECT IN

falling

STROBE falling edge to SELECT IN

falling

SELECT IN falling to BUSY rising 25

BUSY rising to SELECT IN rising 0

SELECT IN rising to STROBE rising -45

SELECT IN rising to BUSY falling 33

D0-D7 (Address) hold time after

BUSY falling

Parallel Port Data Write (Figure 2)

t

SETUP1

t

SETUP2

t

AF-B1

t

B-AF1

t

HOLD1

t

AF-B2

t

HOLD2

D0-D7 valid or STROBE falling to

SELECT IN

falling

STROBE falling to A UT OFEED falling -25

AUTOFEED falling to BUSY rising 34

BUSY rising to AUTOFEED rising 0

AUTOFEED rising to STROBE rising -40

AUTOFEED rising to BUSY falling

D0-D7 valid after BUSY falling -10

=DGND

I/O

A=TJ=TMIN

SRAM

MCLK

to T

All Except Dataport

Dataport

=0V, VA=VD=V

DI/O=VSRAM

=+5.0VDC,

Typical

(Note 9)

(Note 10)

64

0.75

40

5

=0V, VA=VD=V

= f

CRYSTAL IN

; all other limits TA=TJ=25°C. (Notes 7 & 8)

MAX

DI/O=VSRAM

/MCLK DIVIDER, f

Typical

(Note 9)

-60

-15

=+5.0VDC,

Limits

(Note 10)

-10

-10

40

20

-15

50

-10

-60

0

-10

-10

50

20

-10

1.5 t

16

ADC CLK

3 t

ADC CLK

35

0

Limits

83

0.95

48

6.5

ADC CLK

Units

(Limits)

mA (max)

mA (max)

mA (max)

mA (max)

= f

MCLK

Units

(Limits)

ns (min)

ns (min)

ns (max)

ns (min)

ns (min)

ns (max)

ns (min)

ns (min)

ns (min)

ns (max)

ns (min)

ns (min)

ns (max)

ns (max)

ns (min)

P-P

/8,

4

http://www.national.com

Page 5

AC Electri cal Characteristics

The following specifications apply for AGND=DGND=DGND

f

CRYSTAL IN

C

= 50MHz, MCLK DIVIDER = 1.0 (unless otherwise noted), f

(databus loading) = 20pF/pin.

L

Boldface limits apply for T

Symbol Parameter Conditions

Parallel Port 8 Bit Data Read (Figure 3)

t

AF-B3

t

EPP ACCESS

t

B-AF2

t

EPP HOLD

t

AF-B4

AUTOFEED falling to BUSY rising

D0-D7 valid before BUSY rising (Note 14) 7

BUSY rising to AUTOFEED rising 1

AUTOFEED rising to D0-D7 Tri-State 20

AUTOFEED rising to BUSY falling 3 t

Nibble Data Read (Figure 4)

t

AF-B3

t

NIB ACCESS1

t

B-AF2

t

NIB ACCESS2

t

AF-B4

AUTOFEED falling to BUSY rising

D4-D7 valid before BUSY rising 2

BUSY rising to AUTOFEED rising 1

D0-D3 valid after AUT OFEED rising 5

AUTOFEED rising edge to BUSY

falling

Microprocessor Mode (Figures 5, 6, and 7)

t

ALE SETUP

t

ALE HOLD

t

ALE

t

ALE-R/W

t

WR SETUP

t

WR HOLD

t

WR

t

RD ACCESS

t

RD TRI-STATE

D0-D7 (Address) valid before ALE

falling

D0-D7 (Address) valid after ALE

falling

ALE high time 2

ALE falling to CS/RD/WR falling (next

operation)

D0-D7 valid before WR rising 0

D0-D7 valid after WR rising 2

WR pulse width 3

RD low to D0-D7 valid 22

RD high to D0-D7 Tri-State 20

=DGND

I/O

A=TJ=TMIN

All Except Dataport

Dataport

All Except Dataport

Dataport

=0V, VA=VD=V

SRAM

= f

MCLK

CRYSTAL IN

to T

; all other limits TA=TJ=25°C. (Notes 7 & 8)

MAX

DI/O=VSRAM

/MCLK DIVIDER, f

Typical

(Note 9)

(Note 10)

25

1.5 t

ADC CLK

MCLK

3 t

4 t

25

1.5 t

ADC CLK

3 t

MCLK

3 t

4 t

0

2

=+5.0VDC,

ADC CLK

Limits

45

ADC CLK

-5

10

10

27

MCLK

45

ADC CLK

-20

10

15

MCLK

6

8

8

16

6

10

10

31

28

= f

MCLK

Units

(Limits)

ns (max)

ns (max)

ns (min)

ns (min)

ns (min)

ns (max)

ns (max)

ns (max)

ns (max)

ns (min)

ns (min)

ns (max)

ns (max)

ns (min)

ns (min)

ns (min)

ns (min)

ns (min)

ns (min)

ns (min)

ns (max)

ns (max)

/8,

5

http://www.national.com

Page 6

AC Electri cal Characteristics

The following specifications apply for AGND=DGND=DGND

f

CRYSTAL IN

C

= 50MHz, MCLK DIVIDER = 1.0 (unless otherwise noted), f

(databus loading) = 20pF/pin.

L

Boldface limits apply for T

Symbol Parameter Conditions

SRAM Write Timing (Figure 8) - Typical Values Represent Worst Case Timing for Different MCLK Frequencies

t

WR F ADDR

SETUP

t

WR R ADDR

SETUP

t

WR DATA SETUP

t

WR

t

WR ADDR HOLD

t

WR DATA HOLD

Address valid to WR falling

Address valid to WR rising

DB0-DB7 valid to WR rising

WR pulse width

WR rising to Address data change

WR rising to DB0-DB7 data Tri-State 1

SRAM Read Timing (Figure 9) - Typical Values R epresent Worst Case Timing for Different MCLK Frequenc ies

t

RD SETUP

Note 1: Absolute Max im um Ratings indicate limit s beyond w hic h damage to the device may occu r. Operating R atings indicate condit ions for which the device is functional,

but do not guarantee specific perform ance limits. For guarantee d specifications an d t est conditions, see t he Electrical Cha rac teristics. The guaranteed specifications apply

only for the test condition s list ed. Some performance c haracteristics may degrade w hen the device is not operated un der the listed test conditions.

Note 2: All voltages are measured with respect to GND=AGND=DGND=DGND

Note 3: When the input voltage (V

imum package input cur rent rating limits the numbe r of pins t hat can simultaneously sa fely exceed t he power supplies with an input current of 25mA to two.

Note 4: The ma xi mu m power dissipation mus t be derated at elevated temperatures and is dictated by T

able power dissipation at any temperature is P

is 53°C/W

.

Note 5: Human body m odel, 100pF capacitor discharged throug h a 1. 5kΩ resistor.

Note 6: See AN450 “Surface M ount ing M et hods and T heir Effect o n Pro duct Re liabilit y” o r the sect ion t itled “Surface M oun t” found in any Nation al Semic onducto r Linear

Data Book for other methods of soldering surface mount devices.

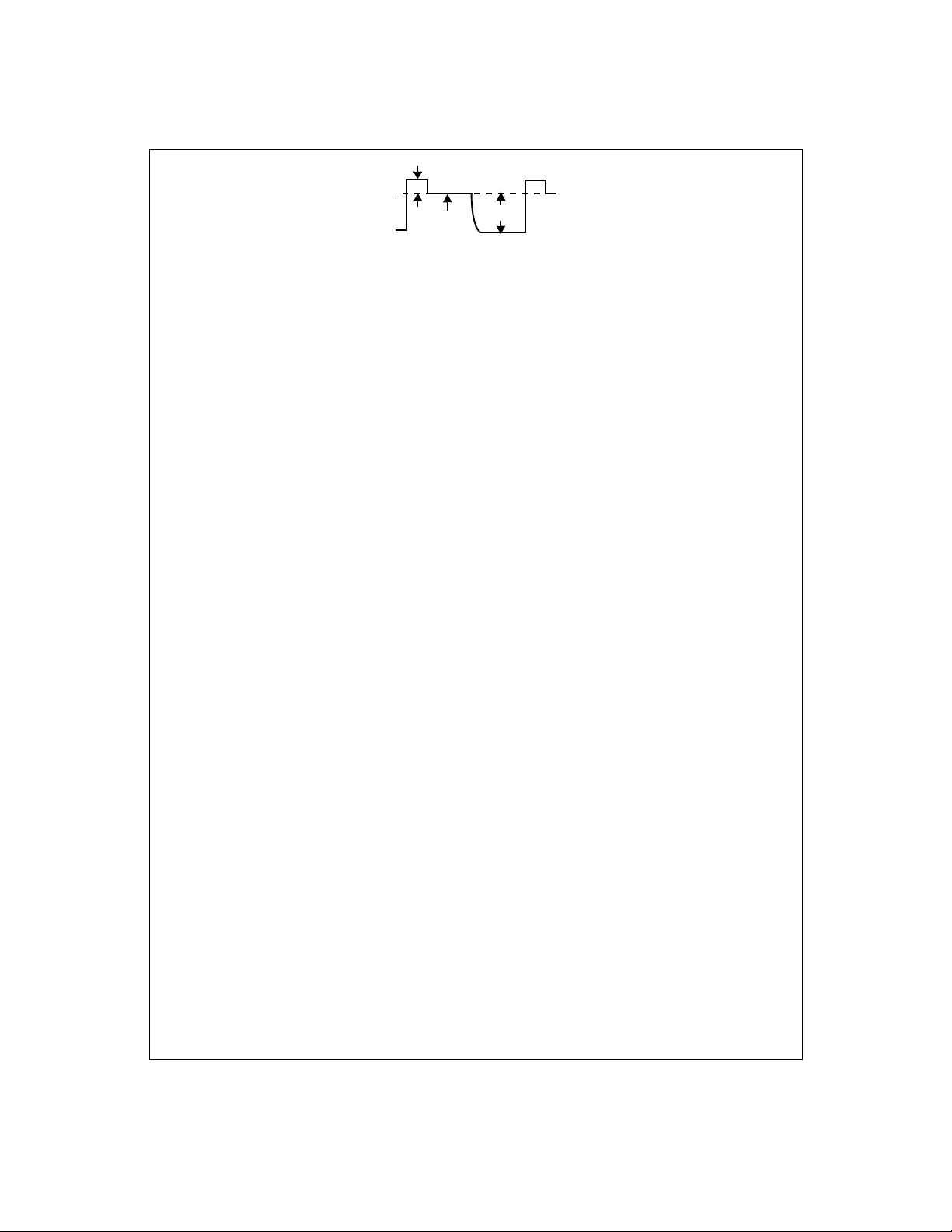

Note 7: Two diodes clamp the OS analog inputs to

impedance of the sensor, prevents damage to the LM9830 fro m tran s ients during power-up.

Address valid to DB0-DB7 data valid

) at any pin exceeds the power supplies (VIN<GND or VIN>VA or VD), the current at that pin should be limited to 25mA. The 50mA max-

IN

= (TJmax - TA) / ΘJA. TJmax = 150°C for this device. The typical thermal resistance (ΘJA) of this part when board m ounted

D

AGND

and VA as shown below. This input protection, in com bination with the external clamp cap ac it or and the output

=DGND

I/O

A=TJ=TMIN

=0V, VA=VD=V

SRAM

= f

MCLK

CRYSTAL IN

to T

; all other limits TA=TJ=25°C. (Notes 7 & 8)

MAX

4 slot mode 2 t

8 slot mode

= 25MHz)

(f

MCLK

I/O

=DGND

=0V, unless otherwis e s pec ified.

SRAM

VA

max, ΘJA and the ambient temperat ure, TA. The maximum allow-

J

DI/O=VSRAM

/MCLK DIVIDER, f

Typical

(Note 9)

0.5 t

MCLK

- 7ns

1.5 t

MCLK

- 9ns

1 t

MCLK

- 9ns

1 t

MCLK

- 5ns

0.33 t

MCLK

- 4ns

- 12ns

MCLK

1 t

- 12ns

MCLK

=+5.0VDC,

Limits

(Note 10)

3

21

11

15

2

4

28

ADC CLK

= f

MCLK

Units

(Limits)

ns (min)

ns (min)

ns (min)

ns (min)

ns (min)

ns (max)

ns (max)

/8,

AGND

6

T o In te rnal

Circuitry

is defined as the peak CCD pixel output voltage for

WHITE

of the reset feedthrough pulse. The maximum

(due to PRNU, light so urce intensity var iation, optics, et c.) that the

WHITE

REF

http://www.national.com

OS Input

Note 8: For best performanc e, it is required that all supply pin s be powered from the same power su pply with separate bypass capacitors at each supply pin.

Note 9: Typicals are at T

Note 10: Tested limits are guaranteed to Natio nal's AOQL (Average Outgoing Quality Level).

Note 11: Integral linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line that best fits the actual transfer function o f th e ADC.

Note 12: V

a white (full scale) image with respect to the reference level, V

correctable range of pixel-to-pixel V

is defined as the CCD OS voltage for the reference period following the reset feedthrough pulse. V

REF

J=TA

=25°C, f

= 50MHz, and represent most likely parametric norm.

CRYSTAL IN

is defined as the peak positive deviation above V

. V

REF

variation is define d as the maximu m variation in V

WHITE

RFT

Page 7

LM9830 can correct for using its internal PGA.

CCD Output Signal

V

RFT

V

Note 13: PGA Gain Error is the maximum difference between the measured gain for any PGA code and the ideal gain calculated by using the formula

V

Gain

--- -

PGA

V

Note 14: Interaction w it h an actual parallel po rt load (C

For this reason, it is recomme nded that the parallel port be driven to 0x00h by the PC w hen not in the reverse transfer phase. When readin g c oefficient data from regis t er 6

PGA code

G0X

-------------- ------------ -+=XG

where .

32

32

------=

–()

31G0

31

> 200pF) can increase data settling ti m e by as m uc h as 100ns if the para llel port databus is precharged high.

LOAD

V

REF

WHITE

(register 3 = 00000 XX1 bina r y), the EP P hands hakin g generat ed by the hos t PC may be faste r than the data ca n settle. For this reason it is recommended that software

handshaking (“PS2” mode) be used when verifying coefficient data.

7

http://www.national.com

Page 8

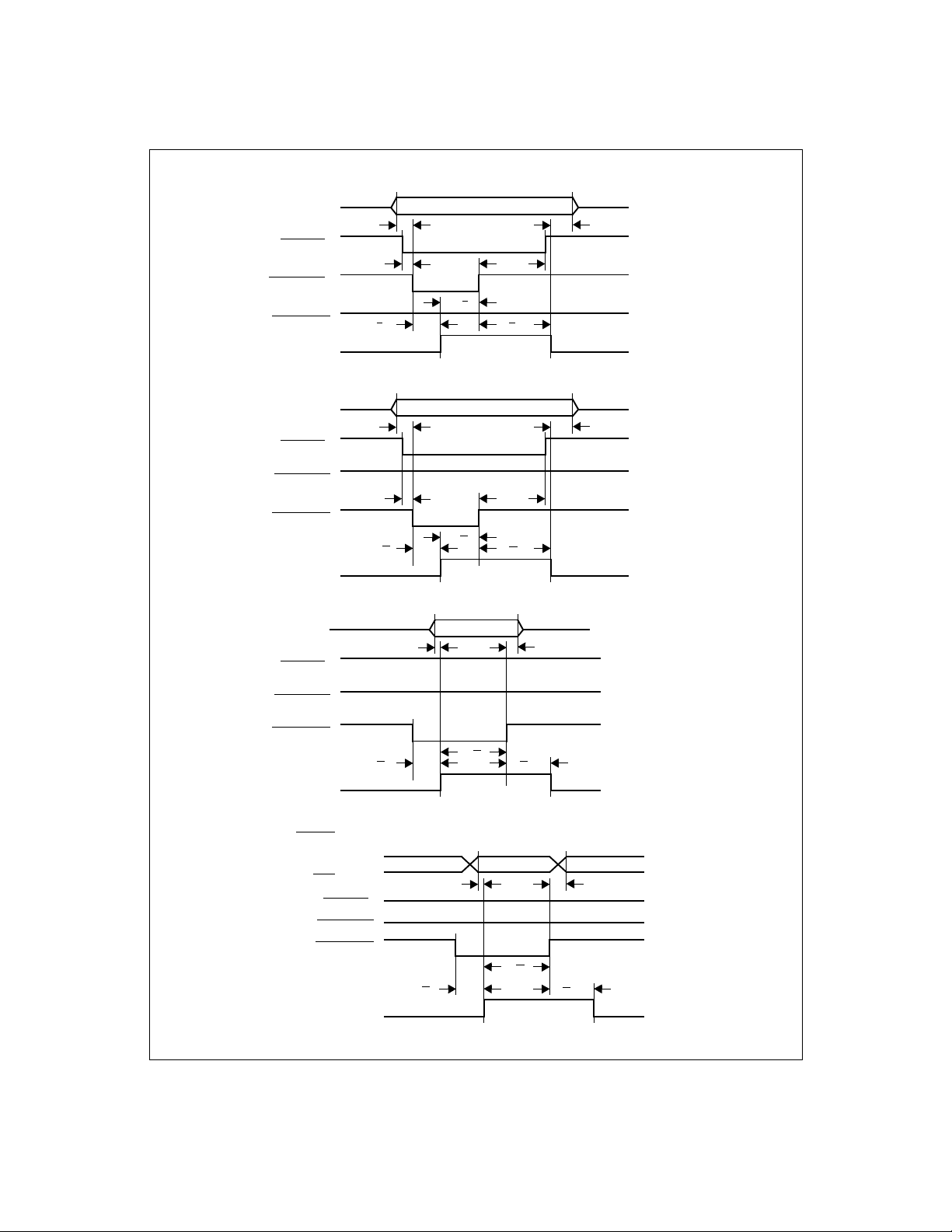

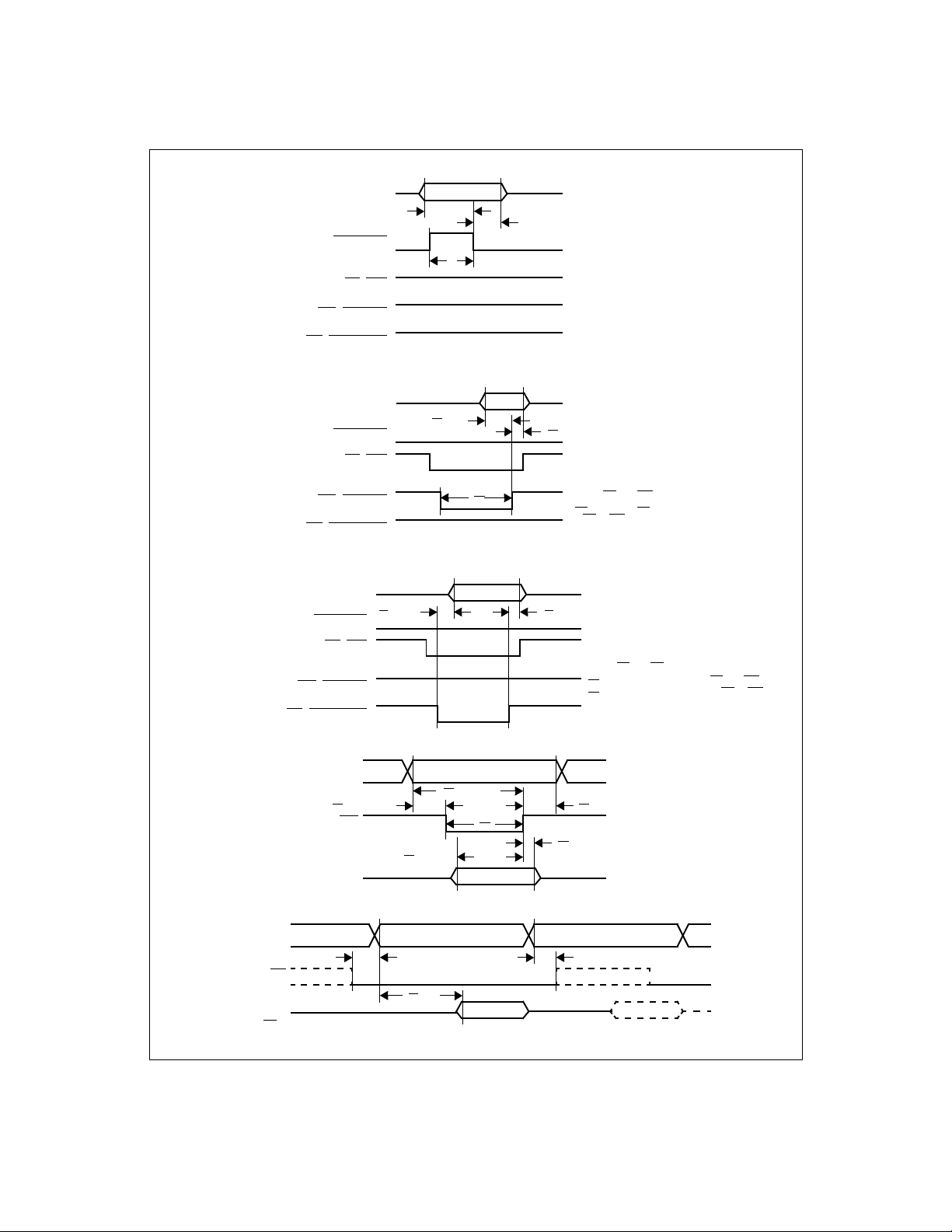

Timing Diagrams

D0 - D7

STROBE

SELECT IN

AUTOFEED

BUSY

D0 - D7

STROBE

SELECT IN

AUTOFEED

BUSY

D0 - D7

STROBE

Address

t

SETUP1

t

SETUP2

t

B-SI

t

SI-B1

Figure 1: Parallel Port Address Write

Data

t

SETUP1

t

SETUP2

t

t

AF-B1

B-AF1

Figure 2: Parallel Port Data Write

Data

t

EPP ACCESS

t

HOLD1

t

HOLD1

t

SI-B2

t

AF-B2

t

EPP HOLD

t

HOLD2

t

HOLD2

SELECT IN

AUTOFEED

BUSY

ERROR (D0, D4)

SELECT (D1, D5)

PE (D2, D6)

ACK

STROBE

SELECT IN

AUTOFEED

t

t

AF-B3

B-AF2

Figure 3: Parallel Port 8 Bit Data Read

(D3, D7)

t

NIB ACCESS1

t

AF-B3

BUSY

Figure 4: Parallel Port Nibble Data Read

8

t

AF-B4

D7-D4 D3-D0

t

NIB ACCESS2

t

B-AF2

t

AF-B4

http://www.national.com

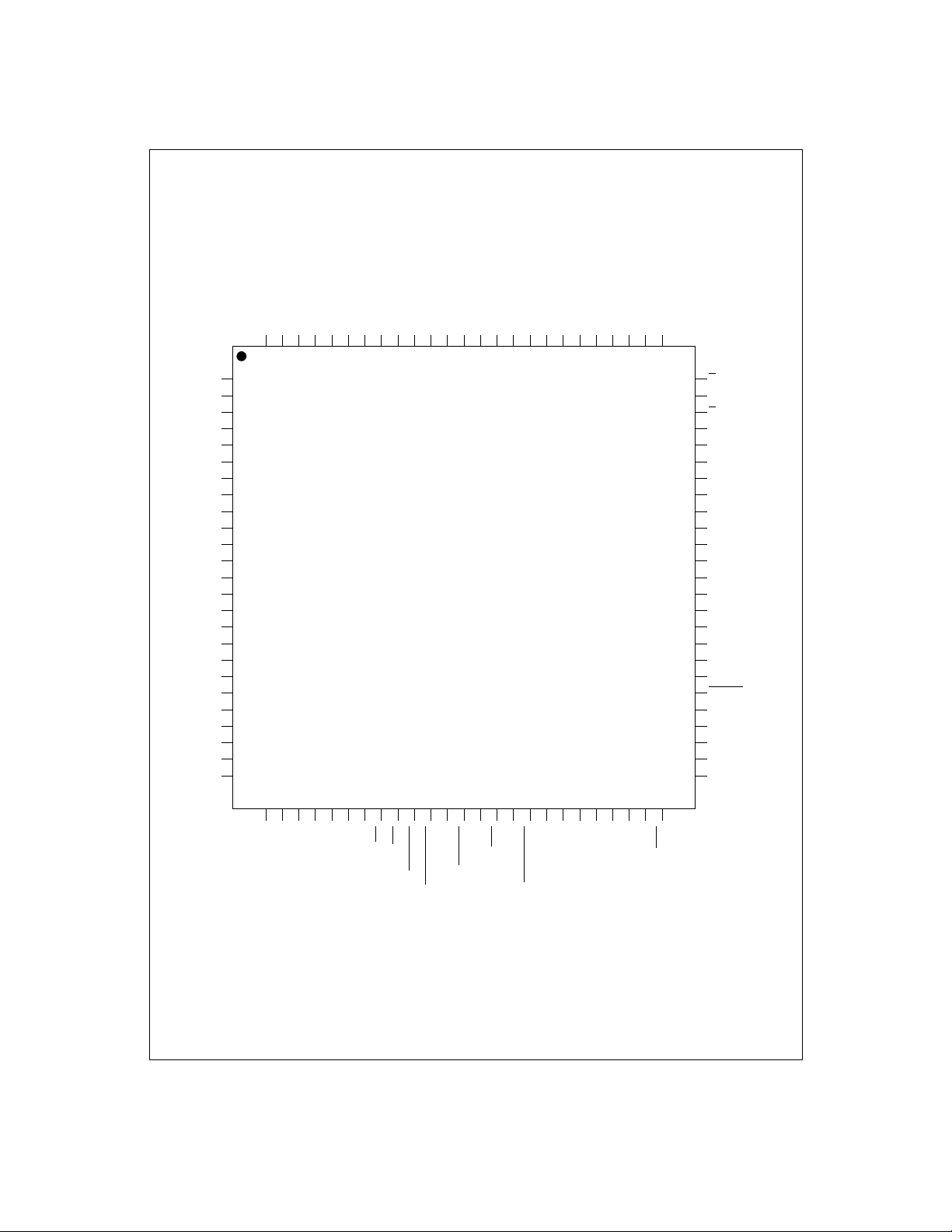

Page 9

D0 - D7

h

ALE (SELECTIN)

CS

(INIT)

WR (STROBE)

RD (AUTOFEED)

Address

t

ALE SETUP

t

ALE

t

ALE HOLD

Figure 5: µP Mode Address Latch

D0 - D7

ALE (SELECTIN)

CS (INIT)

WR (STROBE)

RD (AUTOFEED)

D0 - D7

ALE (SELECTIN)

(INIT)

CS

WR (STROBE)

RD (AUTOFEED)

A0-A17

t

WR F ADDR SETUP

WR

DB0-DB7

t

WR SETUP

Figure 6: µP Mode Write

t

RD ACCESS

Figure 7: µP Mode R ead

t

WR R ADDR SETUP

t

WR DATA SETUP

Figure 8: SRAM Write

Data

t

WR

Data

Address

t

WR

Data

t

WR HOLD

NOTE: CS and WR are ORed together.

t

and t

WR SETUP

of CS or WR, whichever goes high first.

t

RD TRI-STATE

WR HOLD

NOTE: CS and RD are ORed together.

t

begins when both CS and WR go low.

RD ACCESS

t

t

WR ADDR HOLD

t

WR DATA HOLD

RD TRI-STATE

begins when either CS or WR go hig

refer to the first rising edge

A0-A17

0.5MCLK 0.5MCLK

Address

RD

t

DB0-DB7

RD SETUP

Data

Note: RD will stay low during consecutive read operations.

Figure 9: SRAM Read

9

Address

Data

http://www.national.com

Page 10

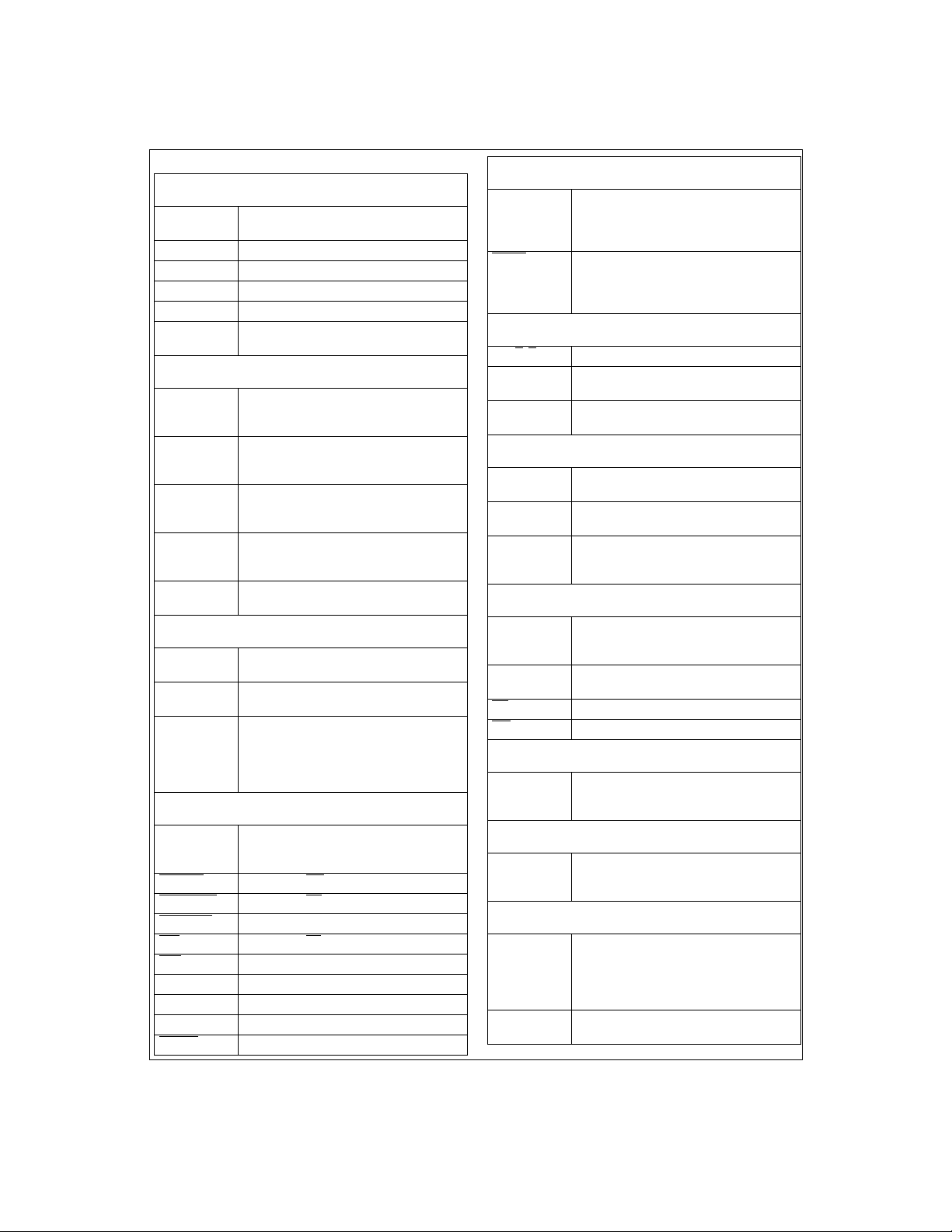

Connection Diagram

GND

V

DGND

V

DGND

A0

A1

A2

A3

A4

D I/O

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

D I/O

A16

A17

DB0

DB1

DB2

CP2

CP1RSø2ø1TR2

VAOSBV

REF HI SENSEVREF HI FORCE

TR1

AGND

OSGV

REF MID SENSEVREF MID FORCE

OSRV

REF LO SENSEVREF LO FORCEVBANDGAP

AGND

VASENSE

SENSEBSENSEATEST

100999897969594939291908988878685848382818079787776

1

2

3

4

5

6

7

I/O

8

9

10

11

12

13

14

LM9830VJD

15

16

17

18

19

20

I/O

21

22

23

24

25

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

B

B

A

A

CLK_SEL

DGND

I/O

V

D I/O

CMODE

LAMP

B

LAMP

G

LAMP

R

MISC I/O #2

MISC I/O #1

PSENSE #2

PSENSE #1

DGND

SRAM

V

SRAM

CRYSTAL OUT

CRYSTAL IN

LATCH

NC

TRISTATE

SELECT

PE

BUSY

26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

DB3

DB4

DB5

DB6

DB7

V

D

RD

DGND

WR

STROBE

AUTOFEED

D0

ERROR

10

D1

D3

V

D I/O

I/O

D4D5D6

D7

ACK

D2

INIT

DGND

SELECT IN

http://www.national.com

Page 11

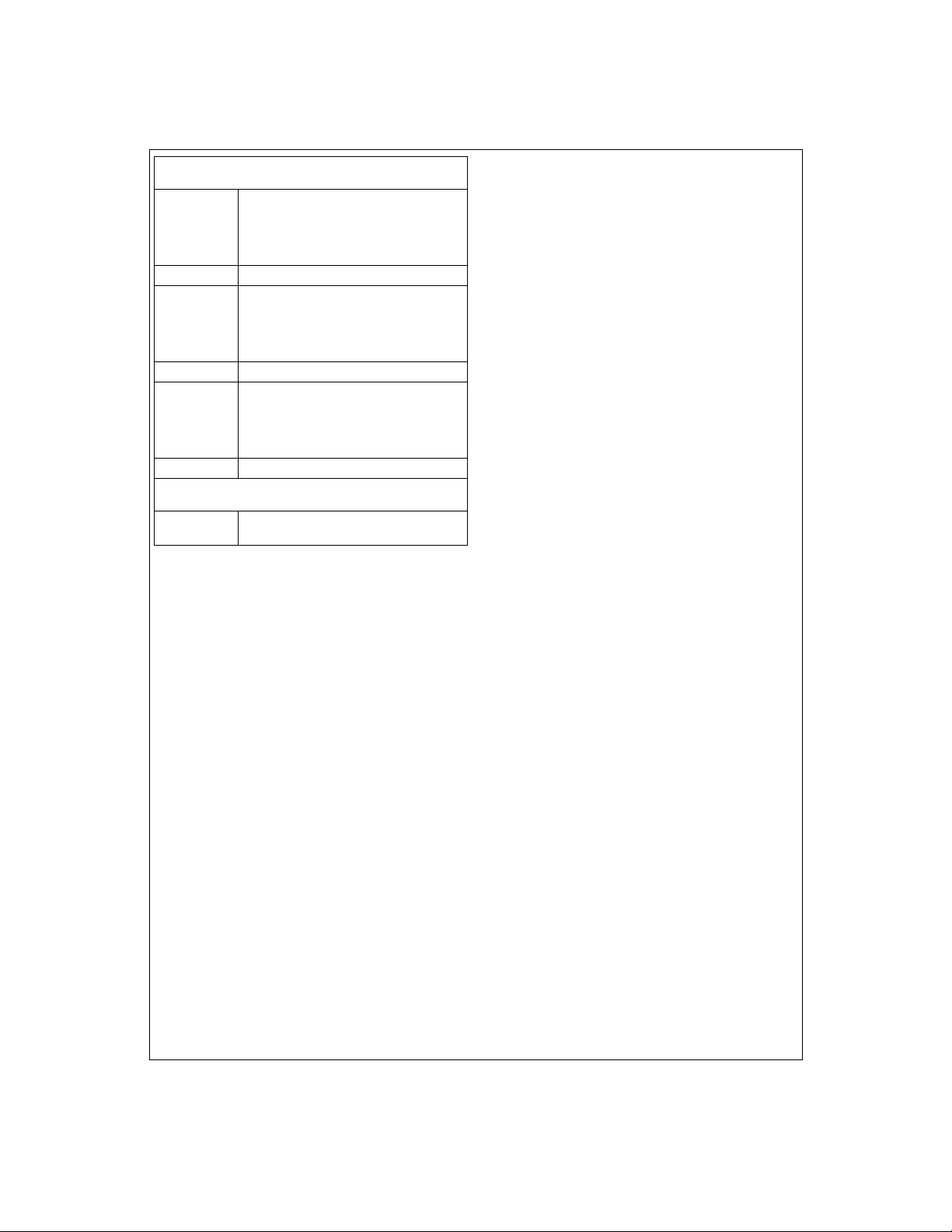

Pin Descriptions

CCD Driver Signals

ø1 Digital Output. CCD/ CIS clock signal, phase

ø2 Digital Output. CCD clock signal, phase 2.

RS Digital Output. Reset pulse for the CCD.

CP1 Digital Output. Clamp pulse for the CCD.

CP2 Digital Output. Clamp pulse for the CCD.

TR1, TR2 Digital Outputs. Transfer pulses for the

1.

CCD(CIS).

Analog I/O

OSR, OSG,

OS

B

V

REF LO FORCE,

V

REF LO SENSE

V

REF MID FORCE ,

V

REF MID SENSE

V

REF HI FORCE,

V

REF HI SENSE

V

BANDGAP

Analog Inputs. These in puts (for Red, Green,

and Blue) shou ld be tied to th e sensor’s output signal through DC blocking capacitors.

Analog Output/Input . Conne ct V

V

monolithic capacit or.

Analog Output/Input. Connect V

to V

0.05µF monolithic capacitor.

Analog Output/Inp ut. Connect V

V

monolithic capacit or.

Analog Output. Bypass to AGND with a

0.05µF monolithic capacitor.

and bypass to AGND with a 0.05µF

REF LO IN

REF MID IN

REF HI IN

and bypass to AGND with a

and bypass to AGND with a 0.05µF

REF LO OUT

REF MID OUT

REF HI OUT

General Digital I/O

CRYSTAL IN Digital Input. This is the 50MHz (typical) mas-

CRYSTAL OUT Digital Output. Used with CRYSTAL IN and an

CLK_SEL Digital Input. Should be tied to DGND for

ter system clock.

external crystal to form a crystal oscillator.

operation with an external cry stal. To use an

external TTL or CMOS clock source, tie

CLK_SEL to V

CRYSTAL OUT pin.

and driv e th e c lock into t h e

D I/O

PC I/O

D0 (LSB) -D7

(MSB)

STROBE

AUTOFEED

SELECTIN

INIT

ACK

BUSY Digital Output.

PE Digital Output.

SELECT Digital Output.

ERROR

Digital Inputs/Outputs. This is the 8 bit d ata

path between the LM9830 and the host computer.

Digital Input. WR signal in µP Mode.

Digital Input. RD signal in µP Mode.

Digital Input. ALE signal in µP Mode.

Digital Input. CS signal in µP Mode.

Digital Output.

Digital Output.

Printer Passthrough

TRISTATE Digital Output. Low when in printer

LATCH

passthrough mode, high when the LM9830 is

active. Low when no power is app lied to the

LM9830.

Digital Output. High when in printer

passthrough mode, low when th e LM9830 is

active. Tri-state when no power is applied to

the LM9830.

Stepper Motor I/O

A, B, A, B Digital Outputs. Pulses to stepper motor.

,

Analog Inputs. Current sensing for PWM

winding current control.

Analog Input. Ground sense input for PWM

winding current control.

Scanner Support I/O

Digital Inputs. Programmable, used for sensing paper, front panel switches, etc.

Digital Inputs/Outputs. Programmable, used

for front panel switches, status LEDs, etc.

Digital Outputs. Used to control R, G, and B

LEDs of single output CIS, as well as bright-

B

ness of CCFL.

to

to

SENSE

A

SENSE

B

SENSE

GND

PSense #1,

PSense #2

Misc I/O #1,

Misc I/O #2

,

LAMP

R

LAMP

, LAMP

G

External RAM I/O

DB0 (LSB) DB7 (MSB)

A0-A17 Digital Outputs. Add ress pins for up to 256k

RD

WR

Digital Inputs/Outputs. This is the 8 bit data

path between the external RAM and the

LM9830.

bytes external RAM.

Digital Output. Read signal to external RAM.

Digital Output. Write signal to external RAM.

Communication Mode

CMODE Digital Input. Tie to DGND to operate in paral-

lel port mode, or to V

processor c ompatible mode.

D I/O

Test

TEST Analog Output. This pin can be used to view

the Sample Signal, Sample Reference, and

Clamp Signals.

Analog Power Supplies

V

A

AGND This is the ground ret urn for the analog su p-

This is the positive supply pin for the analog

supply. It should be connected to a voltage

source of +5V and bypassed to AGND with a

0.1µF monolithic c apacitor in parallel with a

10µF tantalum capacitor.

ply.

to operate in micro-

11

http://www.national.com

Page 12

Digital Power Supplies

V

D

DGND This is the ground return for V

V

D I/O

DGND

I/O

V

SRAM

DGND

SRAM

This is the positive supply pin for the

LM9830’s digital circuitry. It should be connected to a voltage source of +5V and

bypassed to DGND with a 0.1µF monolithic

capacitor.

.

D

This is the positive supply pin for the

LM9830’s external I/O. It should be connected

to a +5V voltage source and bypassed to the

closest DGND

capacitor.

This is the ground return for V

pin with a 0.1µF mo nolithic

I/O

.

D I/O

This is the positive supply pin for the

LM9830’s internal SRAM sense amplifiers

and crystal o scillator. It should be connected

to a +5V voltage source and bypassed to

DGND

This is the ground return for V

with a 0.1µF monolithic capacitor.

SRAM

D SRAM

.

Other

NC Do Not Connect. This pin should be left float-

ing.

12

http://www.national.com

Page 13

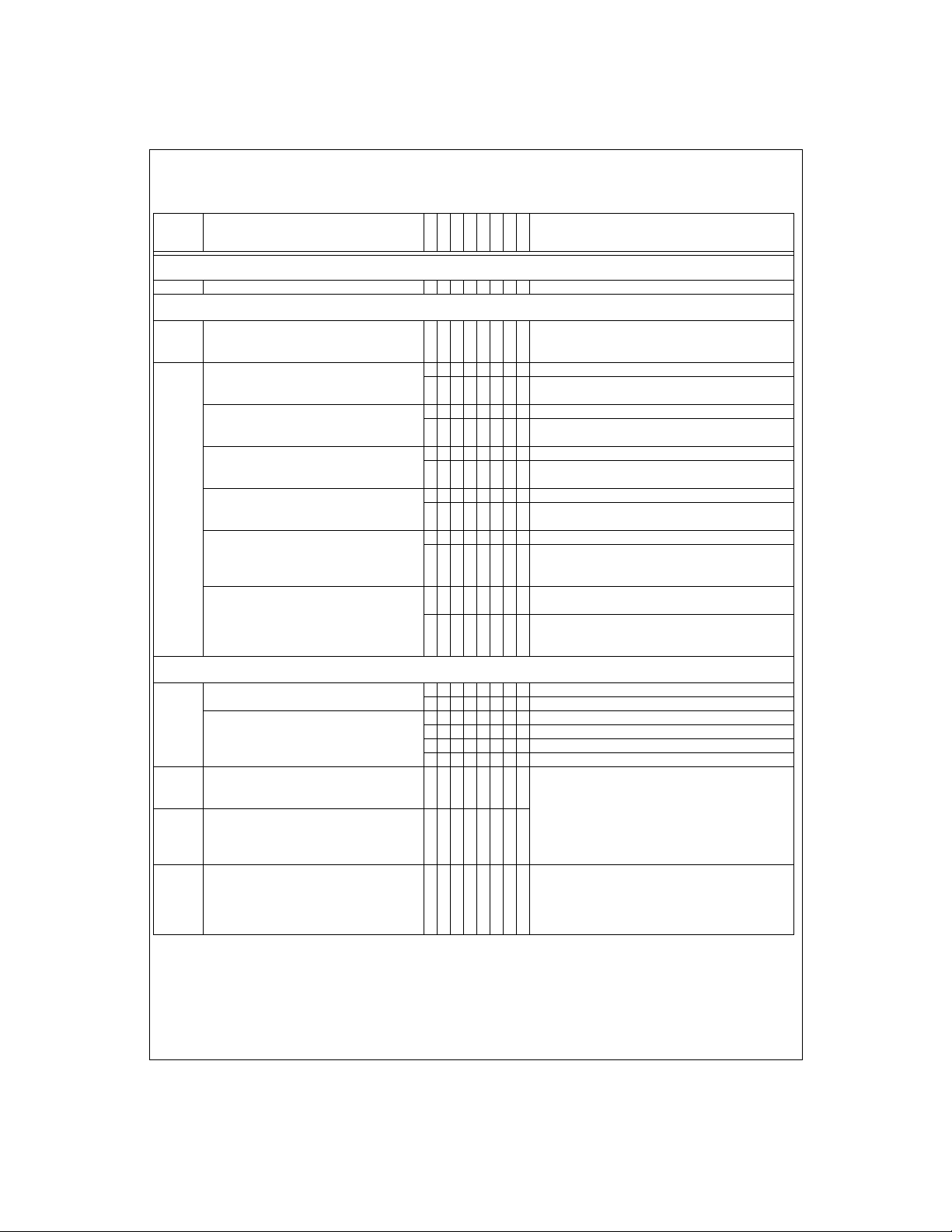

LM9830 Register Listing

(Registers in bold boxes are reset to t hat value on power-up. All register addre sses are in hexadec imal. All other numbers

are decimal unless otherwi se noted.)

Address Function

IMAGE BUFFER (READ ONLY)

00 Pixel (Image) Data nnnnnnnnOne byte of image data.

STATUS REGISTERS (READ ONLY)

01 Image Data Available In Buffer nnnnnnnn

Paper Sensor #1 State

If this input is edge sensitive, reading this

Status Register will clear it.

Paper Sensor #2 State

If this input is edge sensitive, reading this

Status Register will clear it.

Misc I/O #1 State

If this input is edge sensitive, reading this

Status Register will clear it.

Misc I/O #2 State

02

If this input is edge sensitive, reading this

Status Register will clear it.

Pause

This bit indicates whether or not the scanner

is currently paused due to a buffer full

condition.

Powerdrop

This bit is used to detect if the power supply

has dipped below 3V since the last time this

register was read. Reading this register

clears this bit.

DATAPORT REGISTERS

DataPort Target

DataPort Target Color (Note: If using 1

03

Channel Mode A, the color for the gamma

table is selected by register 26, bits 3 and 4,

not this register)

04 DataPort Address - MSB

05 DataPort Address - LSB aaaaaaaa

06 DataPort nnnnnnnn

D7D6D5D4D3D2D1D

0Normal State

1

0

1

R

/Waaaaa

0

n kbytes of image data available

(always read this register twice to make sure its value

was not changing while it was being read)

0False

1True

0False

1True

0False

1True

0False

1True

The scanner entered the pause/reverse cycle during

the processing of this line.

False: Power has not dipped below 3V since the last

time this register was read

True: Power

the register was read

0 Gamma Lookup Table

1 Offset/Gain Coefficient Data (external SRAM)

00 Red

01 Green

10 Blue

11 N/A

Address of location to be read/written to.

a = 0 to 1023 for gamma tables,

0 to 2729 for Offset/Gain Coefficient Data (300dpi),

0 to 5459 for Offset/Gain Coefficient Data (600dpi).

Addresses greater than these are illegal.

Bit D5 of register 4 indicates whether next operation

will be a Read (D5=1) or a Write (D5=0)

Data to be read from or written to the address of the

currently selected Dataport Target. The DataPort

Address is automatically incremented whenever one

(Gamma) or two (Offset/Gain Coefficient Data) bytes

are read from or written to this register.

has

dipped below 3V since the last time

Value

13

http://www.national.com

Page 14

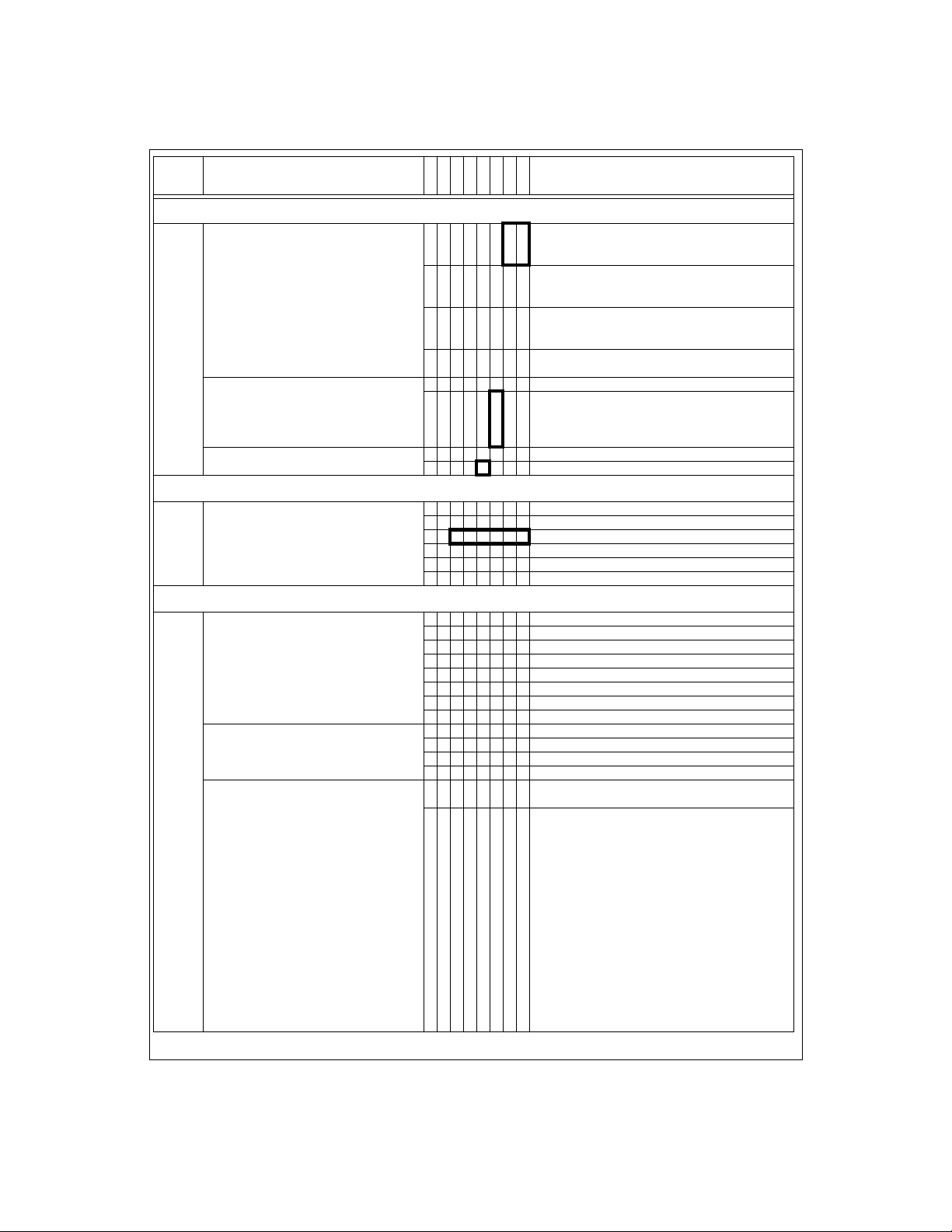

Address Function

COMMAND REGISTER

Command Register

This regis t er i s use d t o s tart an d e nd a s ca n.

It is also used to home the sensor in a

flatbed scanner or eject the image in a

sheetfed scanner.

07

Standby

When this bit is set the crystal oscillator

continues to run but all internal clock signals

are frozen. The analog circuitry is turned off

to reduce power consumption.

Reset

(Host mu st write a 1 then a 0 to enter

and exi t the reset state)

MASTER CLOCK DIVIDER

MCLK Divider

This register sets the master clock frequency

for the entire scanner.

08

f

MCLK

f

ADC

= f

= f

CRYSTAL

MCLK

/MCLK_Divider

/8

HORIZONT AL RESOLUTION AND DATAMODE SETTINGS

Horizontal DPI Divider

This register determines the horizontal

resolution of the scan.

Scan resolution = Optical resolution divided

by the Horizontal_DPI_Divider.

Pixel Packing

This register determines how many bits in

each byte of data are transmitted to the host

when DataMode = 0

DataMode

When DataMode = 0, the pixel data is fully

processed, going through the Offset,

09

Shading, Horizontal DPI Adjust, Gamma,

and Pixel Packing blocks.

D7D6D5D4D3D2D1D

0

Idle - Stops motor (A, B, A

completes current line of data (if scanning).

00

Note: CCD/CIS clocks continue clocking.

High Speed Forward - Moves motor forward at a

01

speed determined by the Fast Feed Step Size

(registers 48 and 49).

High Speed Reverse - Moves motor backward at a

10

speed determined by the Fast Feed Step Size

(registers 48 and 49).

Start Scan - Resets the LM9830’s data pointers and

11

starts an image scan.

0 Operating

1 Low Power Standby Mode

0 Normal Operation

1 Resets the LM9830

000000÷1.0

000001÷1.5

000110÷4

aaaaaa÷ ((aaaaaa/2)+1)

111110÷32.0

111111÷32.5

000÷1

001÷1.5

010÷2

011÷3

100÷4

101÷6

110÷8

111÷12

0 0 1 bit/pixel (1 bit grayscale/3 bit color)

0 1 2 bits/pixel (2 bit grayscale/6 bit color)

1 0 4 bits/pixel (4 bit grayscale/12 bit color)

1 1 8 bits/pixel (8 bit grayscale/24 bit color)

0

1, 2, 4, or 8 bit image data,

as determined by the Pixel Size setting.

Value

, B = 0),

When DataMode = 1, 10 bit data is extracted

following the Horizontal DPI Adjust stage.

Gamma and any other post processing must

be done by the host.

When DataMode = 1, Horizontal DPI Adjust

= 0, and the Offset and Gain coefficients are

set to 0, the 12 bit data straight from the

ADC is transmitted. Offset, Shading,

Gamma and any other post processing must

be done by the host.

10 bit image data - sent in 2 bytes:

X X X X 9 8 7 6- 5 4 3 2 1 0 X X

1

12 bit image data - sent in 2 bytes:

X X X X 11 10 9 8 - 7 6 5 4 3 2 1 0,

Horizontal DPI Divider = 0.

14

http://www.national.com

Page 15

Address Function

RESERVED

Reserved

0A

SENSOR CONFIGURATION

Input Signal Polarity

CDS On/Off

Standard/Even Odd Sensor

0B

Sensor Resolution

(used only for SRAM coefficient allocation)

Line Skipping Color Phase Delay

Part of the “n out of m” function, consisting of

registers 0B (bits 4-7) 44, 45 (bit 5), and 5A.

SENSOR CONTROL SETTINGS

Ø1 Polarity

Ø2 Polarity

RS Polarity

CP1 Polarity

0C

CP2 Polarity

TR1 Polarity

TR2 Polarity

Ø1 Active/Off

Ø2 Active/Off

RS Active/Off

CP1 Active/Off

0D

CP2 Active/Off

TR1 Active/Off

TR2 Active/Off

Number of TR Pulses

TR Pulse Duration

0E

TR-Ø1 Guardband Duration

Optical Black Clamp Start

0F

Optical Black Clamp End

10

Reset Pulse Start

11

Reset Pulse Stop

12

CP1 Pulse Start

13

CP1 Pulse Stop

14

CP2 Pulse Start

15

CP2 Pulse Stop

16

Reference Sample Position

17

Signal Sample Position

18

D7D6D5D4D3D2D1D

0

Value

00000000Write 00 to this register

0 Negative (CCD Sensor)

1 Positive (CIS Sensor)

0 CDS Off

1 CDS On

0 Standard (1 pixels per Ø period)

1 Even/Odd (2 pixels per Ø period)

0 300 dpi (pixels < 2731)

1 600 dpi (2730 < pixels < 5461)

n n n n n lines, n = 0-15

0Positive

1 Negative

0Positive

1 Negative

0Positive

1 Negative

0Positive

1 Negative

0Positive

1 Negative

0Positive

1 Negative

0Positive

1 Negative

0 Off

1Active

0 Off

1Active

0 Off

1Active

0 Off

1Active

0 Off

1Active

0 Off

1Active

0 Off

1Active

01 TR Pulse

12 TR Pulses

nnnnn+1 pixel periods (1-16)

n n n n n pixel periods (0-15)

nnnnn

nnnnn

nnnnn

nnnnn

nnnnn

nnnnn

nnnnn

nnnnn

nnnnn

nnnnn

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

15

http://www.national.com

Page 16

Address Function

CIS TR1 Timing Mode

19

Fake Optical Black Pixels

(for Dyna-type CIS sensors)

RESERVED

Reserved

1A

Reserved

1B

SENSOR PIXEL CONFIGURATION

Optical Black Pixels Start

1C

Optical Black Pixels End

1D

Active Pixels Start - MSB

1E

Active Pixels Start - LSB

1F

Line End - MSB

20

Line End - LSB

21

PIXEL DATA RANGE TO PROCESS

Data Pixels Start - MSB

22

Data Pixels Start - LSB

23

Data Pixels End - MSB

24

Data Pixels End - LSB

25

D7D6D5D4D3D2D1D

00000000Write 00 to this register

00000000Write 00 to this register

nnnnnnnnn pixels (0 - 255)

nnnnnnnnn pixels (0 - 255)

nnnnnn

nnnnnnnn

nnnnnn

nnnnnnnn

nnnnnnn pixels (

nnnnnnnn

nnnnnnn pixels (

nnnnnnnn

0

0 0 Off - use standard CCD Timing

CIS TR1 Timing Mode 1:

01

TR1 pulse = exactly one Ø clock,

starting at rising edge of Ø1

CIS TR1 Timing Mode 2:

10

TR1 pulse = exactly one Ø clock,

TR1 centered around Ø1 high.

11N/A

0 Off: Normal operat ion

On: RS pulse held high during entire Optical Black

1

period

n pixels (10 - 16383)

This is wh ere image data starts coming out of the

sensor, and determines the pixel where offset and

shading correction begins (pixel 0 in the DataPort)

n pixels (0 - 16383)

This selects the pixel count at which the current line is

ended and the next line begins. This determines the

integration time of one line.

Active Pixels Start

This selects the start of the range of pixels transmitted

to the PC. This value must be >=

Data Pixels Start

This selects the end of the range of pixels transmitted

to the PC. This value must be <= [

Value

- [

- 16383)

Active Pixels Start

Line End

- 20])

Line End

- 20]

16

http://www.national.com

Page 17

Address Function

COLOR MODE SETTINGS

AFE Operation

3 Channel or 1 Channel

1 Channel Mode A Channel Color

(1 Channel Mode B always uses the

26

Blue Channel)

(=TR1) position

TR

RED

(3 Channel Line Rate Mode only)

TR

(=TR2) position

GREEN

(3 Channel Line Rate Mode only)

TR

(=CP2) position

BLUE

(3 Channel Line Rate Mode only)

Integration Time Adjust

drop rate)

(TR

RED

(3 Channel Line Rate Mode only)

Integration Time Adjust

GREEN

drop rate)

(TR

27

(3 Channel Line Rate Mode only)

Integration Time Adjust

drop rate)

(TR

BLUE

(3 Channel Line Rate Mode only)

RESERVED

Reserved

28

D7D6D5D4D3D2D1D

0

Value

0003 Channel Pixel Rate Color

0013 Channel Line Rate Color

1001 Channel Mode A (1 Channel Grayscale)

1011 Channel Mode B (1 Channel Line Rate Color)

00 Red

01 Green

10 Blue

11 N/A

0 1st TR pulse position (inside Ø1 high)

1 2nd TR pulse position (inside Ø1 low)

0 1st TR pulse position (inside Ø1 high)

1 2nd TR pulse position (inside Ø1 low)

0 1st TR pulse position (inside Ø1 high)

1 2nd TR pulse position (inside Ø1 low)

0 0 Do not drop any TR

01Drop 1 TR

10Drop 2 TR

11N/A

RED

RED

0 0 Do not drop any TR

0 1 Drop 1 TR

1 0 Drop 2 TR

11 N/A

GREEN

GREEN

0 0 Do not drop any TR

0 1 Drop 1 TR

1 0 Drop 2 TR

11 N/A

BLUE

BLUE

pulses

RED

pulse (double integration time)

pulses (triple integration time)

pulses

GREEN

pulse (double integration time)

pulses (triple integration time)

pulses

BLUE

pulse (double integration time)

pulses (triple integration time)

00000000Write 00 to this register

17

http://www.national.com

Page 18

Address Function

D7D6D5D4D3D2D1D

ILLUMINATION SETTINGS

Illumination Mo de

Controls the function of the 3 LAMP outputs,

, LAMPG, and LAMP

LAMP

R

B

Mode 0 is the Off/Reset state.

Mode 1 is typically used for CCFL lamps.

29

Mode 2 is for color scanning with tri-color

LEDs.

Mode 3 is for grayscale scanning with tricolor LEDs.

PWM - MSB

LAMP

2A

(Illumination Mode 1)

LAMP

LAMP

2C

LAMP

2D

LAMP

2E

LAMP

2F

LAMP

30

LAMP

31

LAMP

32

LAMP

33

LAMP

34

LAMP

35

LAMP

36

LAMP

37

G

PWM - LSB

G

On - MSB

R

On - LSB

R

Off - MSB

R

Off - LSB

R

On - MSB

G

On - LSB

G

Off - MSB

G

Off - LSB

G

On - MSB

B

On - LSB

B

Off - MSB

B

Off - LSB

B

(Illumination Mode 1) nnnnnnnn

nnnnnnn pixels (1 - 16384)

nnnnnnnn

nnnnnnn pixels (1 - 16384)

nnnnnnnn

nnnnnnn pixels (1 - 16384)

nnnnnnnn

nnnnnnn pixels (1 - 16384)

nnnnnnnn

nnnnnnn pixels (1 - 16384)

nnnnnnnn

nnnnnnn pixels (1 - 16384)

nnnnnnnn

STATIC OFFSET AND GAIN SETTINGS FOR ANALOG FRONT END

Static Offset (Red)

38

Static Offset (Green)

39

Static Offset (Blue)

3A

Static Gain (Red)

3B

Static Gain (Green)

3C

Static Gain (Blue)

3D

0nnnnnOffset = +n*9.3mV, n = 0 to 31

1nnnnnOffset = -n*9.3mV , n = 0 to 31

0nnnnnOffset = +n*9.3mV, n = 0 to 31

1nnnnnOffset = -n*9.3mV , n = 0 to 31

0nnnnnOffset = +n*9.3mV, n = 0 to 31

1nnnnnOffset = -n*9.3mV , n = 0 to 31

0nnnnnGain = 0.93 + 0.067*n (V/V), n = 0 to 31

1nnnnnGain = 3(0.93 + 0.067*n) (V/V), n = 0 to 31

0nnnnnGain = 0.93 + 0.067*n (V/V), n = 0 to 31

1nnnnnGain = 3(0.93 + 0.067*n) (V/V), n = 0 to 31

0nnnnnGain = 0.93 + 0.067*n (V/V), n = 0 to 31

1nnnnnGain = 3(0.93 + 0.067*n) (V/V), n = 0 to 31

0

00

01

10

11

nnnn

Value

LAMP

= LAMPG = LAMPB = 0V

R

(Power-On/Reset Default)

Illumination Mode 1 - LAMP

every line, with their on and off points controlled by

the Pixel Counter settings. LAMP

continuous PWM pulse stream. (Figure 28)

LAMP

and/or LAMPB may be set to stay on or off at

R

all times by setting the LAMP Off or LAMP On settings

and LAMPB turn on

R

Output is

G

(registers 2C-37) greater than the Line End value

(registers 20 and 21).

Illumination Mode 2 - LAMP

on sequentially at the line rate, with their on and off

, LAMPG, LAMPB turn

R

points controlled by Pixel Counter settings. (Figure

29)

Illumination Mode 3 - LAMP

on every line, with their on and off points controlled by

, LAMPG, LAMPB turn

R

the Pixel Counter settings. (Figures 30 and 31)

LAMP

output is a PWM pulse stream. Duty cycle is

G

n/4095. Clock for counter is CRYSTAL IN, giving max

output frequency of 12.2kHz for f

CRYSTAL IN

This selects the pixel count at which the LAMP

output goes high (if programmed)

This selects the pixel count at which the LAMP

output goes low (if programmed)

This selects the pixel count at which the LAMP

output goes high (if programmed)

This selects the pixel count at which the LAMP

output goes low (if programmed)

This selects the pixel count at which the LAMP

output goes high (if programmed)

This selects the pixel count at which the LAMP

output goes low (if programmed)

= 50MHz.2B

R

R

G

G

B

B

18

http://www.national.com

Page 19

Address Functio n

DIGITAL PIXEL RATE OFFSET AND GAIN SETTINGS

Multiplier Gain Range

Smaller gain ranges provide finer control.

Larger gain ranges correct for larger shading

errors.

Offset/Gain data format

3E

Multiplier Coefficient Source

Offset Coefficient Source

Fixed Offset Coefficient

3F

Fixed Multiplier Coefficient - MSB

40

Fixed Multiplier Coefficient - LSB

PARALLEL PORT SETTINGS

Communicati on Mode

(for reading data from any of the LM9830’s

registers)

Note: This register must be set

appropriately before data can be read

42

from the LM9830!

Parallel Port Output Driver Current

(I

and IOH can be used to calculate rise

OL

and fall times into the load capacitance:

rise/fall time approximately equals 5V*C/i)

EXTERNAL SRAM SETTINGS

External SRAM Size

SRAM Interface Output Driver Current

and IOH can be used to calculate rise

(I

OL

and fall times into the load capacitance:

rise/fall time approximately equals 5V*C/i)

SRAM Bandwidth (8 Bit Data Mode)

43

8 slot mode should always be used to

maximize performance. If the external

SRAM is to slow to meet the t

requirement, the slower 4 SRAM

RD SETUP

accesses/ADC clock mode may be used.

Scanning Duplex (10/12 bit Data Mode)

Full Duplex mode should always be used to

maximize scan speed. If the external SRAM

is to slow to meet the t

the slower Half Dupl ex mode may be used.

RD SETUP

requirement,

D7D6D5D4D3D2D1D

0

0 0 1.5:1 (33%)

0 1 2.0:1 (50%)

1 0 3.0:1 (66%)

1 1 Bypass Multiplier

0 6 bits offset/10 bits gain

1 8 bits offset/8 bits gain

0 Configura tion Register 3F (Fixed)

1 External SRAM

0 Configuration Register 40 and 41 (Fixed)

1 External SRAM

nnnnnnnn

Fixed Offset to use for calibration - 2MSBs are

assumed to be 0 if using 6 bit offset format

n n Fixed Gai n to use f o r cal ibr at ion - 2L SBs ar e ass ume d

nnnnnnnn

to be 0 if using 8 bit gain format41

0 8 bit Bidirectional/EPP

1 4 bit Nibble

00 I

01 I

10 I

11 I

= 5mA, IOH = -6mA

OL

= 7mA, IOH = -9mA

OL

= 9mA, IOH = -12mA

OL

= 15mA, IOH = -21mA

OL

0 0 64 kbytes (not recommended for 600dpi scanners)

0 1 128 kbytes

1 0 256 kbytes

11N/A

00 I

01 I

10 I

11 I

= 3.5mA, IOH = -4mA

OL

= 6mA, IOH = -7.5mA

OL

= 12mA, IOH = -17mA

OL

= 21mA, IOH = -32mA

OL

0 4 SRAM accesses/ADC clock

1

0

1

8 SRAM accesses/ADC clock

must be 25MHz or lower)

(f

MCLK

Full Duplex- Can transmit data while scanning

must be 25MHz or lower)

(f

MCLK

Half Duplex - Can only transmit data when buff er is full

or scan has been stopped

Value

19

http://www.national.com

Page 20

Address Function

STEPPER MOTOR CONTROL SETTINGS 1

n (Line Skipping)

44

Part of the “n out of m” function, consisting of

registers 0B (bits 4-7) 44, 45 (bit 5), and 5A.

Full/Microstepping

Current Sensing Phases

= 0 for fullstepping

= 1 for microstepping

Stepper Motor Pha se A Polarity

45

Stepper Motor Pha se B Polarity

, and B stepper motor status

A, B, A

Line Skipping Phase

Part of the “n out of m” function, consisting of

registers 0B (bits 4-7) 44, 45 (bit 5), and 5A.

Scanning Step Size - MSB

46

Scanning Step Size - LSB

Fast Feed Step Size - MSB

48

Fast Feed Step Size - LSB

Fullsteps to Skip at Start of Scan - MSB

4A

Fullsteps to Skip at Start of Scan - LSB

Fullsteps to Scan after Paper Sensor #2

4C

trips -MSB

Fullsteps to Scan after Paper Sensor #2

trips -LSB

Pause scanning, stop/reverse motor

4E

Resume scanning, start motor

4F

Full steps to reverse when buffer is full

50

Acceleration Profile (stopped)

Acceleration Profile (25%)

51

Acceleration Profile (50%)

Default Phase Difference - MSB

52

Default Phase Difference - LSB

Lines to Process After Pause Scan Signal

54

Lines to Discard after Resume Scan

Signal

Kickstart Steps

55

Hold Current Timeout

Stepper Motor PWM Frequency

56

Stepper Motor PWM Set Duty Cycle

57

(fullstepping mode) nnnMotor gets maximum current for first n (0-7) full steps

D7D6D5D4D3D2D1D

tttttttt

0

1

0 Red sensor data arrives before Green sensor

1 Blue sensor data arrives before Green sensor

nnnnnnThe step size of one microstep while scanning, in

nnnnnnnn

nnnnnnThe step size of one microstep while fast feeding, in

nnnnnnnn

nnnnnnWhen scan starts, paper is fed forward n full steps (0 -

nnnnnnnn

nnnnnnAdds a delay of n (0-16383) full steps between when

nnnnnnnn

nnnnnnnnPause scan when buffer is n kbytes full

nnnnnnnnResume scan when buffer is n kbytes full

nnnnnnn (0-63) full steps (0 = do not reverse)

n n n (0-3) full steps at 50% speed

nnnnnnnnUsed to calculate when motor resumes after reversing

nnnnnnnn

nnn

nnnnn Full step time units (1-31), 0 = no hold current

nnnnnnnn

nnnnnn= n/64 (default = 0)

0

n lines saved in SRAM for every m lines (register 5A)

scanned, function bypassed if register value = 0.

n (lines saved per m lines scanned) = 256 - t

t = 256 - n

If t = 0 then function is bypassed

0 Full Step Mode

1 MicroStepping Mode

1 Phase - No microsteppi ng, just kickstart/stop

0

functions

1 2 Phases - necessary for microstepping

0

Positive (A/B/A

1

0

1

n n n (0-3) full steps at 25% speed

Negative (A/B/A

Positive (A/B/A

Negative (A/B/A

A, B, A

, and B output pins in Tri-State

A, B, A

, and B output pins active

units of pixel periods (minimum 2).47

units of pixel periods (minimum 2).49

16383) at highest speed. For “zooming” in flatbeds4B

Paper Sensor #2 trips and when the scanning bit is

reset, terminating the scan/motor movement.4D

n n n (0-3) full step time units pause while stopped

and stopping. 1 < n < 6553553

n (0-7) lines. This only applies if the motor doesn’t

nnn

reverse (reverse steps = 0).

n (0-7) lines. This only applies if the motor doesn’t

reverse (reverse steps = 0).

Should be set to same value as bits 0-2.

=CRYSTAL IN/(4*n) (0 < n < 256)

=CRYSTAL IN/(4*256) (n = 0)

Value

/B Output high = winding energized)

/B output low = winding energized)

/B Output high = winding energized)

/B output low = winding energized)

20

http://www.national.com

Page 21

Address Function

PAPER SENSOR SETTINGS

Paper Sensor #1 Polarity

Paper Sensor #1: Level/Edge sensitive

Paper Sensor # 1: Stop Scan

Paper Sensor #2 Polarity

58

Paper Sensor #2: Level/Edge sensitive

Paper Sensor # 2: Stop Scan

MISC I/O PIN SETTINGS

Misc I/O #1: Input or Output

Misc I/O #1: Polarity

(if configured as an input)

Misc I/O #1: Level/Edge sensitive

(if configured as an input)

Misc I/O #1: Output State

(if configured as an output)

59

Misc I/O #2: Input or Output

Misc I/O #2: Polarity

(if configured as an input)

Misc I/O #2: Level/Edge sensitive

(if configured as an input)

Misc I/O #2: Output State

(if configured as an output)

STEPPER MOTOR CONTROL SETTINGS 2

m (Line Skipping)

5A

Part of the “n out of m” function, consisting of

registers 0B (bits 4-7) 44, 45 (bit 5), and 5A.

D7D6D5D4D3D2D1D

0

1

0

1

0 The Misc I/O #2 pin is configured as an input.

1 The Misc I/O #2 pin is configured as an output.

0 A low input on Misc I/O #2 is True

1 A high input on Misc I/O #2 is True

0

1

0

1

mmmmmmmm

0

0 A low input on Paper Sensor #1 is True

1 A high input on Paper Sensor #1 is True

Level sensitive: Paper Sensor #1 State bit (in Status

0

Register) is set to a 1 if Paper Sensor #1 is currently

True.

Edge sensitive: Paper Sensor #1 State bit (in Status

1

Register) is set to a 1 if Paper Sensor #1 has been

True since the last time the Status Register was read.

Transitions on Paper Sensor #1 will not clear the

0

scanning bit.

A False - to - True transition on Paper Sensor #1 will

1

0 A low input on Paper Sensor #2 is True

1 A high input on Paper Sensor #2 is True

0

1

clear the Command Register and stop the scan.

Level sensitive: Paper Sensor #2 State bit (in Status

Register) is set to a 1 if Paper Sensor #2 is currently

True.

Edge sensitive: Paper Sensor #2 State bit (in Status

Register) is set to a 1 if Paper Sensor #2 has been

True since the last time the Status Register was read.

Transitions on Paper Sensor #2 will not clear the

scanning bit.

A False - to - True transition on Paper Sensor #2 will

clear the Command Register and stop the scan (after

the number of lines specified in the

after Paper Sensor #2 trips

0 The Misc I/O #1 pin is configured as an input.

1 The Misc I/O #1 pin is configured as an output.

0 A low input on Misc I/O #1 is True

1 A high input on Misc I/O #1 is True

Level sensitive: Misc I/O #1 State bit (in Status

0

Register) is set to a 1 if Misc I/O #1 is currently True.

Edge sensitive: Misc I/O #1 State bit (in Status

1

Register) is set to a 1 if Misc I/O #1 has been True

since the last time the Status Register was read.

The output of the Misc I/O #1 pin will be a logic low

(0V).

The output of the Misc I/O #1 pin will be a logic high

(5V).

Level sensitive: Misc I/O #2 State bit (in Status

Register) is set to a 1 if Misc I/O #2 is currently True.

Edge sensitive: Misc I/O #2 State bit (in Status

Register) is set to a 1 if Misc I/O #2 has been True

since the last time the Status Register was read.

The output of the Misc I/O #2 pin will be a logic low

(0V).

The output of the Misc I/O #2 pin will be a logic high

(5V).

n lines (register 44) saved in SRAM for every m lines

scanned. m = 1 to 255.

If m = 0 then function is bypassed

Value

Fullsteps to Scan

register).

21

http://www.national.com

Page 22

Address Function

TEST MODE SETTINGS

Reserved

5B

ADC Output Code - MSB

5C

ADC Output Code - LSB

Reserved

Offset Subtractor Input Select

5E

CDS Signal

Reserved

5F-6F

Parallel Port Noise Filter

70

Reserved

71-7F

D7D6D5D4D3D2D1D

00000000Write 00 to this register

nnnnnnnn

00000000

0 The ADC is input to Offset Subtractor

1 Registers 5C and 5D are input to Offset Subtractor

0 Normal Operation

1 CDS signal is output on TEST pin

00000000Write 00 to these registers

01110000Write 70 to this register

00000000Write 00 to these registers

0

nnnnUsed to force the input to the Offset Subtractor

to a known value for digital tests5D

Write 00 to this register for normal operation, modify

bits 5 and 7 as shown below for test modes

Value

22

http://www.national.com

Page 23

Applications Informat ion

pixel

100dpi

p

n-2pn-1pn

++

3

-------------------- ----------------------- -=

1.0 THEORY OF OPERATION

1.1 Overview

A scanner is composed of many different but tightly interconnected blocks (the analog fro nt end a nd ADC, sensor c lock generation, stepper motor con trol, data buffering, parallel por t I/O,

and others).

1.2 Signal Processing Overview

1.3 Scanner Support Functions Overview

2.0 Signal Processing Operation

2.1 ADC

The ADC is a 6MHz 12 bit pipelined architecture.

2.2 Pixel Rate Offset Correction Block

Two bytes are used to store the pixel rate offs et and gain co efficients for each pixel. For CCDs, the split is usually 6 bits for offset

and 10 bits for gain. For som e CIS sensors w ith unusually large

offsets, the offset correction range may be increased by changing

the split to 8 bit s for offset and 8 bits for gai n. This split is determined by a bit in the configuration register.

A digital subtractor subtra cts the 6 (or 8) bit offset word (corresponding to that pixel’s offset error) from each pixel. The LSB of

the offset word is the same size as the 10 bit LSB of the ADC (the

two smallest 12 bit ADC output bits, D1 and D0, are not used with

the offset subtractor). Th e coefficients are stor ed in the external

RAM and accessed at the pixel rate.

The subtractor saturates at 0, i.e. if the coefficient to be subtracted is greater than the ADC o utput code, th e resu lt is an o utput of 0.

2.3 Pixel Rate Gain Correction Block

This is a digital multiplier that multiplies the output word from the

subtractor by a 10 (or 8) bit digital correct ion coefficient corresponding to that pixel’s gain error. The coefficients are st ored in

the external RAM and a ccessed at the pixel rate. When in 8 bit

mode, the 8 bits correspond to the top 8 MSBs of the 10 bit digital

correction coefficient word. Th e 10 bit LSB s o f the inpu t word a re

padded with 0s in 8 bit mode.

The multiplier saturates at 1023, i.e. if the result of the multiplication is greater than 1023, the multiplier output is 1023.

2.4 Pixel Processing Block

2.4.1 Pixel Processing In 8/24 Bit Mode

In the 8 and 10 bit o utput mod es (for 24 and 30 bit c olor scan s),

this stage is where the optical resolution of the sensor is digitally

reduced.

To maximize scanning speed and imag e quality at the popular

resolutions of 400, 300, 200, 150, 100, 75, and 50 dpi, the resolution can be reduced ins ide the scanner, prior to th e gamma correction stage. (Resolu tion in t he ver tic al dir ection is cont rolled by

the stepper motor speed.) This is done by averaging adjacent pixels. For example, to get 100 dpi from a 300dpi optical sensor, you

would average 3 300dpi pixels:

The number of pixels out of the Pixel Processing block is equal to

the integer portion of the number of pixels in to the Pixel Processing block divided by the “Divide By” setting, fro m the table shown

in Figure 11.

Pixels

IN

------------------- ------

OUT

=

INT

Divide By

Pixels

If there are not enough pixels at the end of a lin e to form a complete pixel, the last pixel will be eliminated. For example, if a line

is 35 pixels wide and the Horizontal DPI setting is set to divide by

6, then the output of the Pixel Processing block will be 5 pixels

(the integer portion of 35/6). The last 5 pixels will be discarded,

since 6 pixels would be required to form a new pixel in this mode.

Boost

1V/V or

3V/V

+

+

V

IN

G

Σ

+

V

OS1

B

+

Σ

+

V

OS2

Offset

D

= (((VIN + V

OUT

simplified, with all offsets = 0, this is:

D

OUT

PGA

0.93V/V t o

3V/V

Σ

+

V

DAC

DAC

+ V

OS1)GB

= (VINGB + V

G

PGA

DAC

+

Σ

+

V

OS3

+ V

OS2)GPGA

DAC)GPGA

+ V

12 Bit

ADC

OS1

D

OUT

)C

C

C is a constant that combines the gain error through the AFE, reference voltage variance, and analog voltage

to digital code conversion into one constant. Ideally, C = 2048 codes/V (4096codes/2V). Manufacturing toler-

ances widen the range of C. See Electrical Specifications

Figure 10: Analog Front End (AFE) Model

23

http://www.national.com

Page 24

This equation also applies to the divide by 1.5 function.

(X=mask out in software).

Divide

By

DPI

(600 DPI sensor)

DPI

(300 DPI sensor)

1 600 300

1.5 400 200

2 300 150

3 200 100

4 150 75

6 100 50

875 37.5

12 50 25

Figure 11:

Decreasing Horizontal Resolution

The output of this stage is sen t through the gamma and pixel

packing stages, resulting in output data for matted as shown in

Figure 15.

2.4.2 Pixel Processing 10/30 Bit Mode

Scanning in 10 bit mode (30 bit co lor) supports the Horizontal

DPI Divider function as wel l as the pixel rate shading and offse t

functions. The output dat a is formatted as shown in Figure 12

(X=mask out in software).

76543210 Order

XXXX9876 First Byte

543210XX Second Byte

Figure 12:

10 Bit Mode Pixel Data Format

The software on the host PC must perform any gamma correction

desired.

There are two varia tions on t he 10 and 12 bi t ou tput m odes: Ful l

Duplex and Half Duplex, determined by bit 5 of Configuration

Register 43. In the Fu ll Duplex mode, there are 6 S RAM operations per pixel: offset data read , gain data r ead, pixel MSB wri te,

pixel LSB write, pixel MSB r ead , p ixel LSB re ad) . S in c e t her e are

8 MCLKs per pixel, the writes take 2 MCLK periods and the reads

take 1 MCLK period. T his mode is preferred because it permits

faster scanning, but it requires fast SRAM access.

The Half Duplex mode accommodates slower SRAM. In Half

Duplex mode, the data in the SRA M ca n not be r ead by th e hos t

PC until the buffer is full. Therefore there are two phases to scanning data in the Half Duplex mode. The first is writing pixel data to

SRAM using 4 operations/pixel (offset data read, gain data read,

pixel MSB write, pixel LSB write). In this mode the read and write

cycles will all be 2 MCLKs long. The second phase is reading the

contents of the SRAM and sen ding them to the host PC. This

read operation uses 2 MCLK read cycles/byte.

2.4.3 Pixel Processing: 12/36 Bit Mode

Scanning in 12 bit mo de (36 bit color) can onl y be done at the

optical resolution of the se nsor, and the shading and of fset functions can not be used. The Horizon tal DPI Divide r function must

be set to 1 (register 09, bits 0-2 = 0) to get 12 bit data. The shading and offset functions must a lso be disabled (registe rs 3E, 3F,

40, and 41 all set to 0). The 10 bi t p ixel output from the multiplier

is combined with the 2 12 bit LSBs from the ADC to re create the

12 bit pixel. The output data is formatted as shown in Figure 13

76543210 Order

XXXX111098 First Byte

76543210 Second Byte

Figure 13:

12 Bit Mode Pixel Data Format

The software on the host PC must perform all offset an d shading

correction, horizonta l resolution adju stment, and gamm a correction.

The 12 bit mode uses the same Full or Half Duplex options

described in

2.4.2 Pixel Processing 10/30 Bit Mode

2.5 Gamma Correction Tables

There are 3 ga mma lookup tables for R, G, and B. The input to

the table is the 10 b it pixel data coming from the previous stage

2.4 Pixel Processing Block

(

). The output is the 8 bit gamma corrected pixel data. The tables are therefore 1K bytes x 8 bits in

size. Each gamma table (red, green, and blue) can be loaded with

255

8 Bit Pixel Out

0

0 1023

10MSBs of 12 bit Output

Figure 14:

Gamma Table

any arbitrary user-defined transfer curve.

The gamma ta bles ar e l oa ded t hro ugh the dataport ( see

5.1 The

DataPort: Reading and Wr iting to Gamma, Offset, and Gain

Memory

). In most LM9830 m odes, the DataPort selects which

color (Red, Green or Blue) gamma table will be read from or written to. In 1 Channel Mode A, the on ly gamma table that can be

accessed is the gamma table for the 1 Channel Mod e A color

selected by bits 3 and 4 of register 26.

2.6 Pixel Packing/Thresholding Block

Some scans require only one bit per pixel (“line art” mode), others

may need only 2 or 4 bits/pixel. To increase scanning speed for

lower pixel depths, the LM9830 pa cks the d esire d M S Bs of multiple pixels together, increasing the tran smi ssio n s pee d to the host

by a factor of 2, 4, or 8. Figure 15 shows how the pixels are

Pixel

Depth

76543210

8b7 p

4b7 p0b6 p0b5 p0b4 p0b7 p1b6 p1b5 p1b4 p

b6 p0b5 p0b4 p0b3 p0b2 p0b1 p0b0 p

0

2b7 p0b6 p0b7 p1b6 p1b7 p2b6 p2b7 p3b6 p

1b7 p0b7 p1 b7 p2b7 p3b7 p4b7 p5b7 p6b7 p

Figure 15:

Packing Multiple Pixels Into One Byte

0

1

3

7

packed together for 8, 4, 2, and 1 b it pixel depths. In Figure 15,

“b” indicates the bit po sition (b7 = the m ost significant and b0 =

24

http://www.national.com

Page 25

the least significant bit) of the original 8 bit pixel data, and pn indi-

LPI4C

StepSize

pixels/line

------------------- -------=

cates the original pixel sequence, i.e p

, p1, p2, p3...

0

If there are not enough un packed pixels at the end of a line to

complete the packed byte for transmission, that final byte is not

sent.

The gamma table in

2.5 Gamma Correction Tables

allows the

user to set the thresho ld of each transition for various line ar t or

reduced pixel depth modes.

of the image sen sor, determines the effective ver tical resolution

(Lines Per Inch, or LPI).

The stepper motor is moved forwards and ba ckwards by two signals, A and B, 90° out of phase with each other. The phase for the

forward direction is set in Configuration Register 45.

The A and B signals are either squarewaves (in Full Step Mode,

Figure 16), or a staircase approximation of a sine wave (in

Microstep mode, Figures 18 and 19 ) .

2.7 Line Buffer

The line buffer uses the exter nal SRAM to st ore t he pi xel data a t

the fixed rate and send it back to the PC at a n asynchronous,

unpredictable, and non-constant rate.

This buffer is tightly coupled to the st epper motor (

Motor Controller

), and is responsible for stopping the motor

3.0 Stepper

before the buffer overflows and starting the moto r again as the

buffer nears empty.

If the scanner is generating p ixel data faster than the PC can

acquire it, the line buffer will start to fill up. As the buffer nears

100% full, the scan mu st be paused before it star ts acquiri ng a

line it cannot store becaus e of lack of R AM. Th is Pause Threshold limit (register 4E) is programmable in 1 kbyte increments

between 0 and 255 kbytes but should be no higher than 100 % of

the buffer RAM size minus 1 line of data (for single output CCDs

and CIS) or 3 lines of data (for triple output CCDs and CIS).

When this point is re ached the buffer sends a command to the

stepper motor controller to stop scanning. The remainde r of the

line being processed will continue being processed and be sen t

to the buffer. If the Lines To Process After Pause Scan Signal register (register 54) is greater than 0, then room for these additional

lines need to be added into th e Pause Threshold value calculation.

After a pause, the buffer will now transmit data to the PC until it

hits the Resume Threshold li mit (register 4F), wh ich is also programmable in 1 kbyte increments between 0 and 256kbytes.

When the Resume T hreshold is reache d, the Line Buffer sends

the motor controller a command to resume.

Note that the scanner soft ware on the host PC is resp onsible for

ensuring that the Pause Thresho ld value is low eno ugh to ensure

that any data that comes aft er a pause request (the rest o f the

current line and any s ubsequent lines if register 54 bits 0-2 are

greater than 0) will fit into the SRAM buffer size, which is equal to

SRAM size - COEFFICIENT size.

The pause condi tion i s rea ched w hen the nu mber of bytes in the

buffer is equal to the value in register 4E * 1024. The scan will

resume when the number of bytes in the buffer is equal to (the

value in register 4F * 1024 + 1023).

Since the external SRAM also contains the pixel gain and offset

data (see

2.2 Pixel Rate Offset Correct ion B lock

Rate Gain Correction Block

), the buffer is as large as the SRAM

and

2.3 Pixel

size minus the coefficient storage. Suppor ted SRAM sizes are

64kbyte, 128kbyte, and 256kbyte. Coefficient data always takes

up a total of 16kbytes for 300dpi sensors and 32kbytes for 600dpi

sensors.

A

A

1 full step = 4

microsteps

B

B

Figure 16:

Stepper Motor Waveform - Full Stepping

The LM9830 always counts stepper motor steps in units of

microsteps. A full step is equal to four microsteps. Even when the

LM9830 is in Full Step Mode, it is counting in microsteps, and will

increment the step per motor (generating a f ull step) every four

microsteps.

The microstep Step Size is defined in units of time. These units of

time are pixel period s, as defined i n the hor izontal pixel counter.

In the 3 channel pixel rate input mo de, the pixel period is the

f

/3 (= f

ADC

modes, the pixel period is equa l to f

Size is stored in the

/24). In the 3 channel line rate and 1 channel

MCLK

Scanning Step Size

/3 (= f

ADC

MCLK

configuration register

/24). The Step

as a 14 bit value. During nor mal operation, the stepper motor is

advanced 1 microstep every Step Size pixel periods. The LPI can

be calculated as follows: