Page 1

LH5481

LH5491

FEATURES

•• Fastes t 64 × 8/9 Cascadable FIFO

35/25/15 MHz

•• Expandable in Word Width and

FIFO Depth

•• Almost- Full/ Almost -Em pty a nd

Half-Full Flags

•• Fully Ind ependent Asynchro nous

Inputs and Output s

•• LH5481 Output Enable forces Data

Output s to High-Impedance State

•• Pin-Compatible Replacements for Cypress

CY7C408A/09A or L ogic Devices

L8C408/09 FIFOs

•• Industry Standard Pinout

•• Packages:

28-Pin, 300-mil DIP

28-Pin PLCC

FUNCTIONAL DESCRIPTION

The LH5481 and LH5491 are high-performance , asyn-

chronous First-In, First-O ut (FIFO) memories organized

64 words deep b y eight or nine bits wide. The eight-bit

LH5481 has an Out put Enable ( OE) function, which can

be used to force the eig ht data out puts (DO) to a high -impedance stat e. The LH5491 has nine da ta outp uts.

These FI FOs acc ept eight or nine- bit dat a at the Data

Inputs (DI). A Shift In (SI) signal writes the DI data into the

FIFO. A Shif t Out (SO) sign al shift s stor ed data to the Data

Outputs (DO). The Ou tput Ready (OR) signal i ndicates

when valid data is present on the DO outputs.

If the FIFO is full and unable to accep t more DI data ,

Input Ready (IR) will not return HIG H, and SI pulses will

be ignored. If the FIFO is empty and unab le to shift data

to the DO outputs, OR will not return HIGH, and SO

pulses will be ignored. The Almost-Full/Almost-Empty

(AFE) flag is asserted (HIGH) when the FIFO is almost-full

(56 wor ds or more) or alm ost- em pty (eight words or les s).

The Half-Fu ll (HF) flag is ass erted ( HIGH) when the FI FO

contains 32 words or more .

Reading and writing operat ions may be asynchr onous,

allowing these FIFOs to be used as buffers between

digital machines of different oper ating frequencies. The

high speed make s these FIFOs ideal for high performance communication and contr oller applications.

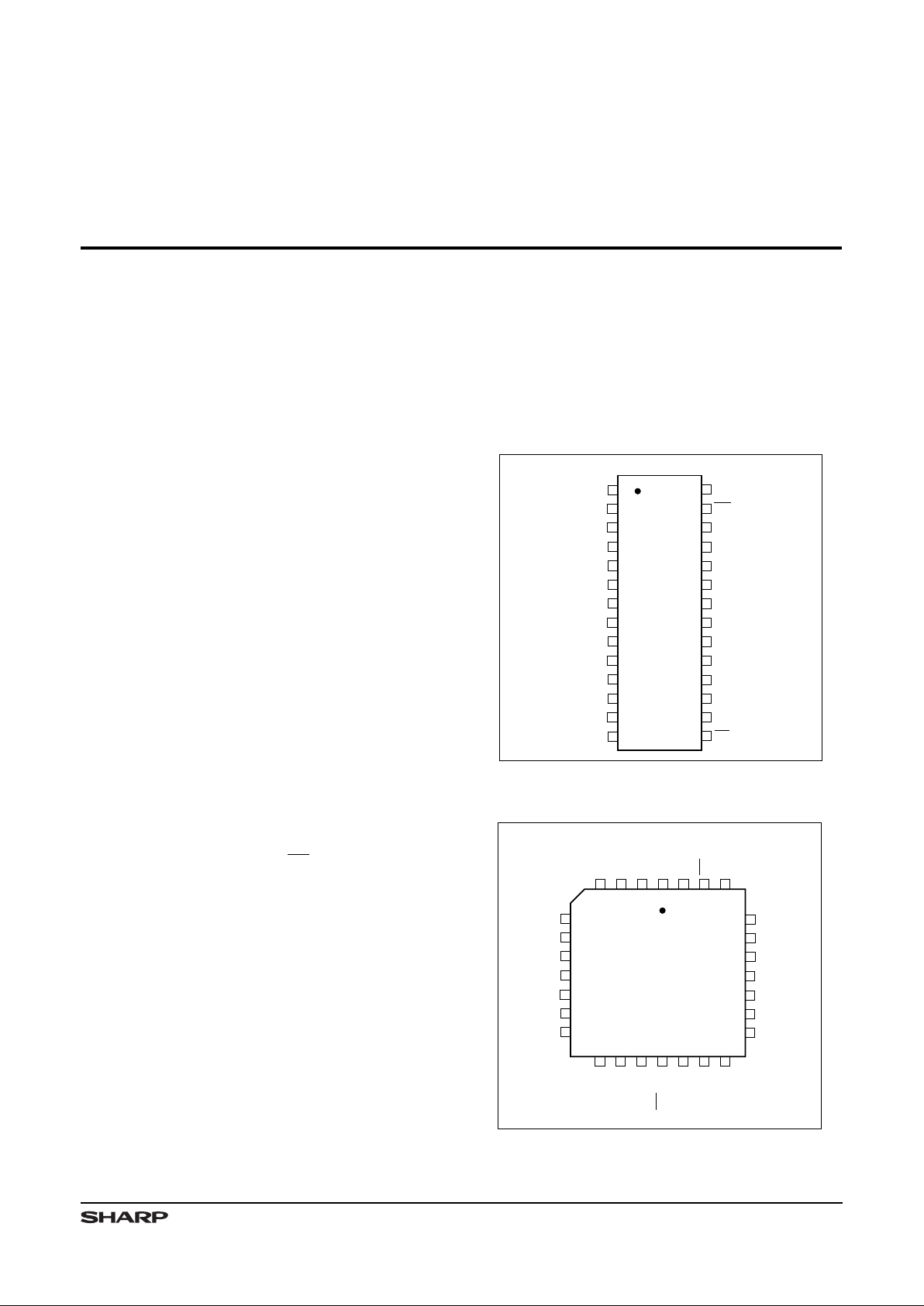

PIN CONNECTIONS

5481-1D

1

2

3

4

5

6

7

8

9

10

11

12

13

14

AFE

HF

IR

SI

DI

0

DI

1

V

SS

DI

2

DI

3

DI

4

DI

5

DI

6

DI

7

NC/DI

8

28

27

26

25

24

23

22

21

20

19

18

17

16

15

V

CC

MR

SO

OR

DO

0

DO

1

V

SS

DO

2

DO

3

DO

4

DO

5

DO

6

DO

7

OE/DO

8

28-PIN PDIP TOP VIEW

Figure 1. Pin Connections for DIP Package

5481-2D

1

2

3

4

5

6

7

8

9

10

11

12

13

14

DI

0

DI

1

DI

2

DI

3

DI

4

DI

5

28

27

26

25

24

23

22

21

20

19

18

17

16

15

OR

DO

0

DO

1

DO

2

DO

3

DO

4

SI

IR

HF

AFE

V

CC

MR

SO

DI6DI

7

NC/DI

8

OE/DO

8

DO

7

DO

6

DO

5

28-PIN PLCC

TOP VIEW

V

SS

V

SS

Figure 2. Pin Connections for PLCC Package

Cascadable 64 × 8 FIFO

Cascadable 64 × 9 FIFO

1

Page 2

PIN DESCRIPTIONS

PIN PIN TYPE * DESCRIPTION

DI0 – DI

7 I

Data Input s, LH5481

DO0 – DO

7

O/Z

Data O u t pu t s, LH5481

DI0 – DI

8

I

Data Input s, LH5491

DO0 – DO

8

O

Data O u t pu t s, LH5491

SI

I

Shift In

SO

I

Shift Out

IR

O

Input Ready

OR

O

Output Ready

* I = Input, O = Output, Z = High-Impedance, V = Power Voltage Level

PIN PIN TYPE * DESCRIPTION

HF

O

Half-Full Flag

AFE

O

Alm ost -Fu ll / Almost -

Empt y

MR

I

Master Reset

OE

I

Output Enable

(LH5481 only)

V

CC

V

Positive Power Supply

V

SS

V

Ground

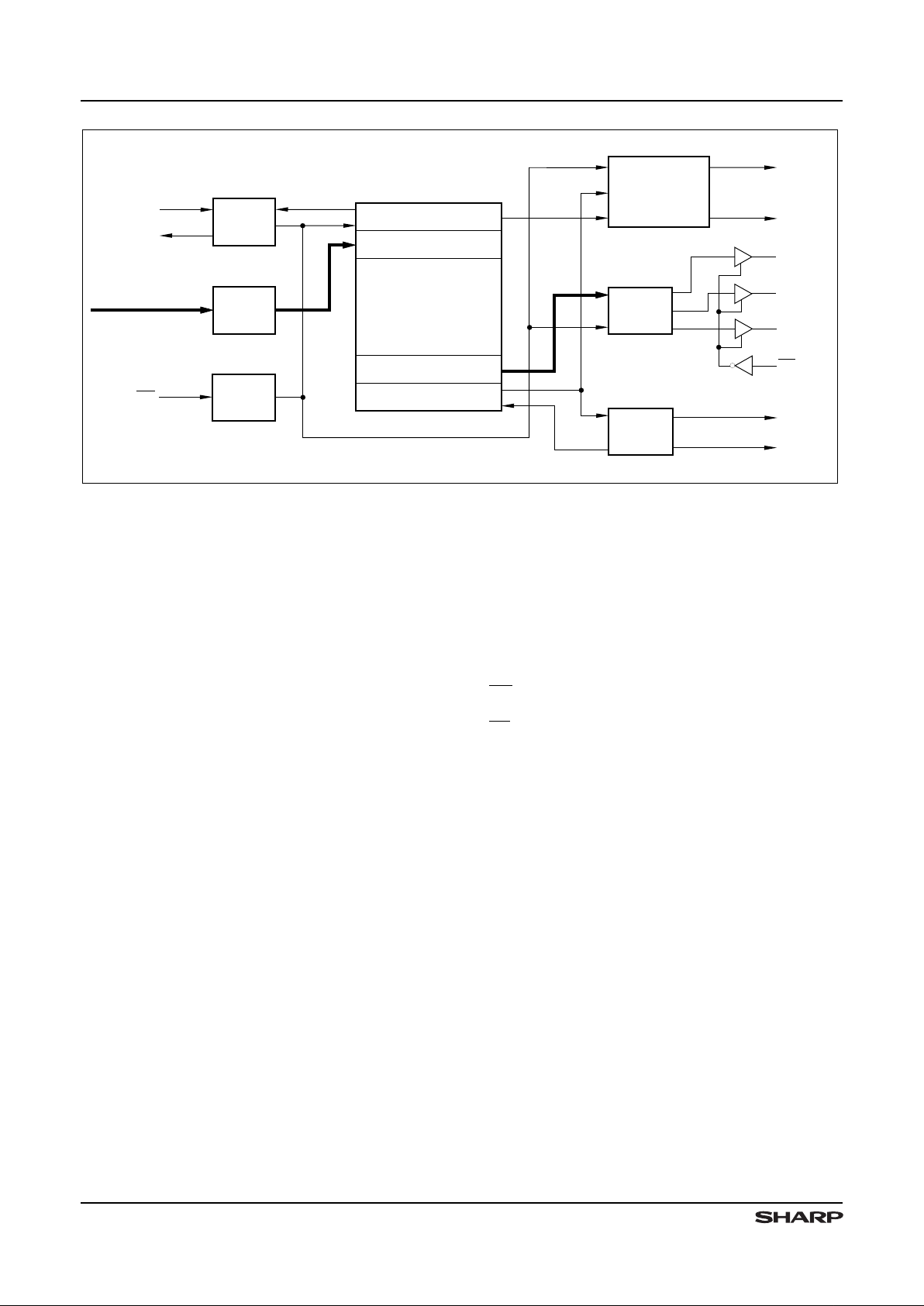

5481-3

WRITE POINTER

WRITE MULTIPLEXER

MEMORY ARRAY

READ MULTIPLEXER

READ POINTER

INPUT

CONTROL

LOGIC

DATA IN

MASTER

RESET

SI

IR

(LH5491) DI0 - DI

8

(LH5481) DI0 - DI

7

MR

ALMOST-FULL/

ALMOST-EMPTY

HALF-FULL

DATA OUT

OUTPUT

CONTROL

LOGIC

AFE

HF

DO

0

DO

7

OR

SO

DO

8

(LH5491)

OE

(LH5481)

.

.

.

.

.

.

Figure 3. LH5481/ 91 Bl o ck Diagr am

LH5481/91 64 × 8 / 64 × 9 FIFO

2

Page 3

ABSOL UTE MAXI MUM RATING S

1,2

PARAMETER RATING

Vcc Range –0.5 V to 7 V

Input Vo ltage Range –0.5 V to Vcc + 0.5 V (not to exceed 7 V)

DC Out put Current

3

±40 mA

Storag e Temper at ur e –65oC to 150oC

DC Voltage Appl ied T o Output s In High-Z state –0.5 V to Vcc + 0.5 V (not to exceed 7 V)

Sta tic Discharge Vol tage

4

> 2000 V

Power Dissipation (Packag e Limit) 1.0 W

NOTES:

1. All voltages are measured with respect to Vss.

2. Stresses greater than those listed under ‘Absolute Maximum Ratings’ may cause permanent damage to the dev ice.

This is a stress rating for transient conditions only. Functional operation of the device at these or any other conditions

above those indicated in the ‘Operating Range’ o f this specification is not implied. Exposure to abs olute maximum r at ing

conditions for extended periods may affect device reliability.

3. Outputs should not be shorted for more than 30 seconds. No more than one output should be short ed at any time.

4. Sample tested onl y.

OPERATING RANGE

1

PARAMETER DESCRIPTION MIN MAX UNIT

T

A

Temp eratu re, Amb ient

0.0 70

o

C

V

CC

Supply Vol tage

4.5 5.5 V

Vss Ground

0.0 0.0 V

V

IL

Input Low Voltag e (Lo g ic ‘0’)

2

–0.5 0.8 V

V

IH

Input High Volta ge (Logic ‘1’)

2.0 Vcc + 0.5 V

NOTES:

1. All voltages are measured with respect to Vss.

2. FIFO inputs are able to withstand a –1.5 V undershoot for less than 10 ns per cycle.

DC ELECTRICAL CHARACTERIS TIC S 1 (Over Operating Range Unless Otherwise Noted)

PARAMETER DESCRI PTION TEST CONDITIONS MIN MAX UNIT

I

LI

Input Leakage Current VCC = 5. 5 V, VIN = 0 V to V

CC

–10 10

µA

I

LO

Output Leakage Current (High-Z ) VCC = 5. 5 V, V

OUT

= 0 V to V

CC

–10 10 µA

V

OH

Output High Voltage VCC = 4. 5 V, IOH = –4 mA

2.4 V

V

OL

Output Low Voltage VCC = 4. 5 V, IOL = 8.0 mA

0.4 V

I

CCQ

Power Supply Quiescent Current

VCC = 5. 5 V, I

OUT

= 0 mA

V

IN

≤ V

IL, VIN ≥ VIH

25 mA

I

CC

Power Supply Curr ent

2

fsi = 35 MHz, fso = 35 MHz

45 mA

NOTES:

1. All voltages are measured with respect to Vss.

2. Icc is dependent upon actual output loading and cycle rates. Specified values are with outputs open.

64 × 8 / 64 × 9 FIFO LH5481/91

3

Page 4

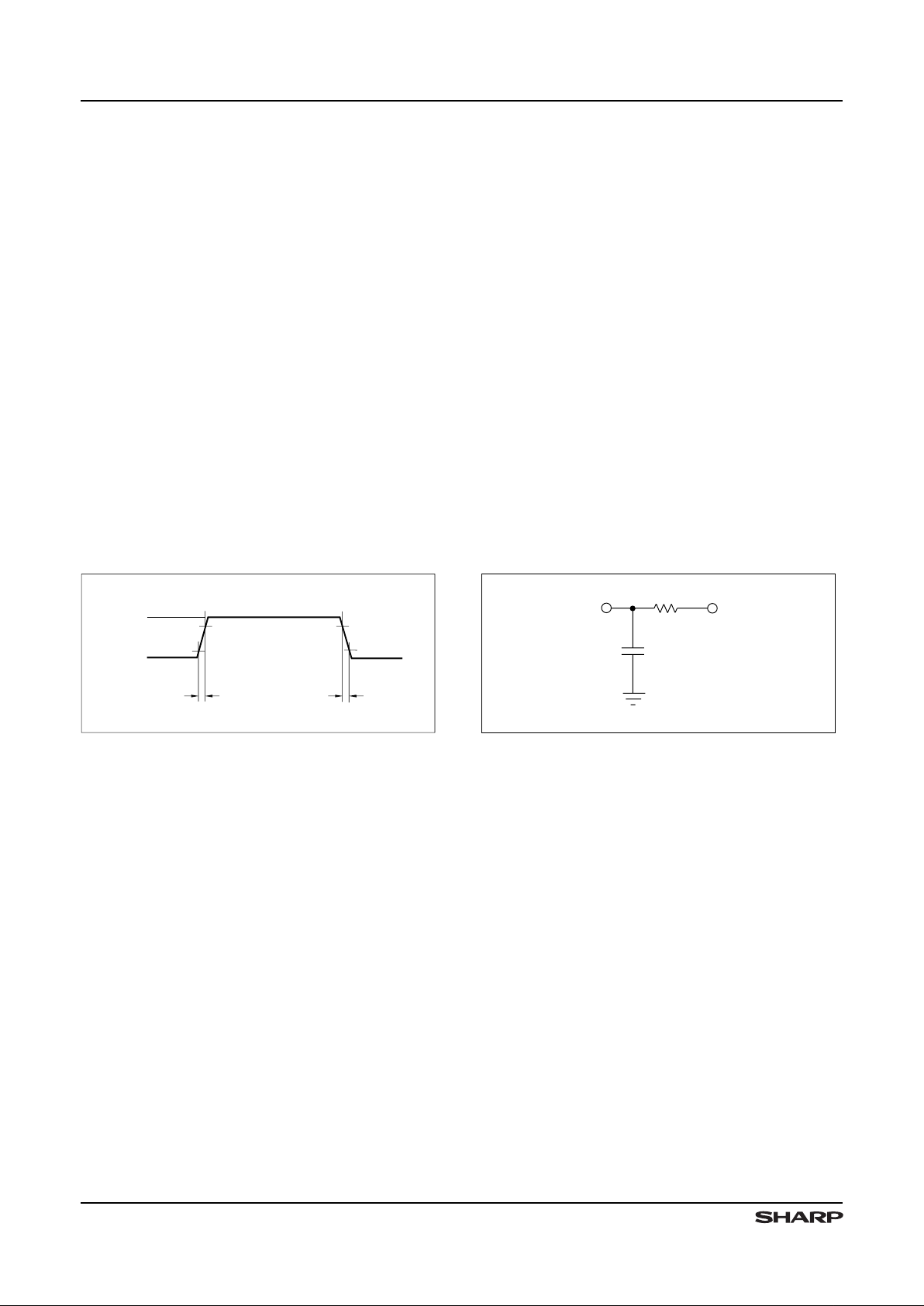

AC TEST CONDIT IO NS

1

PARAMETER RATING

Input Pulse Levels

0 to 3 V

Input Rise a nd Fall Tim es (10% / 90%)

Figure 4a

Input Timing Ref er ence Le vels

1.5 V

Output T iming Ref ere nce Lev e ls

1.5 V

Output Load for AC Timing Tests

Figure 4b

NOTE:

1. All vol tages are measured with respect to Vss.

CAPACITANCE

1,2

PARAMETER DESCRIPTION TEST CONDITIONS RATING

C

IN

Input Capacitanc e

TA = 2 5 °C, f = 1 MHz, VCC = 4.5 V 5 pF

C

OUT

Output Ca pacit ance TA = 2 5oC, f = 1 MHz, Vcc = 4.5 V

7 pF

NOTES:

1. All vol tages are measured with respect to Vss.

2. Sample tested onl y.

167 Ω

1.73 V

DEVICE

UNDER

TEST

CL = 30 pF *

5481-4

* INCLUDES JIG AND SCOPE CAPACITANCES

Figu r e 4b. Output Load Circuit

GND

10%10%

90%

90%

5 ns

5 ns

5481-18

3.0 V

Figur e 4a. Input Rise and Fall Ti mes

LH5481/91 64 × 8 / 64 × 9 FIFO

4

Page 5

AC ELECTRI CAL CHARACTERIS TICS 1 (Over Operating Range)

SYMBOL PARAMETER

15MHz 25MHz 35MHz

UNITS

MIN MAX MIN MAX MIN MAX

f

O

Operating Frequency

2

15 25 35 MHz

t

PHSI

SI HIGH Time

3,8

15 11 9 ns

t

PLSI

SI LOW Time

3,8

20 18 17 ns

t

SSI

Data Setup to SI

4

–1 –1 –1 ns

t

HSI

Data Hold from SI

4

14 12 10 ns

t

DLIR

Delay, SI HIGH to IR LOW 20 18 16 ns

t

DHIR

Delay, SI LOW to IR HIGH 24 20 18 ns

t

PHSO

SO HIGH Time

3

15 11 9 ns

t

PLSO

SO LOW Time

3

20 18 17 ns

t

DLOR

Delay, SO HIGH to OR LOW 20 18 16 ns

t

DHOR

Delay, SO LOW to OR HIGH 24 20 18 ns

t

SOR

Data Setup to OR HIGH –1 –1 –1 ns

t

HSO

Data Hold from SO LOW 0 0 0 ns

t

FT

Fallt hrou gh T im e 36 34 30 ns

t

BT

Bubblethrough Time 28 26 25 ns

t

SIR

Data Setup to IR

5

555ns

t

HIR

Data Hold from IR

5

555ns

t

PIR

Input Ready Pulse HIGH

8

777ns

t

POR

Output Ready Pulse HIGH

8

777ns

t

DLZOE

OE LOW to LOW Z (LH5481)

6,9

35 30 25 ns

t

DHZOE

OE HIGH to HIGH Z (LH5481)

6,9

35 30 25 ns

t

DHHF

SI LOW to HF HIGH 40 40 36 ns

t

DLHF

SO LOW to HF LOW 40 40 36 ns

t

DLAFE

SO or SI LOW to AFE LOW 40 40 36 ns

t

DHAFE

SO or SI LOW to AFE HIGH

40 40 36 ns

t

PMR

MR Pulse Width 35 35 35 ns

t

DSI

MR HIGH to SI HIGH 25 25 22 ns

t

DOR

MR LOW to OR LOW

7

25 25 20 ns

t

DIR

MR LOW to IR HIGH

7

25 25 20 ns

t

LXMR

MR LOW to Output LOW

7

25 25 20 ns

t

AFE

MR LOW to AFE HIGH 30 30 30 ns

t

HF

MR LOW to HF LOW

30 30 30 ns

t

OD

SO LOW to Next Data Out Valid 26 22 20 ns

NOTES:

1. All time measurements performed at ‘AC Test Conditions.’

2. fO = fSI = fSO.

3. t

PHSI

+ t

PLSI

= t

PHSO

+ t

PLSO

= I/fO.

4t

SSI

and t

HSI

apply when memory is not full.

5. t

SIR

and t

HIR

apply when memory is full and SI is HIGH.

6. High-Z transitions are referenced to the steady-state VOH – 500 mV and VOL + 500 mV levels on the output.

7. After reset goes LOW, all Data outputs will be at LOW lev el, IR goes HIGH and O R goes LOW.

8. Common dash number devices are guaranteed by design to function properly in a cascaded configuration.

64 × 8 / 64 × 9 FIFO LH5481/91

5

Page 6

OPERATIONAL DESCRIPTION

Unlike earlier versions of FIFOs, the LH5481 and

LH5491 use dual-port Random-Access-Memory, write

and read pointers, and special control logic. The write

pointe r is incremented by the falling edge of the Shift In

(SI) signal, while the read pointer is incremented by the

falling edge of the Shift O ut ( SO) signal. Th e Input Ready

(IR) signal enables data writing to the FIFO. The Output

Ready (OR) signal indicates valid read information i s

available on the Data Output (DO) pins.

Resetting The FIFO

The FIFO must be rese t, upon power-up, using the

Master Reset (MR) s ig nal. This causes t he FI FO t o enter

an empty state, indicated by the Output Ready (OR) being

LOW and Input Ready (IR) being HIG H. All Data Outp ut

(DO) pins will be LOW in this stat e. The AFE flag will be

HIGH, and the HF flag will be LOW .

If Shi ft In (SI) is HIGH, when the Master Reset (MR)

signal is ended, then t he d ata on the Dat a Input (DI) pins

will be written into the FIFO , and Input Ready (IR ) will

return LOW until Shift In (SI) is brought LOW.

If Shift In (SI) is LOW when the Master Reset (MR) is

deasserte d, then Input Ready (IR) goes HIGH, but the

data on th e Data Input (DI ) pins does not enter the FIFO

until Shift In (SI) goes HIGH.

Shifting Data In

Data Input (DI) is shifted into the FIFO on the rising

edge of Shift In (SI). This loads input data into the FIFO,

and causes Input Ready (I R) to go LOW. When a fal ling

edge of Shift In (SI) occurs,the write pointer i ncrements

to the next word position, and Input Ready (IR) goes

HIGH, indicating that the FIFO is ready to accept new

data. When the FIFO is full, Input Ready (IR) remains

LOW after the negative edge of Shift In (SI) signal; Shift

Out (SO) action is requ ired to unload a word of data and

bring Input Ready (IR) HIGH. (See ‘Bubblethrough Co ndition’ des cript ion. )

Shifting Data Out

Data is shifted out of the FIFO on the falling edge of

Shift Out (SO). The read pointer increments to the next

word locat ion; FIFO dat a, if present, appear s on the Data

Output (DO) pins; and the Outpu t Ready (O R) signal goes

HIGH. If F IFO da ta is n ot present, Output Ready ( OR)

sta ys LOW , in dicating that the FIFO is empty; in this case ,

the last va lid dat a read from the FIFO remains on the Data

Output (DO) pins. When the FIFO is not empty, Output

Rea dy (OR) goes LOW after the rising edge of Shift Out

(SO). The previous dat a remains on the Data Output (DO)

pins until a falling edge of Shift Out (SO).

Fallthro ugh Condition

When the FI FO is empt y , a data word en tering through

the Shift In (SI) action follows one of two seq uence s.

If Shift Out (SO) is LOW, the data propagates to the

Data Ou tpu t (DO) pins; and Output Ready (O R) goes

HIGH and stays HIGH until the next rising edge of Shift

Out (SO).

If Shift Out (SO) is held HIGH while data is shifted into

an emp ty FIFO as occurs i n depth cascading of FIFOs,

dat a propagat es to the Data Outpu t (DO) pins, and Outpu t

Read y ( OR) pulses HIGH for a minimum time duration

specified by t

POR

and then goes back LOW again. The

stor ed word remains on the Data Output (DO) pins. If

mor e words are writt en int o the FIFO, the y line up behind

the fir st word, and do not app ear on the Dat a Outp ut (DO)

pins until Shift Out (SO) has return ed LO W .

Bubblethrough Condition

When the FIF O is full, Shift O ut (SO) action initiates

one of the following two sequences:

If Shif t In (SI ) is LOW , Input Ready (IR) goes HIGH and

sta ys HIG H unt il the next rising edge of Shift In (SI) .

If Shift In (SI) is held HIGH while data is shifted out of

a full FIFO , as occur s in dept h cascading of FIF Os , Input

Ready (IR) pulses HIGH for a minimum time duration

specif ied by t

PIR

, and then goes back LOW again. Special

Data Input (DI) setup and hold times (t

SIR

and t

HIR

,

respectively) are defined for this condition.

LH5481/91 64 × 8 / 64 × 9 F IFO

6

Page 7

TIMING DIAGRAMS

5481-5

SHIFT IN

INPUT READY

DATA IN

AFE

HF

1/fo 1/fo

t

PHSI

t

PLSI

t

DHIR

t

HSI

t

DLAFE

t

SSI

(LOW)

*

t

DLIR

* NOTE: FIFO Contains 8 Words

Figure 5. Data In Tim in g

5481-6

SHIFT OUT

OUTPUT READY

DATA OUT

AFE

HF

1/fo 1/fo

t

PHSO

t

PLSO

t

DHOR

t

HSO

(LOW)

**

t

DLOR

t

SOR

t

DHAFE

** NOTE: FIFO Contains 9 Words

t

OD

Figure 6. Data Out Timing

64 × 8 / 64 × 9 FIFO LH5481/91

7

Page 8

TIMING DIAGRAMS (co nt ’d)

5481-7

SHIFT IN

INPUT READY

DATA IN

AFE

HF

1/fo 1/fo

t

PHSI

t

PLSI

t

DHIR

t

SSI

(LOW)

***

t

DLIR

t

DHHF

t

HSI

*** NOTE: FIFO Contains 31 Words

Figure 7. Data In Tim in g

5481-8

SHIFT OUT

OUTPUT READY

DATA OUT

HF

AFE

1/fo 1/fo

t

PHSO

t

PLSO

t

DHOR

t

HSO

t

DLHF

(LOW)

****

t

DLOR

t

SOR

**** NOTE: FIFO Contains 32 Words

t

OD

Figure 8. Data Out Timing

LH5481/91 64 × 8 / 64 × 9 FIFO

8

Page 9

TIMING DIAGRAMS (co nt ’d)

5481-9

SHIFT IN

INPUT READY

DATA IN

HF

AFE

1/fo 1/fo

t

PHSI

t

PLSI

t

DHIR

t

SSI

(HIGH)

*****

t

DLIR

t

DHAFE

t

HSI

***** NOTE: FIFO Contains 55 Words

Figure 9. Data In Tim in g

5481-10

SHIFT OUT

OUTPUT READY

DATA OUT

1/fo 1/fo

t

PHSO

t

PLSO

t

DHOR

t

HSO

t

DLAFE

(HIGH)

******

t

DLOR

t

SOR

AFE

HF

****** NOTE: FIFO Contains 56 Words

t

OD

Figure 10. Data Out Timin g

64 × 8 / 64 × 9 FIFO LH5481/91

9

Page 10

TIMING DIAGRAMS (co nt ’d)

5481-11

SHIFT OUT

SHIFT IN

INPUT READY

t

PIR

DATA IN

t

HIR

t

SIR

t

BT

Figure 11. Bubblethroug h Timing (Readi ng a Ful l FIFO)

5481-12

SHIFT OUT

SHIFT IN

OUTPUT READY

t

POR

DATA OUT

t

FT

t

SOR

Figure 12. Fallthro ugh Ti ming (W riti ng an Empty FIFO)

LH5481/91 64 × 8 / 64 × 9 FIFO

10

Page 11

TIMING DIAGRAMS (co nt ’d)

5481-13

MASTER RESET

INPUT READY

OUTPUT READY

SHIFT IN

t

DIR

t

PMR

t

DOR

t

LXMR

t

DHF

t

DAFE

t

DSI

DATA OUT

HF

AFE

Figure 13. Master Reset Timing

64 × 8 / 64 × 9 FIFO LH5481/91

11

Page 12

TIMING DIAGRAMS (co nt ’d)

5481-14

SHIFT IN

. . . . . . . . .

. . .

EMPTY

HF

AFE

2

1

8

9

10

31

32

33

55

56

57

64

FULL

Figur e 14. Shifti ng Words I n

5481-15

SHIFT OUT

. . . . . . . . .

. . .

EMPTY

HF

AFE

1

31

32

30

FULL

7

8

9

54

55

56

63

64

Figure 15. Shifting Words Out

LH5481/91 64 × 8 / 64 × 9 FIFO

12

Page 13

FIFO EXP A NS ION

5481-16

IR

SI

DI

0

DI

1

DI

2

DI

3

DI

4

DI

5

DI

6

DI

7

DI

8

SO

OR

DO

0

DO

1

DO

2

DO

3

DO

4

DO

5

DO

6

DO

7

DO

8

256 x 8/9

MR

IR

SI

DI

0

DI

1

DI

2

DI

3

DI

4

DI

5

DI

6

DI

7

DI

8

SO

OR

DO

0

DO

1

DO

2

DO

3

DO

4

DO

5

DO

6

DO

7

DO

8

64 x 8/9

MR

IR

SI

DI

0

DI

1

DI

2

DI

3

DI

4

DI

5

DI

6

DI

7

DI

8

SO

OR

DO

0

DO

1

DO

2

DO

3

DO

4

DO

5

DO

6

DO

7

DO

8

256 x 8/9

MR

IR

SI

DI

0

DI

1

DI

2

DI

3

DI

4

DI

5

DI

6

DI

7

DI

8

SO

OR

DO

0

DO

1

DO

2

DO

3

DO

4

DO

5

DO

6

DO

7

DO

8

64 x 8/9

MR

IR

SI

DI

0

DI

1

DI

2

DI

3

DI

4

DI

5

DI

6

DI

7

DI

8

SO

OR

DO

0

DO

1

DO

2

DO

3

DO

4

DO

5

DO

6

DO

7

DO

8

256 x 8/9

MR

IR

SI

DI

0

DI

1

DI

2

DI

3

DI

4

DI

5

DI

6

DI

7

DI

8

SO

OR

DO

0

DO

1

DO

2

DO

3

DO

4

DO

5

DO

6

DO

7

DO

8

64 x 8/9

MR

HF/AFE

HF/AFE

SHIFT OUT

MR

SHIFT IN

COMPOSITE

INPUT READY

COMPOSITE

OUTPUT READY

Figure 16. 320 × 24/27 Conf iguration

Using 64 × 8/9 (LH5481/ 91) & 256 × 8/9 (LH5485/95) FIFOs

64 × 8 / 64 × 9 FIFO LH5481/91

13

Page 14

FIF O EX PANSION ( con t’d)

FIFOs are expandable in depth and width. H owever,

in for ming wider words, exter nal logic is required to generate c omposite Input Ready and Output Ready flags.

This is due to the variation of delays of the FIFOs. For

example, the circu it of Figure 16 uses sim ple A ND gates

as the external IR and OR gener ators. More complex logic

may be required if fallthrough and bubblethrough pulses

are needed by the external sys te m.

FIFOs can be easi ly cascaded to any desired depth,

as illustrated in Figure 17. The handshaking and associated t iming bet ween t he FIFO s are ha n dled b y the inhe rent timing of the devices.

NOTE S:

1. When the memory is empty, the last word read remains on the outputs until Master Reset is strobed, or a new data word bubbles

through to the output. However , OR remains LOW, indicating

that the data word at the output is not valid .

2. When the output data word changes as a result of a pulse on SO,

the OR signal always goes LOW before the output data word

changes and stays LOW until a new data word has appeared at

the outputs. Anytime OR is HIGH, there is valid stable data on

the out put s.

3. All SHA RP FIFOs can be cascaded with ot her SHAR P FIFOs of

the sam e architecture (i. e., 64 × 8/9 with 64 × 8/9). However,

they may not cascade with FIFOs from other manufacturers.

5481-17

SI

IR

DI

0

DI

1

DI

2

DI

3

DI

4

DI

5

DI

6

DI

7

DI

8

OR

SO

DO

0

DO

1

DO

2

DO

3

DO

4

DO

5

DO

6

DO

7

DO

8

256 x 8/9

MR

SI

IR

DI

0

DI

1

DI

2

DI

3

DI

4

DI

5

DI

6

DI

7

DI

8

OR

SO

DO

0

DO

1

DO

2

DO

3

DO

4

DO

5

DO

6

DO

7

DO

8

64 x 8/9

MR

HF/AFE

SHIFT IN

INPUT READY

DATA IN

OUTPUT READY

SHIFT OUT

DATA OUT

MR

HF/AFE

Figure 17 . 128 × 8/9 Confi guration

LH5481/91 64 × 8 / 64 × 9 FIFO

14

Page 15

PACKAGE DIAGRAMS

28SK-DIP (DIP028-P-0300)

DIMENSIONS IN MM [INCHES]

MAXIMUM LIMIT

MINIMUM LIMIT

114

1528

28DIP-1

7.05 [0.278]

6.65 [0.262]

0.51 [0.020] MIN.

4.40 [0.173]

4.00 [0.157]

3.40 [0.134]

3.00 [0.118]

2.54 [0.100]

TYP.

0.56 [0.022]

0.36 [0.014]

0.35 [0.014]

0.15 [0.006]

DETAIL

35.00 [1.378]

34.40 [1.354]

0° TO 15°

3.65 [0.144]

3.25 [0.128]

7.62 [0.300]

TYP.

28-pin, 300-mil PDIP

28PLCC

MAXIMUM LIMIT

MINIMUM LIMIT

DIMENSIONS IN MM [INCHES]

28PLCC (PLCC28-P-S450)

1.27 [0.050] BASIC

NON-ACCUM

12.57 [0.495]

12.32 [0.485]

0.10 [0.004]

1.22 [0.048]

1.07 [0.042]

x 45°

12.57 [0.495]

12.32 [0.485]

0.51

[0.020]

MIN.

10.92 [0.430]

9.91 [0.390]

DETAIL

11.56 [0.455]

11.43 [0.450]

11.56 [0.455]

11.43 [0.450]

0.81 [0.032]

0.66 [0.026]

2.79 [0.110]

2.52 [0.099]

0.53 [0.021]

0.33 [0.013]

4.57 [0.180]

4.19 [0.165]

28-pin, 450-mil PLCC

64 × 8 / 64 × 9 FIFO LH5481/91

15

Page 16

ORDERING INFO RMATION

LH####

Device Type

X

Package

- ##

Speed

Examples:

LH5481D-25 (64 x 8 FIFO, 28-pin, 300-mil PDIP, 25 MHz)

LH5491U-35 (64 x 9 FIFO, 28-pin PLCC, 35 MHz)

5481MD

D 28-pin, 300-mil PDIP (DIP028-P-0300)

U 28-pin Plastic Leaded Chip Carrier (PLCC28-P-S450)

5481 64 x 8 FIFO

5491 64 x 9 FIFO

15

25 Frequency (MHz)

35

LH5481/91 64 × 8 / 64 × 9 FIFO

16

Loading...

Loading...