Page 1

LH53B16R00

CMOS 16M (1M × 16/51 2K × 32) MROM

FEATURES

•• 1,048,5 76 × 16 bit organization

(Word mode: W = VIL)

524,288 × 32 bit organization

(Double Word mode: W = VIH)

•• Access time: 120 ns (MAX.)

Access time in page mode : 50 ns (MAX.)

•• Supply curre nt :

– Operating: 180 mA (MAX.)

– Standby: 300 µA (MAX.)

•• TTL compatible I/O

•• Three-state outputs

•• Singl e +5 V p owe r su ppl y

•• Static operation

•• Packa ge:

70-pi n , 500 -mil SSOP

•• Others:

– Non prog rammab le

– Not de sign ed o r ra ted a s rad iation

– harden ed

– CMOS process (P typ e sil icon

substrate)

DESCRIPTION

The LH53B16R00 is a 16M-bit CMOS mask ROM

(mask-programmable-read-only mem ory) organized as

1,048,576 × 16 bits (Word mode) or 524,288 × 32 bits

(Double Word mode). It is fabricated using silicon-gate

CMOS process technology.

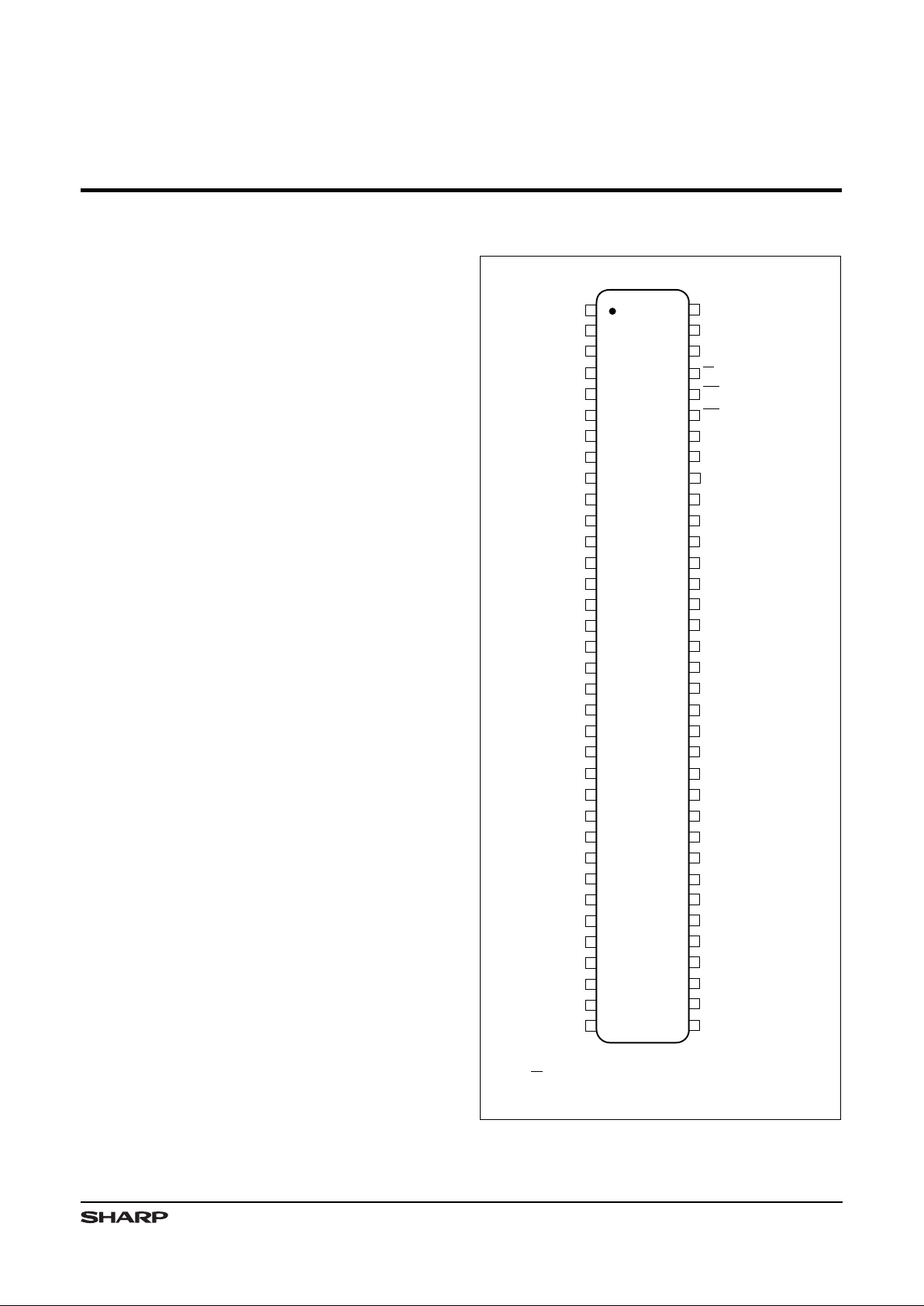

PIN CONNECTIONS

53B16R00-1

TOP VIEW

2

3

4

5

8

9

D

0

A

4

67

66

65

64

63

62

59

56

A

2

A

3

6

7V

CC

V

CC

A

5

61

60

W

OE

GND

D

15

D

13

10

11

12

69

68 NC

D

16

13 58

D

29

V

CC

GND

57

GND

D

1

CE

70-PIN SSOP

14

15

16

17

18

19

20

21

53

50

55

54

52

51

D

12

D

27

D

11

D

26

D

20

D

5

D

4

D

3

D

18

D

19

D

2

D

21

GND GND

D

31/A-1

(NOTE)

D

30

D

28

NC701

A

1

A

0

22 49

D

10

D

17

D

14

NC

46

43

48

47

V

CC

23

24

25

26 45

D

8

D

24

D

9

44

V

CC

27

28

29

30

31

32

33

34

40

37

42

41

39

38

A

18

A

17

A

16

A

15

A

9

A

10

A

8

A

6

A

7

GND

A

11

A

12

V

CC

NC

35 36

A

14

A

13

D

6

D

7

D

23

D

22

D

25

NOTE: D31/A-1 pin becomes LSB address input (A-1) when the

W pin is set to be LOW in word mode, and data output

(D

31

) when set to be HIGH in double word mode.

Figure 1. Pin Connecti ons

1

Page 2

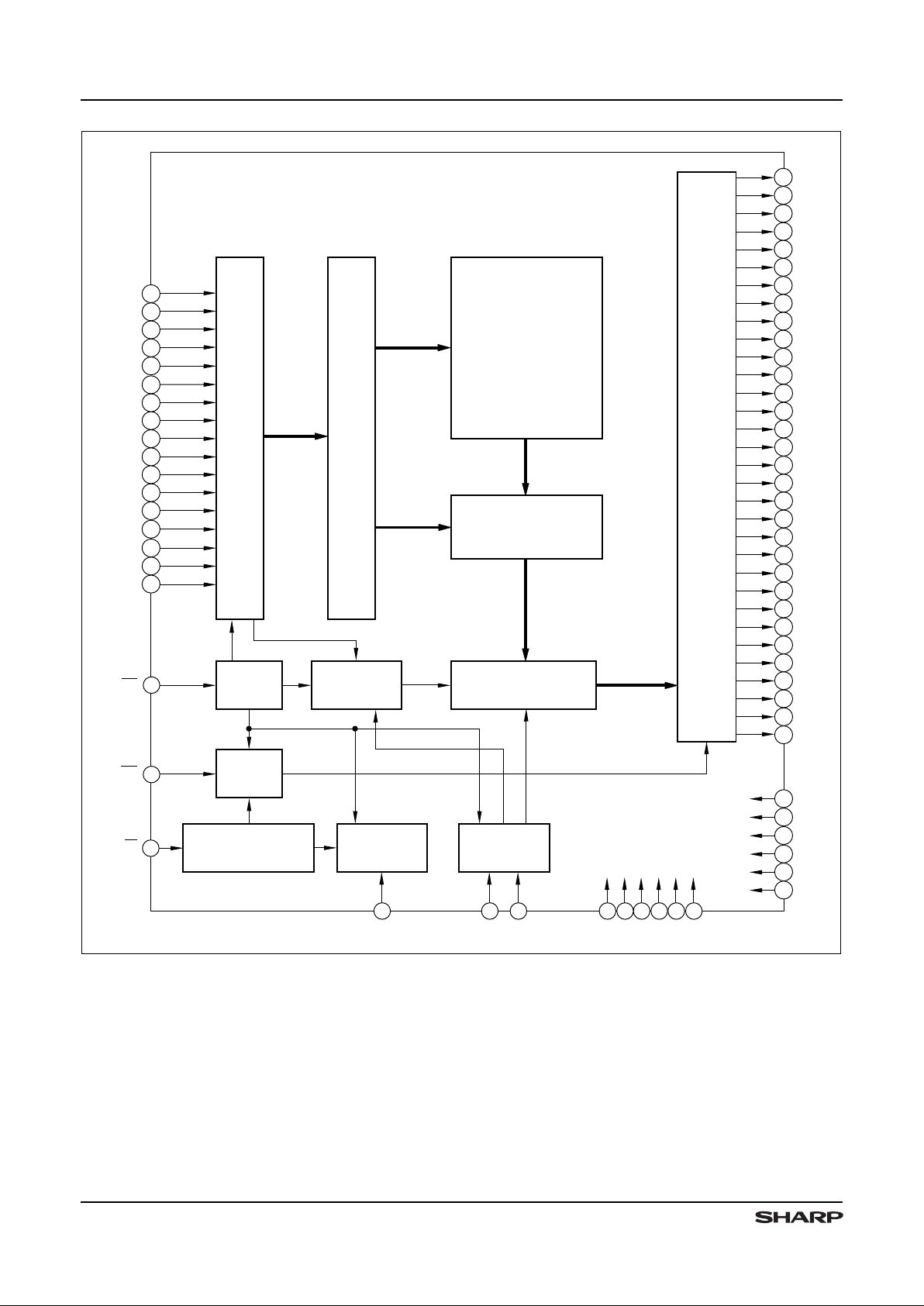

53B16R00-2

A

3

A

2

A

12

A

11

A

10

A

9

A

8

35

34

33

32

29

4

3

A

7

A

6

A

4

MEMORY

MATRIX

(1,048,576 x 16)

(524,288 x 32)

SENSE AMPLIFIER

30

67

5

31

A

5

6

A

13

36

ADDRESS BUFFER

CE

ADDRESS DECODER

COLUMN SELECTOR

CE

BUFFER

OE

BUFFER

A

14

37

A

15

38

65

TIMING

GENERATOR

A

16

39

W

A

17

40

A

18

41

ADDRESS

BUFFER

WORD/DOUBLE

WORD SWITCHOVER

CIRCUIT

66

OE

ADDRESS

BUFFER

DATA SELECTOR/OUTPUT BUFFER

D

3

D

2

D

1

D

7

D

6

D

4

D

5

D

0

20

14

10

8

59

16

26

D

8

44

D

9

46

18

24

D

13

D

12

D

11

D

17

D

16

D

14

D

15

D

10

62

54

52

50

56

11

D

18

15

D

19

17

60

9

D

23

D

22

D

21

D

27

D

26

D

24

D

25

D

20

47

25

21

19

27

53

D

28

55

D

29

57

D

30

61

D

31

63

45

51

63

A

-1

A

0

1

A

1

2

V

CC

GND

48

64

49

28

22

12

5823 437 13

Figure 2. LH53B16R00 Block Diagram

LH53B16 R00 CMOS 1 6M (1 M x 16/512 K x 32) MROM

2

Page 3

TRUTH TABLE

CE OE W

A

-1

(D31)

DATA OUTPUT ADDRESS INPUT

SUPPLY

CURRENT

D

0

- D

15

D16 - D

31

LSB MSB

H X X X High-Z High-Z Standby (ISB)

L H X X High-Z High-Z

Operating

LL H

D

0

- D

15D16

- D

31

A

0

A

18

Operating

LL L L D

0

- D

15

High-Z A

-1

A

18

Operating

LL L H D

16

- D

31

High-Z A

-1

A

18

Operating

NOTE:

X = Don’t care; High-Z = High-impedance

ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL RATING UNIT

Suppl y v olt age V

CC

-0.3 to +7.0 V

Input vol tage V

IN

-0.3 to VCC + 0.3 V

Output vo lta ge V

OUT

-0.3 to VCC + 0.3 V

Operat ing te mpe ratu re T

OPR

0 to +70

°C

Storag e t emp era ture T

STG

-65 to +150

°C

RECOMMENDED OPERATING CON DITIONS (TA = 0 to +7 0°C)

PARAMETER SYMBOL MIN. TYP. MAX. UNIT

Suppl y v olt age V

CC

4.5 5.0 5.5 V

PIN DESCRIPTION

SIGNA L PIN N AME

A

-1

- A

1

Addr ess in put

(pag e mo de ope rat ion )

A

2

- A

18

Addr ess in put

D

0

- D

31

Data ou tput

W

×16 b it / ×32 bit

(word /do ubl e w ord )

mode se lec t in put

SIGNA L PIN NAM E

CE Chip ena ble in put

OE

Outpu t e nab le i np ut

V

CC

Power pi n (+ 5 V)

GND

Groun d

NC No co nne cti on

CMOS 16M (1M x 16/512K x 32) MROM LH53B16R00

3

Page 4

DC ELECTRICAL CHARACTERISTICS (VCC = 5 V ± 10%, TA = 0 to +70°C)

PARAMETER SYMBOL CONDITIONS MIN. MAX. UNIT NOTE

Input ‘Hi gh’ voltage V

IH

2.2 V

CC

+0.3 V

Input ‘Lo w’ voltage V

IL

-0.3 0.8 V

Output ‘H igh ’ vol tag e V

OH

IOH = -400 µA

2.4

V

Output ‘L ow’ v olt age V

OL

IOL = 2 .0 mA

0.4 V

Input leakage current | I

LI

|VIN = 0 V to V

CC

10

µA

Output le aka ge cur ren t

| ILO |

V

OUT

= 0 V to V

CC

10 µA1

Operat ing cu rre nt I

CC1

tRC = 12 0 n s

180 mA 2

Standb y c urr ent

I

SB1

CE = V

IH

2mA

I

SB2

CE = VCC - 0.2 V

300

µA

Input cap acitan ce C

IN

f = 1 MHz , tA = 25°C

10 pF

Output ca pac ita nce

C

OUT

10 pF

NOTES:

1. CE = VIH, OE = VIH, output is open

2. VIN = VIH, VIL, CE = VIL, output is open

AC ELECTRICAL CHARACTERISTICS (V

CC

= 5 V ±10%, TA = 0 t o +70°C)

PARAMETER SYMBOL M IN. MAX. UNIT NOTE

Read c yc le t ime t

RC

120

ns

Addres s a cc ess ti me t

AA

120 ns

Chip e nab le acc es s ti me

t

ACE

120 ns

Page a ddr ess ac ce ss time t

APA

50 ns

Output en abl e d ela y t ime t

OE

50 ns

Output ho ld time t

OH

5

ns

Output fl oat ing tim e

t

CHZ

40 ns

1

t

OHZ

40 ns

NOTE:

1. Determ ined by the time f or the output to be opened. (Irrespective of out put voltage)

AC TEST CONDITIONS

PARAMETER R ATING

Input voltage amplitude 0.4 V to 2.6 V

Input sig nal rise time 10 ns

Input sig nal fall time 10 ns

Input/ out put ref ere nce le vel 1.5 V

Output load condition 1TTL + 100 pF

LH53B16 R00 CMOS 1 6M (1 M x 16/512 K x 32) MROM

4

Page 5

t

AA

A2 - A

18

53B16R00-4

t

ACE

CE

(NOTE)

(NOTE)

OE

t

OE

(NOTE)

A

-1

- A

1

t

APA

(NOTE)

DATA

VALID

t

APA

(NOTE)

t

CHZ

t

OHZ

t

OH

t

OH

t

OH

t

OH

DATA

VALID

DATA

VALID

DATA

VALID

(A

0

- A1)

D

0

- D

15

(D0 - D31)

NOTE: The output data becomes valid when the

last intervals, t

AA

, t

ACE

, t

APA

, or tOE, have concluded.

Figure 4. Page Mode Read Cycle

t

AA

A

-1

- A

18

t

OHZ

t

CHZ

D0 - D

15

53B16R00-3

t

RC

t

ACE

CE

DATA VALID

(NOTE)

(NOTE)

OE

t

OE

(NOTE)

(A0 - A18)

(D

0

- D31)

t

OH

NOTE: The output data becomes valid when the

last intervals, t

AA

, t

ACE

, t

APA

, or tOE, have concluded.

Figure 3. Read Cycle

CMOS 16M (1M x 16/512K x 32) MROM LH53B16R00

5

Page 6

LH53B16R00

Device Type

N

Package

53B16R00-5

Example: LH53B16R00N (CMOS 16M (1M x 16 or 500K x 32) Mask-Programmable ROM, 70-pin, 500-mil SSOP)

CMOS 16M (1M x 16 or 500K x 32) Mask-Programmable ROM

with page mode operation

70-pin, 500-mil SSOP (SSOP70-P-500)

ORDERING INFORMATION

DIMENSIONS IN MM [INCHES]

MAXIMUM LIMIT

MINIMUM LIMIT

70SSOP (SSOP70-P-500)

16.20 [0.638]

15.60 [0.614]

12.90 [0.508]

12.50 [0.492]

14.60 [0.575]

14.00 [0.551]

28.8 [1.134]

28.4 [1.118]

0.15 [0.006]

1.275 [0.050]

0.20 [0.008]

0.00 [0.000]

1.275 [0.050]

2.9 [0.114]

2.5 [0.098]

0.20 [0.008]

0.10 [0.004]

0.40 [0.015]

0.20 [0.008]

.08 [0.003]

TYP.

70

36

351

70SSOP

2.9 [0.114]

2.5 [0.098]

1.275 [0.050]

0.25 [0.010]

0.05 [0.002]

0 - 10°

SEE

DETAIL

DETAIL

0.10 [0.004]

0.15 [0.006]

M

PACKAGE DIAGRAM

LH53B16 R00 CMOS 1 6M (1 M x 16/512 K x 32) MROM

6

Loading...

Loading...