Page 1

LH53259

CMOS 256K (32K × 8) MROM

FEATURES

•• 32,768 words × 8 bit organ ization

•• Access time: 150 ns (MAX.)

•• Low-power consumption:

Operating: 137.5 mW (MAX.)

Standby: 550 µW (MAX.)

•• Programmab le o utput enable

•• Static operatio n

•• TTL compa tible I/O

•• Three-state outpu ts

•• Si ngl e +5 V pow e r supp ly

•• Pa ckage s :

28-pin , 600-mil DIP

28-pin , 450-mil SOP

28-pin , 8 × 13 .4 m m

2

TSOP (Type I)

•• JEDEC s tandard EPROM pinout (DIP)

DESCRIPTION

The LH53259 is a mask-programmable RO M organized as 32,768 × 8 bits. It is fabricated using silicon-gate

CMOS process technology.

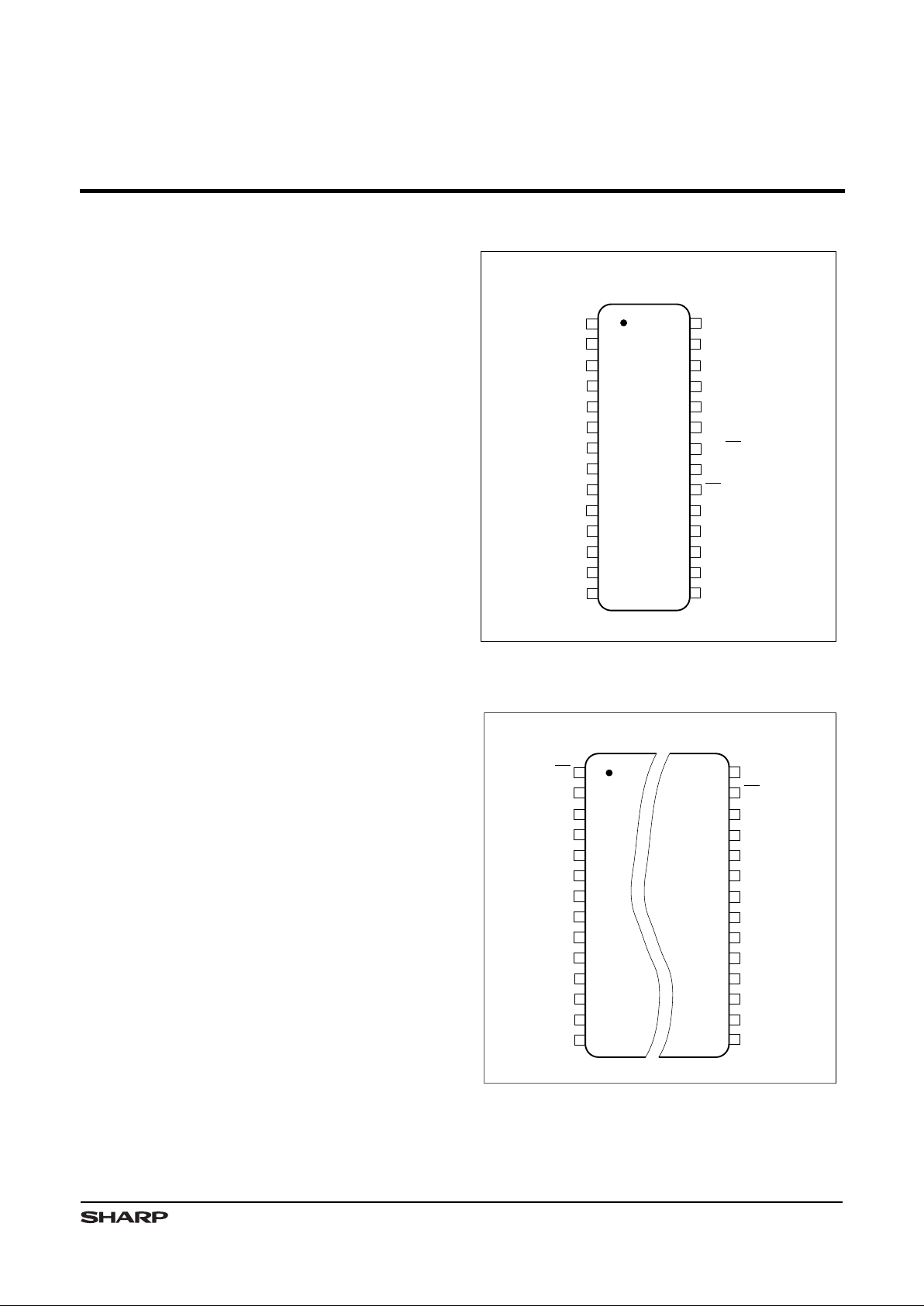

PIN CONNECTIONS

53259-1

TOP VIEW

28-PIN DIP

28-PIN SOP

1

2

3

4

7

8

A

2

A

5

26

25

24

23

22

21

18

15

A

7

A

6

5

6

A

3

A

4

20

19

A

12

GND

A

13

A

8

A

11

A

10

CE

D

7

D

6

D

3

9

10

11

28

27

A

14

A

1

V

CC

12

17

D

5

16

D

4

D

1

D

2

A

0

D

0

A

9

13

14

NC

OE/OE

Figure 1. Pin Connections for DI P and

SOP Packages

1

2

3

4

7

8

NC

A

13

26

25

24

23

22

21

18

15

A

9

A

8

5

6

V

CC

A

14

20

19

OE/OE

A

11

D

7

D

6

D

4

GND

D

1

D

0

A

2

9

10

11

28

27

CE

A

12

A

10

12

17

A

0

16

A

1

A

5

A

4

A

7

A

6

D

5

13

14

D

3

53259-7

TOP VIEW28-PIN TSOP (Type I)

A

3

D

2

Figure 2. Pin Connections for TSOP Package

1

Page 2

NOTE:

1. The active level of OE/OE is mask-programm able.

TRUTH TABLE

CE OE/OE MODE D0 - D

7

SUPPLY CURRENT NOTE

HX

Non selected High-Z

Standby 1

L

L/H

Operating

H/L Selected D

OUT

NOTE:

1. X = H or L

ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL RATING UNIT

Suppl y v olt age V

CC

–0.3 to +7.0 V

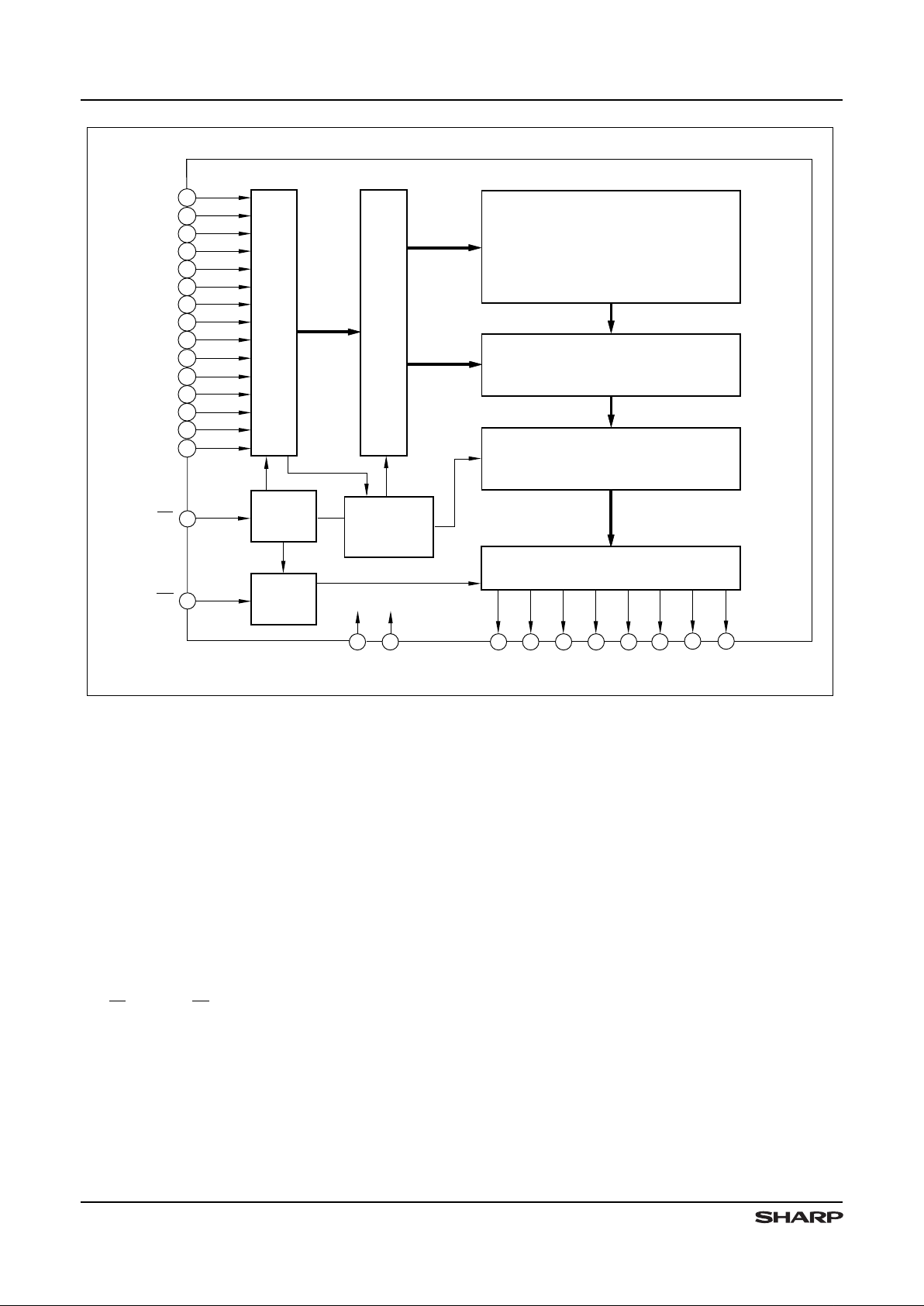

53259-2

A

3

A

2

A

1

A

12

A

11

A

10

A

9

A

8

28

2

23

21

24

4

7

8

A

7

A

6

V

CC

A

4

16

17

181119

D

0

MEMORY

MATRIX

(32,768 x 8)

SENSE AMPLIFIER

14

3

GND

D

1D2D3D4D5D6D7

22

1512

13

6

25

A

5

5

A

13

26

OE/OE

ADDRESS BUFFER

CE

A

0

ADDRESS DECODER

COLUMN SELECTOR

CE

BUFFER

OE

BUFFER

A

14

27

20

TIMING

GENERATOR

NOTE: Pin numbers apply to the 28-pin DIP or SOP.

9

10

OUTPUT BUFFER

Figure 3. LH53259 Block Diagram

PIN DESCRIPTION

SIGNAL PIN NAME NOTE

A0 – A

14

Addres s i npu t

D

0

– D

7

Data o utp ut

CE Chip e nab le inp ut

OE/

OE Output en abl e i npu t 1

SIGNAL PIN NAME NOTE

V

CC

Power sup ply (+ 5 V)

GND

Ground

NC No conne cti on

LH53259 CMOS 256K MROM

2

Page 3

Input vol tage V

IN

–0.3 to VCC +0.3 V

Output vo lta ge V

OUT

–0.3 to VCC +0.3 V

Operat ing te mpe ratu re

Topr 0 to +70 °C

Storag e t emp era ture

Tstg –55 to +150 °C

RECOMMENDED OPERATING CONDITIO NS (T

A

= 0 to +70°C)

PARAMETER SYMBOL MI N. TYP. MAX. UNIT

Suppl y v olt age V

CC

4.5 5.0 5.5 V

DC CHARACTERISTICS (VCC = 5 V ± 10%, TA = 0 t o +70°C)

PARAMETER SYMBOL CONDITIONS MIN. TYP. MAX. UNIT NOTE

Input ‘Lo w’ voltage V

IL

–0.3 0.8 V

Input ‘Hi gh’ voltage V

IH

2.2 VCC + 0.3 V

Output ‘L ow’ v olt age V

OL

IOL = 1 .6 m A 0.4 V

Output ‘H igh ’ vol tag e

V

OH

IOH = –4 00 µA 2.4 V

Input lea kag e c urr ent

| I

LI

|

V

IN

= 0 V to V

CC

10 µA

Output le aka ge cur ren t

| I

LO

|

V

OUT

= 0 V to V

CC

10 µA1

Operat ing cu rre nt

I

CC1

tRC = 15 0 n s 25

mA 2

I

CC2

tRC = 1 µs

20

I

CC3

tRC = 15 0 n s 20

mA 3

I

CC4

tRC = 1 µs15

Standb y c urr ent

I

SB1

CE = V

IH

2mA

I

SB2

CE = VCC – 0.2 V 100 µA

Input cap acitan ce C

IN

f = 1 MHz

T

A

= 25°C

10 pF

Output ca pac ita nce C

OUT

10 pF

NOTES:

1. CE/OE = VIH or OE = V

IL

2. VIN = VIH/VIL, CE = VIL, outputs open

3. V

IN

= ( VCC – 0.2 V) or 0.2 V, CE = 0.2 V, outputs open

AC CHARACTERISTICS (V

CC

= 5 V ±10%, TA = 0 to +70°C)

PARAMETER SYMBOL MIN. TYP. MAX. UNIT NOTE

Read c yc le t ime t

RC

150 ns

Addres s a cc ess ti me t

AA

150 ns

Chip e nab le acc es s ti me t

ACE

150 ns

Output en abl e t ime

t

OE

10 80 ns

Output ho ld time t

OH

5ns

CE to out put in Hig h-Z t

CHZ

70 ns

1

OE to out put in Hig h-Z t

OHZ

70 ns

NOTE:

1. This is the time require d for the output to become high impedance.

CMOS 256K MROM LH53259

3

Page 4

AC TEST CONDITIONS

PARAMETE R RATING

Input voltage amplitude 0.6 V to 2.4 V

Input rise/fall time 10 ns

Input ref erence level 1.5 V

Output reference level 0.8 V and 2.2 V

Output load condition 1TTL + 100 pF

t

AA

(NOTE)

A0 - A

14

t

OHZ

t

CHZ

D0 - D

7

53259-3

t

RC

t

ACE

CE

OE

t

OH

DATA VALID

OE

NOTE: Data becomes valid after the intervals t

AA

, t

ACE

, and tOE from address

inputs, chip enable and output enable, respectively have been met.

(NOTE)

(NOTE)

t

OE

Figure 4. Timin g Diagram

LH53259 CMOS 256K MROM

4

Page 5

PACKAGE DIAGRAMS

DIMENSIONS IN MM [INCHES]

MAXIMUM LIMIT

MINIMUM LIMIT

28DIP (DIP028-P-0600)

114

1528

28DIP-2

13.45 [0.530]

12.95 [0.510]

0.51 [0.020] MIN.

5.20 [0.205]

5.00 [0.197]

3.50 [0.138]

3.00 [0.118]

2.54 [0.100]

TYP.

0.60 [0.024]

0.40 [0.016]

0.30 [0.012]

0.20 [0.008]

DETAIL

36.30 [1.429]

35.70 [1.406]

0° TO 15°

4.50 [0.177]

4.00 [0.157]

15.24 [0.600]

TYP.

28-pin, 600-mil DIP

DIMENSIONS IN MM [INCHES]

MAXIMUM LIMIT

MINIMUM LIMIT

28SOP (SOP028-P-0450)

12.40 [0.488]

11.60 [0.457]

8.80 [0.346]

8.40 [0.331]

10.60 [0.417]

18.20 [0.717]

17.80 [0.701]

0.15 [0.006]

1.025 [0.040]

0.20 [0.008]

0.00 [0.000]

1.025 [0.040]

2.40 [0.094]

2.00 [0.079]

0.20 [0.008]

0.10 [0.004]

0.50 [0.020]

0.30 [0.012]

1.27 [0.050]

TYP.

28 15

141

1.70 [0.067]

1.70 [0.067]

28SOP

28-pin, 450-mil SOP

CMOS 256K MROM LH53259

5

Page 6

DIMENSIONS IN MM [INCHES]

MAXIMUM LIMIT

MINIMUM LIMIT

28TSOP (TSOP028-P-0813)

28

1

28TSOP

14

15

0.28 [0.011]

0.12 [0.005]

0.55 [0.022]

TYP.

12.00 [0.472]

11.60 [0.457]

13.70 [0.539]

13.10 [0.516]

8.20 [0.323]

7.80 [0.307]

0.15 [0.006]

1.10 [0.043]

0.90 [0.035]

1.20 [0.047]

MAX.

12.60 [0.496]

12.20 [0.480]

0.20 [0.008]

0.10 [0.004]

0.20 [0.008]

0.00 [0.000]

1.10 [0.043]

0.90 [0.035]

0.425 [0.017]

0.20 [0.008]

0.00 [0.000]

0 - 10°

DETAIL

0.425 [0.017]

28- pin, 8 × 13.4 mm2 TSOP (Type I)

D 28-pin, 600-mil DIP (DIP028-P-0600)

N 28-pin, 450-mil SOP (SOP028-P-0450)

T 28-pin, 8 x 13.4 mm

2

TSOP (Type I) (TSOP028-P-0813)

LH53259

Device Type

X

Package

53259-6

Example: LH53259D (CMOS 256K (32K x 8) Mask Programmable ROM, 28-pin, 600-mil DIP)

CMOS 256K (32K x 8) Mask Programmable ROM

ORDERING INFORMATION

LH53259 CMOS 256K MROM

6

Loading...

Loading...