Datasheet LH5164AT-80L, LH5164AT-10L, LH5164AN-80L, LH5164AN-10L, LH5164AHT-10L Datasheet (Sharp)

...Page 1

LH5164A/AH

CMOS 6 4K (8 K × 8) S tatic RA M

FEATURES

•• 8,192 × 8 bit orga niza ti on

•• Access times: 80/10 0 n s (MAX.)

•• Low-pow er consumption :

Operating :

303 mW (MAX.) LH5164A/D/N

@ 80 ns

248 mW (MAX.) LH5164A/D/N/T

@ 100 ns

275 mW (MAX.) LH5164AH/HD/H N/HT

@ 100 ns

Standby:

LH5164A/D/N/T: 5.5 µW (MAX.)

LH5164AH/HD/HN/HT:

T

A

≤ 85°C: 16.5 µW (MAX.)

T

A

≤ 70°C: 5.5 µW (MAX.)

•• Fully-static operatio n

•• Three-state outputs

•• Singl e +5 V p owe r su ppl y

•• TTL compatible I/O

•• Wide temp erature ra nge avail abl e

LH5164 A: -10 to +70°C

LH5164AH: -40 to +85°C

•• Packages:

28-pi n , 600 -mil DIP

28-pi n , 300 -mil SK-DIP

28-pi n , 450 -mil S OP

28-pi n , 8 × 13 mm

2

TSOP (Type I)

DESCRIPTION

The LH5164A/AH ar e static RAMs organized as 8,192

× 8 bits. It is f abricated using silicon-gate CMOS pr ocess technology.

The LH5164AH is designed for wide temperature

range from -40 to +85°C.

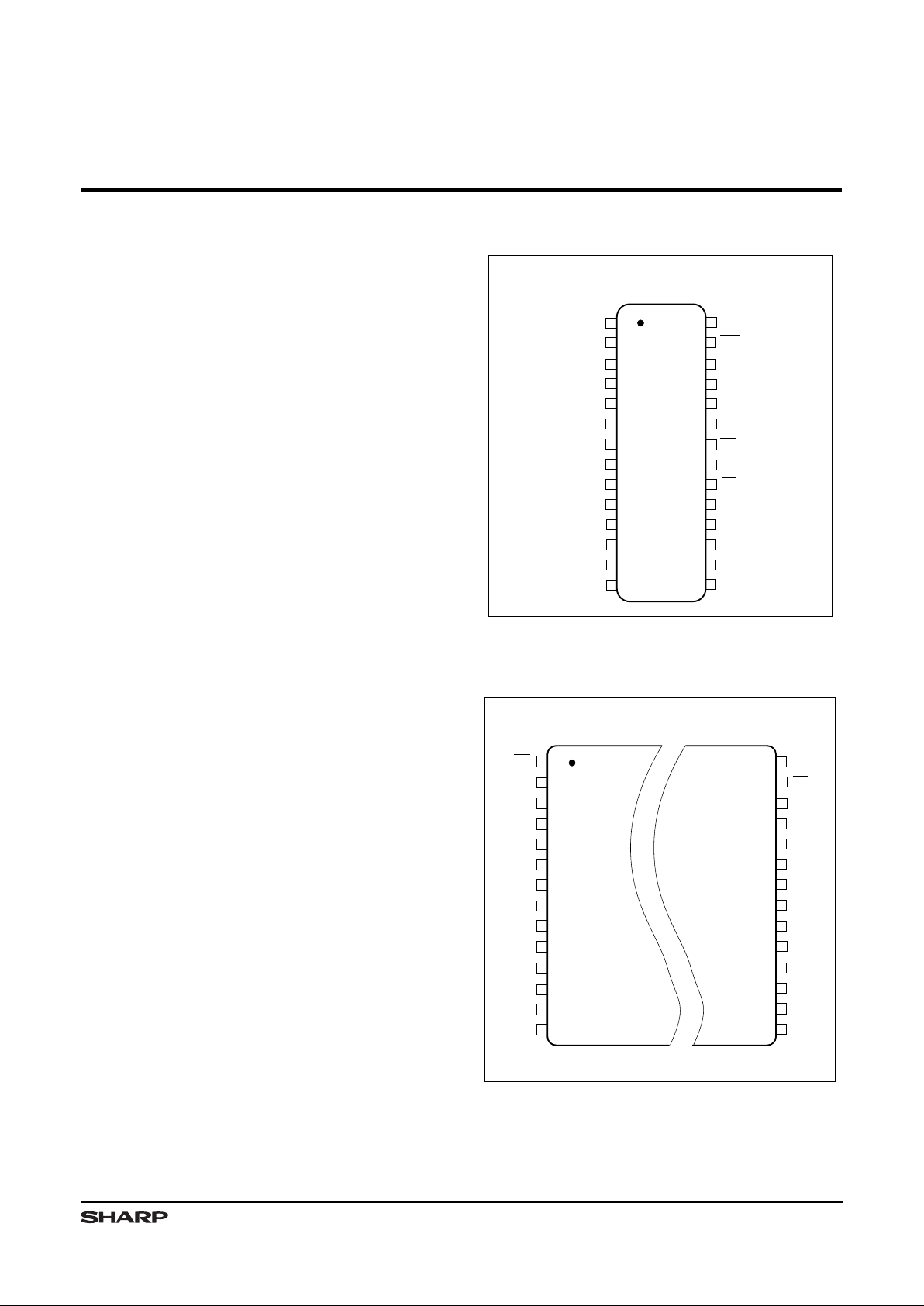

PIN CONNECTIONS

1

2

3

4

7

8

A

2

A

5

26

25

24

23

22

21

18

15

A

7

A

6

5

6

A

3

A

4

20

19

A

12

GND

A

8

A

11

A

10

CE

1

9

10

11

28

27

WE

A

1

V

CC

12

17

16

A

0

I/O

1

A

9

13

14

NC

OE

I/O

2

I/O

3

I/O

7

I/O

6

I/O

5

I/O

4

I/O

8

CE

2

5164A-1

TOP VIEW

28-PIN DIP

28-PIN SK-DIP

28-PIN SOP

Figure 1. Pin Connections for DIP, SK-DIP,

and SOP Packages

2

3

4

5

6

9

10

7

8

A

11

11

1

28

27

26

25

22

21

24

23

20

19

A

10

28-PIN TSOP (Type I)

12

13

14

17

16

18

15

OE

A

8

A

9

CE

2

WE

A

12

NC

I/O

3

I/O

2

A

1

I/O

8

CE

1

I/O

6

I/O

7

GND

I/O

5

I/O

4

I/O

1

A

0

5164A-8

V

CC

A

7

A

6

A

5

A

4

A

3

A

2

TOP VIEW

Figure 2. Pin Connect ions for TSOP Package

1

Page 2

TRUTH TABLE

CE

1

CE

2

WE OE MODE I/O1 - I/O

8

SUPPLY CURRENT NOTE

H X X X Deselect High-Z Standby (ISB)1

X L X X Deselect High-Z Standby (I

SB

)1

L H L X Write D

IN

Operating (ICC)1

L H H L Read D

OUT

Operating (ICC)

L H H H Output disable High-Z Operating (I

CC

)

NOTE:

1. X = H or L

I/O

8

A

8

A

9

A

12

25

24

2

11

15

18

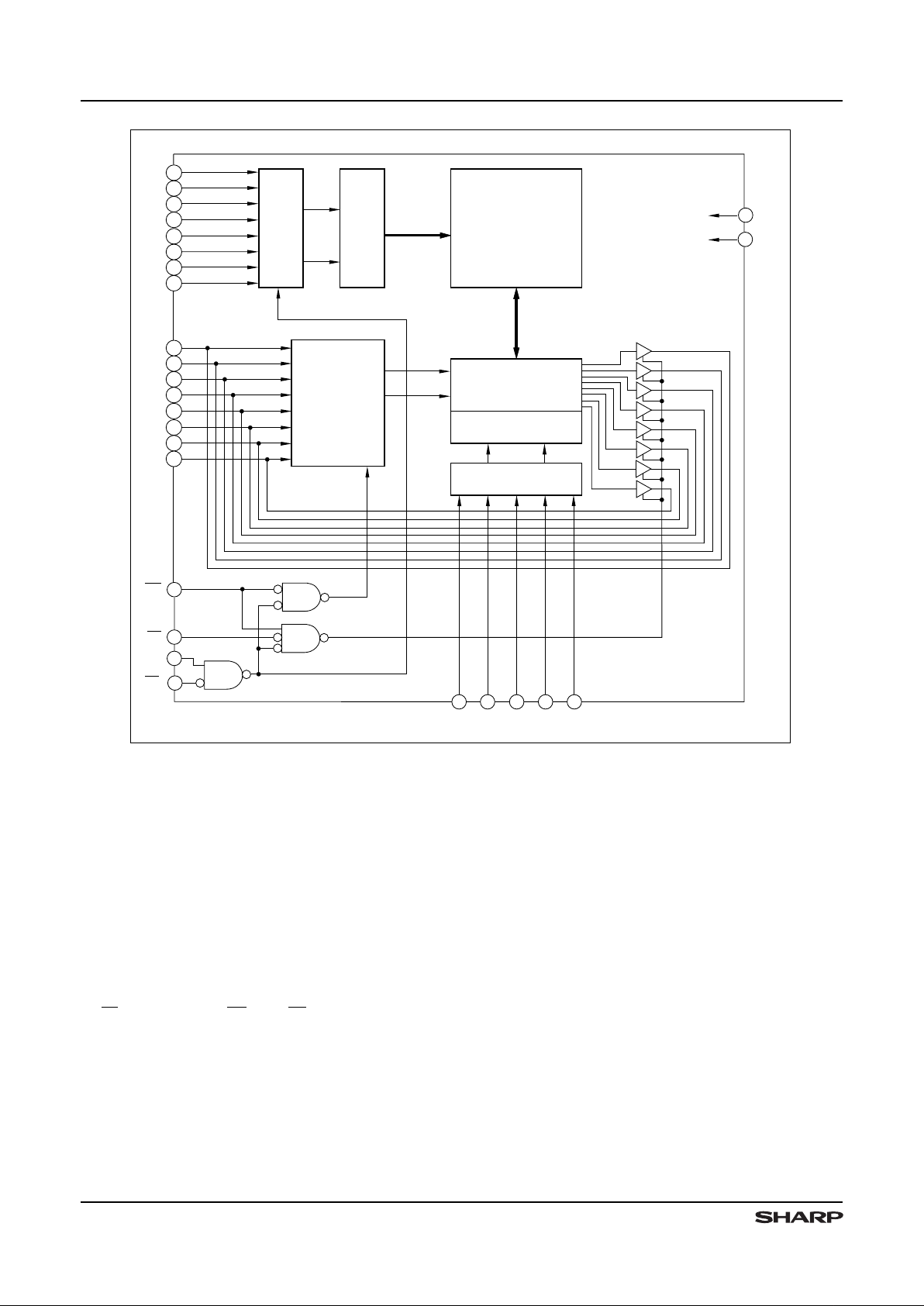

5164A-2

MEMORY

ARRAY

(256 x 256)

13

17

12

16

A

7

3

ROW ADDRESS

BUFFERS

WE

A

6

4

A

5

5

27

A

4

6

ROW DECODERS

I/O

CIRCUITS

COLUMN DECODERS

V

CC

GND

OE

I/O

7

I/O

6

I/O

5

I/O

4

I/O

3

I/O

2

I/O

1

22

19

COLUMN ADDRESS

BUFFER

10

A

0A1A2A10

21

9

8

28

14

A

3

7

CE

1

20

26

CE

2

DATA CONTROL

A

11

23

NOTE: Pin numbers apply to 28-pin DIP, SK-DIP, or SOP.

Figure 3. LH5164A/AH Bl ock Diagram

PIN DESCRIPTION

SIGNA L PIN N AME

A0 - A

12

Addre ss inputs

CE1 - CE

2

Chip Ena ble in put

WE Write E na ble inp ut

OE Outpu t E nab le inp ut

SIGNAL PIN NAME

I/O1 - I/O

8

Data i npu ts and ou tpu ts

V

CC

Power sup ply

GND Ground

NC No connec tion

LH5164A /AH CMOS 64K (8 K × 8) Static RAM

2

Page 3

ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL

80 ns 100 ns

UNIT NOTE

RATING RATING

Suppl y v olt age V

CC

-0.3 to +7.0 -0.3 to +7.0 V 1

Input vol tage V

IN

-0.3 to VCC + 0.3 -0.3 to VCC + 0.3 V 1, 2

Operat ing te mpe ratu re Topr

-10 to +70 -10 to +70

°C

3

-40 to +85 °C4

Storage temperature Tstg -55 to +150 -55 to +150

°C

NOTES:

1. The maximum applicable voltage on any pin with respect to GND.

2.

V

IN

(MIN.) = -3.0 V f or pulse width ≤50 ns.

3. LH5164A/AD/AN/ AT

4. LH5164AH/AHD/AHN/AHT

RECOMMENDED OPERATING CONDITIONS

1

PARAMETER SYMBOL

80 ns 100 ns

UNIT NOTE

MIN. TY P. MAX. MIN. TYP. MAX.

Suppl y v olt age V

CC

4.5 5.0 5.5 4.5 5.0 5.5 V

Input vol tage

V

IH

2.2 VCC + 0.3 2.2 VCC + 0.3 V

V

IL

-0.3 0.8 -0.3 0.8 V 2

NOTES:

1.

T

A

= -10 to +70°C (LH5164A/AD/AN/AT), TA = -40 to +85°C (LH5164AH/ AHD/AHN/AHT).

2.

V

IN

(MIN.) = -3.0 V f or pulse width ≤50 ns.

DC CHARACTERISTICS 1 (VCC = 5 V ±10%)

PARAMETER SYMBOL CONDITI ONS MIN. MAX. UNIT NOTE

Input lea kag e c urr ent

I

LI

VIN = 0 to V

CC

-1.0 1.0 µA

Output le aka ge

curren t

I

LO

CE1 = VIH or CE2 = V

IL

or OE = VIH or WE = V

IL

V

I/O

= 0 to V

CC

-1.0 1.0 µA

Operat ing cu rre nt I

CC

CE1 = VIL, VIN = VIL or V

IH

CE2 = VIH, Outputs open

t

CYCLE

=

80 ns

55 mA

CE1 = VIL, VIN = VIL or V

IH

CE2 = VIH, Outputs open

t

CYCLE

=

100 ns

45

mA

2

50 3

CE1 = VIL, VIN = 0.2 V or

V

CC

- 0.2 V

CE

2

= VIH, Outputs open

t

CYCLE

=

1.0 µs

10

Standb y c urr ent I

SB1

CE1 = V

IH or CE2

= V

IL

5mA

CE2 ≤ 0.2 V or

CE1 ≥ VCC - 0.2 V

T

A

≤ 70°C 1.0 µA 2, 3, 4

T

A

≤ 85°C 3.0 µA 3, 4

Output vo lta ge

V

OL

IOL = 2.1 mA 0.4 V

V

OH

IOH = -1 mA 2.4 V

NOTES:

1.

T

A

= -10 to 70°C (LH5164A/AD/ AN/AT), TA = -40 to +85°C (LH5164AH/ AHD/AHN/AHT)

2. LH5164A/AD/AN/ AT

3. LH5164AH/AHD/AHN/AHT

4.

CE

2

should be ≥ VCC – 0.2 V or ≤ 0.2 V wh en CE1 ≥ VCC – 0. 2 V

CMOS 64K (8K × 8) Static RAM LH5164A/AH

3

Page 4

AC CHARACTERISTICS

1

(1) READ CYCLE (VCC = 5 V ±10%)

PARAMETER SYMBOL

80 ns 100 ns

UNIT NOTE

MIN. MAX. M IN. MAX.

Read c yc le t ime t

RC

80 100 ns

Addres s a cc ess ti me t

AA

80 100 ns

Chip e nab le

acces s t ime

(

CE1)t

AC E 1

80 100 ns

(CE

2

)t

AC E 2

80 100 ns

Output en abl e a cce ss tim e t

OE

40 40 ns

Output ho ld time t

OH

10 10 ns

Chip e nab le to

output in Lo w-Z

(

CE1)t

LZ1

10 10 ns 1

(CE

2

)t

LZ2

10 10 ns 1

Output en abl e t o ou tpu t i n

Low-Z

t

OLZ

5 5 ns 1

Chip e nab le to

output in Hi gh- Z

(

CE1)t

HZ1

0 30 0 30 ns 1

(CE

2

)t

HZ2

0 30 0 30 ns 1

Output disable to outp ut in

High-Z

t

OHZ

0 20 0 20 ns 1

(2) WRITE CYCLE (VCC = 5 V ±10%)

PARAMETER SYMBOL

80 ns 100 ns

UNIT NOTE

MIN. MAX. MIN. M AX.

Write c ycl e t ime t

WC

80 100 ns

Chip e nab le to end of wri te t

CW

70 80 ns

Addres s v al id t o e nd of writ e t

AW

70 80 ns

Addres s s etu p t ime t

AS

00ns

Write p uls e w idt h t

WP

60 60 ns

Write re co ver y ti me t

WR

00ns

Data v ali d t o e nd of w rit e t

DW

40 40 ns

Data h old ti me t

DH

00ns

Output ac tiv e f rom end of wri te t

OW

10 10 ns 2

WE to out put in Hig h-Z t

WZ

030030ns2

OE to out put in Hig h-Z t

OHZ

020020ns2

NOTES:

1.

T

A

= -10 to +70°C (LH5164A/AD/AN/AT), TA = -40 to +85°C (LH5164AH/ AHD/AHN/AHT)

2.

Active output to high-impedance and high-impedance to output active tests specified for a ±200 mV transition

from steady state levels into the test load.

AC TEST CONDITIONS

PARAMETER MODE NOTE

Input voltage amplitude 0.6 to 2.4 V

Input rise/fall time 10 ns

Timing re fer enc e l eve l 1.5 V

Output load conditions 1TTL + CL (100 pF) 1

NOTE:

1. In cludes scope and jig capacitance.

LH5164A /AH CMOS 64K (8 K × 8) Static RAM

4

Page 5

CAPACITANCE 1 (TA = 25°C, f = 1 MHz)

PARAMETER SYMBOL CONDITIONS MIN. TYP. MAX. UNIT

Input cap acitan ce C

IN

VIN = 0 V 7 pF

Input/ out put ca pac ita nce C

I/O

V

I/O

= 0 V 10 pF

NOTE:

1. Th is parameter is sampled and not production tested.

DATA RETENTION CHARACTERISTICS

1

PARAMETER SYMBOL CONDITIONS MIN. MAX. UNIT NOTE

Data r ete nti on v ol tag e V

CCDR

CE2 ≤ 0.2 V or

CE1 ≥ V

CCDR

- 0.2 V

2.0 5.5 V 2

Data r ete nti on c urr ent I

CCDR

V

CCDR

= 3 V,

CE

2

≤ 0.2 V or

CE1 ≥ V

CCDR

- 0.2 V

T

A

=

25°C

0.2 µA 2, 3

T

A

=

40°C

0.4 µA 2, 3

0.6

µA

2, 3

V

CCDR

= 3 V,

CE

2

≤ 0.2 V or

CE1 ≥ V

CCDR

- 0.2 V

T

A

=

25°C

0.2

µA

2, 4

T

A

=

70°C

0.6

µA

2, 4

1.5 µA 2, 4

Chip d isa ble to da ta rete nti on t

CDR

0ns

Recov ery tim e t

R

t

RC

ns 5

NOTES:

1.

T

A

= -10 to +70°C (LH5164A/AD/AN/AT), TA = -40 to +85°C (LH5164AH/ AHD/AHN/AHT)

2.

CE

2

should be ≥ V

CCDR

- 0.2 V or ≤ 0.2 V when CE1 ≥ V

CCDR

– 0. 2 V

3. LH5164A/AD/AN/ AT

4. LH5164AH/AHD/AHN/AHT

5. t

RC

= Read cycle time

CMOS 64K (8K × 8) Static RAM LH5164A/AH

5

Page 6

4.5 V

DATA RETENTION MODE

V

CC

0 V

2.2 V

t

CDR

5164A-6

t

R

V

CCDR

CE

1

CE1 ≥ V

CCDR

- 0.2 V

0 V

V

CCDR

0.8 V

4.5 V

DATA RETENTION MODE

t

CDR

t

R

CE2 CONTROL

CE

1

CONTROL (NOTE)

CE

2

0.2 V

NOTE: To control data hold at CE

1

, fix the input level of CE2 between V

CCDR

to V

CCDR

- 0.2 V or 0 V to 0.2 V

during the data retention mode.

V

CC

CE2

≥

Figure 4. Low V oltage Data Ret e ntion

t

LZ1

t

ACE1

A0 - A

12

t

OHZ

I/O1 - I/O

8

DATA VALID

OE

t

RC

5164A-3

t

OLZ

WE = 'HIGH.'NOTE:

t

ACE2

t

AA

t

LZ2

CE

1

CE

2

t

HZ1

t

OE

t

OH

t

HZ2

Figure 5. Read Cycle

LH5164A /AH CMOS 64K (8 K × 8) Static RAM

6

Page 7

DATA VALID

t

DH

t

DW

WE

D

IN

(NOTE 6)

t

CW

A0 - A

12

OE

t

WC

5164A-4

t

WR

t

CW

t

AW

CE

1

CE

2

t

AS

t

OHZ

t

WP

(NOTE 2)

t

WR

(NOTE 3)

D

OUT

(NOTE 5)

(NOTE 1)

t

WR

HIGH-Z

1. The writing occurs during an overlapping period of CE1 = 'LOW,' CE2 = 'HIGH,' and WE = 'LOW' (tWP).

2. t

CW

is defined as the time from the last occuring transition, either CE1 LOW transition or CE2 HIGH transition,

to the time when the writing is finished.

3. t

AS

is defined as the time from address change to writing start.

4. t

WR

is defined as the time from writing finish to address change.

5. If CE

1

LOW transition or CE2 HIGH transition occurs at the same time or after WE LOW transition, the

outputs will remain high-impedance.

6. While I/O pins are in the output state, input signals with the opposite logic level must not be applied.

NOTES:

(NOTE 4)

Figure 6. Write Cyc l e 1

CMOS 64K (8K × 8) Static RAM LH5164A/AH

7

Page 8

DATA VALID

t

DH

t

DW

WE

D

IN

(NOTE 7)

t

CW

A0 - A

12

t

WC

5164A-5

t

WR

t

CW

t

AW

CE

1

CE

2

t

AS

t

WZ

t

WP

(NOTE 2)

(NOTE 4)

t

WR

(NOTE 3)

D

OUT

(NOTE 5)

(NOTE 1)

t

WR

HIGH-Z

t

OW

(NOTE 6)

OE = 'LOW'

1. The writing occurs during an overlapping period of CE1 = 'LOW,' CE2 = 'HIGH,' and WE = 'LOW' (tWP).

2. t

CW

is defined as the time from the last occuring transition, either CE1 LOW transition or CE2 HIGH transition,

to the time when the writing is finished.

3. t

AS

is defined as the time from address change to writing start.

4. t

WR

is defined as the time from writing finish to address change.

5. If CE

1

LOW transition or CE2 HIGH transition occurs at the same time or after WE LOW transition, the

outputs will remain high-impedance.

6. If CE

1

HIGH transition or CE2 LOW transition occurs at the same time or before WE HIGH transition, the

outputs will remain high-impedance.

7. While I/O pins are in the output state, input signals with the opposite logic level must not be applied.

NOTES:

Figure 7. Write Cyc l e 2

LH5164A /AH CMOS 64K (8 K × 8) Static RAM

8

Page 9

PACKAGE DIAGRAMS

DIMENSIONS IN MM [INCHES]

MAXIMUM LIMIT

MINIMUM LIMIT

28DIP (DIP028-P-0600)

114

1528

28DIP-2

13.45 [0.530]

12.95 [0.510]

0.51 [0.020] MIN.

5.20 [0.205]

5.00 [0.197]

3.50 [0.138]

3.00 [0.118]

2.54 [0.100]

TYP.

0.60 [0.024]

0.40 [0.016]

0.30 [0.012]

0.20 [0.008]

DETAIL

36.30 [1.429]

35.70 [1.406]

0° TO 15°

4.50 [0.177]

4.00 [0.157]

15.24 [0.600]

TYP.

28-pin, 600-mil DIP

28DIP (DIP028-P-0300)

DIMENSIONS IN MM [INCHES]

MAXIMUM LIMIT

MINIMUM LIMIT

114

1528

28DIP-6

7.05 [0.278]

6.65 [0.262]

0.51 [0.02] MIN.

4.40 [0.173]

4.00 [0.157]

3.40 [0.134]

3.00 [0.118]

2.54 [0.100]

TYP.

0.56 [0.022]

0.36 [0.014]

0.35 [0.014]

0.15 [0.006]

DETAIL

35.00 [1.378]

34.40 [1.354]

0° TO 15°

3.65 [0.144]

3.25 [0.128]

7.62 [0.300]

TYP.

28-pin, 300-mi l SK-DIP

CMOS 64K (8K × 8) Static RAM LH5164A/AH

9

Page 10

DIMENSIONS IN MM [INCHES]

MAXIMUM LIMIT

MINIMUM LIMIT

28SOP (SOP028-P-0450)

12.40 [0.488]

11.60 [0.457]

8.80 [0.346]

8.40 [0.331]

10.60 [0.417]

18.20 [0.717]

17.80 [0.701]

0.15 [0.006]

1.025 [0.040]

0.20 [0.008]

0.00 [0.000]

1.025 [0.040]

2.40 [0.094]

2.00 [0.079]

0.20 [0.008]

0.10 [0.004]

0.50 [0.020]

0.30 [0.012]

1.27 [0.050]

TYP.

28 15

141

1.70 [0.067]

1.70 [0.067]

28SOP

28-pin, 450-mil SOP

LH5164A /AH CMOS 64K (8 K × 8) Static RAM

10

Page 11

DIMENSIONS IN MM [INCHES]

MAXIMUM LIMIT

MINIMUM LIMIT

28TSOP (TSOP028-P-0813)

28

1

28TSOP

14

15

0.28 [0.011]

0.12 [0.005]

0.55 [0.022]

TYP.

12.00 [0.472]

11.60 [0.457]

13.70 [0.539]

13.10 [0.516]

8.20 [0.323]

7.80 [0.307]

0.15 [0.006]

1.10 [0.043]

0.90 [0.035]

1.20 [0.047]

MAX.

12.60 [0.496]

12.20 [0.480]

0.20 [0.008]

0.10 [0.004]

0.20 [0.008]

0.00 [0.000]

1.10 [0.043]

0.90 [0.035]

0.425 [0.017]

0.20 [0.008]

0.00 [0.000]

0 - 10°

DETAIL

0.425 [0.017]

28-pin, 8 × 13 mm2 TSOP (Type I)

10 100

80 80

LH5164A

Device Type

X

Package

- ##

Speed

5164A-7

CMOS 64K (8K x 8) Static RAM

Blank 28 pin, 600-mil DIP (DIP028-P-0600)

D 28-pin, 300-mil SK-DIP (SK-DIP028-P-0300)

N 28-pin, 450-mil SOP (SOP028-P-0450)

T 28-pin, 8 x 13 mm

2

TSOP (Type I) (TSOP028-P-0813)

Example: LH5164AD-10L (CMOS 64K (8K x 8) Static RAM, 100 ns, Low-power standby,

28-pin, 300-mil SK-DIP)

X

Blank -10 to 70°C

H -40 to +85°C

Operating

Temperature

Access Time (ns)

L

Power

Low-power standby

ORDERING INFORMATION

CMOS 64K (8K × 8) Static RAM LH5164A/AH

11

Loading...

Loading...