Page 1

1/4June 2002

IP Library: High PSRR, Very Low Power,

40mA Low Dropout Volt age Regulator

■

DIGITAL BASEBAND REGULATOR

■

VERY LOW DROPOUT VOLTAGE : 50mV

■

HIGH PSRR : 55dB

■

VERY LOW QUIESCENT CURRENT : 100µA

FULL LOAD

■

NO CURRENT IN POWER DOWN MODE

■

SHORT CIRCUIT PROTECTION

■

SMALL DECOUPLING CERAMIC CAPACIT OR

TYPICAL APPLICATIONS

– Cellular and Cordless phones suppli ed by 1 cell

Lithium-ion battery / 3 cells Ni-MH or Ni-Cd

battery.

– PDA (Personal Digital Assistant), Smart phone.

– Portable equipm ent

– Supply for Digital (DSP/Microcontroller) devices.

APPLICATION NOTE

An external capacitor (C

OUT

= 1µF) with an

equivalent serial resistance (ESR) in the range

0.02 to 0.6Ω is used for regulator stability.

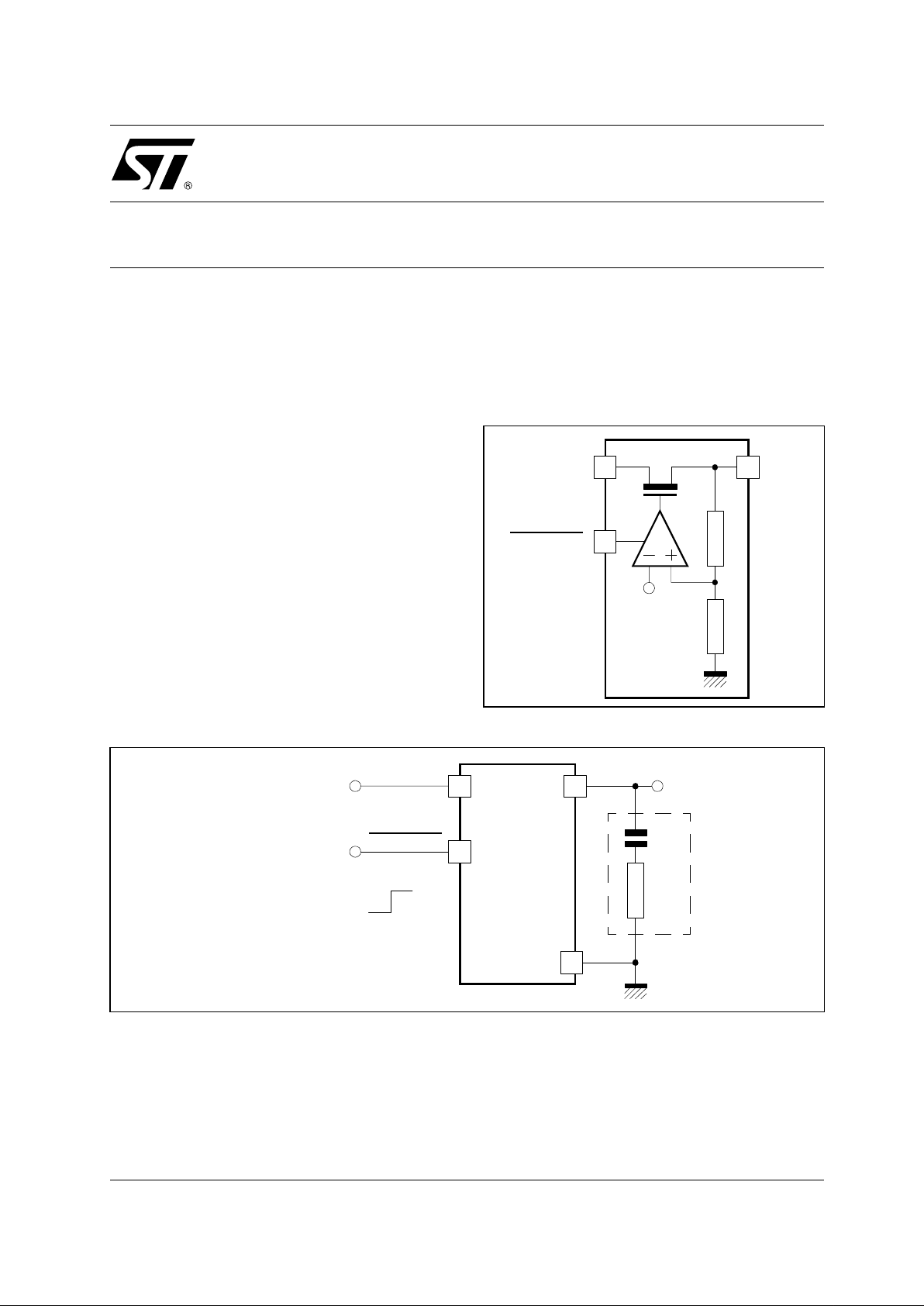

Figure 1 :

Block Diagram

?

V

REF

?

?

LDO_53

OUTIN

PWRDWN

Figure 2 :

Typical Application Circuit

1µF

ESR

V

OUT

C

OUT

?

?

OUT

GND

?

?

V

IN

IN

Power Dow n Mode

OFF

ON

LDO_53

PWRDWN

LDO_53

This is advance information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

PRODUCT PREVIEW

Page 2

LDO_53

2/4

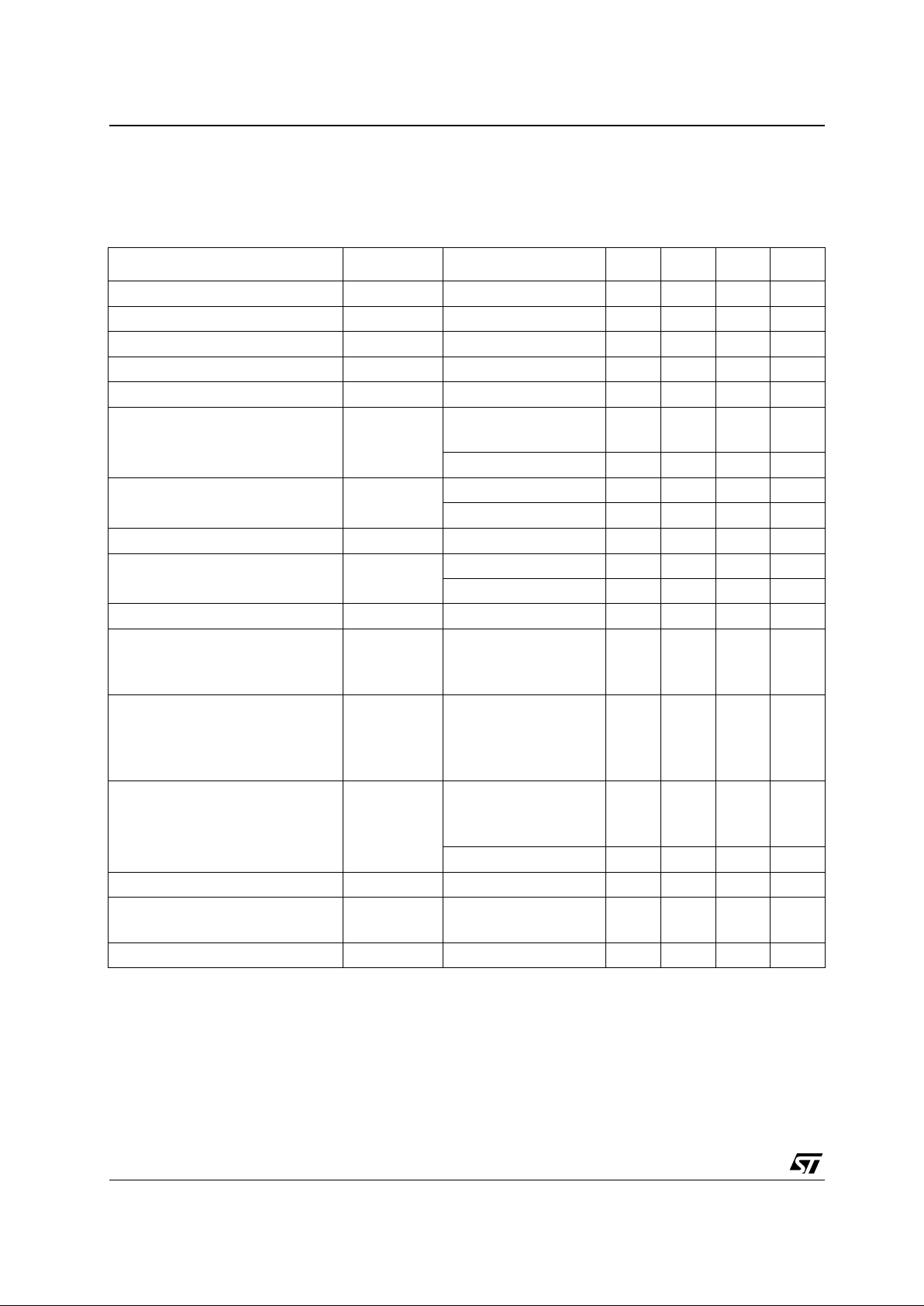

ELECTRICAL CHARACTERISTICS

3V < V

IN

< 5.5V, -30°C < T < +85°C, V

REF

= 2.8V, 0.8µF < C

OUT

< 1.2µF, 20mΩ < ESR < 0.6Ω.

100µA < I

LOAD

< 40mA.

Typical case :

V

IN

= 4V, T = 25°C, I

OUT

= 20mA.

Notes: 1. Above characteristics are given for 3V minimum input operating range voltage, but regulator is

operational with 2.7V minimum input voltage.

2. All parameters are guaranteed with 170mV Dropout voltage.

Parameter Symbol Test Condition Min Typ Max Unit

Input Voltage Range (Note 1) V

IN

3 5,5 V

Output Voltage V

OUT

2,8 V

Output Voltage Accuracy -3 3 %

Output current I

OUT

0,1 40 mA

P

MOS

Output Resistance R

ON

0,4 Ω

Dropout Voltage ∆V

DO

∆V

OUT

= 50mV,

I

LOAD

= 40mA

50 mV

(Note 2) 170

Quiescent current I

Q

I

LOAD

= 100µA2030µA

I

LOAD

= 40mA 100 120

Power down mode quiescent current I

QPDN

Power down active 1 µA

Power Supply Rejection Ratio PSRR DC 50 55 dB

f < 10KHz 45 50

Load Regulation Ldr 15 25 mV

Line Regulation Lir I

LOAD

= 40mA,

V

IN

= 3V to 5.1V,

V

OUT

= 2.8V

23mV

Line Transcient Lirt V

OUT

= 2.8V,

I

OUT

= 40mA,

∆V

IN

= 300mV

t

RISE

= t

FALL

= 10µs

3mV

Load Transcient Ldtr V

OUT

= 2.8V,

t

RISE

= t

FALL

= 10µs

100µA < I

LOAD

< 40mA

3mV

Recovery time 5 6 µs

Output decoupling capacitor C

OUT

1 µF

Settling time

(from power down to active mode)

V

OUT

= 2.8V, C

OUT

= 1µF2050µs

Short Circuit Current Limit I

SHORT

200 mA

Page 3

LDO_53

3/4

010203040

20

40

60

80

100

OUTPUT LOAD (mA)

CURRENT COMSUMPTION (µA)

TYPICAL CHARACTERISTICS

Figure 7 :

Load Transient - rising edge

(I

L

= 0 to 40 mA - VIN = 4V)

Figure 8 :

Load Transient - falling edge

(I

L

= 40 to 0 mA - VIN = 4V)

Figure 5 :

Line Transient - rising edge

(V

IN

= 4V + 300mV with 10µs)

Figure 6 :

Line Transient - falling edge

(V

IN

= 4V + 300mV with 10µs)

Figure 3 :

Quiescent Current vs Output Current

(I

L

= 0 to 40mA - VIN = 4V)

Figure 4 :

Settling time

(V

IN

= 4V ; I

LOAD

= 20mA)

Page 4

LDO_53

4/4

Information furnished is bel ieved to be accurate and reliable. However, STMicroe lectronics assumes no responsibility for the

consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from

its use. No li cense is granted by imp lica tion or otherwise under a ny patent or patent rig hts of STMicroelectronics. Sp ec ificat ions

mentioned in this publication ar e subject to change without notice. This publication supersedes and replaces all information

previously supplied. S TMicroelectronics products are not authorized for use as critica l components in life suppo rt devices or

systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 2002 STMicroelectronics - All Rights Reserved

STMicroele ct ronics GROUP OF COM P ANIES

Australia - Brazil - Canada - Chi na - F i nland - Franc e - Germany - Hong Kong - Ind i a - Israel - Ital y - Japan - Mala ysia - Malt a - Moroc co

Singapor e - S pai n - Sweden - Swi tzerland - U ni ted Kingdom - United States

http://www.st.com

100 1000 10000 100000

30

40

50

60

70

Frequenc y (Hz)

PSRR (dB)

Figure 9 :

PSRR vs Frequency

(I

LOAD

max - VINmin)

Loading...

Loading...