Page 1

Ordering number : ENN*6697

LC865520B/16B/12B/08B/04B

8-Bit Single Chip Microcontroller with On-Chip

20/16/12/08/04K-Byte ROM and 512-Byte RAM

Preliminary

Overview

The LC865520B/16B/12B/08B/04 B are 8-bit single chip microcontrollers with the following one-chip features:

- CPU : Operable at a minimum bus cycle time of 0.5µs

- On-chip ROM Capacity : 20K/16K/12K/8K/4K bytes

- On-chip RAM Capacity : 512 bytes (LC865520B/16B/12B/08B/04B)

- 16-bit timer/counter (can be divided into two 8 bit timers)

- 16-bit timer/PWM (can be divided into two 8 bit timers)

- 8-channel × 8-bit AD converter

- Two 8-bit synchronou s serial-interface circuits

- 13-source 10-vectored interrupt system

Features

(1) Read Only Memory (ROM) : LC865520B 20480 × 8 bits

: LC865516B 16384

: LC865512B 12288

: LC865508B 8192

: LC865504B 4096

(2) Random Access Memory (RAM) : LC865520B/16B/12B/08B/04B 512 × 8 bits

(3) Bus Cycle Time/Instruction Cycle Time

8 bits

×

8 bits

×

8 bits

×

8 bits

×

The LC865520B/16B/12B/08B/04B are constructed to read ROM twice within one instruction cycle.

It has 1.7 times the performance capability for the same instruction cycle compared to our 4-bit

microcontrollers (LC66000 series).

Bus cycle time indicates the speed to read ROM.

Bus cycle time Instruction cycle time Clock divider System clock oscillation Oscillation Frequ ency Voltage

0.5µs

2µs

7.5µs

183µs

1µs

4µs

15µs

366µs

1/1 Ceramic (CF) 6MHz 4.5V to 6.0V

1/2 Ceramic (CF) 3MHz 2.5V to 6.0V

1/2 Internal RC 800kHz 2.5V to 6.0V

1/2 Crystal (XTAL) 32.768kHz 2.5V to 6.0V

CMOS IC

Ver.1.02

32300

11901 RM (IM) Chigira No.6697-1/21

Page 2

LC865520B/16B/12B/08B/04B

(4) Ports

- Input/output ports : 3 ports (16 terminals : port 1,7,8)

Input/output programmable for each bit individually

- Maximum 15V withstand tolerance input/output port : 2 p or ts (15 terminals)

Input/output programmable in nibble units : 1 port (8 terminals : port 0)

(When the N-channel open drain output is selected, input/output can be specified by bit.)

Input/output programmable for each bit individually : 1 port (7 terminals : port 3)

- Input ports : 2 ports (6 terminals : port 7,8)

(5) AD converter

- 8-channel × 8-bit AD converter

(6) Serial interface

- 1 channel × 16-bit serial interface (8-bit transm is s ion available by program)

- 1 channel × 8-bit serial interface

LSB first/MSB first-f u nction available

- An internal 8-bit baud-rate generator is common to both serial-interface circuits.

(7) Timer

- Timer 0

16-bit timer/counter

2-bit prescaler + 8-bit programmable prescaler

Mode 0 : Two 8-bit timers with programmable prescaler

Mode 1 : 8-bit timer with programmable prescaler + 8-bit counter

Mode 2 : 16-bit timer with programmable prescaler

Mode 3 : 16-bit counter

The resolution of Timer is t

CYC. (tCYC: cycle time)

- Timer 1

16-bit timer/PWM

Mode 0 : Two 8-bit timers

Mode 1 : 8-bit timer + 8-bit PWM

Mode 2 : 16-bit timer

Mode 3 : Variable-bit PWM (9-16bits)

In Mode 0 and Mode 1, the resolution of Timer and PWM is t

In Mode 2 and Mode 3, the resolution of Timer and PWM is selectable by program: t

CYC.

CYC or 1/2 tCYC.

- Base timer

Generates an overflow every 500ms for a clock application (using 32.768kHz crystal oscillation for the base timer

oscillator).

Generates an overflow every 976µs, 3.9ms, 15.6ms or 62.5ms (using 32.768kHz crystal oscillation for the base timer

clock)

Clock for the base timer is selectable from 32.768kHz crystal oscillation, system clock, or programmable prescaler

output of Timer 0.

(8) Buzzer output

- Built-in 4KHz and 2KHz buzzer generation function (using 32.768kHz crystal oscillation for the base timer oscillator)

(9) Remote receiver circuit (share with P73/INT3/T0IN terminal)

- Noise Rejection function (The filtering time of the noise rejection filter (1tCYC/16tCYC/64tCYC) can be switched by

program.) (t

CYC: instructio n-c ycle-tim e

)

- Polarity switch function

(10) Watchdog timer

- External RC circuit is required.

- Interrupt or system reset is activated when the timer overflows.

No.6697-2/21

Page 3

LC865520B/16B/12B/08B/04B

(11) Interrupt

- 13-source and 10-vectored interrupt function:

1. External interrupt INT0 (including watchdog timer)

2. External interrupt INT1

3. External interrupt INT2, Timer/counter T0L (lower 8 bits of Timer 0)

4. External interrupt INT3, Base timer

5. Timer/counter T0H (upper 8 bits of Timer 0)

6. Timer T1L (lower 8 bits of Timer 1), Timer T1H (upper 8 bits of Timer 1)

7. Serial interface SIO0

8. Serial interface SIO1

9. AD converter

10. Port 0

- Built-i n I nterrupt Priority control r egister

Three interrupt priorities are supported (low, high and highest) and multi-level nesting is possible. Low or high

priority level can be assigned to the 11 interrupt sources of interrupts 3 to 10 shown above by the interrupt priority

control register. For the external interrupt INT0 and INT1(interrupt 1 and 2), low or highest can be set regardless of

the interrupt priority register.

(12) Sub-routine stack levels

- A maximum of 128 levels (set stack inside RAM)

(13) Multiplication and division

16 bits × 8-bit (7 instruction-cycle-times)

16 bits / 8-bit (7 instruction-cycle-times)

(14) 3 types of oscillation circuits

- Built-in RC oscillation circuit used for the system clock.

- CF oscillation circuit used for the system clock.

- Crystal oscillation circuit used for the system clock and the time-base clock.

(15) Standby function

- HALT mode

The HALT mode stops the program execution, which minimizes power consumption. This operation mode can be

released b y a system reset or an interrupt req ue st.

- HOLD mode

The HOLD mode stops all oscillation circuits: CF, RC and Crystal oscillations. This mode can be released by the

following conditions.

• Feed "L" level to the reset terminal (

RES )

• Feed the selected level to P70/INT0, P71/INT1 terminals

• Feed "L" level to the Port 0

(16) Shipping form

• DIP42S

• QIP48E

(17) Development tools

Evaluation (EVA) chip : LC866096

EPROM version : LC86E5420

One time version : LC86P5420

Emulator : EVA-86000 + ECB867100 (Evaluation chip board) + POD865 400 (POD)

No.6697-3/21

Page 4

LC865520B/16B/12B/08B/04B

Notice for use

1. The following must be taken into consideration by the user:

Oscillation frequency range for system clock. Supply voltage range Clock Divider

15kHz to 30kHz 1/1 Can not use 1/2 divider

30kHz to 6MHz

15kHz to 30kHz 1/1 Can not use 1/2 divider

30kHz to 1.5MHz 1/1,1/2

1.5MHz to 3MHz

4.5V to 6.0V

2.5V to 6.0V

4.5V to 6.0V 1/1,1/2 Internal RC oscillation

2.5V to 6.0V 1/2 Can not use 1/1 divider

Notes

1/1,1/2

1/2 Can not use 1/1 divider

No.6697-4/21

Page 5

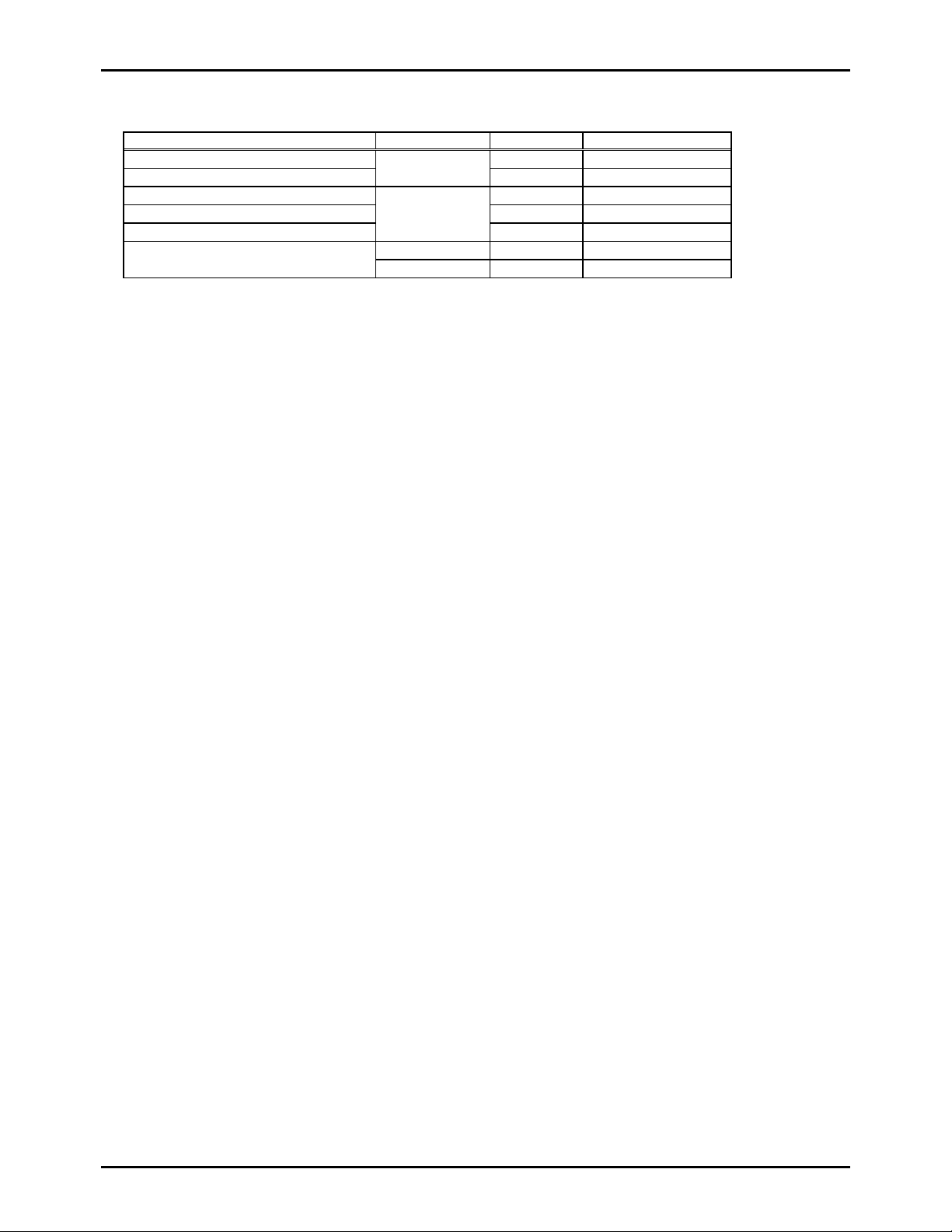

Pin Assignment

•DIP42S

Package Dimension

(unit : mm)

3025B

P00

P01

P02

P03

P04

P05

P06

P07

P70/INT0

RES

XT1/P74

XT2/P75

VSS

CF1

CF2

VDD

P80/AN0

P81/AN1

P82/AN2

P83/AN3

P84/AN4

LC865520B/16B/12B/08B/04B

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

P17/PWM0

P16/BUZ

P15/SCK1

P14/SI1/SB1

P13/SO1

P12/SCK0

P11/SI0/SB0

P10/SO0

P36

P35

P34

P33

P32

P31

P30

P73/INT3/T0IN

P72/INT2/T0IN

P71/INT1

P87/AN7

P86/AN6

P85/AN5

SANYO : DIP-42S(600mil)

No.6697-5/21

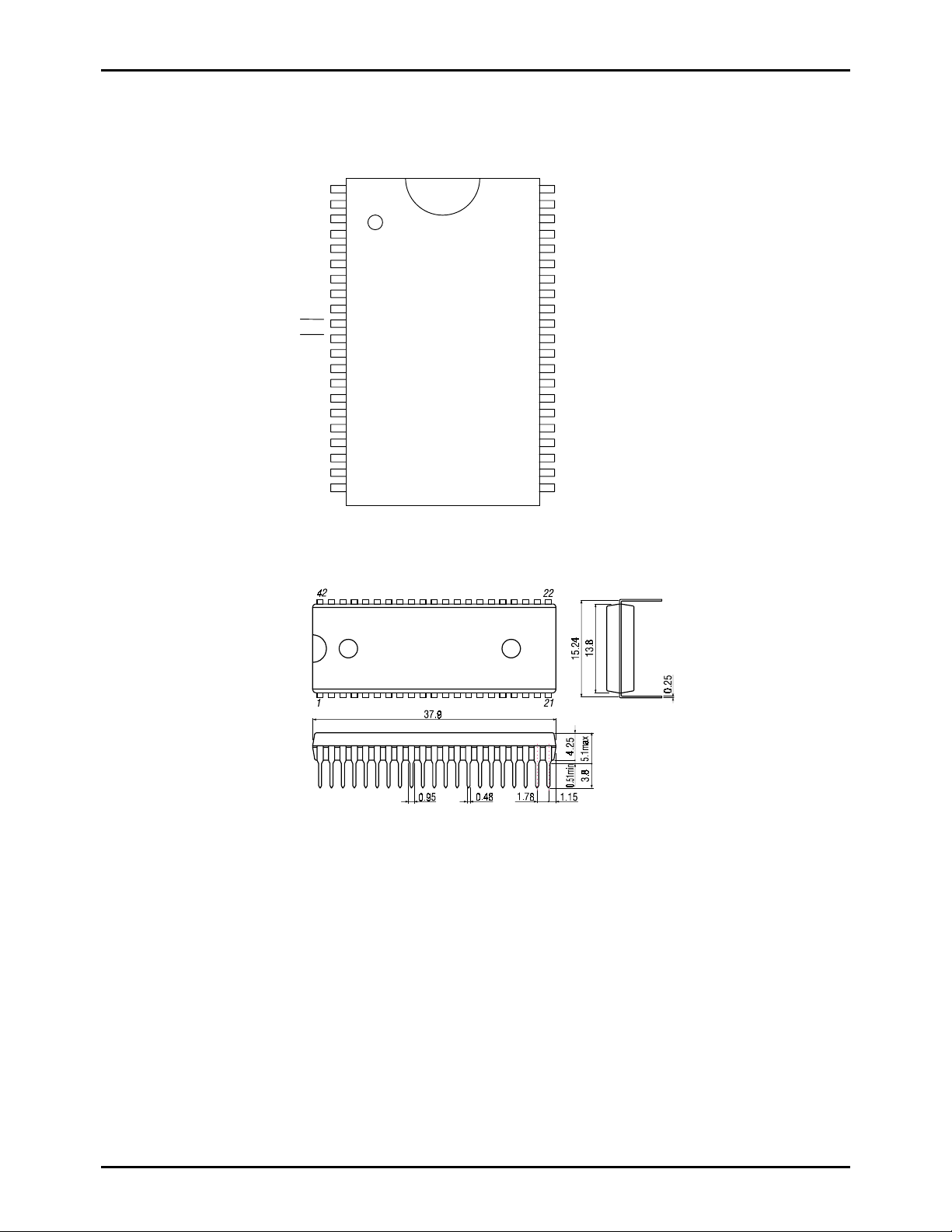

Page 6

Pin Assignment

•QIP48E

Package Dimension

(unit : mm)

3156

P13/SO1

P14/SI1/SB1

P15/SCK1

P16/BUZ

P17/PWM0

NC

P00

P01

P02

P03

P04

NC

LC865520B/16B/12B/08B/04B

P12/SCK0

P11/SI0/SB0

P10/SO0

P36

P35

P34

P33

NC

P32

P31

P30

3635343332313029282726

37

38

39

40

41

42

43

44

45

46

47

48

1 2 3 4 5 6 7 8 9

P05

P06

P07

RES

XT1/P74NCXT2/P75

P70/INT0

10

11

CF1

CF2

VSS

P73/INT3/T0IN

25

24

23

22

21

20

19

18

17

16

15

14

13

12

VDD

NC

P72/INT2/T0IN

P71/INT1

P87/AN7

P86/AN6

P85/AN5

NC

P84/AN4

P83/AN3

P82/AN2

P81/AN1

P80/AN0

*Leave NC pins open.

SANYO : QIP-48E

No.6697-6/21

Page 7

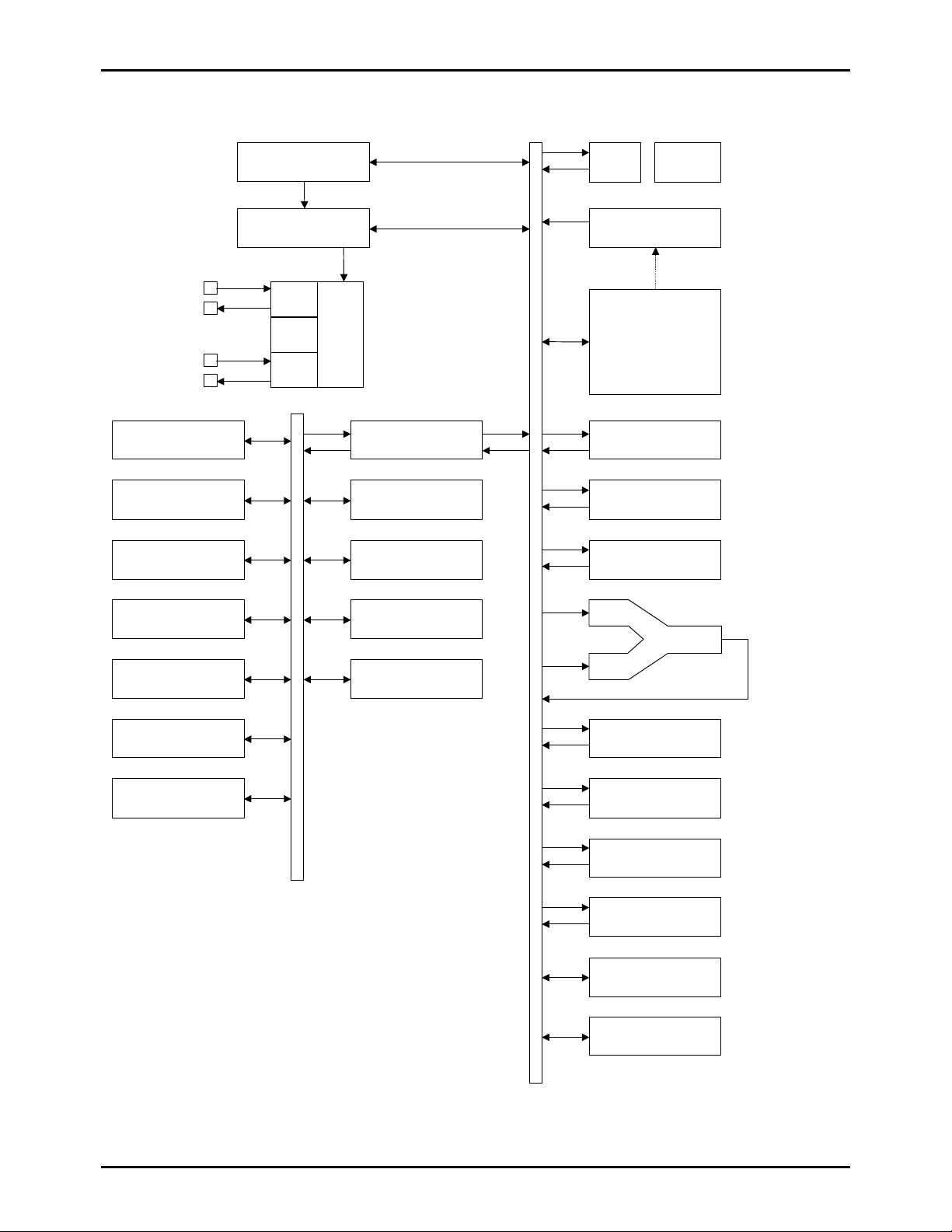

System Bl ock Diagram

SIO0

Timer 1

ADC

INT0-3

Noise Rejection Filter

Interrupt Control

Stand-by C ontr ol

X’tal

CR

RC

LC865520B/16B/12B/08B/04B

Clock

Generator

Port 1

Port 7 SIO1

Port 8 Timer 0

Port 3

PLA IR

ROM

PC

ACC Bus Interface Base Timer

B Register

C Register

ALU

PSW

RAR

RAM

Stack Pointer

Port 0

Watch Do g Timer

No.6697-7/21

Page 8

LC865520B/16B/12B/08B/04B

Pin descriptio n

Name I/O Function description Option

VSS - Power terminal (-) VDD - Power terminal (+) PORT0

P00 to P07

PORT1

P10 to P17

PORT3

P30 to P36

PORT7

P70 to P73

P74

, P75

I/O • 8-bit input/output port

• Port 0 interrupt input

• Data direction programmable in nibble units

• HOLD release input

• A withstand tolerance of 15V when selecting N-channel

open drain output

I/O • 8-bit input/output port

• Data direction programmable for each bit individually

• Other functions

P10 SIO0 data output

P11 SIO0 data input, bus input/output

P12 SIO0 clock input/output

P13 SIO1 data output

P14 SIO1 data input, bus input/output

P15 SIO1 clock input/output

P16 Buzzer output

P17 Timer 1 output (PWM0 output)

I/O • 7-bit input/output port

• Data direction programmable for each bit individually

• A withstand tolerance of 15V when selecting N-channel

open drain output

• 4-bit input/output port

• Data direction programmable for each bit individually

• 2-bit input port

• Other functions

P70 : INT0 input/HOLD release input/N-ch Tr. output

I/O

I

for watchdog timer

P71 : INT1 input/HOLD release input

P72 : INT2 input/timer 0 event input

P73 : INT3 input with noise filter/timer 0 event input

P74

: Input terminal XT1 for 32.768kHz X'tal oscillation

P75 : Output terminal XT2 for 32.768kHz X'tal oscillation

• Interrupt detection style, vector ad dress

Rising Falling Rising/

Falling

INT0 enable enable disable enable enable 03H

INT1 enable enable disable enable enable 0BH

INT2 enable enable enable disable disable 13H

INT3 enable enable enable disable disable 1BH

H level L level Vector

Continue.

• Pull-up resistor :

Provided/Not provided

(specified in nibble units)

• Output form :

CMOS/N-channel open drain

(specified by bit)

• Output form :

CMOS/N-channel open drain

(specified by bit)

• Pull-up resistor :

Provided/Not provided

(specified by bit)

• Output form :

CMOS/N-channel open drain

(specified by bit)

No.6697-8/21

Page 9

LC865520B/16B/12B/08B/04B

Name I/O Function description Option

PORT8

P80 to 83

P84 to 87

RES

XT1/

XT2/P75 O • Output terminal for 32.768kHz X'tal oscillation

CF1 I Input terminal for ceramic resonator CF2 O Output te rmin al for ceramic resonator -

• 4-bit input port

I

• Data direction programmable for each bit individually

I/O

• 4-bit input/output port

• Other function

AD converter input port (8 pins)

I Reset -

P74

I • Input terminal for 32.768kHz X'tal oscillation

• Other function

XT1 : Input port

• When not in use, connect terminal to VDD

• Other function

XT2 : Input port P75

• When not in use

- If set as port, co nnect terminal to VDD.

- If set as oscillation, leave terminal open.

P74

-

-

-

* All port options (except pull-up resistor of port 0) can be specified by bit.

A state of port terminals at reset

Name Input/output mode Style of pull-up resistors when pull-up option is enabled

Port 0 Input Fixed pull-up resistor OFF

Ports 1,3 Input Programmable pull-up resistor OFF

No.6697-9/21

Page 10

LC865520B/16B/12B/08B/04B

V

1. Absolute Maximum Ratings at VSS=0V and Ta=25°C

Parameter Symbol Pins Conditions

Ratings

[V]

DD

min. typ. max.

Supply voltage VDDMAX VDD VDD -0.3 +7.0

Input voltage VI(1) • Ports 74,75

-0.3 VDD+0.3

• Ports 80,81,82,83

RES

•

Input/Output

voltage

VIO(1) • Port 1

• Ports 70,71,72,73

-0.3 VDD+0.3

• Ports 84,85,86,87

• Ports 0, 3 of CMOS

output

VIO(2) Ports 0, 3 of N-ch open

-0.3 15

drain output

High

level

output

current

Peak

output

current

Total

output

current

IOPH • Ports 0, 1, 3

• Ports 71,72,73

• Ports 84,85,86,87

IOAH(1)

Σ

IOAH(2)

Σ

IOAH(3)

Σ

Ports 0, 1 Total of all pins -30

Port 3 Total of all pins -15

• Ports 71,72,73

• CMOS output

-10

• For each pin

Total of all pins -10

• Ports 84,85,86,87

Low

level

output

current

output

current

Total

output

current

IOPL(1) Ports 0, 1, 3 For each pin 20 Peak

IOPL(2) • Ports 70,71,72,73

• Ports 84,85,86,87

IOAL(1)

Σ

IOAL(2)

Σ

IOAL(3)

Σ

Ports 0,1,70 Total of all pins 60

Port 3 Total of all pins 40

• Ports 71,72,73

For each pin 15

Total of all pins 20

• Ports 84,85,86,87

power

consumption

Operating

Pdmax(1) DIP42S

Pdmax(2) QFP48E

Ta= -30 to+70°C

Ta= -30 to+70°C

Topr -30 70

630 Maximum

350

temperature

range

Storage

Tstg -55 125

temperature

range

unit

V

mA

mW

C

°

No.6697-10/21

Page 11

LC865520B/16B/12B/08B/04B

2. Recommended Operating Range at Ta=-30°C to +70°C, VSS=0V

Parameter Symbol Pins Conditions

Operating

Supply

voltage range

VDD(1)

VDD(2)

VDD

0.98µs ≤ t

3.9µs ≤ t

CYC

CYC

≤ 400µs

≤ 400µs

Hold voltage VHD VDD RAM and register data

are kept in HOLD

mode.

Input high

VIH(1) Port 0 of CMOS output Output disable 2.5 to 6.0 0.33VDD

voltage

Output disable

drain output

VIH(3) • Port 1

• Ports 72,73

Output disable 2.5 to 6.0 0.75VDD VDD

• Port 3 of CMOS

output

Output disable

drain output

VIH(5) • Port 70

Output disable 2.5 to 6.0 0.75VDD VDD

Port input/interrupt

• Port 71

RES

•

VIH(6) Port 70

Output disable 2.5 to 6.0 0.9VDD VDD

Watchdog timer

Input low

voltage

VIH(7) • Port 8

74

• Ports

,75

VIL(1) Port 0 of CMOS output Output disable 2.5 to 6.0 VSS 0.2VDD

VIL(2) Port 0 of N-ch open

• Output disable

• Using as port

Output disable 2.5 to 6.0 VSS 0.25VDD

drain output

VIL(3) • Ports 1,3

Output disable 2.5 to 6.0 VSS 0.25VDD

• Ports 72,73

VIL(4) • Port 70

Output disable 2.5 to 6.0 VSS 0.25VDD

Port input/interrupt

• Port 71

RES

•

VIL(5) Port 70

Output disable 2.5 to 6.0 VSS 0.8VDD

Watchdog timer

VIL(6) • Port 8

74

• Ports

CYC

t

,75

• Output disable

• Using as port

cycle time

Oscillation

frequency

range

(Note 1)

FmCF(1) CF1, CF2 • 6MHz

(ceramic resonator)

• Refer to figure 1

FmCF(2) CF1, CF2 •3MHz

(ceramic resonator)

• Refer to figure 1

FmRC Internal RC oscillation 2.5 to 6.0 0.3 0.8 3.0

FsXtal XT1, XT2 •32.768kHz

(crysta l os cillation)

• Refer to figure 2

Continue.

Ratings

VDD[V] min. typ. max.

4.5 6.0

unit

V

2.5 6.0

2.0 6.0

VDD

+1.0

4.0 to 6.0 0.75VDD 13.5 VIH(2) Port 0 of N-ch open

2.5 to 4.0 0.8VDD 13.5

4.0 to 6.0 0.75VDD 13.5 VIH(4) Port 3 of N-ch open

2.5 to 4.0 0.8VDD 13.5

2.5 to 6.0 0.75VDD VDD

to 1.0

2.5 to 6.0 VSS 0.25VDD

4.5 to 6.0 0.98 400 Operation

s

µ

2.5 to 6.0 3.9 400

4.5 to 6.0 5.88 6 6.12

MHz

2.5 to 6.0 2.94 3 3.06

2.5 to 6.0 32.768 kHz

No.6697-11/21

Page 12

LC865520B/16B/12B/08B/04B

Parameter Symbol Pins Conditions

Oscillation

stabilizing time

(Note 1)

tmsCF(1) CF1, CF2 •6MHz

(ceramic resonator)

• Refer to figure 3

(ceramic resonator)

• Refer to figure 3

tssXtal XT1, XT2 •32.768kHz

(crysta l os cillation)

• Refer to figure 3

(Note 1) The oscillation parameters are shown on table 1 and 2.

Ratings

VDD[V] min. typ. max.

4.5 to 6.0

4.5 to 6.0 tmsCF(2) CF1, CF2 •3MHz

2.5 to 6.0

4.5 to 6.0

2.5 to 6.0

unit

ms

s

No.6697-12/21

Page 13

LC865520B/16B/12B/08B/04B

3. Electrical Characteristics at Ta=-30°C to +70°C, VSS=0V

Parameter Symbol Pins Conditions

Input high

current

IIH(1) Ports 0,3 of open

drain output

• Output disable

• VIN=13.5 V

(including the off-leak

current of the ou tput Tr.)

IIH(2) • Port 0 without

pull-up MOS Tr.

• Ports 1,3

• Ports 70,71,72,73

• Port 8

IIH(3)

IIH(4) Ports

RES

VIN=VDD 2.5 to 6.0 1

74

,75 • VIN=VDD

• Output disabl e

• Pull-up MOS Tr. OFF.

• VIN=VDD

(including the off-leak

current of th e output Tr.)

• Using as port

Input low

current

IIL(1) • Ports 1,3

• Port 0 without

pull-up MOS Tr.

• Ports 70,71,72,73

• Port 8

IIL(2)

IIL(3) Ports

RES

VIN=VSS 2.5 to 6.0 -1

74

• Output disabl e

• Pull-up MOS Tr. OFF.

• VIN=VSS

(including the off-leak

current of th e output Tr.)

,75 • VIN=VSS

• Using as port

VOH(1) IOH=-1.0mA 4.5 to 6.0 VDD-1 Output high

voltage

VOH(2)

• Ports 0,1,3 o f

CMOS output

• Ports 71,72, 73

IOH=-0.1mA 2.5 to 6.0 VDD-0.5

• Ports 84,85,86,87

Output low

voltage

VOL(1) IOL=10mA 4.5 to 6.0 1.5

VOL(2) IOL=1.6mA 4.5 to 6.0 0.4

VOL(3)

Ports 0,1,3

• IOL=1.0mA

• Every pin's IOL ≤ 1mA

VOL(4) IOL=1.6mA 4.5 to 6.0 0.4

VOL(5)

• Ports 71,72, 73

• Ports 84,85,86,87

• IOL=0.5mA

• Every pin's IOL ≤ 1mA

VOL(6) IOL=1mA 4.5 to 6.0 0.4

VOL(7)

Port 70

• IOL=0.5mA

• Every pin's IOL ≤ 1mA

Tr. resistor

Rpu • Ports 0,1,3

• Ports 70,71,72,73

VOH=0.9VDD

• Ports 84,85,86,87

Hysteresis

voltage

Pin

capacitance

VHIS • Port 1

• Ports 70,71,72,73

RES

•

CP All pins • f=1MHz

Output disable 2.5 to 6.0

• All pins except the measured

terminal: VIN=VSS

• Ta=25°C

Ratings

VDD[V] min. typ. max.

2.5 to 6.0 5

unit

µ

2.5 to 6.0 1

2.5 to 6.0 1

2.5 to 6.0 -1

2.5 to 6.0 -1

V

2.5 to 6.0 0.4

2.5 to 6.0 0.4

2.5 to 6.0 0.4

4.5 to 6.0 15 40 70 Pull-up MOS

kΩ

2.5 to 4.5 25 70 150

0.1VDD

V

2.5 to 6.0 10 pF

A

No.6697-13/21

Page 14

LC865520B/16B/12B/08B/04B

4. Serial Input/Output Cha racteristics at Ta=-30°C to +70°C, VSS=0V

Parameter Symbol Pins Conditions

Cycle t

Low Level

CKCY

CKL

t

SCK0,SCK1 Refer to figure 5 2.5 to 6.0

(1) 2

(1) 1

pulse width

High Level

Input clock

pulse width

Cycle t

Low Level

Serial clock

pulse width

High Level

Output clock

pulse width

Data set-up time

Data hold time

Serial input

Output delay time

(External clock

used for serial

transfer clock)

CKH

t

(1)

CKCY

CKL

t

SCK0,SCK1

(2) 2

(2) 1/2t

• Use a 1kΩ pull up resistor in the

open drain

CKH

t

(2)

output.

• Refer to figure 5

ICK

t

• SI0,SI1

• SB0,SB1

• Data set-up to

SCK0,1

• Data hold from

CKI

t

SCK0,1

• Refer to figure 5

CKO(1)

t

• SO0,SO1

• SB0,SB1

• Use a 1kΩ pull up resistor in the

open drain

output.

• Data hold from

SCK0,1

CKO(2)

Output delay time

(Internal clock

Serial output

used for serial

t

• Refer to figure 5

transfer clock)

VDD[V] min. typ. max.

2.5 to 6.0

4.5 to 6.0 0.1

2.5 to 6.0 0.4

4.5 to 6.0 0.1

2.5 to 6.0 0.4

4.5 to 6.0 7/12

2.5 to 6.0

4.5 to 6.0 1/3

2.5 to 6.0

Ratings

unit

CYC

t

1

CKCY

CKCY

1/2t

µ

CYC

t

+0.2

7/12

CYC

t

+1

CYC

t

+0.2

1/3

CYC

t

+1

s

No.6697-14/21

Page 15

LC865520B/16B/12B/08B/04B

5. Pulse Input Conditions at Ta=-30°C to +70°C, VSS=0V

Parameter Symbol Pins Conditions

pulse width

tPIH(1)

tPIL(1)

tPIH(2)

tPIL(2)

tPIH(3)

tPIL(3)

tPIH(4)

tPIL(4)

tPIL(5)

• INT0, INT1

• INT2/T0IN

INT3/T0IN

(The noise rejection clock

is selected to 1/1.)

INT3/T0IN

(The noise rejection clock

is selected to 1/16.)

INT3/T0IN

(The noise rejection clock

is selected to 1/64.)

RES

• Interrupt acceptable

• Timer0-countable

• Interrupt acceptable

• Timer0-countable

• Interrupt acceptable

• Timer0-countable

• Interrupt acceptable

• Timer0-countable

Reset acceptable 2.5 to 6.0 200

Ratings

VDD[V] min. typ. max.

2.5 to 6.0 1

2.5 to 6.0 2

2.5 to 6.0 32

2.5 to 6.0 128

unit

CYC

t

High/low level

s

µ

6. AD Converter Characteristics at Ta=-30°C to + 70°C, VSS=0V

Parameter Symbol Pins Conditions

Resolution N 8 bit

Absolute precision

(Note 2)

Conversion time tCAD

Analog input

voltage range

input current

ET ±1.5 LSB

AD conversion time = 16 × tCYC

(ADCR2=0) (Note 3)

AD conversion time = 32 × tCYC

(if ADCR2=1) (Note 3)

VAIN VSS VDD V

IAINH VAIN=VDD 1 Analog port

IAINL

AN0 - AN7

VAIN=VSS

Ratings

VDD[V] min. typ. max.

4.5 to 6.0

15.68

(tCYC=

0.98µs)

31.36

(tCYC=

0.98µs)

-1

65.28

(tCYC=

4.08µs)

130.56

(tCYC=

4.08µs)

unit

s

µ

A

µ

(Note 2) Absolute precision excludes the quantizing error (±1/2 LSB).

(Note 3) The conversion time is the time from executing the AD conversion instruction to setting the complete digital

conversion value in the register.

No.6697-15/21

Page 16

LC865520B/16B/12B/08B/04B

7. Sample Current Dissipation Characteristics at Ta=-30°C to +70°C, VSS=0V

Parameter Symbol Pins Conditions

Current drain during

basic operatio n

(Note 4)

IDDOP(1) • FmCF=6MHz by

IDDOP(2) 4.5 to 6.0 3 7

IDDOP(3)

VDD

ceramic resonator

• FsXtal= 32.7 68k Hz

by crystal oscillation

• System clock : CF

oscillation (6MHZ)

• Internal RC oscillation

stops

• 1/1 divided

• FmCF=3MHz by

ceramic resonator

• FsXtal= 32.7 68kHz by

crystal oscillation

• System clock : CF

oscillation (3MHz)

• Internal RC oscillation

stops

• 1/2 divided

Ratings

VDD[V] min. typ. max.

4.5 to 6.0 12 22

2.5 to 4.5 2.0 5

unit

mA

IDDOP(4) 4.5 to 6.0 1.2 3

IDDOP(5)

IDDOP(6) 4.5 to 6.0 35 130

IDDOP(7)

• FmCF=0Hz

(when oscillation stops)

• FsXtal= 32.7 68kHz by

crystal oscillation

• System clock : RC

oscillation

• 1/2 divided

• FmCF=0Hz

(when oscillation stops)

• FsXtal= 32.7 68kHz by

crystal oscillation

• System clock : X'tal

oscillation (32.768kHz)

• Internal RC oscillation

stops

• 1/2 divided

2.5 to 4.5 1.0 2.5

2.5 to 4.5 25 70

Continue.

A

µ

No.6697-16/21

Page 17

LC865520B/16B/12B/08B/04B

Parameter Symbol Pins Conditions

Current drain

in HALT mode

(Note 4)

IDDHALT(1) • HALT mode

IDDHALT(2) 4.5 to 6.0 2.2 5

IDDHALT(3)

IDDHALT(4) 4.5 to 6.0 800 2000

IDDHALT(5)

VDD

• FmCF=6MHz by

ceramic resonator

• FsXtal= 32.768 kHz by

crystal oscillation

• System clock : CF

oscillation (6MHz)

• Internal RC oscill ation

stops

• 1/1 divided

• HALT mode

• FmCF=3MHz by

ceramic resonator

• FsXtal= 32.7 68kHz by

crystal oscillation

• System clock : CF

oscillation (3MHz)

• Internal RC oscillation

stops

• 1/2 divided

• HALT mode

• FmCF=0Hz

(when oscillation stops)

• FsXtal= 32.7 68kHz by

crystal oscillation

• System clock : RC

oscillation

•1/2 divided

Ratings

VDD[V] min. typ. Max.

4.5 to 6.0 7 12

2.5 to 4.5 1.2 3

2.5 to 4.5 500 1500

unit

mA

A

µ

• HALT mode

• FmCF=0Hz

(when oscillation stops)

• FsXtal= 32.7 68k Hz by

crystal oscillation

• System clock : X'tal

oscillation (32.768kHz)

• Internal RC oscillation

stops

• 1/2 divided

2.5 to 4.5 12 55

2.5 to 4.5 0.02 20

in HOLD mode

(Note 4)

IDDHALT(6) 4.5 to 6.0 25 100

IDDHALT(7)

IDDHOLD(1) 4.5 to 6.0 0.06 30 Current drain

IDDHOLD(2)

VDD HOLD mode

(Note 4) The current of the output transistors and pull-up MOS transistors are excluded.

No.6697-17/21

Page 18

LC865520B/16B/12B/08B/04B

Recommended Oscillation Circuit and Characteristics

The recommended circuit parameters are verified by an oscillator manufacturer using a SANYO provided oscillation

evaluation board.

Table 1. Recommended circuit parameters for the main system clock using the ceramic resonator

Recommended circuit

Frequency Manufacturer Oscillator

CSA6.00MG 33pF 33pF

CSTS0600MG03 (15pF) (15pF)

CSA3.00MG 33pF 33pF

CST3.00MGW (30pF) (30pF)

6MHz

3MHz

MURATA

MURATA

parameter

C1 C2 Rd1

470Ω

470Ω

470Ω

470Ω

Table 2. Recommended circuit parameters for the sub system clock using the cryst al osci lla tion

Recommended circuit

Frequency Manufacturer Oscillator

32.768kHz SEIKO EPSON MC-306 18pF 18pF 560Ω 2.5V to 6.0V

parameter

C3 C4 Rd2

The recommended circuit parameter may vary according to the applications. For further assistance, please contact the

oscillator manufacturer keeping the following in mind.

!"

Since the oscillation frequency precision is affected by the wiring capacitance of the application board, etc., is it required

to adjust the oscillation frequency on the production board.

!"

The oscillation frequency and the recommended circuit parameter shown above apply when the operating temperature

range is -30°C to +70°C. When using the clock oscillation circuit under the conditions which exceed the operating

temperature range or in applications that require precision tolerances, please contact the oscillator manufacturer.

!"

If using other circuit parameter than listed above, please contact SANYO.

Since the gain of oscillation circuit is reduced in order to minimize the power consumption of the circuit and the circuit can be

affected by the noise, wiring capacity, etc., it is suggested to take the followings into consideration.

!"

The distance between the clock I/O terminals (XT1, XT2) and external parts should be as short as possible.

!"

The capacitors' (C1, C2) VSS should be placed close to the microcontroller's GND terminal and away from any other

GND.

!"

The signal lines with large current or with rapid state changes should be placed away from the oscillation circuit.

CF2 CF1

Rd1

C1 C2

CF

C3

Figure 1 Ceramic oscillation circuit Figure 2 Crystal oscillation circuit

Operating supply

voltage range

4.5V to 6.0V

4.5V to 6.0V Internal C1, C2

2.5V to 6.0V

2.5V to 6.0V Internal C1, C2

Operating supply

voltage range

XT2 XT1

X’tal

Note

Note

Rd2

C4

No.6697-18/21

Page 19

LC865520B/16B/12B/08B/04B

Power supply

RES

Reset time

VDD

VDD limit

0V

RC oscillation

tmsCF

CF1, CF2

tssXtal

XT1, XT2

Operation mode

Unstable

Reset

Instruction

execution

OCR6=1

Instruction execution

<Reset time and oscillation stabilizing time>

HOLD release signal

Valid

RC oscillation

tmsCF

CF1, CF2

tssXtal

XT1, XT2

Operation mode

HOLD

Instruction execution

<HOLD release signal and oscillation stabilizing time>

(OCR6=1when entering HOLD)

Figure 3 Oscillation stabilizing time

No.6697-19/21

Page 20

LC865520B/16B/12B/08B/04B

m

VDD

RES

R

RES

RES

C

(Note) Select CRES and RRES value to assure that

at least 200µs reset time is generated after

the VDD becomes higher than the minimu

operating voltage.

Figure 4 Reset circuit

0.5VDD

<AC timing point>

tCKCY

VDD

SCK0

SCK1

SI0

SI1

SO0, SO1

SB0, SB1

tCKO

<Timing>

tCKH tCKL

1kΩ

tCKI tICK

50pF

<Test load>

Figure 5 Serial input / output test condition

tPIH tPIL

Figure 6 Pulse input timing condition

No.6697-20/21

Page 21

memo:

LC865520B/16B/12B/08B/04B

No.6697-21/21

PS

Loading...

Loading...