Page 1

Ordering number : ENN*6727

LC651306A/04A/02A/01A

4-Bit Single-Chip Microcontroller

for Small-Scale Control Applications

Preliminary

Overview

The LC651306A, LC651304A, LC651302A, LC651301A belong to our 4-bit single-chip microcontroller LC6500 series

fabricated using CMOS process technology. They are ideally suited for use in small-scale control applications. Their basic

architecture and instruction set are the same. These microcontrollers include an 8-input 8-bit A/D converter and are

appropriate for use in a wide range of applications. That range includes applications with a small number of control circuits

that were previously implemented in standard logic, and applications with a larger scale such as home appliances,

automotive equipment, communications equipment, office equipment, and audio equipment such as decks and players.

Features

1) CMOS technology for a low-power consumption operation (A standby function that can be invoked under program

control is also provided.)

2) ROM/RAM

LC651306A ROM : 6K × 8 bits, RAM : 256 × 4 bits

LC651304A ROM : 4K × 8 bits, RAM : 256 × 4 bits

LC651302A ROM : 2K × 8 bits, RAM : 256 × 4 bits

LC651301A ROM : 1K × 8 bits, RAM : 256 × 4 bits

3) Instruction set : 81 instructions common to all microcontrollers of the LC6500 series

4) Wide operating voltage range : 2.5V to 6.0V

5) Instruction cycle time : 0.92 µs

6) On-chip serial I/O port

CMOS IC

Ver.0.90

62600

91400 RM (IM) TY No.6727-1/21

Page 2

LC651306A/04A/02A/01A

7) Flexible I/O port

• Number of ports : 5 ports / 18 pins (max.)

• All ports : Input / output common

Input / output capacity voltage 15V max. (open-drain specification C and D only)

Output current 20 mA max. sink current (Can drive an LED

directly)

• Support options for system specification

A. Open drain output, pull-up resistor : all ports in bit unit

B. Output level in the reset mode : high/low level for port C and D specified in 4-bit unit

8) Interrupt function

Interrupt by timer overflow (can be tested under program control)

Interrupt by the state of the

pin or completion of transmission/reception at serial I/O port (can be tested under

INT

program control)

9) Stack level : 8 levels (common use with interrupt)

10) Timer : 4-bit variable prescaler + 8-bit programmable counter

11) Clock oscillation options for user’s intended system

• Oscillator circuit options : two-pin RC oscillator

two-pin ceramic osci llator

• Divider circuit options : No divider

built-in divide by 3

built-in divide by 4

12) Continuous square wave output (64 times of the cycle time)

13) AD converter (successive approximation)

• Precise conversion (expressed in 8 bits), 8 input channels

14) Watchdog timer

• RC circuit time constant

• Watchdog timer reset function can be assigned to an external pin by the option.

15) Low voltage detection circuit

• Can be implemented by the option.

16) Factory shipment

• DIP24S, MFP24S, SSOP24

No.6727-2/21

Page 3

LC651306A/04A/02A/01A

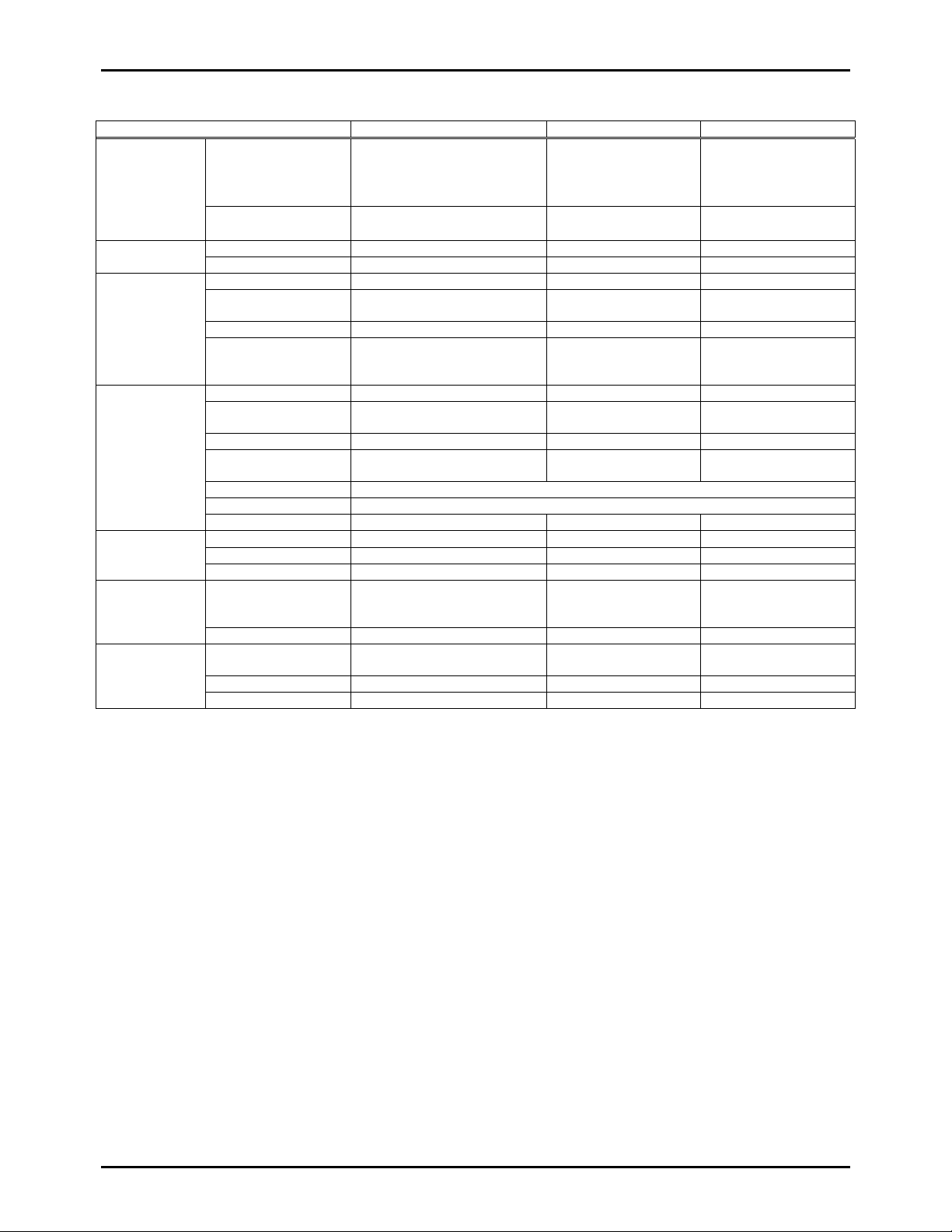

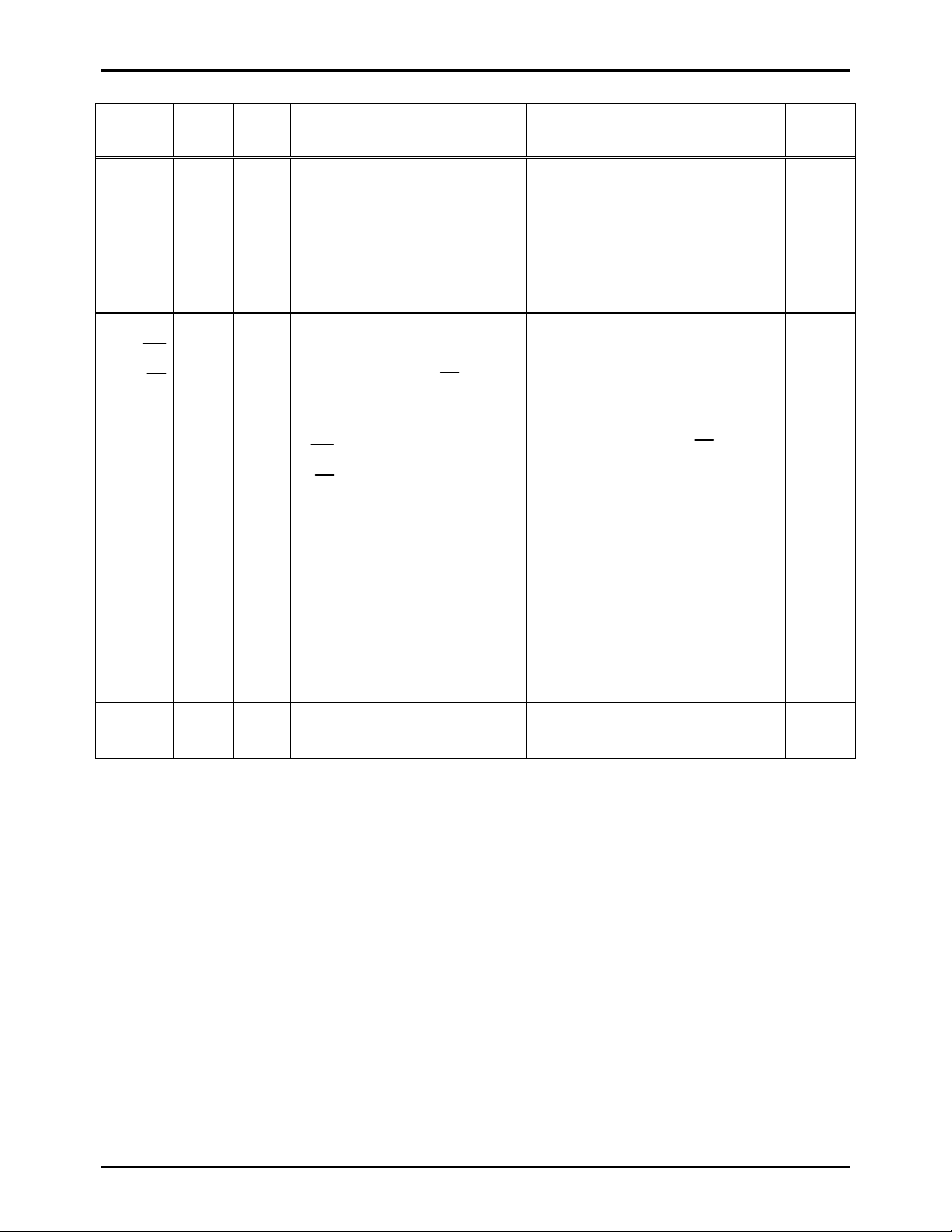

Function Table

Parameter LC651306A/04A/02A/01A LC651154F/1152F LC651432F/1431F

Memory

On-chip

functions

I/O ports

Characteristics

Oscillator

Other items

Note: The above oscillator and oscillator circuit constants are tentative. They will be announced as the recommended circuits

for these microcontrollers are determined. Please confirm the progress of these developments periodically.

ROM

RAM

Instruction set 81 80 80 Instructions

Table reference Supported Supported Supported

Interrupt 1 external, 1 internal 1 external, 1 internal 1 external, 1 internal

Timer 4-bit variable prescaler + 8-bit

Stack level 8 8 4

Standby function Standby mode by the HALT

Port number 18 I/O port pins 22 I/O port pins 25 I/O port pins (max.)

Serial port Input and output in 4 or 8 bit units Input and outp ut in 4 or 8

I/O voltage capacity 15 V max. 15 V max. 15 V max.

Output current 10 mA typ. 20 mA max. 10 mA typ. 20 mA

I/O circuit type Open drain (N-channel) or pull- up resistor output option can be specified in 1- bit unit

Output level at reset High or low level output can be selected in port unit (ports C and D only)

Square wave output Supported Supported Supported

Minimum cycle time

Supply voltage 2.5 to 6 V 2.5 to 6 V 3 to 6 V

Supply current 1.5 mA typ. 2 mA typ. 1.5 mA typ.

Oscillator RC (800 kHz typ.)

Divider circuit option 1/1, 1/3, 1/4 1/1 1/1

Package DIP24S MFP24S SSOP24 DIP30S-D MFP30S

Watchdog timer Supported Supported Not supported

OTP Only DIP24S MFP24S Only DIP30S-D MFP30S Only DIP30S-D MFP30S

6144 × 8 bits (1306A)

4096 × 8 bits (1304A)

2048 × 8 bits (1302A)

1024 × 8 bits (1301A)

256 × 4 bits

(1306A/04A/02A/01A)

timers

instruction s upported

0.92 µs (VDD ≥ 2.5 V) 0.92 µs (VDD ≥ 2.5 V) 0.92 µs (VDD ≥ 3 V)

Ceramic (400k, 800k,1MHz,

4MHz)

4096 × 8 bits (1154F)

2048 × 8 bits (1152F)

256 × 4 bits

(1154/1152F)

4-bit variable prescaler +

8-bit timers

Standby mode by the

HALT instruction

supported

bit units

max.

Ceramic 4 MHz Ceramic 4 MHz

SSOP30

2048 × 8 bits (1432F)

1024 × 8 bits (1431F)

128 × 4 bits (1432F)

64 × 4 bit (1431F)

4-bit fixed prescaler +

8-bit timers

Standby mode by the

HALT instruction

supported

Input and output in 4 or 8

bit units

10 mA typ. 20 mA

DIP30S-D MFP30S

SSOP30

max.

No.6727-3/21

Page 4

LC651306A/04A/02A/01A

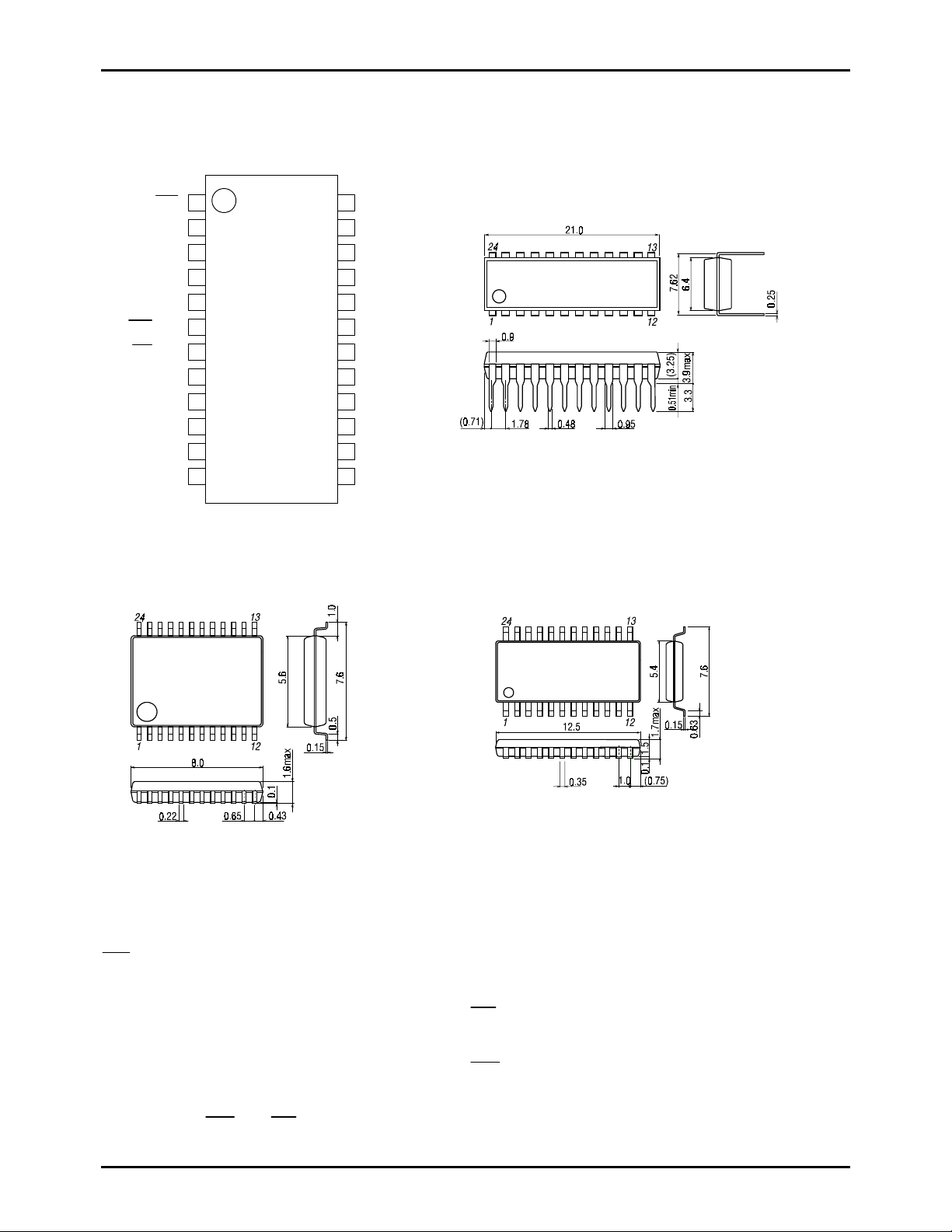

Pin Assignment

DIP24S, SSOP24, MFP24S

PE0/SQR

PE1/WDR

PF0/SI/AD4

PF1/SO/AD5

PF2/

SCK

PF3/

INT

PA0/AD0

PA1/AD1

PA2/AD2

PA3/AD3

RES

/AD6

/AD7

VDD

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

OSC1

OSC2

TEST

VSS

PD3

PD2

PD1

PD0

PC3

PC2

PC1

PC0

Package Dimensi on

(unit : mm)

3067A

SANYO : DIP24S(300mil)

Package Dimension

(unit : mm)

3175A

Package Dimensi on

(unit : mm)

3112A

SANYO : SSOP24(275mil) SANYO : MFP24S(300mil)

Pin Functions

OSC1, OSC2 : Ceramic Oscillator fo r OSC, RC TEST : Test

: Reset AD0-AD7 : AD converter analog input

RES

PA0-3 : Common I/O port A0-3 SQR : Square wave output

PC0-3 : Common I/O port C0-3 WDR : Watch Dog Reset pin

PD0-3 : Common I/O port D0-3

PE0-1 : Common I/O port E0-1 SI : Serial Input pin

PF0-3 : Common I/O port F0-3 SO : Serial Output pin

Notes: • SQR and WDR are common with PE0 and PE1 respectively.

SI, SO,

•

SCK

, and

are common with PF0 to PF3 respectively.

INT

: Interrupt Request pin

INT

: Serial Clock input/output pin

SCK

No.6727-4/21

Page 5

LC651306A/04A/02A/01A

g

g

PA0-3

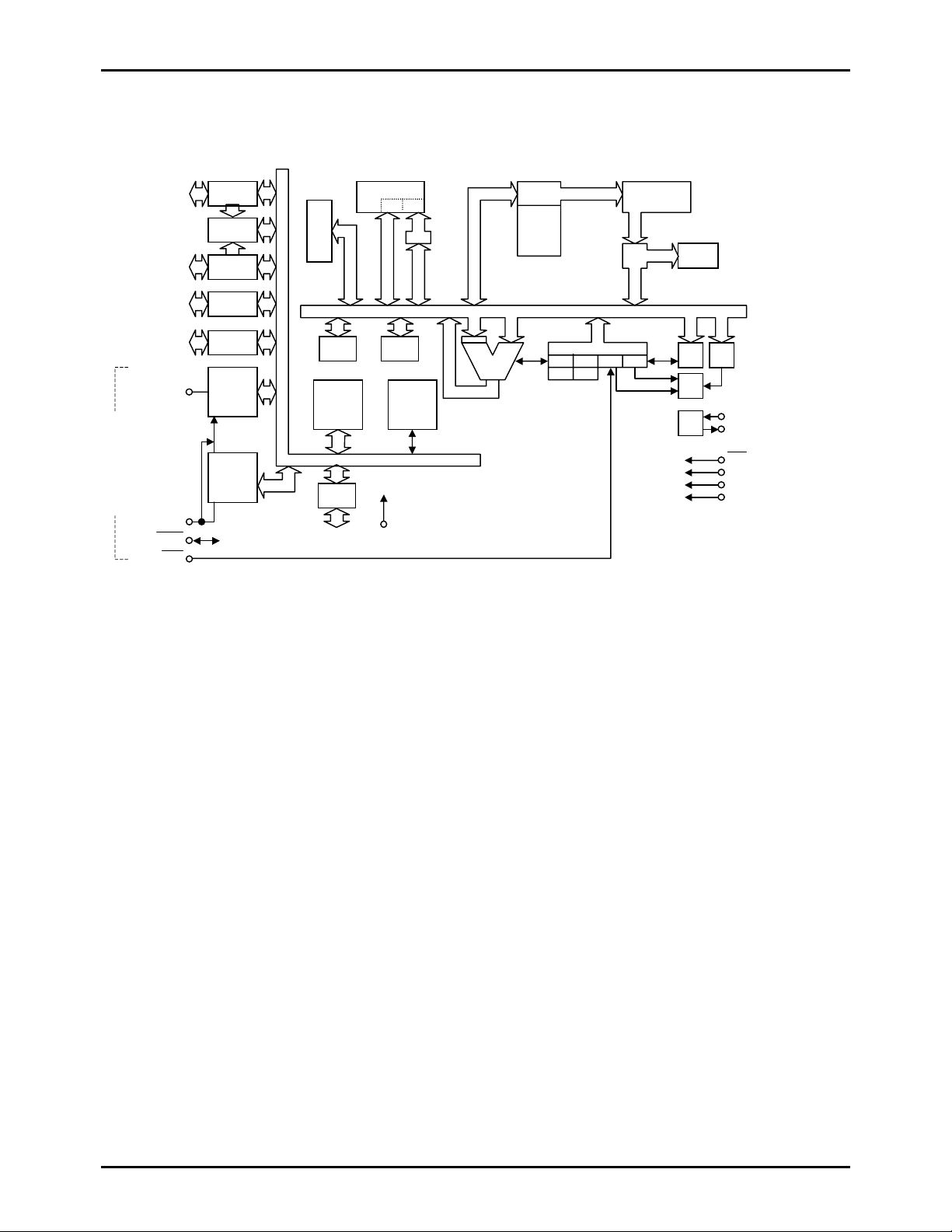

System Block Diagram

LC651306A/1304A/1302A/1301A

Shared with port F

PF2/SCK

PF3/INT

AD0-3

PF0-3

AD4-7

PC0-3

PD0-3

PF1/SO

4/8 bit

4 bit

PF0/SI

Port A

8-BIT

ADC

Port F

Port C

Port D

Serial

shift

register

lower di

Serial

shift

register

hi

4/8 bit

her digit

I/O Buffer

Serial

mode

register

it

Port E

PE0-1

RAM

F WR

E AC

Serial

mode

register

I/O Bus

WDR

DP

System Bus

ALU

PC

STACK

to

STACK

CF

CSF

STS

ZF

EXTF

RAM : Data Memory ROM : Program Memory

F : Flag PC : Program Counter

WR : Working Register INT : Interrupt control

AC : Accumulator IR : Instruction Register

ALU : Arithmetic and Logic Unit I.DEC : Instruction Decoder

DP : Data Pointer CF, CSF : Carry Flag, Carry Save Flag

E : E register ZF, ZSF : Zer o Flag, Zero Sav e Flag

CTL : Control register EXTF : External Interrupt Request Flag

OSC : Oscillation Circuit TMF : Internal Interrupt Request Flag

TM : Timer

STS : Status register

IR

TMF

ROM

I.DEC

TM CTL

INT

OSC

OSC1

OSC2

RES

TEST

VDD

VSS

No.6727-5/21

Page 6

LC651306A/04A/02A/01A

P

o

P

Development Support

The following are currently in the development stage and will soon be available to the user for the development of the

LC651306A/04A/02A/01A.

1. User’s manual

Refer to the “LC65F1306A/LC651300 series user’s manual.”

2. Development tool manual

Refer to the “EVA86000 Development Tool Manual for 4-bit microcontrollers.”

3. Software manual

“LC65/66 Series Software Manual”

4. Development tool

a. For program development (EVA86000 system)

b. For program evaluation

Microcontroller with Flash ROM (LC65F1306)

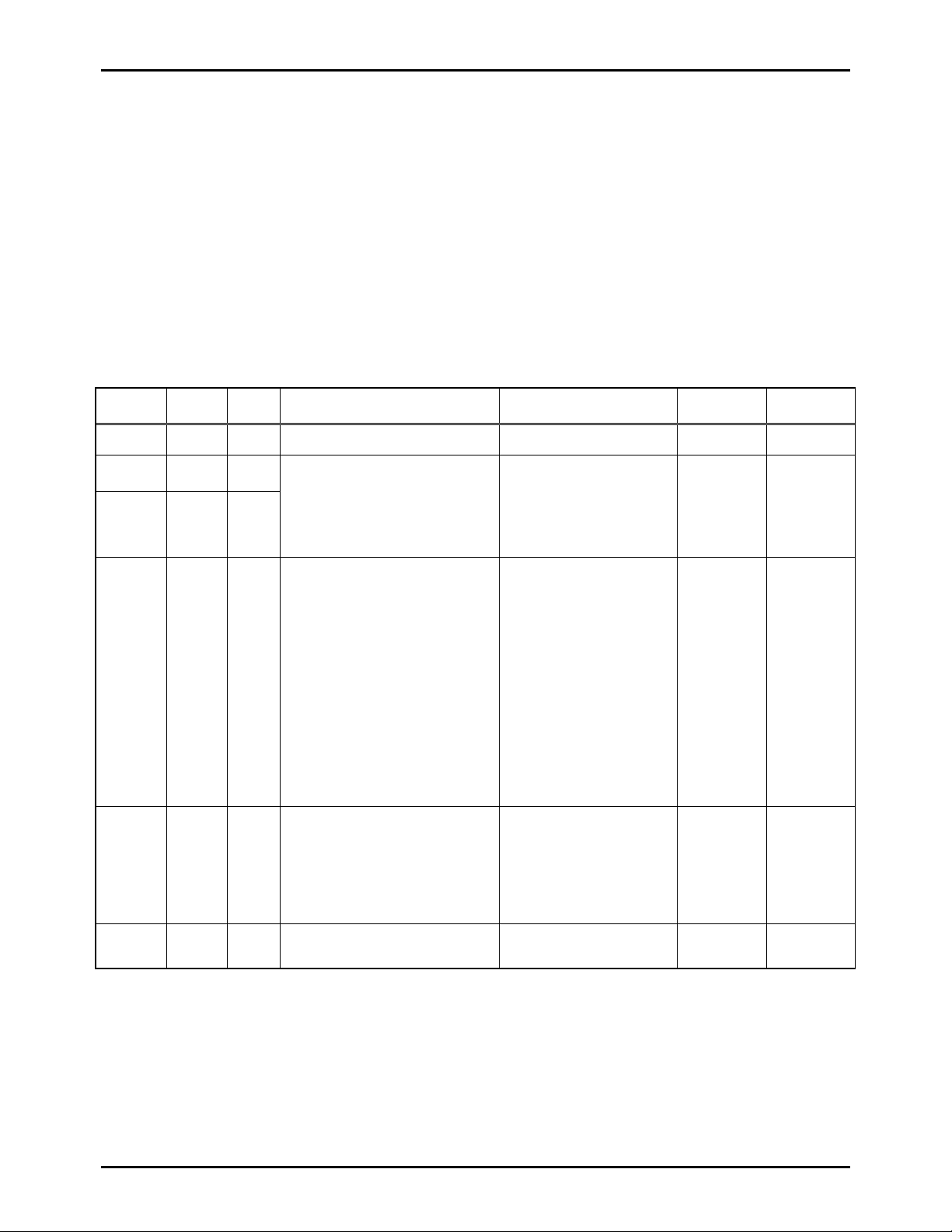

Pin Functions

Symbol

VDD 1 - Power supply - - VSS 1 -

OSC1 1 Input

OSC2 1 Output

PA0-PA3/

AD0-AD3

PC0-PC3 4 I/O •I/O port C0 to C3

PD0-PD3 4 I/O •I/O port D0 to D3

Number

of pins

4 I/O • I/O port A0 to A3

I/O Function Option At reset

Pins for connecting system clock

•

oscillation RC or ceramic resonator.

Leave OSC2 open when OSC1 is used

•

for an external clock input

Input in 4-bit unit (IP instruction)

Output in 4-bit unit

(OP instruction)

Testing in 1-bit unit

(BP, BNP instructions)

Set and reset in 1-bit unit

(SPB, RPB instructions)

PA3 is used for standby mode control.

•

Chattering should not be occurred on

•

the PA3 during HALT instruction

execution.

All four pins have shared function.

•

PA0/AD0:AD converter input AD0

PA1/AD1:AD converter input AD1

PA2/AD2:AD converter input AD2

PA3/AD3: converter input AD3

The port functions are identical to those

of PA0 to PA3 (See note).

The output during a reset can be

•

selected to be either high or low as an

option.

Note: This port has no standby mode

The port functions and options are

identical to those of PC0 to PC3.

control function.

(1) Two-pin RC oscillator,

external clock

(2) Two-pin ceramic oscillator

(3) Divider option

1. No divider

2. Divide by 3

3. Divide by 4

(1) Open-drain output

(2) Pull-up resistor

(1), (2) can be specified in bit

unit.

(1) Open-drain output

(2) Pull-up resistor

(3) High level output during reset.

(4) Low level output during reset.

(1) and (2) can be specified in

•

bit unit.

(3) and (4) are specified 4 bits

•

at a time

Same as PC0 to PC3. Same as PC0 t

- -

High-level

output (The

output

N-channel

transistor s in

the off state.)

High-level

•

output.

Low-level

•

output.

(Depending on

options

selected)

PC3.

Handling

when unused

Select the

open-drain

output option

and connect to

VSS.

Same as PA0 to

A3.

Same as PA0 to

A3.

No.6727-6/21

Page 7

/WDR

SCK

INT

Number

of pins

2 I/O

4 I/O

1 Input

I/O Function Option At reset

I/O port E0 to E1

•

Input in 4-bit unit (IP instruction)

Output in 4-bit unit (OP instruction)

Set and reset in 1-bit unit

(SPB and PRB instructions)

Testing in 1-bit unit

(BP and BNP instructions)

PE0 also has a continuous pulse (64 Tcyc)

•

output function.

PE1 becomes the watchdog reset pin WDR

•

when selected as an option.

I/O port F0 to F3

•

The port functions and options are identical

to those of PE0 to PE1 (See note).

PF0 to PF3 have shared functions with the

•

serial interface pins and the

The function can be selected under program

control.

SI... Serial input pin

SO...Serial output pin

SCK

INT

The serial I/O function can be switched

between 4-bit and 8-bit transfers under

program control.

Note: There is no continuous pulse output

function.

All four pins have shared function.

•

PF0/AD4: AD converter input AD4

PF1/AD5: AD converter input AD5

PF2/AD6: AD converter input AD6

PF3/AD7: AD converter input AD7

System reset input

•

Provide an external capacitor for the

•

power-on reset.

Apply low level to this pin for 4 or more

•

clock cycles to reset and restart the program.

Test pin for LSI.

•

This pin must be connected to VSS during

normal operation.

Symbol

PE0-PE1

PF0/SI/AD4

PF1/SO/AD5

PF2/

/AD6

PF3/

/AD7

RES

TEST 1 Input

LC651306A/04A/02A/01A

input.

INT

...Input and output of the serial clock

signal.

...Interrupt request signal

Handling

when

unused

(1) Open -drain output

(2) Pull-up resistor

Options (1) or (2) can be

•

specified in bit unit.

(3) Normal port PE1

(4) Watchdog reset WDR

Either options (3) or (4)

•

can be selected.

Identical to those for PA0 to

PA3.

- - -

- - This pin

High level

output (The

output

N-channel

transistor s in

the off state)

Identical to those

for PA0 to PA3.

The serial port

functions are

disabled.

The interrupt

source is set to

.

INT

Identical to

those for

PA0 to PA3.

Identical to

those for

PA0 to PA3.

must be

connected to

VSS.

No.6727-7/21

Page 8

Oscillator Circuit Options

r

Option Circuit Conditions and notes

External clock

Two-pin RC oscillator

Ceramic oscillator

Divider Circuit Options

Option Circuit Conditions and notes

No divider

(1/1)

Built-in divide-by-three

circuit

Built-in divide-by-fou

circuit

Cext

Ceramic

Resonator

fOSC

Oscillator circuit

fOSC

Oscillator circuit

fOSC

Oscillator circuit

LC651306A/04A/02A/01A

OSC1

OSC1

OSC

Rext

C1

C2

OSC1

OSC2

R

Divide by 3

Divide by 4

fOSC

3

fOSC

4

Timing

Generator

Timing

Generator

Timing

Generator

The OSC2 pin should be left

open.

The oscillator frequency or external clock

•

frequency should not exceed 4330 kHz.

• This option can only be used with the external

clock and the ceramic oscillator options.

• The oscillator frequency or external clock

frequency should not exceed 4330 kHz.

This option can only be used with the external

•

clock and the ceramic oscillator options.

The oscillator frequency or external clock

•

frequency should not exceed 4330 kHz.

Note: The following table summarizes the oscillator and divider circuit options. When selecting the divider option, the

relationship between frequency and cycle time must be taken into account.

No.6727-8/21

Page 9

LC651306A/04A/02A/01A

LC651306A/1304A/1302A/1301A Oscillator Options

Circuit type Frequency

Ceramic resonator

External clock (used with the

2-pin RC oscillator circuit)

External clock used with the

ceramic oscillator option

400 kHz 1/1 (10µs) 2.5 to 6V Can not be used with the divide-by-three and

800 kHz 1/1 (5µs)

1 MHz 1/1 (4µs)

4 MHz 1/1 (1µs)

200 k to 4330 kHz

600 k to 4330 kHz

800 k to 4330 kHz

circuit constants. When using other constants by

necessity, use th e frequency and VDD range i dentical to

the external clock written above.

External clock drive is not possible. To use external clock drive, select the 2-pin RC oscillator option.

Divider option

(Cycle time)

1/3 (15µs)

1/4 (20µs)

1/3 (12µs)

1/4 (16µs)

1/3 (3µs)

1/4 (4µs)

1/1 (20 to 0.92µs)

1/3 (20 to 2.77µs)

1/4 (20 to 3.70µs)

VDD range Notes

2.5 to 6V

2.5 to 6V

2.5 to 6V

2.5 to 6V

2.5 to 6V

2.5 to 6V

2.5 to 6V

2.5 to 6V

2.5 to 6V

2.5 to 6V

2.5 to 6V

2.5 to 6V

2.5 to 6V Two-pin RC Use the no divider circuit option and the recommended

divide-by-four options.

Port C and D Output level Option During Reset

The Output level of the C and D ports at reset can be selected from the following two options in 4-bit unit.

Option Conditions and notes

High level output at reset Ports C and D in 4-bit unit

Low level output at reset Ports C and D in 4-bit unit

Port Output Type Op tion

The following two options may be selected for the I/O ports individually (bit units).

Option Circuit Ports

1. Open-drain output

2.Built-in pull-up resistor

Ports A, C, D, E and F

Watchdog Reset Option

This option allows the user to select how the PE1/WDR pin is to be used. It can be used as the normal port PE1, or used as the

watchdog reset pin WDR.

No.6727-9/21

Page 10

LC651306A/04A/02A/01A

1. Absolute Maximum Ratings at Ta=25°C, VSS=0V

Parameter Symbol Conditions

Maxi mum supply

VDD max VDD -0.3 to +7.0

Applicable pins

and notes

Ratings unit

voltage

Output voltage VO OSC2 Output voltage

generated can be

over the maximum

limit of the VDD.

VI (1) OSC1 (Note 1) -0.3 to VDD+0.3 Input voltage

RES

-0.3 to VDD+0.3

-0.3 to +15

I/O voltage

VI (2) TEST,

AV

, AV-

+

VIO (1) PC0 to 3, PD0 to 3 Open-drain

specification ports

VIO (2) PC0 to 3, PD0 to 3 Pull-up resistor

-0.3 to VDD+0.3

specification ports

VIO (3) PA0 to 3, PE0, 1, PF0 to 3 -0.3 to VDD+0 .3

Peak output

IOP I/O Port -2 to +20

current

Average output

current

IOA Average current applied to a pin for

100 ms

IOA(1)

∑

The total curr ent o f PC0 to 3, PD 0 to 3

and PE0 to 1. (Note 2)

I/O Port -2 to +20

PC0 to 3

-15 to +100

PD0 to 3

PE0 to 1

Maximum power

consumption

Operating

IOA(2)

∑

The total current of PF0 to 3 and PA0

to 3. (Note 2)

Pd max (1)

Pd max (2)

Pd max (3)

Ta=-40 to +85°C (DIP package)

Ta=-40 to +85°C (MFP package)

Ta=-40 to +85°C (SSOP package)

Topr -40 to +85

PF0 to 3

-15 to +100

PA0 to 3

310

220

160

temperature

Storage

Tstg -55 to +125

temperature

V

mA

mW

°C

No.6727-10/21

Page 11

LC651306A/04A/02A/01A

k

k

2. Recommended Operating range at Ta=-40 to +85°C, VSS=0V, VDD=2.5 to 6.0V (Unless othe r wis e specified)

Parameter Symbol Conditions

Operating supply voltage VDD VDD 2.5 6.0 V

Standby supply voltage VST RAM and register values retained.

High level input voltage VIH(1) Output Nch Tr. off Port C, D with

VIH(2) Output Nch Tr. off Port C, D with

VIH(3) Output Nch Tr. off Port A, E, F 0.7VDD VDD

VIH(4) Output Nch Tr. off

VIH(5) Output Nch Tr. off

VIH(6) VDD=1.8 to 6V

VIH(7) External clock specifications OSC1 0.8VDD VDD

Low level

input voltage

Operating frequency

(cycle time)

External clock conditions

Frequency

Pulse width textH,

Rising/falling time textR,

Recommended oscillation

constants

Two-pin RC oscillator

Ceramic oscillator

(Note 4)

VIL(1) Output Nch Tr. off VDD=4 to 6 V Port VSS 0.3VDD

VIL(2) Output Nch Tr. off 2.5 to 6V Port VSS 0.25VDD

VIL(3) Output Nch Tr. off VDD=4 to 6 V

VIL(4) Output Nch Tr. off 2.5 to 6V

VIL(5) External cloc

VIL(6) External cloc

VIL(7) VDD=4 to 6V TEST VSS 0.3VDD

VIL(8) 2.5 t o 6V TEST VSS 0.25 VDD

VIL(9) VDD=4 to 6V

VIL(10) 2.5 to 6V

fop

(Tcyc)

text

textL

textF

Cext

Rext

Fig. 3 See Table 1

(Note 3)

VDD=4 to 6V OSC1 VSS 0.25VDD

specification

2.5 to 6V OSC1 VSS 0.2VDD

specification

VDD=2.5 to 6V 200

Fig. 1

VDD=2.5 to 6 V OSC1

VDD=2.5 to 6V OSC1 69 ns

VDD=2.5 to 6V OSC1 50

Fig. 2 VDD=2. 5 to 6V OSC1, OSC2

Applicable

pins and notes

VDD 1.8 6.0

open-drain

specifications.

pull-up resistor

specifications.

,

,

INT

INT

SCK

SCK

,

,

, SI

, SI

SCK

SCK

The

and SI pin with

open-drain

specifications.

The

and SI pin with

pull-up resistor

specifications.

RES

INT

INT

RES

RES

min. typ. max.

0.7VDD 13.5

0.7VDD VDD

0.8VDD VDD

,

0.8VDD VDD

,

0.8VDD VDD

VSS 0.25VDD

VSS 0.2VDD

VSS 0.25VDD

VSS 0.2VDD

(20)

200

Ratings

4330

270±5%

5.6±1%

(0.92)

4330

pF

unit

kHz

(µs)

kHz

kΩ

No.6727-11/21

Page 12

LC651306A/04A/02A/01A

3. Electrical Characteristics at Ta=-40 to +85°C, VSS=0V, VDD=2.5 to 6.0V (Unless otherwise specified)

Parameter Symbol Conditions

Input High level

current

Input Low level

current

Output High level

voltage

VOH (2)

voltage

Hysteresis

Voltage

High level

threshold

voltage

Low level

threshold

Schmitt characteristics

voltage

Current consumption

Two-pin RC oscillator

Ceramic osci llator IDDOP (2)

IDDOP (3)

IDDOP (4)

IDDOP (5)

IDDOP (6)

External clock IDDOP (7)

IDDOP (8)

Standby mode IDDst Output N-channel VDD=6V

IIH(1) Output Nch Tr. OFF

IIH (2) Output Nch Tr. OFF

IIH (3) When external clock is used,

IIL(1) Output Nch Tr. OFF

IIL(2) Output Nch Tr. OFF

IIL(3) VIN=VSS

IIL(4) When external clock is used,

VOH (1)

VOL(1) IOL=10 mA

VOL(2) IOL=1 mA,

VHIS 0.1VDD

VtH 0.4VDD 0.8VDD

VtL

IDDOP (1)

(including OFF leak current

of Nch Tr.)

VIN=+13.5V

(including OFF leak current

of Nch Tr.)

VIN=VDD

VIN=VDD

VIN=VSS

VIN=VSS

VIN=VSS

IOH=-50 µA

VDD=4.0 to 6 .0V

IOH=-10 µA

VDD=4.0 to 6 .0 V

IOL of each Port : 1 mA or less

Output N-channel transistors are off

•

when operating

Port = VDD

•

Fig. 2, fosc=800 kHz (typical)

•

Fig. 3, 4 MHz, no divider

•

Fig. 3, 4 MHz, divide-by-three circuit

•

Fig. 3, 4 MHz, divide-by-four circuit

•

Fig. 3, 400 kHz

•

Fig. 3, 800 kHz

•

200 kHz to 4330 kHz, no divider

•

600 kHz to 4330 kHz, divide-by-three

•

circuit

800 kHz to 4330 kHz, divide-by-four

•

circuit

transistor off,

Ports=VDD VDD=2.5V

Applicable pins and

notes

Port C and D with the

open-drain

specifications

Port A, E and G with

the open-drain

specifications

OSC1 1.0

Ports with the

open-drain

specifications

Ports with the pull-up

resistor specifications

RES

OSC1 -1.0

Ports with the pull-up

resistor specifications

Ports with the pull-up

resistor specifications

Port 1.5 Output Low level

Port 0.5

,

RES

SI, and schmitt

specification OSC1

(Note 5)

VDD

VDD 2.0 6

VDD 1.5 5

VDD 1.5 4

VDD 1.0 2.5

VDD 1.5 4

VDD 2.0 6

VDD 1.5 5

VDD

VDD

INT, S

CK

5.0 µA

1.0

-1.0

-1.3 -0.35 mA

-45 -10

VDD-1.2 V

VDD-0.5

,

0.2VDD 0.6VDD

0.05

Ratings

min. typ. max.

1.5

0.025

10

unit

A

µ

mA

4

A

µ

5

No.6727-12/21

Page 13

LC651306A/04A/02A/01A

Parameter Symbol Conditions Pin

Oscillation characteristics

Ceramic resonator

Frequency

Oscillation stabilizing

time

(Note 8)

Two-pin RC oscillator

frequency

Pull-up resistance

I/O port

RES

External reset

characteristics

Reset time

Pin capacitance Cp f=1MHz,

Serial clock

Input clock Cycle time tCKCY(1)

Output clock Cycle

time

Input clock low level

pulse width

Output clock low

level pulse width

Input clock high level

pulse width

Output clock high level

pulse width

Data setup time

Data hold time

Serial output

Output delay time

fCFOSC

(Note 7)

tCFS

fMOSC

RPP

Ru VIN=VSS VDD=5V

tRST

tCKCY(2)

tCKL(1)

tCKL(2)

tCKH(1)

tCKH(2)

tICK

tCKI

tCKO

Fig. 3 fo=400kHz

•

Fig. 3 fo=800kHz

•

Fig. 3 f o=1MHz

•

Fig. 3 fo=4MHz, with no divider,

•

divide-by-three, or divide-by-four circuit

Fig. 4 fo=400kHz

•

Fig. 4 fo=800kHz, 1MHz, or 4MHz,

•

with no divider, divide-by-three, or

divide-by-four circuit

Fig. 2 Cext=270pF±5%

•

Fig. 2 Rext=5.6kΩ±1%

•

Output N-channel transistors off

•

VIN=VSS VDD=5V

•

Pins except for tested pins, VIN=VSS

Fig. 6

Fig. 6

Fig. 6

Fig. 6

Fig. 6

Fig. 6

Specified for the rising edge of

Fig. 6

Specified for the falling edge of

•

Select only Nch OD option, and add

•

external 1kΩ resistor and external 50pF

capacitor.

Fig. 6

•

SCK

SCK

OSC1,OSC2

OSC1,OSC2

OSC1,OSC2

OSC1,OSC2

10

OSC1, OSC2 587 800 1298 kHz

Pull-up resistor

specification port

RES

10 pF

SCK

SCK

SCK

SCK

SCK

SCK

SI

SI 0.2

SO

min. typ. max.

392

784

980

3920

8 14 30

200 500 800

2.0

0.6

0.6

0.2

Ratings

400

800

1000

4000

See Fig.5

64×tCYC

(Note 9)

32×tCYC

32×tCYC

Serial input

unit

408

kHz

816

1020

4080

ms

10

KΩ

s

µ

0.4

No.6727-13/21

Page 14

LC651306A/04A/02A/01A

Parameter Symbol Conditions

Pulse output

Period

High level pulse width

Low level pulse width

Resolution 8 bit

Absolute

precision

Conversion time TCAD

Analog input

voltage range

Analog port

A/D converter characteristics

input current

Recommended

constants

(Note 10)

Clear time

(discharge)

Clear period

(charge)

Recommended

constants

(Note 10)

Watch dog timer

Clear time

(discharge)

Clear period

(charge)

tPCY

tPH

tPL

AV+=VDD

VAIN AD0 to AD7 VSS VDD V

IAIN

Cw When PE1 is using open-drain WDR

Rw When PE1 is using open-drain WDR

Rl When PE1 is using open-drain WDR

tWCT Fig.8 WDR 100

tWCCY Fig.8

Cw When PE1 is using open-drain WDR

Rw When PE1 is using open-drain WDR

Rl When PE1 is using open-drain WDR

tWCT Fig.8 WDR 10

tWCCY Fig.8

Fig.7

•

TCYC=4 × system clock

•

Select only Nch OD option,

•

and add external 1kΩ resistor

and external 50pF capacitor.

AV

=VSS

-

When AD speed is

1/1=26*TCYC

When AD speed is

1/2=51*TCYC

Including the output off leakage

current.

VAIN=VDD

VAIN=VSS

VDD[V]

3 to 6

3 to 6

2.5 to 6

Applicable pins

Ratings

and notes

PE0

PE0

PE0

24

47

AD0 to AD7

(The shared I/O

function ports

have open-drain

specification)

WDR 36 ms

WDR 4.2 ms

min. typ. max.

(TCYC=

0.92µs)

(TCYC=

0.92µs)

1

-1

64×TCYC

32×TCYC

10%

±

32×TCYC

10%

±

1

±

312

612

0.1±5%

680±1%

100±1%

0.01±5%

680±1%

100±1%

2

±

(TCYC

=12µs)

(TCYC

=12µs)

unit

s

µ

LSB

s

µ

A

µ

F

µ

kΩ

Ω

s

µ

F

µ

kΩ

Ω

s

µ

Notes:

(1) When oscillated internally under the oscillating conditions in Fig.3, generated voltage can be over the maximum limit of

the VDD.

(2) Average for 100 ms period.

(3) Operating supply voltage VDD must be held until the microcontroller enters in the standby mode after the execution of the

HALT instruction. Any chattering should not be generated at the PA3 pin during the HALT instruction execution cycle.

(4) Recommended circuit constants that are verified by the oscillator manufacturer, using oscillator characteristic evaluation

board selected by SANYO.

(5) The OSC1 pin will have schmitt characteristics when external clock oscillator or the two-pin RC oscillator is selected as

an oscillation option.

(6) These are the results of testing using the value at each part on the Fig.3 circuit which is recommended by SANYO. These

results do not include the current applied to the output transistor, nor the current applied to the transistor with a pull-up

resistor on the LSI.

(7) fCFOSC is the frequency when the values in table 1 are used.

(8) T his indicates the elapsed time that is required before the oscillation becomes stable after the VDD exceeds the minimum

limit of the operation supply voltage.

No.6727-14/21

Page 15

LC651306A/04A/02A/01A

(9) TCYC=4×system clock period

(10) When used in an environment that may result in condensation, note that a current leakage between PE1 and adjacent pins

or a current leakage at external integration circu it us ing R and C could occur.

OSC1 (OSC2)

External Clo ck

OPEN

VDD

0.8VDD

0.2VDD

textF

textL

text

textR

textH

VSS

Figure 1 External Clock Input Waveform

OSC2 OSC1

OSC2 OSC1

Cext

Rext

C1 C2

Ceramic

Resonator

Figure 2 Two-pin RC Oscillator Circuit Figure 3 Ceramic Resonator Circuit

No.6727-15/21

Page 16

LC651306A/04A/02A/01A

f

VDD

OSC

Oscillation

stabilizing time

Figure 4 Oscillation Stabilizing Time

Table 1 Recommended Ceramic Resonator constants

Data will be added once evaluation has been

completed.

tCFS

The lowest limit o

the operating VDD

OV

Stable oscillation

RES

CRES(=0.1 µF)

Figure 5 Reset Circuit

(Note) If measured from the instant the voltage level

reaches the lowest limit of the operating VDD

(i.e. not including the rising time), the reset

time when CRES=0.1 µF is used should be

between 10 ms to 100 ms.

No.6727-16/21

Page 17

LC651306A/04A/02A/01A

SCK

tCKL tCKH

tCKCY

0.8VDD

0.2VDD

SI

SO

tCKO

tICK tCKI

Input Data

Output Data

Load circuit

1KΩ

50pF

VDD

Figure 6 Serial I/O Timing

tPCY

tPH

0.7VDD

The load conditions are the

same as those in Figure 5.

0.25VDD

tPL

Figure 7 Port PE0 Pulse Output Timing

Rw

RI

PE1/WDR

Cw

tWCCY tWCT

tWCCY : Charge time made by the external Cw, Rw, and Rl time constants

tWCT : Discharge time made by program control

Figure 8 Watchdog Timer Waveform

No.6727-17/21

Page 18

LC651306A/04A/02A/01A

RC Oscillator Characteristic of LC651306A/1304A/1302A/1301A

Data will be added once evaluation has been completed.

No.6727-18/21

Page 19

LC651306A/04A/02A/01A

Notes on Circuit Board Design

This section provides advice and countermeasures to prevent microcontroller noise problem when designing circuit boards

using these microcontrollers intended for a mass production. These design techniques are effective to prevent and avoid the

defects (e.g. malfunctions of the microcontroller or a runaway program) caused by noise.

1. VDD, VSS : Power Supply Pins

Add capacitors between the VDD and VSS pins so that they meet the following conditions.

The VDD line and the VSS line to the two capacitors (C1 and C2) should be as similar in length as possible (L1=L1’,

•

L2=L2’), and should be as short as possible.

Add the larger capacitor to ‘C1’ position and smaller capacitor to ‘C2’ position.

•

The VDD and VSS lines on the circuit board should be thicker than any other lines.

C1 C2

2. OSC1, OSC2: Clock I/O Pins

• When the ceramic resonator option is selected: (Figure 2- 1)

• The length of the lines (Losc in Fig.2-1) between the clock I/O

pins (input: OSC1, output: OSC2) and the external components

should be as short as possible.

• The length of the lines (Lvss+L1 or L2 ) between each capacitor

and the VSS pin should be as short as possible.

• The VSS line for the oscillation circuit and the VSS line for

other functions should be branched as close as possible to the

microcontroller's VSS pin.

• Oscillatio n constants written in this specification sheet (such as

the capacitor C1, C2 and the damping resistor Rd) may have to

be changed and the frequency should be adjusted, depending

on the pattern capacity of the circuit board. For further information,

contact the oscillator manufacturer

• When two- pin RC oscillator option is selected: (Figure 2-2)

• The length of the lines (Losc) between the clock I/O pins (input:

OSC1, output: OSC2) and the external components (capacitor

Cext, resistor Rext) should be as short a s p ossi ble.

• The length of the line (Lvss+Lc) between the capacitor and the

VSS pin should be as short as possible.

• The VSS line for the oscillation circuit and the VSS line for

other functions should be branched as close as possible to the

microcontroller's VSS pin.

• When the external oscillation option is selected: (Figure 2-3)

• The length of the line (Losc) between the clock input pin (OSC1)

and the external oscillator should be as short as possible.

• The clock output pin (OSC2) should be opened.

• The length of the line between the VSS and the external

oscillator, and the length of the line between the VDD and

the external oscillator should be as short as possible.

L2

L1

VSS

+

VDD

L1'

L2

'

Lvss

Rd

VSS

OSC1

OSC2

L2

L1

C1

C2

Losc

Figure 2-1. Sample Oscillation Circuit 1

(Ceramic resonator)

Lvss

Lc

Cext

VSS

OSC1

Rext

OSC2

Losc

Figure 2-2. Sample Oscillation Circuit 2

(Two-pin RC Oscillator)

Losc

VSS

External

Oscillator

OPEN

OSC1

OSC2

VDD

Figure 2-3. Sample Oscillation Circuit 3

(External Oscillator)

No.6727-19/21

Page 20

LC651306A/04A/02A/01A

A

A

Other note on all oscillator circuit:

•

Place the lines for signals that can easily change suddenly, high amplitude signals connected to the higher capacity voltage

•

(+15 V) ports, and powerful current supplies as far as possible from the oscillation circuit, and do not cross these lines

with lines that have relevance to the clock.

3.

: Reset Pin

RES

• The length o f li ne (Lres) be twe en the

RES

• The length of lines (L1 and L2) between the

pin and the external circuit should be as short as possible.

pin and the capacitor (Cres), and the VSS and the capacitor should

RES

be as short as possible.

External

Circuit

Cres

Figure 3.

Lres

RES

VSS

L2

RES

L1

Pin Patterns

4. TEST: Test Pin

• The length of line (L) between the VSS and the TEST pin should be as short as possible.

• The TEST pin and the VSS pin should be connected as close as possible to the VSS pin.

L

VSS

TEST

Figure 4. Test Pin Patterns

5. AD0 to AD7: Analog Input Pins

The connection for the analog input pins, such as A/D converter input pins and comparator input pin, should meet the

following conditions.

The length of the line (L1) between the damping resistor (R1) and each analog pin should be as short as possible.

•

The capacitor added between each analog pin and AV- pin (base voltage input pin for A/D converter) should be located

•

as close as possible to the AV- input pin.

External circuit

(sensor block)

Rl

D4-7

C

L2

Input Pins

Analog

D3-0

AVVSS

Figure 5. Analog Input Pins Pa tterns

6. I/O Pins

All I/O pins on these microcontrollers have both input and output function.

• When used as an input pin, add a damping resistor and keep the length of the line to that pin as short as possible.

[Supplement]

In addition to the above techniques in designing a circuit board, the following options and programming methods are also

effective in preventing def ect s (such as malfunction or a runaw ay program) in the microcontroller.

• If signals are input from external sources when the microcontroller power supply is unstable, select the higher capacity

voltage (N-channel open drain) output type for the input pin, and add a damping resistor close to the pin.

No.6727-20/21

Page 21

LC651306A/04A/02A/01A

When the external signals are input to pins, key chattering must be removed.

•

The data should be output periodically from the pins using the output instruction, OP or SPB.

•

• To read the data input to the I/O common pins, the output value should be set to ‘1’ using the output instruction, OP or

SPB.

7. Unused Pins

See each microcontroller’s users manual or the final edition of the specification sheet.

•

No.6727-21/21

PS

Loading...

Loading...