Page 1

L4956

5A LOW DROP LINEAR REGULATOR

SPLITTED SUPPLY VOLTAGE FOR IMPROVED EFFICIENCY:

-V

PW: 3V MIN. POWER SUPPLYVOLTAGE

SIG: 4.5VMIN.SIGNALSUPPLYVOLTAGE

-V

5A OUTPUTCURRENT

FASTLOAD TRANSIENT RESPONSE

0.75VTYP.DROPOUT VOLTAGE AT5A

INHIBITWITH ZEROCURRENT COMSUMPTION

POWERGOOD

SHORTCIRCUIT PROTECTION

THERMALSHUTDOWN

HEPTAWATTPACKAGE

APPLICATIONS

PENTIUM AND POWERPC SUPPLIES

LOW COST SOLUTION FOR 3.3V TO 1.5V

CONVERSION

SUITABLE FOR APPLICATIONS WITH

STAND BY FEATURE

DESCRIPTION

The L4956 is an adjustablemonolithiclinearregulator designedto satisfy very heavy load transient

and efficient power conversionfrom 3.3V to1.26V

and lower, up to 5A.

MULTIPOWER BCD TECHNOLOGY

HEPTAWATT

ORDERING NUMBER: L4956

Designed in BCDII technology, it uses a charge

pump techniqueto have a properinternal N-channel gate drive. The signal supply voltage input

can operate from 4.5V up to an absoluteof

V

SIG

7V and the power supply voltage input V

PW

can

opearte from 3V min to an absolute of 7V. An

RDSON of 150mV gives a voltagedrop of 750mV

at 5A of loadcurrent.

Very fast load transients and ±1% of reference

voltage precision makes this device suitable for

supplying last micrprocessors generation and low

voltagelogics.

The Heptawatt package enriches the device with

auxiliaryfunctions like power good and inhibit.

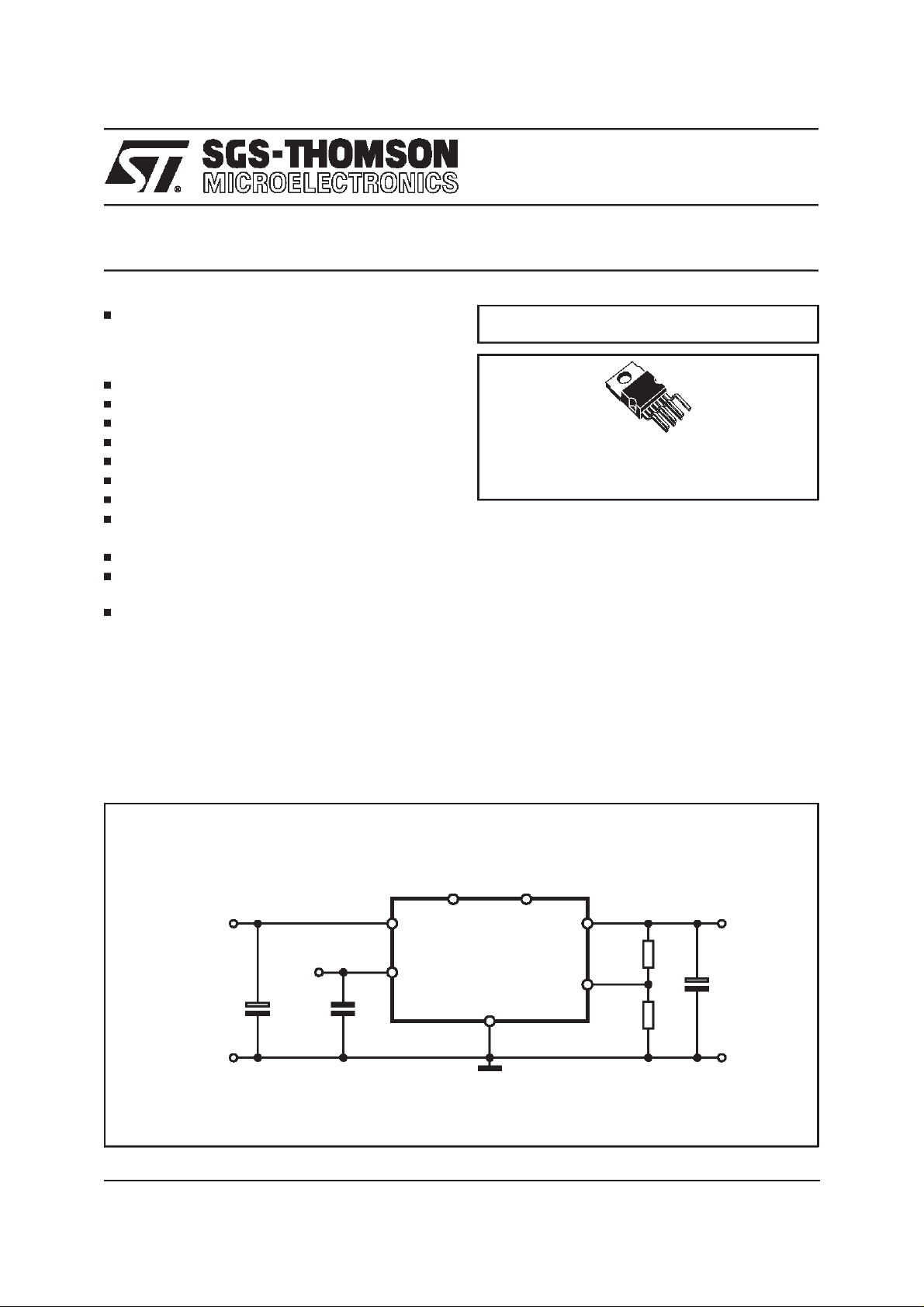

TYPICALAPPLICATION

VPW=3.3Vbus

C

1

March 1998

V

SIG

5Vbus

INH PG

V

PW

=

V

SIG

C

3

36

1

2

L4956

4

GND

OUT

7

ADJ

5

D96IN374B

V

O

R

1

C

2

R

2

1/8

Page 2

L4956

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

PW,VSIG

P

TOT

T

st,Ti

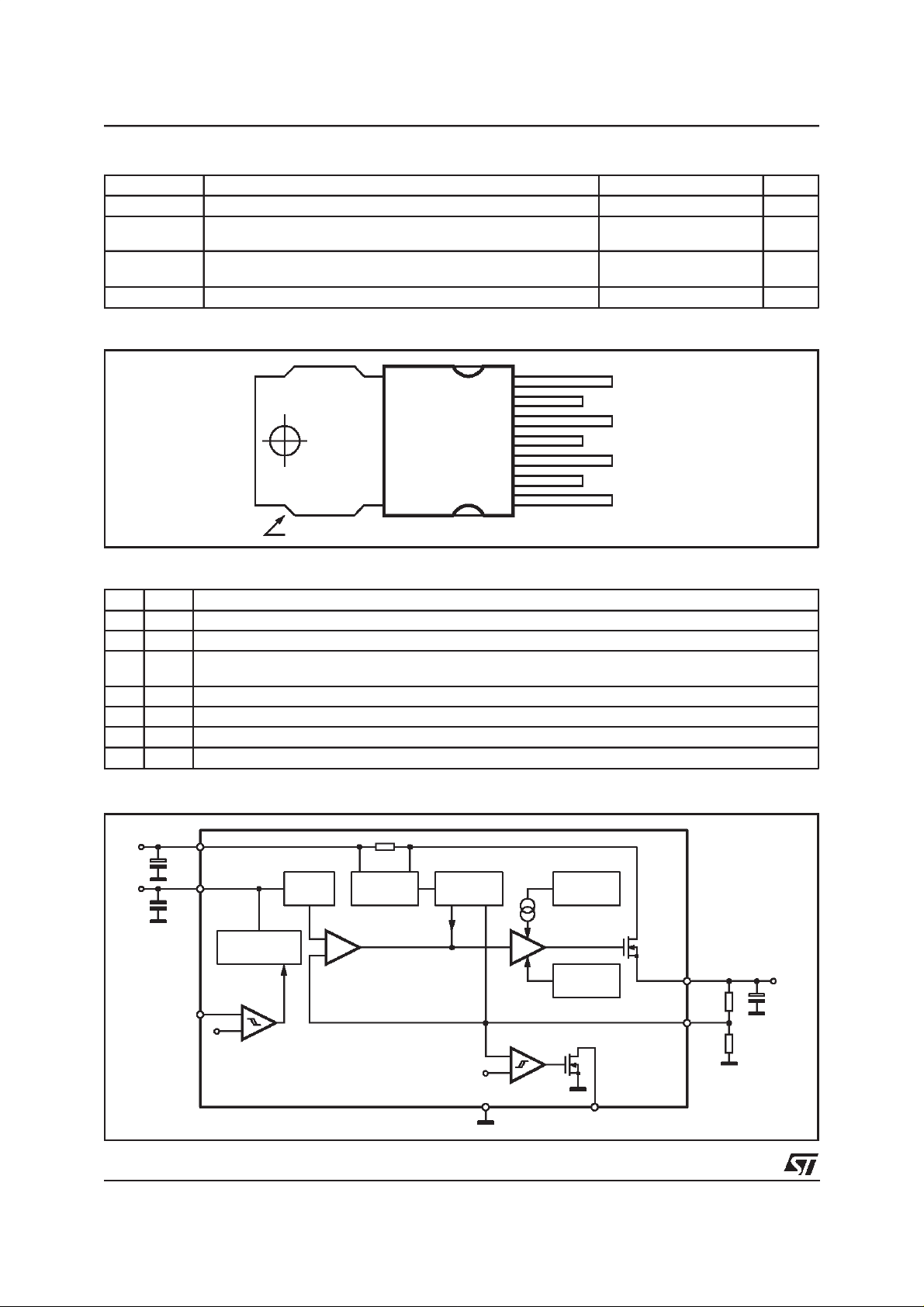

PIN CONNECTION(Top view)

Supply Input Voltage 7 V

ADJ pin

PG and INH pins

Power Dissipation @ T

Power Dissipation @ T

amb

case

=50°C

=90°C

-0.3 to 4

0toV

SIG

2

15

Storage Temperature -40 to +150 °C

7 OUT

6

5

4

3

2

1

PG

ADJ

GND

INH

V

SIG

V

PW

V

V

W

W

tab connected to pin 4

D96IN373

PIN FUNCTIONS

No. Name Function

1V

2V

Unregulated power input voltage; this pin must be bypassed witha capacitor larger than10µF.

PW

Unregulated signal input voltage this pin has to be by passed with a minimum capacitor of0.1µF.

SIG

3 INH TTL-CMOS input. A logic level on this input disable the device. An internal pull-down insures insures

full functionally even if the pin is open.

4 GND Ground.

5 ADJ The output is connected directly to this terminal for 1.26V operation via divider for higher voltages.

6 PG Opendrainoutput, this pin is low when theoutputvoltageis lowerthan 90%,otherwise ishigh.

7 OUT Regulated output voltage.A minimum bypass capacitor of 22µF is required to insure stability.

BLOCK DIAGRAM

V

V

SIG

INH

PW

1

2

REGULATOR

3

1.26V

INHIBIT

ACTIVE HIGH

PRE

V

REF

1.26V

=

+

E/A

-

CURRENT

LIMITATION

FOLDBACK

0.9V

REF

+

-

4

GND PG

CHARGE

BUFFER

THERMAL

SHUTDOWN

PUMP

6

POWER

DMOS

150mΩ

D96IN372A

OUT

7

R1 22µF

ADJ

5

R2

V

V

PW

10µF

SIG

V

OUT

2/8

Page 3

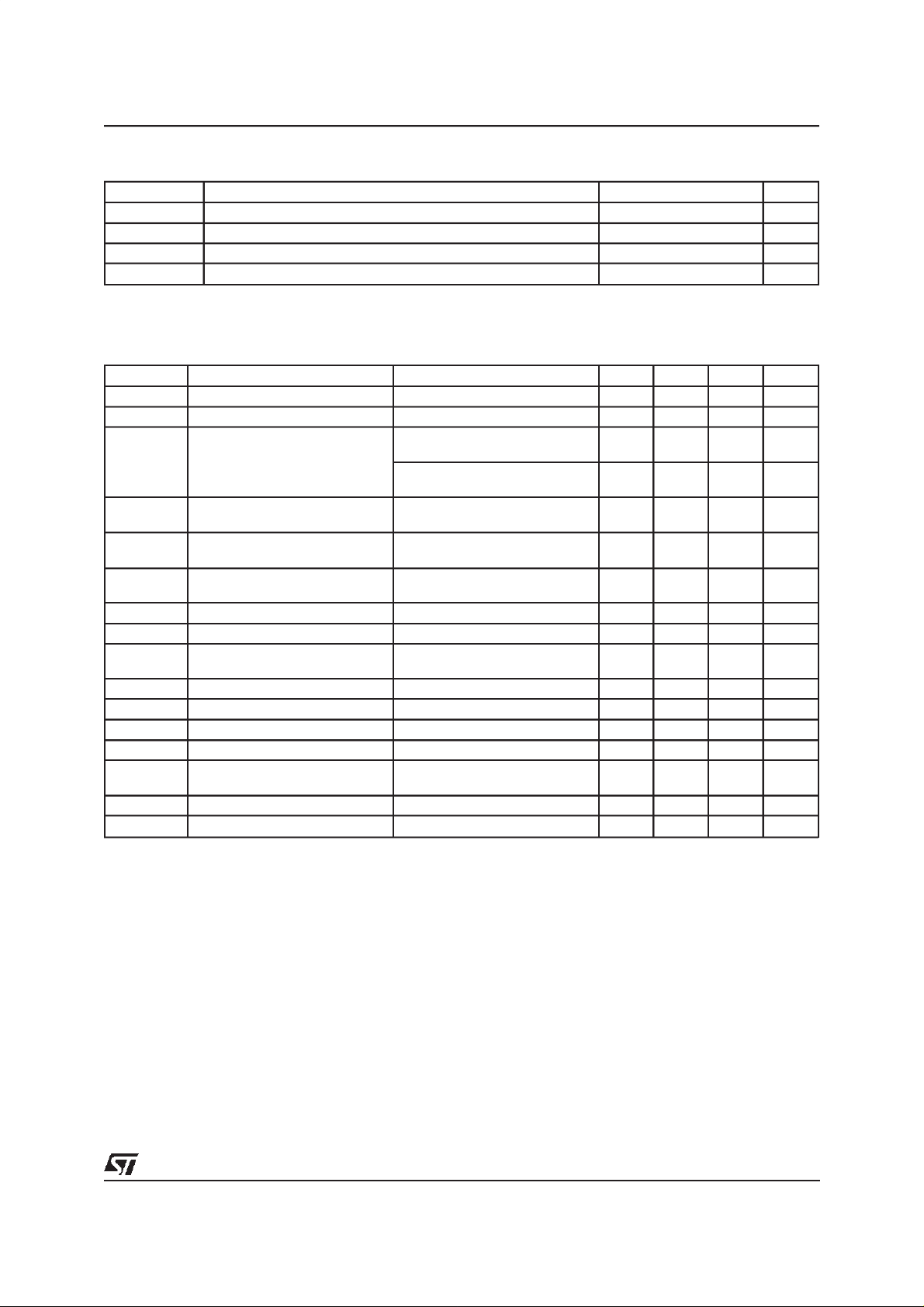

THERMAL DATA

Symbol Parameter Value Unit

R

th j-pins

R

th j-amb

Thermal ResistanceJunction-case 2.5 °C/W

Thermal ResistanceJunction-ambient 50 °C/W

Thermal Shutdown Typ. 150 °C

Thermal Hysteresis Typ. 20 °C

ELECTRICALCHARACTERISTICS (Tj=25°C,unless otherwisespecified)

Symbol Parameter Test Condition Min. Typ. Max. Unit

V

PW

V

SIG

V

OUT

∆V

OUT

∆V

OUT

I

O

I

Q

(1) Output voltage connected to ADJ.

PowerOperatingSupplyVoltage 3 6.5 V

Signal Operating Supply Voltage 4.5 6.5 V

Output Voltage (1) 0 < Tj < 125°C; VPW= 3.3V

4.5V< V

3V< V

0.1A < I

< 6.5V; 0.1A< IO<5A

SIG

<5.5V;4.5V< V

PW

< 5A; 0 < Tj< 125°C

O

SIG

<6.5V

Line regulation (1) 3V < VPW< 5.5V; IO= 10mA

4.5V< V

Load regulation (1) VPW = 3.3V; V

0.1A < I

Drop-out Voltage I

=5A

O

I

= 5A, Tj= 125°C

O

SIG

O

<6.5V

<5A

SIG

=5V

1.240 1.260 1.280 V

1.224 1.260 1.296 V

0.5 3 mV

15mV

0.75

1.1

1.1

1.5

Current Limiting 0 < Tj< 125°C 5.1 6.3 7.5 A

Short Circuit Current V

Quiescent Current at pin V

Stand By Current at pin V

SIG

SIG

= 0V, 0 < Tj< 125°C 1.8 A

O

0.1A < IO<5A

4.5V < V

SIG

<6.5V

INH = HIGH V

= 5V 100 150 µA

SIG

1.5 3 mA

Inhibit Threshold 0 < Tj < 125°C 1.1 1.26 1.42 V

Inhibit Histeresys 0.2 V

Inhibit Bias Sink Current 5 10 µA

Power Good Threshold 0.9x

V

OUT

Power Good Saturation I

= 4mA 0.1 0.4 V

6

Power Good Histeresys 0.2 V

L4956

V

V

V

3/8

Page 4

L4956

Figure 1. DC Operating Area.

O utput C urrent [A]

8

Vpw > 3V

V sig > 4.5 V

7

Tj = 125°C

6

5

4

3

2

Rdson

limit

Cu r r e nt Lim ita tion

Tc = 70°C

Pdm ax=22 W

DC Operating Area

Power

Di ssi p ation

Limit

Tc = 25°C

Pdm ax = 40 W

1

0

012345678

(Vpw - Vout) [V]

Figure 3. Load Regulation.

5

4

3

2

1

0

-1

-2

-3

Output Voltage Deviation [m

-4

-5

012345

Pulsed tecnique has been used

Vpw = 3.3V

Vsig = 5V

Vout = Vadj

Tj = 25 °C

Iout [A]

Figure2. OutputVoltageStability vs.

Junction Temperature

Vout [V]

1.28

1.275

1.27

Vpw = 3.3V

Vsig = 5V

Iout = 10m A

1.265

1.26

1.255

1.25

1.245

1.24

-40 0 40 80 120 160

Tj [°C]

Figure4. DropoutVoltage.

1.25

1

Tj = 125 °C

0.75

Tj = 25 °C

0.5

Minimum Vpw - Vout Voltage [V]

0.25

Pulsed technique has been used

0

0123456

Iout [A]

Tj = -40 °C

Figure 5. MaximumOutput Current vs.

JunctionTemperature

Output Current [A]

10

4/8

9

8

7

6

5

4

3

2

1

0

-40

-20

Pulsed tecnique ha s been u sed

0

20

40

60

Tj [ºC]

(Vpw -Vout) > 2V

80

100

120

140

160

Figure6. QuiescentCurrent at pin VSIG vs.

Junction Temperature.

Iq [m A ]

2

SIG

V

1.8

1.6

1.4

1.2

0.8

0.6

0.4

1

-40

-20

0

20

40

=6.5V

Iout = 10 m A to 5A

3V<VPW<6.5V

80

60

Tj [°C]

100

120

14 0

160

Page 5

L4956

Figure 7. QuiescentCurrent at pin VSIG vs.

Signal InputVoltage.

Iq [m A]

3

2.5

Io = 1 0 m A to 5A

Tj = 25°C

3V < VPW < 6.5V

2

1.5

1

0.5

0

01234567

VSIG [V]

Figure 9. Power Good Function

V

ADJ

0.9 V

ADJ

Figure8. Stand-ByCurrentatpinVSIGvs.Signal

InputVoltagewith INH= LOGICHIGH

Iq [µA]

150

125

100

75

Tj = 25°C

50

25

0

4 4 .5 5 5 .5 6 6 .5 7

V

OUT=VADJ

(R1+R2)/R2

hyst =200mV

3V < VPW < 6.5V

V S IG [V ]

Figure 10. Inhibit Function

Vref = 1.26V

PG

V

INH

Low

regulator

ON

High

regulator

OFF

Low

D96IN364B

hyst = 200mV

regulator

ON

t

t

t

D96IN365A

t

5/8

Page 6

L4956

LOAD TRANSIENTRESPONSE

Figure 11.

Vout

50mV/div

CH1gnd

5A

0.5A

CH2gnd

Iout

2A/div

Figure 13.

Vout

50mV/div

CH1gnd

t=5µs/div

Figure 12.

Vout

50mV/div

CH1gnd

5A

0.5A

CH2gnd

Iout

2A/div

Test conditions:

PW

V

= 3.3V;V

SIG

from 0.5A to 5A;

dl

out

=20A/µs;Tj = 25°C

dt

=5;V

t=5µs/div

out

= 1.5V;Load Transient

5A

0.5A

CH2gnd

Iout

2A/div

t = 100µs/div

Figure 14. Load transient test circuit.

V

PW

1

V

=5V

C1,C2

470µF

Panasonic

HFQ

V

SIG

C16

220nF

SIG

2

GND

PG

6

L4956

43

INH

OUT

7

VOUT=1.5VVIN=3.3V

R4

ADJ

5

24Ω

R5

126Ω

C4 to

C9

100µF/10V

AVX TPS

6 each

D97IN593

C10 to

1µF

AVX

6 each

C15

X7R

6/8

Page 7

HEPTAWATT PACKAGEMECHANICAL DATA

L4956

DIM.

A 4.8 0.189

C 1.37 0.054

D 2.4 2.8 0.094 0.110

D1 1.2 1.35 0.047 0.053

E 0.35 0.55 0.014 0.022

F 0.6 0.8 0.024 0.031

F1 0.9 0.035

G 2.41 2.54 2.67 0.095 0.100 0.105

G1 4.91 5.08 5.21 0.193 0.200 0.205

G2 7.49 7.62 7.8 0.295 0.300 0.307

H2 10.4 0.409

H3 10.05 10.4 0.396 0.409

L 16.97 0.668

L1 14.92 0.587

L2 21.54 0.848

L3 22.62 0.891

L5 2.6 3 0.102 0.118

L6 15.1 15.8 0.594 0.622

L7 6 6.6 0.236 0.260

M 2.8 0.110

M1 5.08 0.200

Dia 3.65 3.85 0.144 0.152

MIN. TYP. MAX. MIN. TYP. MAX.

mm inch

7/8

Page 8

L4956

Information furnished is believedto be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the

consequences of use of such information nor for any infringement of patents or other rights of third partieswhich may result from its use. No

license is granted by implication or otherwise under any patent or patent rightsof SGS-THOMSON Microelectronics. Specificationmentioned

in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGSTHOMSON Microelectronics products are not authorizedfor use as critical components in life support devices or systems without express

written approval of SGS-THOMSON Microelectronics.

1998 SGS-THOMSON Microelectronics– Printed inItaly – All RightsReserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - Canada- China - France- Germany - Italy - Japan - Korea- Malaysia - Malta - Morocco - The Netherlands -

Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

8/8

Loading...

Loading...