Page 1

2002. 3. 7 1/4

SEMICONDUCTOR

TECHNICAL DATA

KIC7WZ74FK

SILICON MONOLITHIC CMOS

DIGITAL INTEGRATED CIRCUIT

Revision No : 1

D-TYPE FLIP FLOP WITH PRESET AND CLEAR

FEATURES

High output drive : 24mA(min.) @VCC=3V.

Super high speed operation : tpd 2.8ns(typ.) @VCC=3V, 50pF.

Operation voltage range : V

CC(opr)

=1.65~5.5V.

Latch-up performance : 500mA or more

ESD performance : 200V or more (EIAJ)

2000V or more (MIL)

Power down protection is provided on all inputs and outputs.

MAXIMUM RATINGS (Ta=25 )

CHARACTERISTIC SYMBOL RATING UNIT

Power Supply Voltage

V

CC

-0.5~6 V

DC Input Voltage

V

IN

-0.5~6 V

DC Output Voltage

V

OUT

-0.5~6 V

Input Diode Current

I

IK

-20 mA

Output Diode Current

I

OK

-20 mA

DC Output Current

I

OUT

50

mA

DC VCC/ground Current I

CC

50

mA

Power Dissipation

P

D

200 mW

Storage Temperature Range

T

stg

-65 150

Lead Temperature (10s)

T

L

260

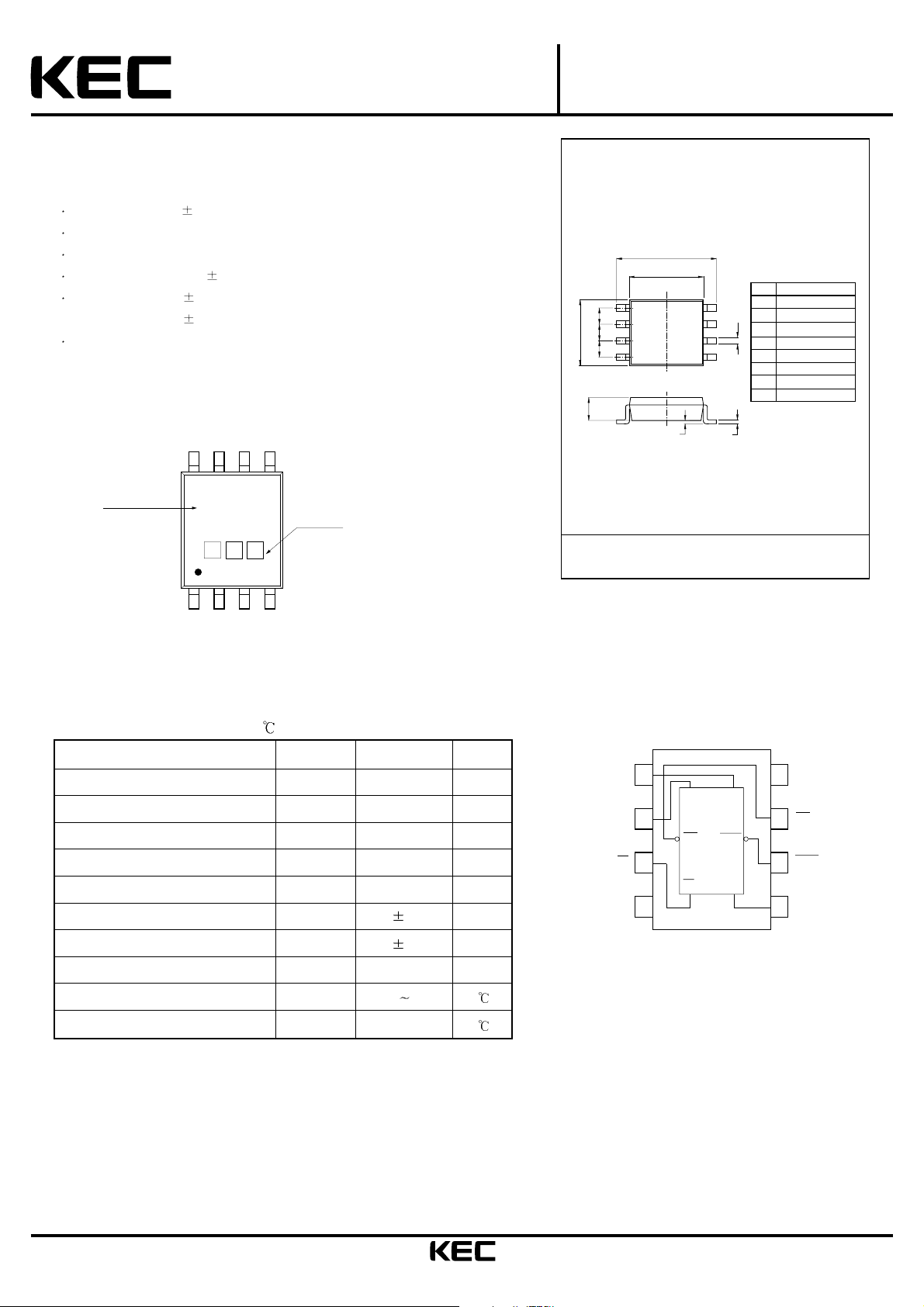

MARKING

B

C

DIM MILLIMETERS

1

D

D

A

D

45

F

H

A

8

B

E

C

D

E

0.2+0.05/-0.04

F

G

H

G

_

+

2.0 0.1

_

+

3.1 0.1

_

+

2.3 0.1

0.5

_

0.7 0.1

+

_

0.12 0.04

+

0 ~ 0.1

Type Name

Z74

Lot No.

US8

PIN CONNECTION(TOP VIEW)

1

CK

GND

D

CK

2

D

PR

CLR

3

Q

QQ

4

8

V

CC

7

PR

6

CLR

5

Q

Page 2

2002. 3. 7 2/4

KIC7WZ74FK

Revision No : 1

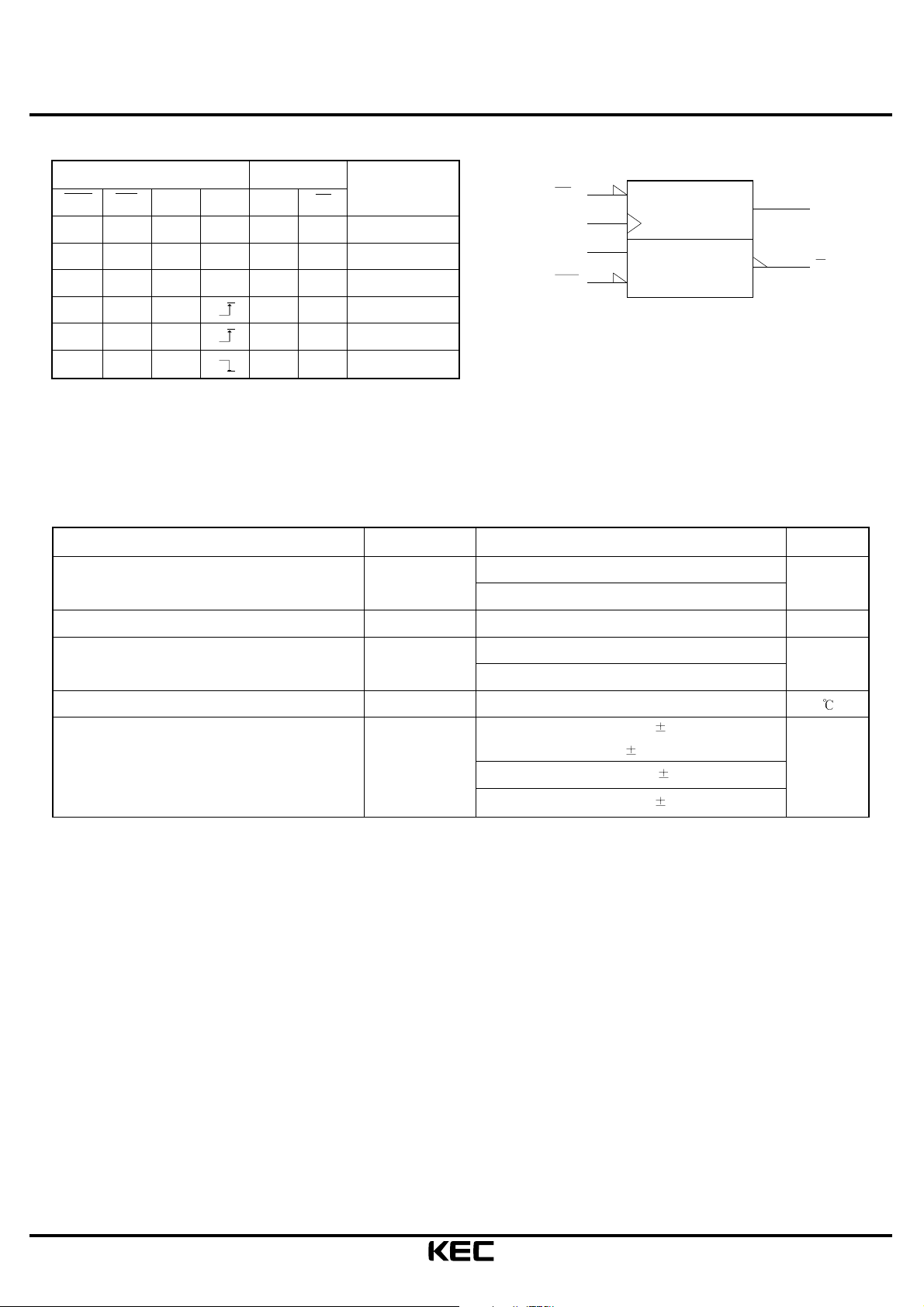

Truth Table Logic Diagram

Recommended Operating Conditions

CHARACTERISTIC SYMBOL RATING UNIT

Supply Voltage

V

CC

1.65~5.5

V

1.5~5.5 (Note1)

Input Voltage

V

IN

0~5.5 V

Output Voltage

V

OUT

0~5.5 (Note2)

V

0~V

CC

(Note3)

Operating Temperature

T

opr

-40~85

Input Rise and Fall Time

dt/d

v

0~20 (VCC=1.8V 0.15V,

2.5V

0.2V)

ns/V

0~10 (VCC=3.3V 0.3V)

0~5 (VCC=5.5V 0.5V)

Note1 : Data retention only.

Note2 : V

CC

=0V.

Note3 : High or low

Inputs Outputs

Function

CLR PR D CK Q Q

L H X X L H Clear

H L X X H L Preset

L L X X H H -

H H L L H -

H H H H L -

H H X Qn Qn No Change

PR

CK

D

CLR

S

Q

C

D

Q

R

Page 3

2002. 3. 7 3/4

KIC7WZ74FK

Revision No : 1

ELECTRICAL CHARACTERISTICS

DC Characteristics

CHARACTERISTIC SYMBOL

TEST CONDITION

Ta=25 Ta=-40~85

UNIT

VCC(V)

MIN. TYP. MAX. MIN. MAX.

Input

Voltage

High Level

V

IH

-

1.65~1.8

0.75

V

CC

- -

0.75

V

CC

-

V

2.3~5.5

0.7 V

CC

- -

0.7 V

CC

-

Low Level

V

IL

-

1.65~1.95 - -

0.25

V

CC

-

0.25

V

CC

2.3~5.5

- -

0.3 V

CC

-

0.3 V

CC

Output

Voltage

High Level

V

OH

VIN=

V

IH

or V

IL

IOH=-100 A

1.65 1.55 1.65 - 1.55 -

V

2.3 2.2 2.3 - 2.2 -

3.0 2.9 3.0 - 2.9 -

4.5 4.4 4.5 - 4.4 -

IOH=-4mA

1.65 1.29 1.52 - 1.29 -

IOH=-8mA

2.3 1.9 2.15 - 1.9 -

IOH=-16mA

3.0 2.4 2.8 - 2.4 -

IOH=-24mA

3.0 2.3 2.68 - 2.3 -

IOH=-32mA

4.5 3.8 4.2 - 3.8 -

Low Level

V

OL

VIN=V

IL

IOH=100 A

1.8 - 0 0.1 - 0.1

V

2.3 - 0 0.1 - 0.1

3.0 - 0 0.1 - 0.1

4.5 - 0 0.1 - 0.1

IOH=4mA

1.65 - 0.08 0.24 - 0.24

IOH=8mA

2.3 - 0.1 0.3 - 0.3

IOH=16mA

3.0 - 0.15 0.4 - 0.4

IOH=24mA

3.0 - 0.22 0.55 - 0.55

IOH=32mA

4.5 - 0.22 0.55 - 0.55

Input Leakage Current

I

IN

VIN=5.5V or GND

0~5.5 - -

1

-

10 A

Power Off Leakage Current

I

OFF

VINor V

OUT

=5.5V

0.0 - - 1 - 10

A

Quiescent Supply Current

I

CC

VIN=5.5V or GND

1.65~5.5 - - 1 - 10

A

Page 4

2002. 3. 7 4/4

KIC7WZ74FK

Revision No : 1

AC Characteristics (unless otherwise specified, Input : tr=tf=3ns)

Note 4 : CPDis defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption

without load. Average operating current can be obtained by the equation : I

CC(opr)=CPDVCCfIN+ICC

CHARACTERISTIC SYMBOL

TEST CONDITION

Ta=25 Ta=-40~85

UNIT

VCC(V)

MIN. TYP. MAX. MIN. MAX.

Maximum Clock

Frequency

f

MAX

CL=50pF, RL=500

1.8 0.15

51 - - 38 -

MHz

2.5 0.2

130 - - 100 -

3.3 0.3

200 - - 150 -

5.0 0.5

200 - - 180 -

Propagation Delay Time

(CK-Q, Q)

t

PLH

t

PHL

CL=15pF, RL=1M

1.8 0.15

2.5 10.0 18.0 2.1 23.0

ns

2.5 0.2

2.0 4.9 7.5 1.7 9.0

3.3 0.3

1.5 3.3 4.8 1.3 5.6

5.0 0.5

1.0 2.4 3.5 1.0 3.9

CL=50pF, RL=500

3.3 0.3

2.0 4.3 5.7 1.5 7.0

5.0 0.5

1.5 2.8 4.0 1.3 4.4

Propagation Delay Time

(CLR, PR,-Q, Q)

t

PLH

t

PHL

CL=15pF, RL=1M

1.8 0.15

2.5 10.0 17.0 2.1 21.0

ns

2.5 0.2

2.0 5.0 7.3 1.7 8.8

3.3 0.3

1.5 3.4 4.8 1.3 5.6

5.0 0.5

1.5 2.2 3.5 1.0 3.9

CL=50pF, RL=500

3.3 0.3

2.0 4.3 5.7 1.5 7.0

5.0 0.5

1.0 3.1 3.9 1.0 4.3

Minimum Setup Time

t

s

CL=50pF, RL=500

2.5 0.2

3.4 - - 4.1 -

ns

3.3 0.3

2.1 - - 2.5 -

5.0 0.5

1.5 - - 1.7 -

Minimum Hold Time

t

h

CL=50pF, RL=500

2.5 0.2

2.4 - - 2.9 -

ns

3.3 0.3

1.4 - - 1.5 -

5.0 0.5

1.0 - - 1.1 -

Minimum Pulse Width

(CK)

tW (L)

t

W

(H)

CL=50pF, RL=500

2.5 0.2

3.0 - - 3.6 -

ns

3.3 0.3

3.0 - - 3.3 -

5.0 0.5

3.0 - - 3.2 -

Minimum Pulse Width

(CLR, PR)

tW (L)

CL=50pF, RL=500

2.5 0.2

3.0 - - 3.6 -

ns

3.3 0.3

3.0 - - 3.3 -

5.0 0.5

3.0 - - 3.2 -

Minimum Removal Time

t

rem

CL=50pF, RL=500

2.5 0.2

3.6 - - 4.4 -

ns

3.3 0.3

2.2 - - 2.5 -

5.0 0.5

1.3 - - 1.4 -

Input Capacitance

C

IN

- 0~0.5 - 3.0 - - - pF

Output Capacitance

C

OUT

- 0~0.5 - 5.0 - - - pF

Power Dissipation

Capacitance

C

PD

(Note 4)

3.3 - 30 - - pF

5.5 - 47 - - -

Loading...

Loading...