Page 1

2003. 3. 11 1/4

SEMICONDUCTOR

TECHNICAL DATA

KIC7SZ66FU

SILICON MONOLITHIC CMOS

DIGITAL INTEGRATED CIRCUIT

Revision No : 1

BILATERAL SWITCH

FEATURES

250MHz-3dB bandwidth.

Super High Speed tPD=2.7nS(Typ.) at VCC=5V.

On Resistance ROH=3 (Typ.) at VCC=4.5V

(V

IN

=0V, IIN=30mA.)

Wide Operating Voltage Range : V

CC(opr)

=1.65~5.5V.

T.H.D : THD=0.11%(Typ.) at VCC=5V.

MAXIMUM RATINGS (Ta=25 )

CHARACTERISTIC SYMBOL RATING UNIT

DC Supply Voltage

V

CC

-0.5~7.0 V

Control Input Voltage

V

IN

-0.5~7.0 V

Swith I/O Voltage

V

I/O

-0.5~7.0 V

Control Diode Current

I

CK

-50 mA

Output Diode Current

I

OK

50

mA

DC VCC/Ground Current I

CC

100

mA

Power Dissipation

P

D

200 mW

Storage Temperature Range

T

stg

-65 150

Lead Temperature (10s)

T

L

260

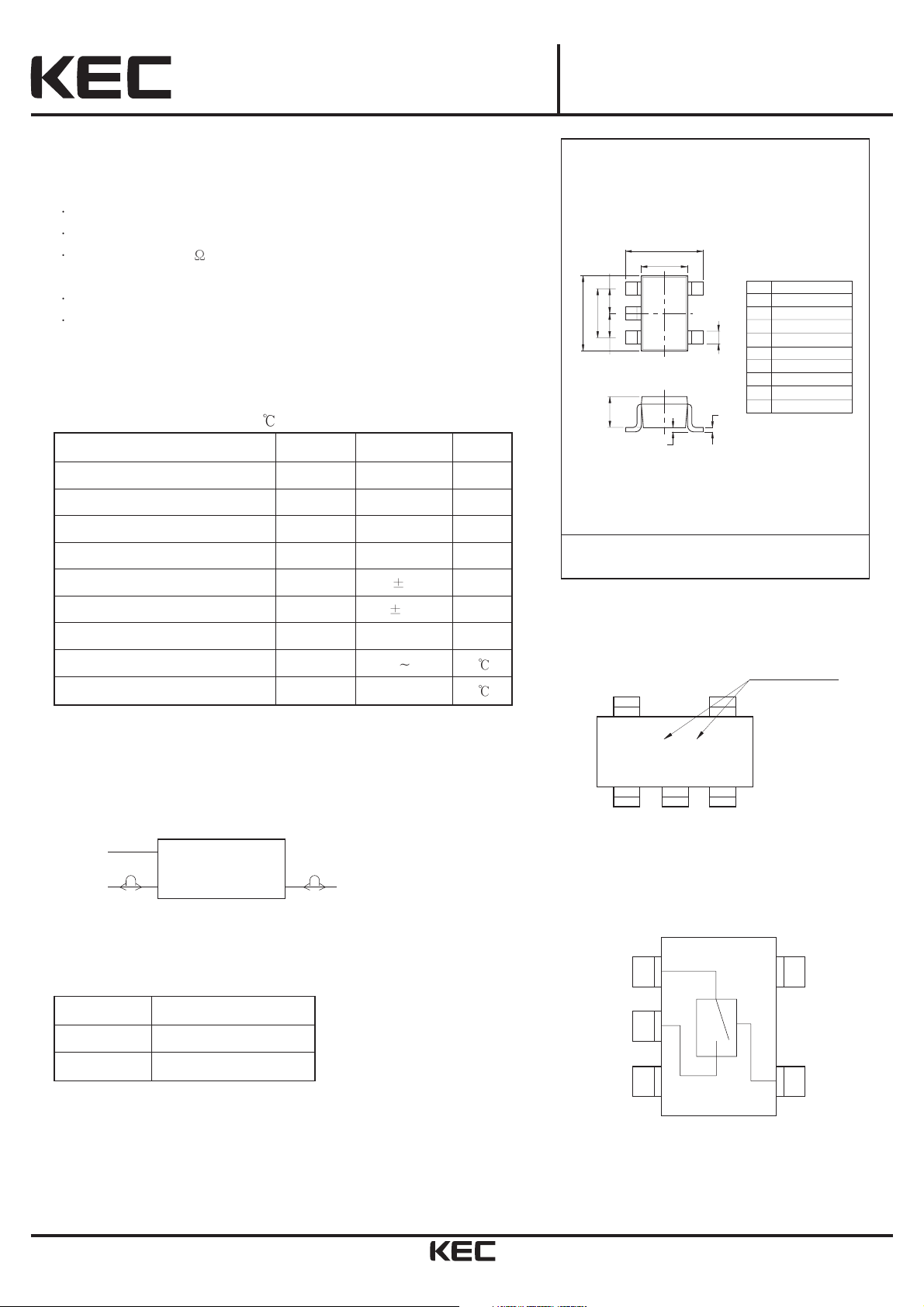

Logic Diagram

CONTROL SWITCH FUNCTION

H ON

L OFF

TRUTH TABEL

B

B1

DIM MILLIMETERS

1

C

2

A

A1

C

3

H

G

5

4

A

2.00 0.20

1.3 0.1A1

B

B1

C

D

G

H

T

2.1 0.1

1.25 0.1

0.2+0.10/-0.05

0.9 0.1

0.15+0.1/-0.05

D

T

0.65

0-0.1

_

+

_

+

_

+

_

+

_

+

C

I/O O/I

X 1

II

USV

MARKING

Type Name

T H

PIN CONNECTION(TOP VIEW)

IN/OUT

1

5

V

CC

OUT/IN

GND

2

3

4

CONT.

Page 2

2003. 3. 11 2/4

KIC7SZ66FU

Revision No : 1

ELECTRICAL CHARACTERISTICS

DC Characteristics

CHARACTERISTIC

SYMBOL

TEST CONDITION

Ta=25 Ta=-40~85

UNIT

VCC(V)

MIN. TYP. MAX. MIN.

TYP.

(Note4)

MAX.

Input

Voltage

High Level

V

IH

-

1.65~1.95 - - -

0.75

V

CC

-

-

V

2.3~5.5

- - -

0.7 V

CC

-

-

Low Level

V

IL

-

1.65~1.95 - - - - -

0.25

V

CC

2.3~5.5

- - -

- -

0.3 V

CC

Switch On Resistance

(Note 1)

R

ON

VIN=0V, IIN=30mA

4.5

- - - - 3 7

A

VIN=2.4V, IIN=15mA

- - - - 5 12

V

VIN=4.5V, IIN=30mA

- - - - 7 15

VIN=0V, IIN=24mA

3.0

- - - - 4 9

VIN=3V, IIN=24mA

- - - - 10 20

VIN=0V, IIN=8mA

2.3

- - - - 5 12

VIN=2.3V, IIN=8mA

- - - - 13 30

VIN=0V, IIN=4mA

1.8

- - - - 7 28

VIN=1.8V, IIN=4mA

- - - - 25 60

On Resistance Flatness

(Note 1)

(Note 2)

(Note 3)

R

flat

IA=-30mA, 0 VBnV

CC

5.0

- 6 - - - -

IA=-24mA, 0 VBnV

CC

3.3

- 12 - - - -

IA=-8mA, 0 VBnV

CC

2.5

- 28 - - - -

IA=-4mA, 0 VBnV

CC

1.8

- 125 - - - -

Input Leakage Current

I

IN

0 VIN=5.5V

0~5.5 - - - -

0.05 1.0 A

Power Off Leakage Current

I

OFF

0 A,B =V

CC

1.65~5.5 - - - -

0.05 10.0 A

Quiescent Supply Current

I

CC

VIN=VCCor GND

I

OUT

=0

1.65~5.5 - - - - 0.05 10

A

Note1 : Measured by the voltage drop between A and B pins at the indicated current through the switch. On Resistance is determined by the

lower of the voltages on the two (A or B) pins.

Note2 : Parameter is characterized but not tested in production.

Note3 : Flatness is defined as the difference between the maximum and minimum value of On Resistance over the specified range of conditions.

Note4 : All typical values are at the specified V

CC

, and Ta=25

CHARACTERISTIC SYMBOL RATING UNIT

Supply Voltage

V

CC

1.65 5.5

V

Control Input Voltage

V

IN

0 5.5

V

Switch I/O Voltage

V

I/O

0 V

CC

V

Operating Temperature

T

opr

-40 85

Input Rise and Fall Time

tr, t

f

0 10 (VCC=2.3~3.6V)

0

5 (VCC=4.5~5.5V)

nS/V

RECOMMENDED OPERATING CONDIITIONS

Page 3

2003. 3. 11 3/4

KIC7SZ66FU

Revision No : 1

AC Characteristics

CHARACTERISTIC SYMBOL

TEST CONDITION

Ta=-40 ~85 ,

C

L

=50pF, RU=RD=500

UNIT

VCC(V)

MIN. TYP. MAX.

Propagation Delay Bus to Bus

(Figures 1,2)

t

PHL

t

PLH

VIN=OPEN

1.65~1.95 - - 4.3

ns

2.3~2.7 - - 1.2

3.0~3.6 - - 0.8

4.5~5.5 - - 0.3

Output Enable Time

(Figures 1,2)

t

PZL

t

PZH

VIN=2 VCCfor t

PZL

VIN=0V for t

PZH

1.65~1.95 1.5 7.0 14.2

ns

2.3~2.7 1.5 3.3 7.0

3.0~3.6 1.5 2.4 5.5

4.5~5.5 1.5 2.0 4.5

Output Disable Time

(Figures 1,2)

t

PLZ

t

PHZ

VIN=2 VCCfor t

PLZ

VIN=0V for t

PHZ

1.65~1.95 1.5 9.2 18.2

ns

2.3~2.7 1.5 5.3 9.0

3.0~3.6 1.5 4.0 7.0

4.5~5.5 1.5 2.7 5.0

Charge Injection

(Figures 3)

Q

CL=0.1nF, V

GEN

=0V,

R

GEN

=0 , f=1MHz

1.65~5.5 - 0.05 - pC

Off lsolation

(Figures 4)

OIRR

RL=50 , CL=5pF,

f=10MHz

1.65~5.5 - -50 - dB

-3dB Bandwidth

(Figures 5)

BW

RL=50

1.65~5.5 - >250 - MHz

Total Harmonic Distortion THD

RL=600 , 0.5V

P-P

f=600Hz~20kHz

5 - 0.011 - %

Symbol Parameter Typ. Max. Units Conditions

C

IN

Control Pin Input Capacitance 2 pF

VCC=0V

C

I/O

Input/Output Capacitance 6 pF

VCC=5.0V

Capacitance

Page 4

2003. 3. 11 4/4

KIC7SZ66FU

Revision No : 1

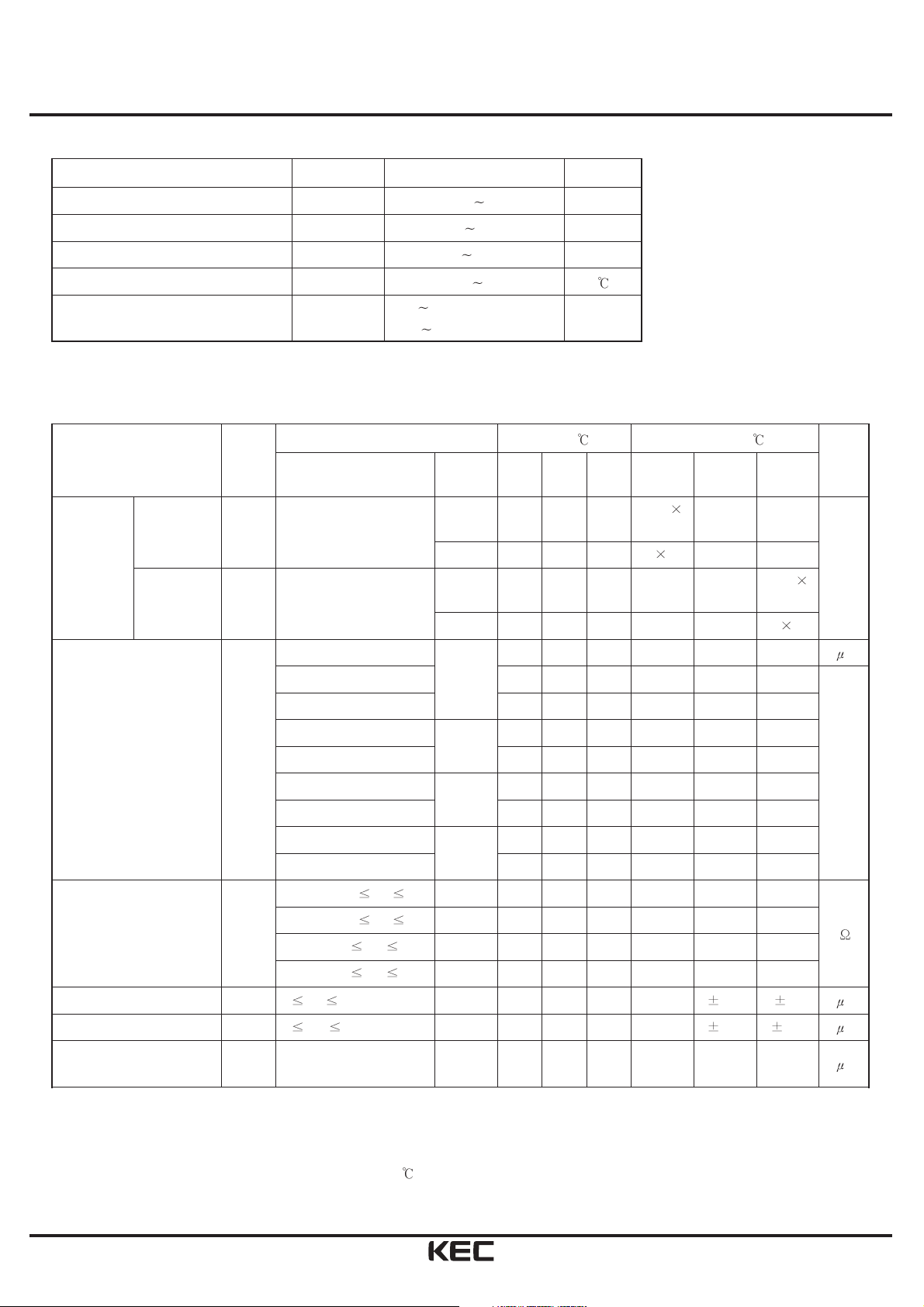

AC Loading and Waveforms

t =2.5ns t =2.5ns

r

SWITCH

INPUT

t

PLH

OUTPUT

SWITCH

INPUT

ENABLE

INPUT

Input driven by 50Ω source terminated in 50Ω

C includes load and stray capacitance.

Input PRR=1.0MHz ; t =500ns

f

90%

50%

t

10%

PHL

t

w

50% 50%

AB

DE

L

FIGURE 1. AC Test Circuit

V

CC

GND

V

OH

V

OL

FIGURE 2. AC Waveforms

VI

RU

SWITCH

OUTPUT

CRD

L

w

t =2.5ns t =2.5ns

ENABLE

INPUT

OUTPUT

OUTPUT

r

t

PZL

50%

t

PZH

50%

90%

50%

10%

f

V

CC

t

PLZ

t

PHZ

GND

V

TRI

V +0.3V

OL

V

OL

V

OH

V - 0.3V

OH

V

TRI

V

GEN

Analyzer

R

Logic

Input

GEN

B

SE1

A

N

R

L

1MΩ

V

OUT

C

L

0.1nF

LOGIC

INPUT

V

OUT

OFF ON OFF

Q=( V )(C )

FIGURE 3. Charge Injection Test

10nF

10nF

SIGNAL

GENERATOR

0dBm

B

SE

50Ω

V

CC

A

LOGIC INPUT

=V

SE

B

GND

CC

LOGIC INPUT

50Ω

=V

CC

FIGURE 4. Off lsolation FIGURE 5. Bandwidth

OUT

V

GND

CC

V

OUT

L

A

50Ω

Loading...

Loading...