Datasheet K4S281632B-NL1L, K4S281632B-NL1H, K4S281632B-NC1L, K4S281632B-NC1H Datasheet (Samsung)

Page 1

K4S281632B-N

CMOS SDRAM

shrink-TSOP

The K4S281632B-N is 134,217,728 bits synchronous high

data rate Dynamic RAM organized as 4 x 2,097,152 words by

16 bits, fabricated with SAMSUNG′s high performance CMOS

technology. Synchronous design allows precise cycle control

with the use of system clock I/O transactions are possible on

every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same

device to be useful for a variety of high bandwidth, high performance memory system applications.

• JEDEC standard 3.3V power supply

• LVTTL compatible with multiplexed address

• Four banks operation

• MRS cycle with address key programs

- CAS latency (2 & 3)

- Burst length (1, 2, 4, 8 & Full page)

- Burst type (Sequential & Interleave)

• All inputs are sampled at the positive going edge of the system

clock.

• Burst read single-bit write operation

• DQM for masking

• Auto & self refresh

• 64ms refresh period (4K cycle)

GENERAL DESCRIPTIONFEATURES

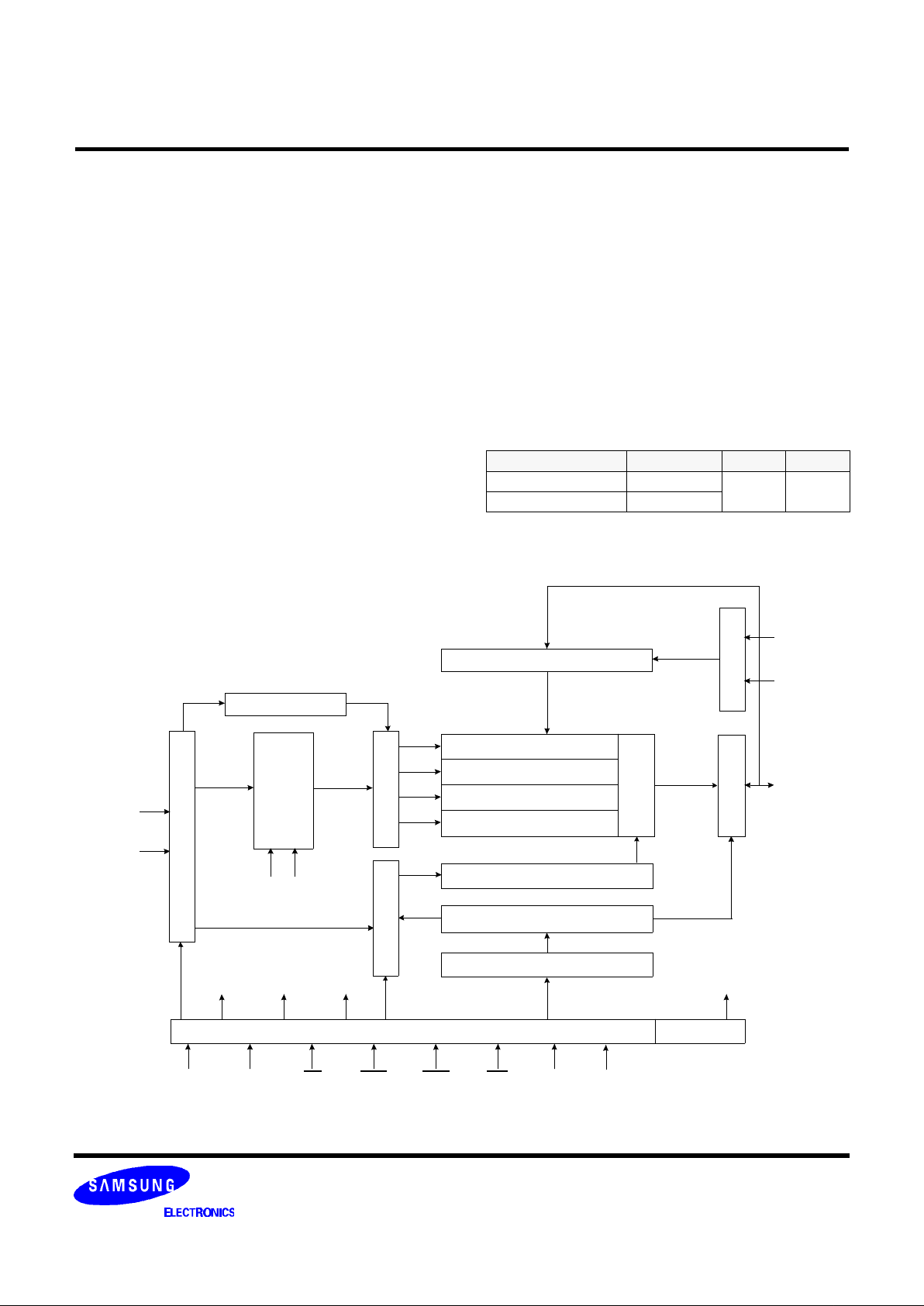

FUNCTIONAL BLOCK DIAGRAM

2M x 16Bit x 4 Banks Synchronous DRAM in sTSOP

Bank Select

Data Input Register

2M x 16

2M x 16

Sense AMP

Output BufferI/O Control

Column Decoder

Latency & Burst Length

Programming Register

Address Register

Row Buffer

Refresh Counter

Row Decoder Col. Buffer

LRAS

LCBR

LCKE

LRAS LCBR LWE LDQM

CLK CKE CS RAS CAS WE LDQM

LWE

LDQM

DQi

CLK

ADD

LCAS LWCBR

2M x 16

2M x 16

Timing Register

UDQM

* Samsung Electronics reserves the right to change products or specification without notice.

ORDERING INFORMATION

Part No. Max Freq. Interface Package

K4S281632B-NC/L1H 100MHz(CL=2)

LVTTL

54pin

sTSOP(II)

K4S281632B-NC/L1L 100MHz(CL=3)

Page 2

K4S281632B-N

CMOS SDRAM

shrink-TSOP

VDD

DQ0

VDDQ

DQ1

DQ2

VSSQ

DQ3

DQ4

VDDQ

DQ5

DQ6

VSSQ

DQ7

VDD

LDQM

WE

CAS

RAS

CS

BA0

BA1

A10/AP

A0

A1

A2

A3

VDD

VSS

DQ15

VSSQ

DQ14

DQ13

VDDQ

DQ12

DQ11

VSSQ

DQ10

DQ9

VDDQ

DQ8

VSS

N.C/RFU

UDQM

CLK

CKE

N.C

A11

A9

A8

A7

A6

A5

A4

VSS

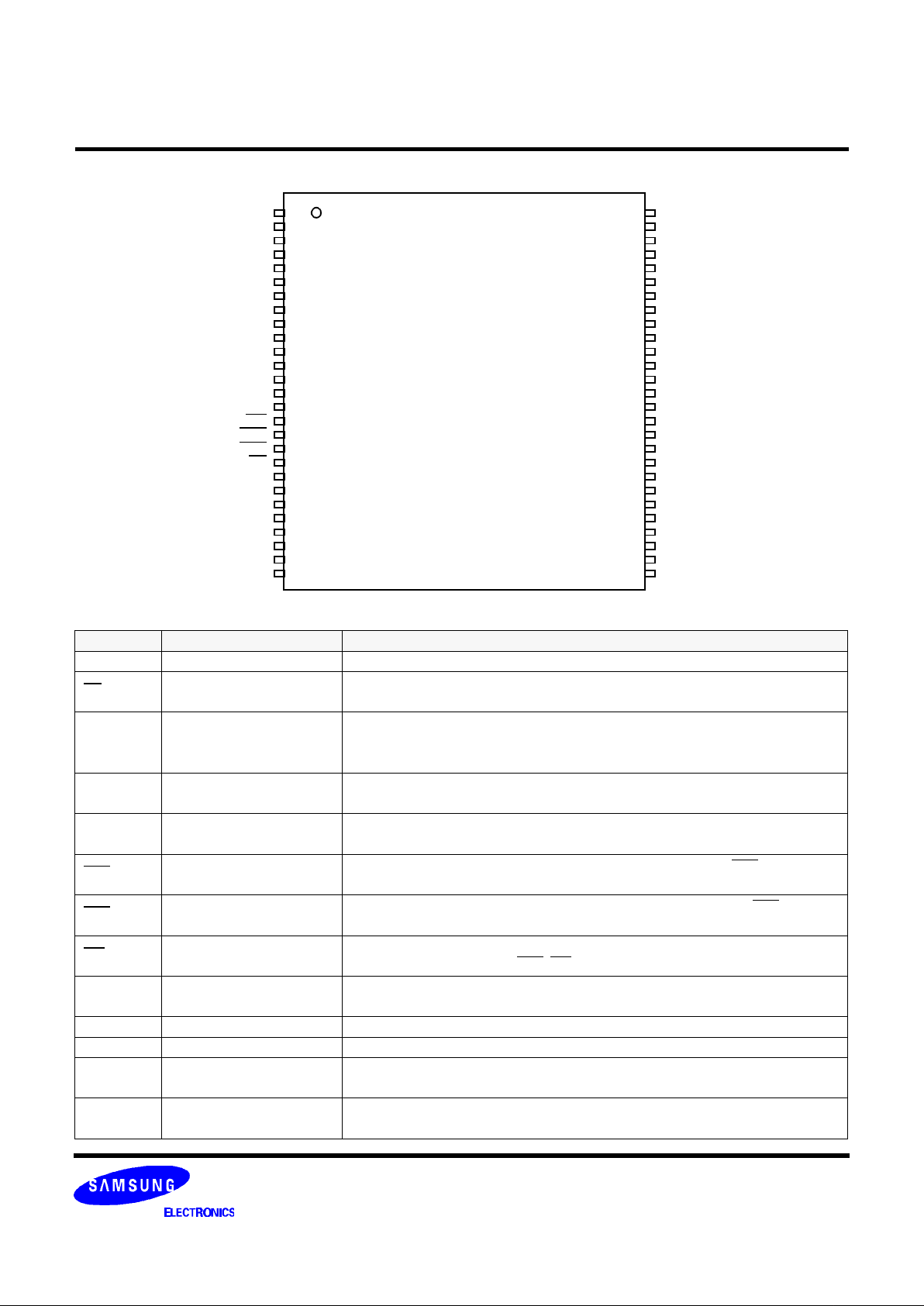

PIN FUNCTION DESCRIPTION

Pin Name Input Function

CLK System clock Active on the positive going edge to sample all inputs.

CS Chip select

Disables or enables device operation by masking or enabling all inputs except

CLK, CKE and DQM

CKE Clock enable

Masks system clock to freeze operation from the next clock cycle.

CKE should be enabled at least one cycle prior to new command.

Disable input buffers for power down in standby.

A0 ~ A11 Address

Row/column addresses are multiplexed on the same pins.

Row address : RA0 ~ RA11, Column address : CA0 ~ CA8

BA0 ~ BA1 Bank select address

Selects bank to be activated during row address latch time.

Selects bank for read/write during column address latch time.

RAS Row address strobe

Latches row addresses on the positive going edge of the CLK with RAS low.

Enables row access & precharge.

CAS Column address strobe

Latches column addresses on the positive going edge of the CLK with CAS low.

Enables column access.

WE Write enable

Enables write operation and row precharge.

Latches data in starting from CAS, WE active.

L(U)DQM Data input/output mask

Makes data output Hi-Z, tSHZ after the clock and masks the output.

Blocks data input when L(U)DQM active.

DQ0 ~ 15 Data input/output Data inputs/outputs are multiplexed on the same pins.

VDD/VSS Power supply/ground Power and ground for the input buffers and the core logic.

VDDQ/VSSQ Data output power/ground

Isolated power supply and ground for the output buffers to provide improved noise

immunity.

N.C/RFU

No connection

/reserved for future use

This pin is recommended to be left No Connection on the device.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

PIN CONFIGURATION (Top view)

54Pin sTSOP

(400mil x 441mil)

(0.4 mm Pin pitch)

Page 3

K4S281632B-N

CMOS SDRAM

shrink-TSOP

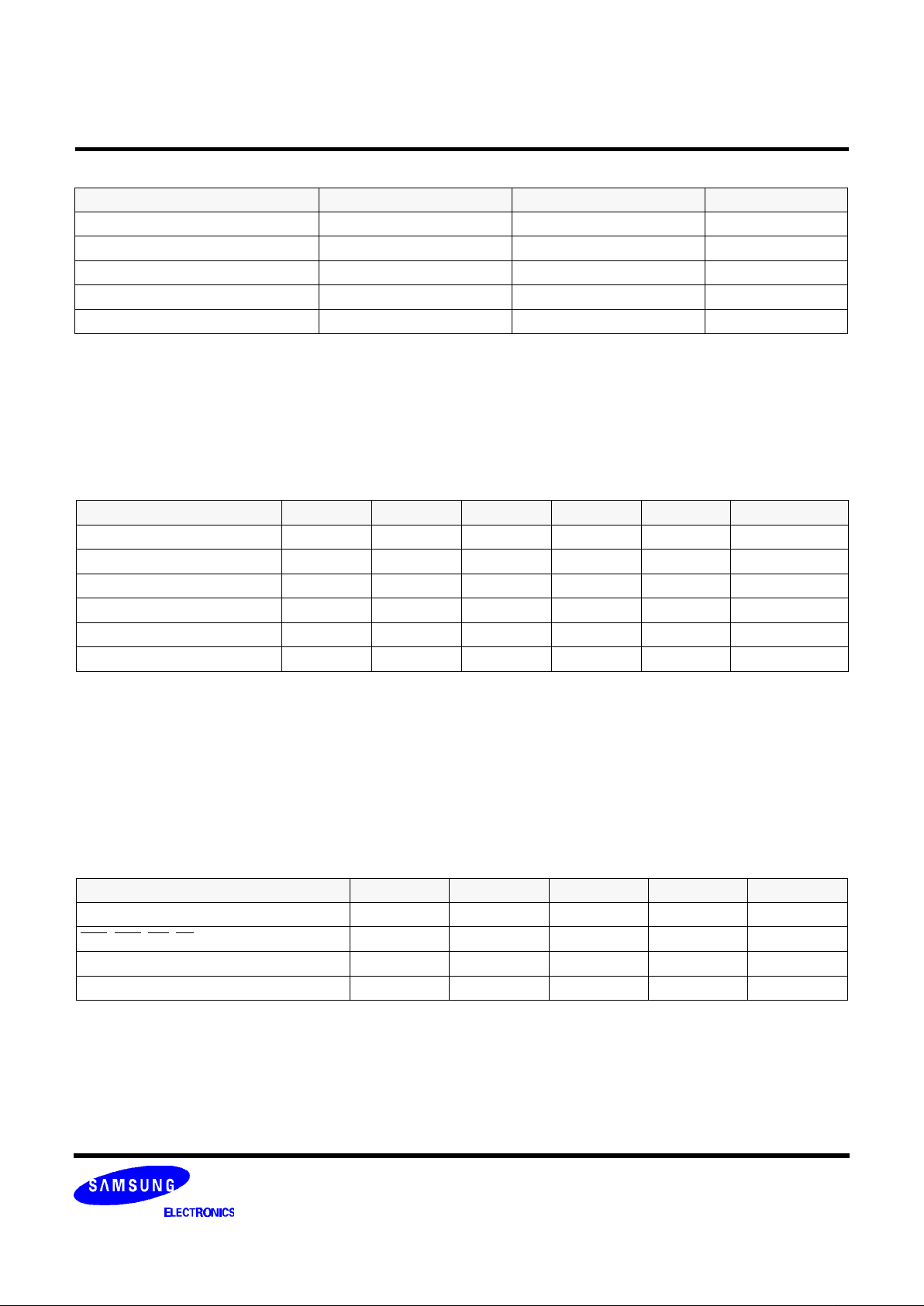

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Value Unit

Voltage on any pin relative to Vss VIN, VOUT -1.0 ~ 4.6 V

Voltage on VDD supply relative to Vss VDD, VDDQ -1.0 ~ 4.6 V

Storage temperature TSTG -55 ~ +150 °C

Power dissipation PD 1 W

Short circuit current IOS 50 mA

Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

Note :

DC OPERATING CONDITIONS

Recommended operating conditions (Voltage referenced to VSS = 0V, TA = 0 to 70°C)

Parameter Symbol Min Typ Max Unit Note

Supply voltage VDD, VDDQ 3.0 3.3 3.6 V

Input logic high voltage VIH 2.0 3.0 VDD+0.3 V 1

Input logic low voltage VIL -0.3 0 0.8 V 2

Output logic high voltage VOH 2.4 - - V IOH = -2mA

Output logic low voltage VOL - - 0.4 V IOL = 2mA

Input leakage current ILI -10 - 10 uA 3

1. VIH (max) = 5.6V AC.The overshoot voltage duration is ≤ 3ns.

2. VIL (min) = -2.0V AC. The undershoot voltage duration is ≤ 3ns.

3. Any input 0V ≤ VIN ≤ VDDQ,

Input leakage currents include Hi-Z output leakage for all bi-directional buffers with Tri-State outputs.

Notes :

CAPACITANCE (VDD = 3.3V, TA = 23°C, f = 1MHz, VREF =1.4V ± 200 mV)

Pin Symbol Min Max Unit Note

Clock CCLK 2.5 4.0 pF 1

RAS, CAS, WE, CS, CKE, DQM CIN 2.5 5.0 pF 2

Address CADD 2.5 5.0 pF 2

DQ0 ~ DQ15 COUT 4.0 6.5 pF 3

Page 4

K4S281632B-N

CMOS SDRAM

shrink-TSOP

DC CHARACTERISTICS

1. Measured with outputs open.

2. Refresh period is 64ms.

3. K4S281632B-NC**

4. K4S281632B-NL**

5. Unless otherwise noted, input swing IeveI is CMOS(VIH /VIL=VDDQ/VSSQ)

Notes :

(Recommended operating condition unless otherwise noted, TA = 0 to 70°C)

Parameter Symbol Test Condition

Version

Unit Note

-1H -1L

Operating current

(One bank active)

ICC1

Burst length = 1

tRC ≥ tRC(min)

IO = 0 mA

140 mA 1

Precharge standby current in

power-down mode

ICC2P CKE ≤ VIL(max), tCC = 10ns 1

mA

ICC2PS CKE & CLK ≤ VIL(max), tCC = ∞ 1

Precharge standby current in

non power-down mode

ICC2N

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

Input signals are changed one time during 20ns

20

mA

ICC2NS

CKE ≥ VIH(min), CLK ≤ VIL(max), tCC = ∞

Input signals are stable

7

Active standby current in powerdown mode

ICC3P CKE ≤ VIL(max), tCC = 10ns 5

mA

ICC3PS CKE & CLK ≤ VIL(max), tCC = ∞ 5

Active standby current in

non power-down mode

(One bank active)

ICC3N

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

Input signals are changed one time during 20ns

30 mA

ICC3NS

CKE ≥ VIH(min), CLK ≤ VIL(max), tCC = ∞

Input signals are stable

20 mA

Operating current

(Burst mode)

ICC4

IO = 0 mA

Page burst

4Banks Activated

tCCD = 2CLKs

145 mA 1

Refresh current ICC5 tRC ≥ tRC(min) 210 mA 2

Self refresh current ICC6 CKE ≤ 0.2V

G 1.5 mA 3

F 800 uA 4

Page 5

K4S281632B-N

CMOS SDRAM

shrink-TSOP

AC OPERATING TEST CONDITIONS (VDD = 3.3V ± 0.3V, TA = 0 to 70°C)

Parameter Value Unit

AC input levels (Vih/Vil) 2.4/0.4 V

Input timing measurement reference level 1.4 V

Input rise and fall time tr/tf = 1/1 ns

Output timing measurement reference level 1.4 V

Output load condition See Fig. 2

3.3V

1200Ω

870Ω

Output

50pF

VOH (DC) = 2.4V, IOH = -2mA

VOL (DC) = 0.4V, IOL = 2mA

Vtt = 1.4V

50Ω

Output

50pF

Z0 = 50Ω

(Fig. 2) AC output load circuit (Fig. 1) DC output load circuit

OPERATING AC PARAMETER

(AC operating conditions unless otherwise noted)

Parameter Symbol

Version

Unit Note

-1H -1L

Row active to row active delay tRRD(min) 20 ns 1

RAS to CAS delay tRCD(min) 20 ns 1

Row precharge time tRP(min) 20 ns 1

Row active time

tRAS(min) 50 ns 1

tRAS(max) 100 us

Row cycle time tRC(min) 70 ns 1

Last data in to row precharge tRDL(min) 2 CLK 2,5

Last data in to Active delay tDAL(min) 2 CLK + 20 ns - 5

Last data in to new col. address delay tCDL(min) 1 CLK 2

Last data in to burst stop tBDL(min) 1 CLK 2

Col. address to col. address delay tCCD(min) 1 CLK 3

Number of valid output data

CAS latency=3 2

ea 4

CAS latency=2 1

1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time

and then rounding off to the next higher integer.

2. Minimum delay is required to complete write.

3. All parts allow every cycle column address change.

4. In case of row precharge interrupt, auto precharge and read burst stop.

5. tRDL=1CLK and tDAL=1CLK+20ns is also supported .

SAMSUNG recommends tRDL=2CLK and tDAL=2CLK + 20ns.

Notes :

Page 6

K4S281632B-N

CMOS SDRAM

shrink-TSOP

AC CHARACTERISTICS (AC operating conditions unless otherwise noted)

Parameter Symbol

-1H -1L

Unit Note

Min Max Min Max

CLK cycle time

CAS latency=3

tCC

10

1000

10

1000 ns 1

CAS latency=2 10 12

CLK to valid

output delay

CAS latency=3

tSAC

6 6

ns 1,2

CAS latency=2 6 7

Output data

hold time

CAS latency=3

tOH

3 3

ns 2

CAS latency=2 3 3

CLK high pulse width tCH 3 3 ns 3

CLK low pulse width tCL 3 3 ns 3

Input setup time tSS 2 2 ns 3

Input hold time tSH 1 1 ns 3

CLK to output in Low-Z tSLZ 1 1 ns 2

CLK to output

in Hi-Z

CAS latency=3

tSHZ

6 6

ns

CAS latency=2 6 7

1. Parameters depend on programmed CAS latency.

2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.

3. Assumed input rise and fall time (tr & tf) = 1ns.

If tr & tf is longer than 1ns, transient time compensation should be considered,

i.e., [(tr + tf)/2-1]ns should be added to the parameter.

Notes :

DQ BUFFER OUTPUT DRIVE CHARACTERISTICS

Parameter Symbol Condition Min Typ Max Unit Notes

Output rise time trh

Measure in linear

region : 1.2V ~ 1.8V

1.37 4.37 Volts/ns 3

Output fall time tfh

Measure in linear

region : 1.2V ~ 1.8V

1.30 3.8 Volts/ns 3

Output rise time trh

Measure in linear

region : 1.2V ~ 1.8V

2.8 3.9 5.6 Volts/ns 1,2

Output fall time tfh

Measure in linear

region : 1.2V ~ 1.8V

2.0 2.9 5.0 Volts/ns 1,2

1. Rise time specification based on 0pF + 50 Ω to VSS, use these values to design to.

2. Fall time specification based on 0pF + 50 Ω to VDD, use these values to design to.

3. Measured into 50pF only, use these values to characterize to.

4. All measurements done with respect to VSS.

Notes :

Page 7

K4S281632B-N

CMOS SDRAM

shrink-TSOP

SIMPLIFIED TRUTH TABLE

(V=Valid, X=Don′t care, H=Logic high, L=Logic low)

Command CKEn-1 CKEn CS RAS CAS WE DQM BA0,1 A10/AP

A11,

A9 ~ A0

Note

Register Mode register set H X L L L L X OP code 1,2

Refresh

Auto refresh

H

H

L L L H X X

3

Self

fefresh

Entry L 3

Exit L H

L H H H

X X

3

H X X X 3

Bank active & row addr. H X L L H H X V Row address

Read &

column address

Auto precharge disable

H X L H L H X V

L

Column

address

(A0 ~ A8)

4

Auto precharge enable H 4,5

Write &

column address

Auto precharge disable

H X L H L L X V

L

Column

address

(A0 ~ A8)

4

Auto precharge enable H 4,5

Burst stop H X L H H L X X 6

Precharge

Bank selection

H X L L H L X

V L

X

All banks X H

Clock suspend or

active power down

Entry H L

H X X X

X

X

L V V V

Exit L H X X X X X

Precharge power down mode

Entry H L

H X X X

X

X

L H H H

Exit L H

H X X X

X

L V V V

DQM H X V X 7

No operation command H X

H X X X

X X

L H H H

1. OP Code : Operand code

A0 ~ A11 & BA0 ~ BA1 : Program keys. (@ MRS)

2. MRS can be issued only at all banks precharge state.

A new command can be issued after 2 CLK cycles of MRS.

3. Auto refresh functions are as same as CBR refresh of DRAM.

The automatical precharge without row precharge command is meant by "Auto".

Auto/self refresh can be issued only at all banks precharge state.

4. BA0 ~ BA1 : Bank select addresses.

If both BA0 and BA1 are "Low" at read, write, row active and precharge, bank A is selected.

If both BA0 is "Low" and BA1 is "High" at read, write, row active and precharge, bank B is selected.

If both BA0 is "High" and BA1 is "Low" at read, write, row active and precharge, bank C is selected.

If both BA0 and BA1 are "High" at read, write, row active and precharge, bank D is selected.

If A10/AP is "High" at row precharge, BA0 and BA1 is ignored and all banks are selected.

5. During burst read or write with auto precharge, new read/write command can not be issued.

Another bank read/write command can be issued after the end of burst.

New row active of the associated bank can be issued at tRP after the end of burst.

6. Burst stop command is valid at every burst length.

7. DQM sampled at positive going edge of a CLK and masks the data-in at the very CLK (Write DQM latency is 0),

but makes Hi-Z state the data-out of 2 CLK cycles after. (Read DQM latency is 2)

Notes :

Page 8

K4S281632B-N

CMOS SDRAM

shrink-TSOP

PACKAGE DIMENSIONS FOR 54-sTSOP

0.010

0.05

MIN

0.008

0.21

± 0.002

± 0.05

0.020

0.50

( )

0.005

-0.001

+0.003

0.125

-0.035

+0.075

0.45~0.75

0.018~0.030

0.010

0.25

TYP

0~8°C

#54

#28

#1

#27

MAX

0.0157

0.40

0.047

1.20

MAX

0.039

1.00

± 0.004

± 0.10

Unit : Millimeters

0.10

0.004

11.76±0.20

0.463±0.008

0.400

10.16

0.457

11.60

MAX

0.441

11.20

± 0.004

± 0.10

0.006

0.16±0.10

±0.004

0.016

0.40

( )

Loading...

Loading...