Datasheet ISPLSI81080V-90LB492, ISPLSI81080V-90LB272, ISPLSI81080V-60LB492, ISPLSI81080V-60LB272, ISPLSI81080V-125LB492 Datasheet (Lattice Semiconductor Corporation)

...Page 1

®

ispLSI

81080V

3.3V In-System Programmable

SuperBIG™ High Density PLD

Features

• SuperBIG HIGH DENSITY IN-SYSTEM

PROGRAMMABLE LOGIC

— 3.3V Power Supply

— 60,000 PLD Gates/1080 Macrocells

— 192-360 I/O Pins Supporting 3.3V/2.5V I/O

— 1440 Registers

— High-Speed Global and Big Fast Megablock (BFM)

Interconnect

— Wide 20-Macrocell Generic Logic Block (GLB) for

High Performance

— Wide Input Gating (44 Inputs per GLB) for Fast

Counters, State Machines, Address Decoders, Etc.

— PCB-Efficient Ball Grid Array (BGA) Package

Options

2

• HIGH-PERFORMANCE E

—

fmax = 125 MHz Maximum Operating Frequency

tpd = 8.5 ns Propagation Delay

—

— Electrically Erasable and Reprogrammable

— Non-Volatile

— Programmable Speed/Power Logic Path

Optimization

• IN-SYSTEM PROGRAMMABLE

— Increased Manufacturing Yields, Reduced Time-to-

Market and Improved Product Quality

— Reprogram Soldered Devices for Faster Debugging

• 100% IEEE 1149.1 BOUNDARY SCAN TESTABLE AND

3.3V IN-SYSTEM PROGRAMMABLE

• ARCHITECTURE FEATURES

— Enhanced Pin-Locking Architecture, Symmetrical

Generic Logic Blocks Connected by Hierarchical

Big Fast Megablock and Global Routing Planes

— Product Term Sharing Array Supports up to 28

Product Terms per Macrocell Output

— Macrocells Support Concurrent Combinatorial and

Registered Functions

— Embedded Tristate Bus Can Be Used as an Internal

Tristate Bus or as an Extension of an External

Tristate Bus

— Macrocell and I/O Registers Feature Multiple Control

Options, Including Set, Reset and Clock Enable

— I/O Pins Support Programmable Bus Hold, Pull-Up,

Open-Drain and Slew Rate Options

— Separate VCCIO Power Supply to Support 3.3V or

2.5V Input/Output Logic Levels

— I/O Cell Register Programmable as Input Register for

Fast Setup Time or Output Register for Fast Clock to

Output Time

CMOS® TECHNOLOGY

• ispDesignEXPERT™ – LOGIC COMPILER AND COMPLETE ISP DEVICE DESIGN SYSTEMS FROM HDL

SYNTHESIS THROUGH IN-SYSTEM PROGRAMMING

— Superior Quality of Results

— Tightly Integrated with Leading CAE Vendor Tools

— Productivity Enhancing Timing Analyzer, Explore

Tools, Timing Simulator and ispANALYZER™

— PC and UNIX Platforms

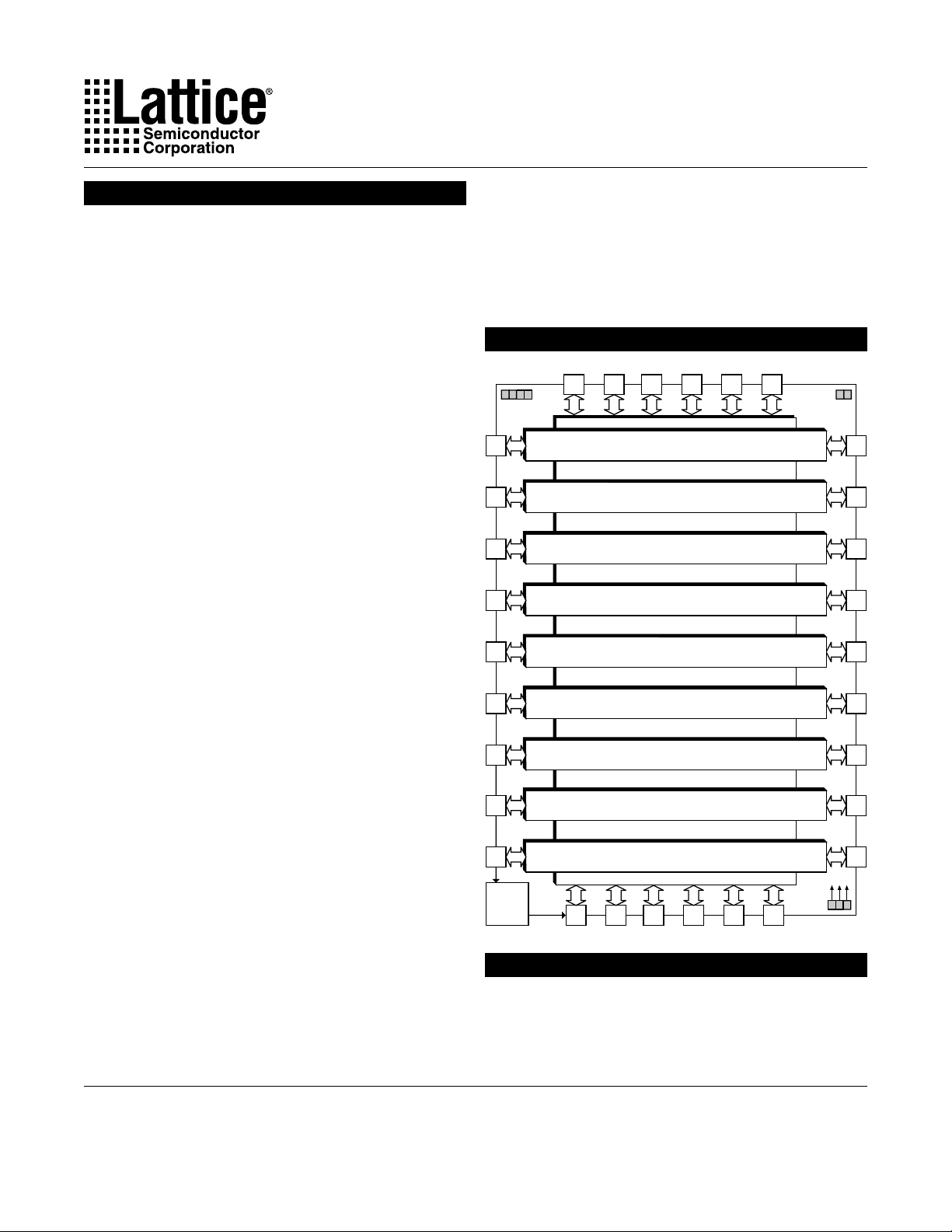

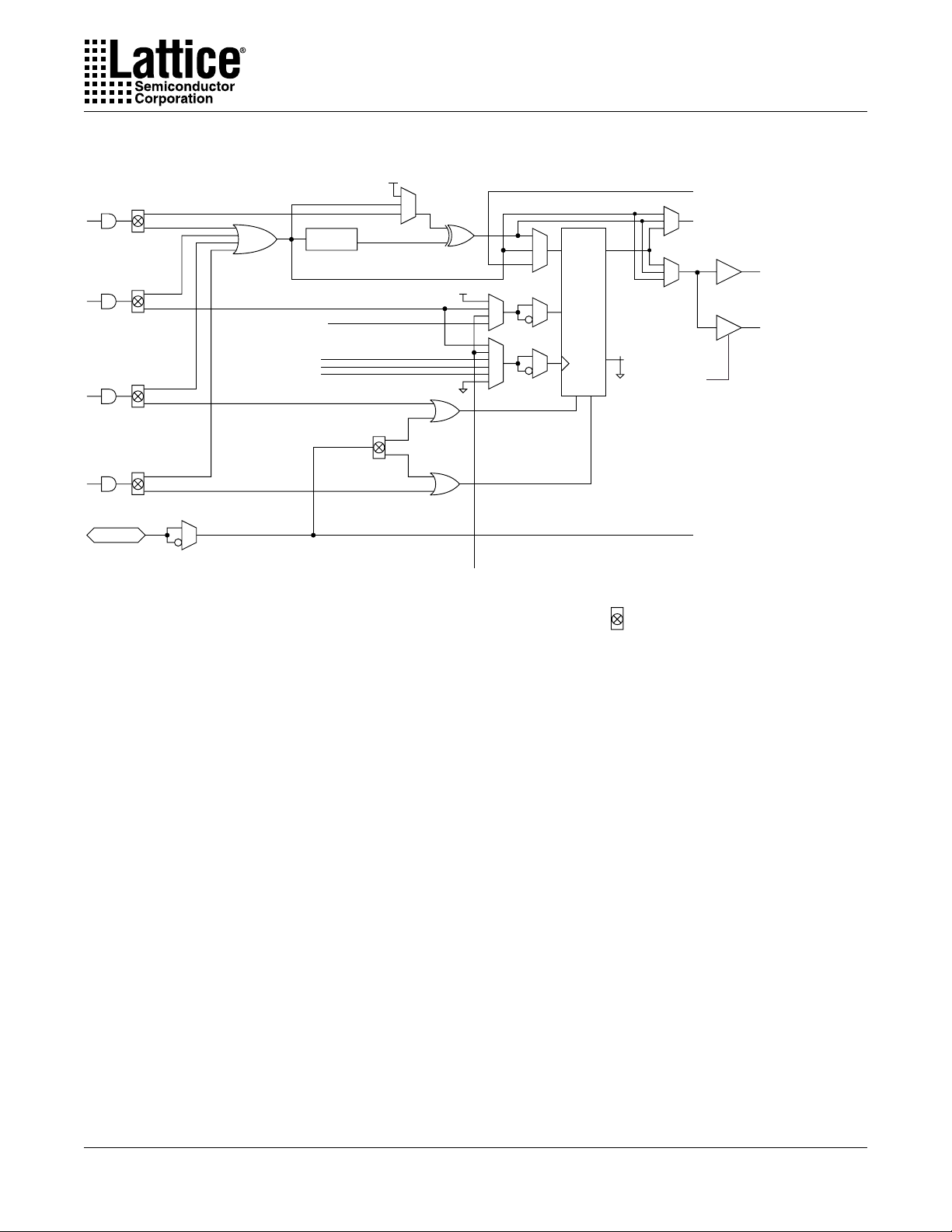

Functional Block Diagram

12

I/O

12

I/O

12

I/O

12

I/O

12

I/O

12

I/O

12

I/O

12

I/O

12

I/O

Boundary

Scan

12

I/O

12

I/O

12

12

I/O

I/O

12

I/O12I/O12I/O

Big Fast Megablock 0

Big Fast Megablock 1

Big Fast Megablock 2

Big Fast Megablock 3

Big Fast Megablock 4

Global Routing Plane

Big Fast Megablock 5

Big Fast Megablock 6

Big Fast Megablock 7

Big Fast Megablock 8

12

12

I/O

I/O

12

I/O12I/O12I/O

81080v block

12

I/O

12

I/O

12

I/O

12

I/O

12

I/O

12

I/O

12

I/O

12

I/O

12

I/O

ispLSI 8000V Family Description

The ispLSI 8000V Family of Register-Intensive, 3.3V

SuperBIG In-System Programmable Logic Devices is

based on Big Fast Megablocks of 120 registered macrocells and a Global Routing Plane (GRP) structure

Copyright © 2000 Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject

to change without notice.

LATTICE SEMICONDUCTOR CORP., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A.

July 2000

Tel. (503) 268-8000; 1-800-LATTICE; FAX (503) 268-8556; http://www.latticesemi.com

81080v_03 1

Page 2

Specifications ispLSI 81080V

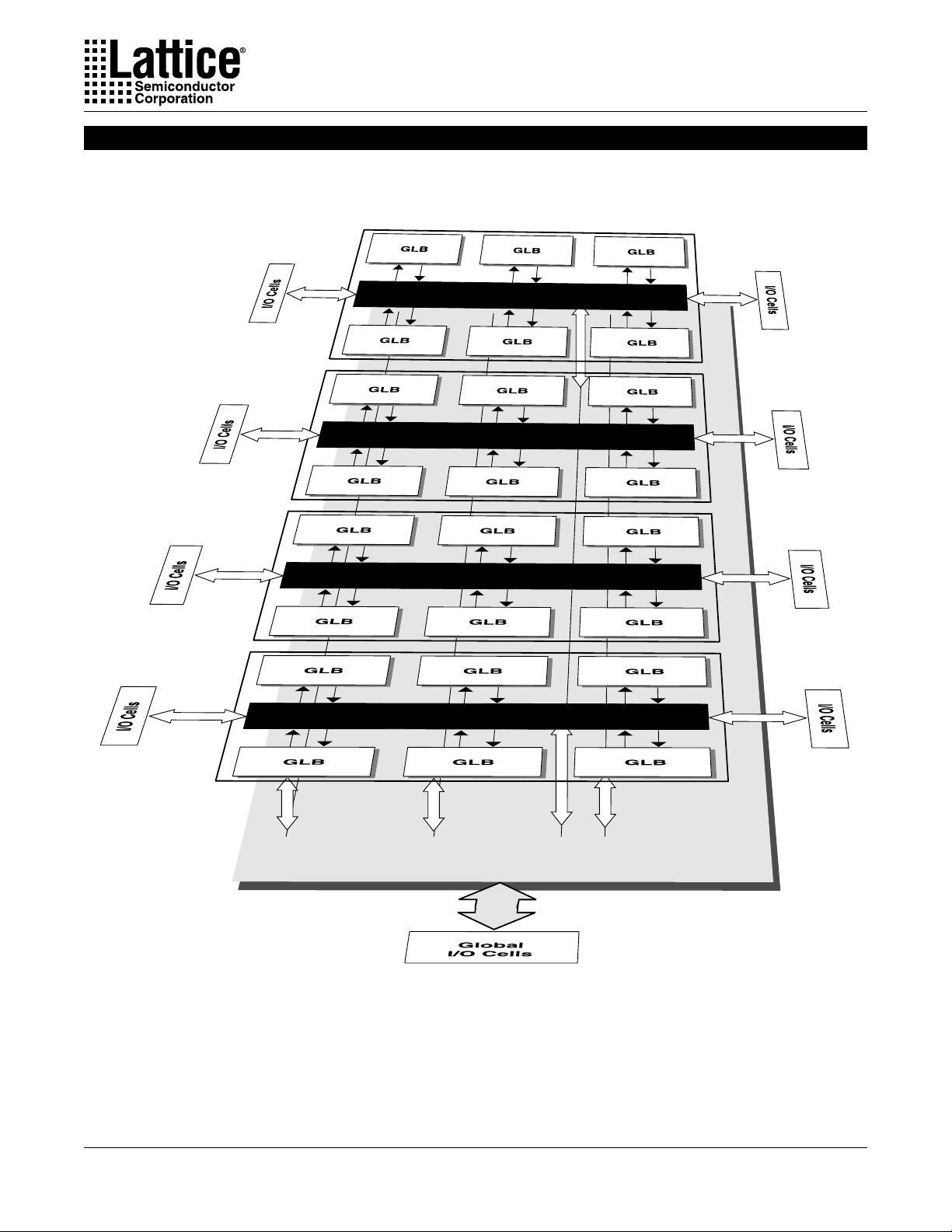

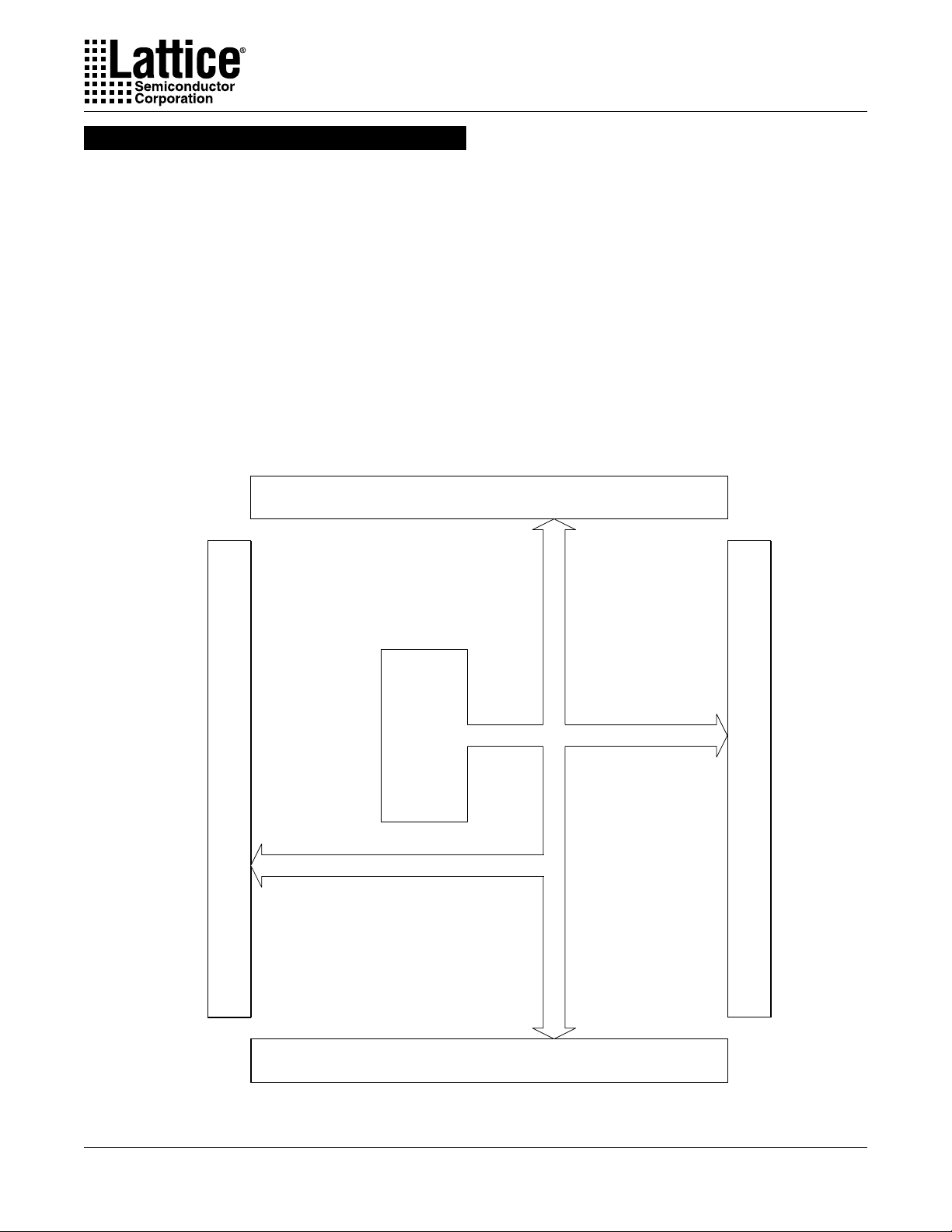

Functional Block Diagram

Figure 1. ispLSI 81080V Functional Block Diagram (Perspective)

Big Fast Megablock Routing Pool (BRP)

Big Fast Megablock Routing Pool (BRP)

Big Fast Megablock Routing Pool (BRP)

Big Fast Megablock Routing Pool (BRP)

Global Routing Plane (GRP) with Tristate Bus Lines

2

Page 3

ispLSI 8000V Family Description (Continued)

Specifications ispLSI 81080V

interconnecting the Big Fast Megablocks. Each Big Fast

Megablock contains 120 registered macrocells arranged

in six groups of 20, a group of 20 being referred to as a

Generic Logic Block, or GLB. Within the Big Fast

Megablock, a Big Fast Megablock Routing Pool (BRP)

interconnects the six GLBs to each other and to 24 Big

Fast Megablock I/O cells with optional I/O registers. The

Global Routing Plane which interconnects the Big Fast

Megablocks has additional global I/Os with optional I/O

registers. The 192-I/O version contains 72 Big Fast

Megablock I/Os and 120 global I/Os, while the 360-I/O

version contains 216 Big Fast Megablock I/Os and 144

global I/Os.

Outputs from the GLBs in a Big Fast Megablock can drive

both the Big Fast Megablock Routing Pool within the Big

Fast Megablock and the Global Routing Plane between

the Big Fast Megablocks. Switching resources are provided to allow signals in the Global Routing Plane to drive

any or all the Big Fast Megablocks in the device. This

mechanism allows fast, efficient connections, both within

the Big Fast Megablocks and between them.

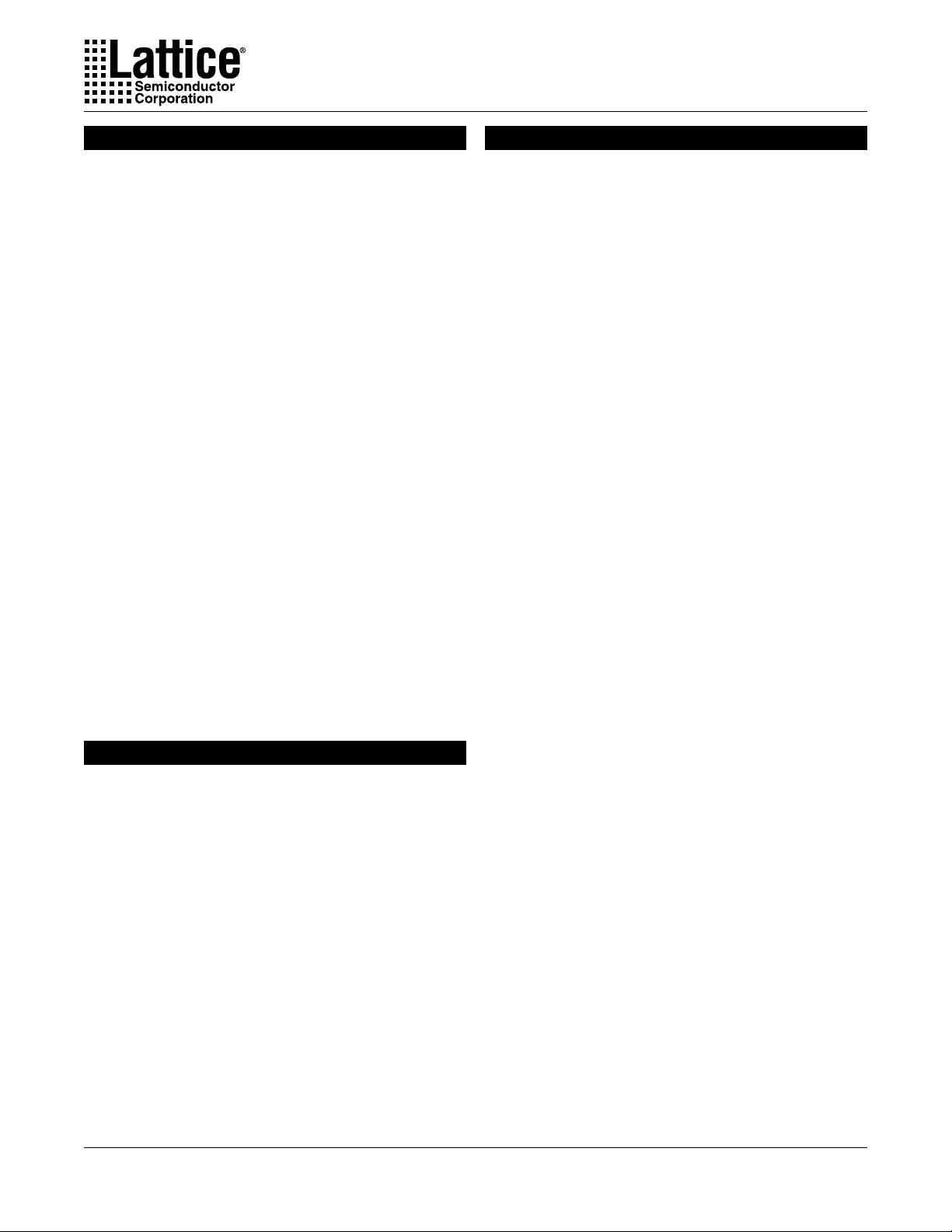

Each GLB contains 20 macrocells and a fully populated,

programmable AND-array with 82 logic product terms.

The GLB has 44 inputs from the Big Fast Megablock

Routing Pool which are available in both true and complement form for every product term. Up to 20 of these inputs

can be switched to provide local feedback into the GLB

for logic functions that require it. The 80 general-purpose

product terms can be grouped into 20 sets of four and

sent into a Product Term Sharing Array (PTSA) which

allows sharing up to a maximum of 28 product terms for

a single function. Alternatively, the PTSA can be bypassed for functions of four product terms or less.

The 20 registered macrocells in the GLB are driven by the

20 outputs from the PTSA or the PTSA bypass. Each

macrocell contains a programmable XOR gate, a programmable register/latch/toggle flip-flop and the

necessary clocks and control logic to allow combinatorial

or registered operation. Each macrocell has two outputs,

one output can be fed back inside the GLB to the ANDarray, while the other output drives both the Big Fast

Megablock Routing Pool and the Global Routing Plane.

This dual output capability from the macrocell allows

efficient use of the hardware resources. One output can

be a registered function for example, while the other

output can be an unrelated combinatorial function.

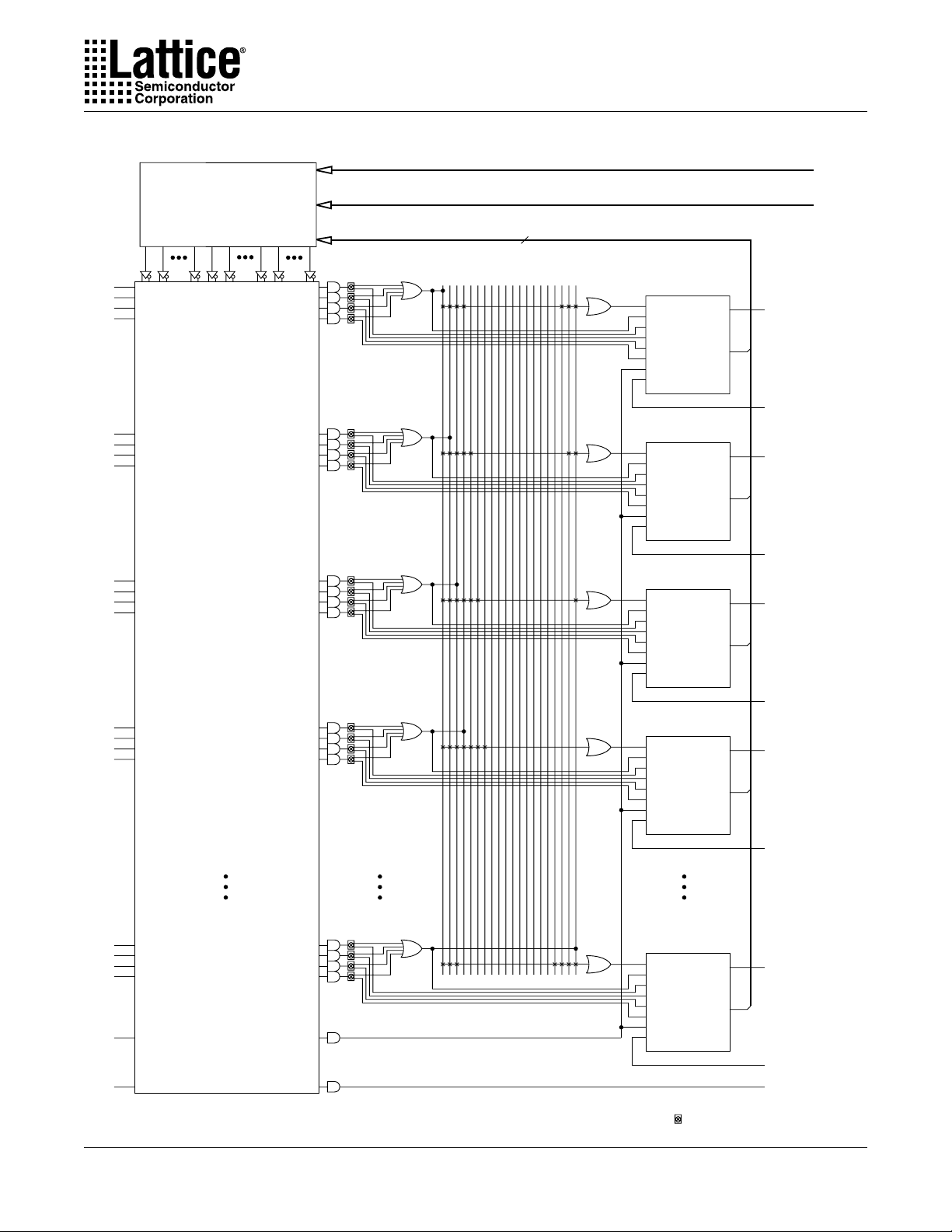

Macrocell registers can be clocked from one of several

global, local or product term clocks available on the

device. A global, local and product term clock enable is

also provided, eliminating the need to gate the clock to

the macrocell registers. Reset and preset for the macrocell register is provided from both global and product term

signals. The polarity of all of these control signals is

selectable on an individual macrocell basis. The macrocell register can be programmed to operate as a D-type

register, a D-type flow-through latch or a T-type flip flop.

The 20 outputs from the GLB can drive both the Big Fast

Megablock Routing Pool within the Big Fast Megablock

and the Global Routing Plane between the Big Fast

Megablocks. The Big Fast Megablock Routing Pool contains general purpose tracks which interconnect the six

GLBs within the Big Fast Megablock and dedicated

tracks for the signals from the Big Fast Megablock I/O

cells. The Global Routing Plane contains general purpose tracks that interconnect the Big Fast Megablocks

and also carry the signals from the I/Os connected to the

Global Routing Plane.

Control signals for the I/O cell registers are generated

using an extra product term within each GLB, or using

dedicated input pins. Each GLB has two extra product

terms beyond the 80 available for the macrocell logic.

The first additional product term is used as an optional

shared product term clock for all the macrocells within the

GLB. The second additional product term is then routed

to an I/O Control Bus using a separate routing structure

from the Big Fast Megablock Routing Pool and Global

Routing Plane. Use of a separate control bus routing

structure allows the I/O registers to have many control

signals with no impact on the interconnection of the GLBs

and Big Fast Megablocks. The I/O Control Bus is split into

four quadrants, each servicing the I/O cell control requirements for one edge of the device. Signals in the

control bus can be independently selected by any or all

I/O cells to act as clock, clock enable, output enable,

reset or preset.

Each Big Fast Megablock has 24 I/O cells. The Global

Routing Pool has 144 I/O cells. Each I/O cell can be

configured as a combinatorial input, combinatorial output, registered input, registered output or bidirectional

I/O. I/O cell registers can be clocked from one of several

global, local or product term clocks which are selected

from the I/O control bus. A global and product term clock

enable is also provided, eliminating the need for the user

to gate the clock to the I/O cell registers. Reset and preset

for the I/O cell register is provided from both global and

product term signals. The polarity of all of these control

3

Page 4

Specifications ispLSI 81080V

ispLSI 8000V Family Description (Continued)

signals is selectable on an individual I/O cell basis. The

I/O cell register can be programmed to operate as a Dtype register or a D-type latch.

The input thresholds are fixed at levels which comply with

both 3.3V and 2.5V interfaces. The output driver can

source 4mA and sink 8mA (3.3V output supply). The

output drivers have a separate VCCIO power supply

which is independent of the main VCC supply for the

device. This feature allows the output drivers to run from

either 3.3V or 2.5V while the device logic is always

powered from 3.3V. The output drivers also provide

individually programmable edge rates and open drain

capability. A programmable pullup resistor is provided to

tie off unused inputs and a programmable bus-hold latch

is available to hold tristate outputs in their last valid state

until the bus is driven again by another device.

The ispLSI 8000V Family features 3.3V, non-volatile insystem programmability for both the logic and the

interconnect structures, providing the means to develop

truly reconfigurable systems. Programming is achieved

through the industry standard IEEE 1149.1-compliant

Boundary Scan interface using the JTAG protocol. Boundary Scan test is also supported through the same interface.

An enhanced, multiple cell security scheme is provided

that prevents reading of the JEDEC programming file

when secured. After the device has been secured using

this mechanism, the only way to clear the security is to

execute a bulk-erase instruction.

ispLSI 81080V Description

The ispLSI 81080V device has nine Big Fast Megablocks

for a total of 9 x 120 = 1080 macrocells.

Each Big Fast Megablock has a total of 24 I/O cells and

the Global Routing Plane has a total of 144 I/O cells. This

gives (9 x 24) + 144 = 360 I/Os for the full I/O version,

while the partial I/O version contains 72 Big Fast

Megablock I/Os + 120 global I/Os = 192 I/Os.

Embedded Tristate Bus

There is a 108-line embedded internal tristate bus as part

of the Global Routing Plane (GRP), enabling multiple

GLBs to drive the same tracks. This bus can be partitioned into various bus widths such as twelve 9-line

buses, six 18-line buses or three 36-line buses. The

GLBs can dynamically share a subset of the Global

Routing Plane tracks. This feature eliminates the need to

convert tristate buses to wide multiplexers on the programmable device. Up to 18 macrocells per GLB can

participate in driving the embedded tristate bus. The

remaining two macrocells per GLB are used to generate

the internal tristate driver control signals on each data

byte (with parity). The embedded tristate bus can also be

configured as an extension of an external tristate bus

using the bidirectional capability of the I/O cells connected to the Global Routing Plane. The Global Routing

Plane I/Os 0-8 and 15-23 from each group (I/OGx as

defined in the I/O Pin Location Table) can connect to the

internal tristate bus as well as the unidirectional/nontristate global routing channels. I/Os 9-14 connect only to

the global routing channel.

The embedded tristate bus has internal bus hold and

arbitration features in order to make the function more

“user friendly”. The bus hold feature keeps the internal

bus at the previously driven logic state when the bus is

not driven to eliminate bus float. The bus arbitration is

performed on a “first come, first served” priority. In other

words, once a logic block drives the bus, other logic

blocks cannot drive the bus until the first releases the bus.

This arbitration feature prevents internal bus contention

when there is an overlap between two bus enable signals. Typically, it takes about 3ns to resolve one bus

signal coming off the bus to another bus signal driving the

bus. The arbitration feature, combined with the predictability of the CPLD, makes the embedded tristate bus the

most practical for real world bus implementation.

The total registers in the device is the sum of macrocells

plus I/O cells, 1080 + 360 = 1440 registers.

4

Page 5

Figure 2. ispLSI 8000V GLB Overview

I/O Big Fast Megablock Input Tracks

Specifications ispLSI 81080V

PT 0

PT 1

PT 2

PT 3

PT 4

PT 5

PT 6

PT 7

PT 8

PT 9

PT 10

PT 11

AND Array Input

0

Fully Populated

Routing

AND Array

General Purpose Big Fast Megablock Input Tracks

Feedback Inputs

43

Product Term

Sharing Array

20

Macrocell 0

From PTSA

PTSA Bypass

Single PT

PT Clock

PT Preset

PT Reset

Shared PT Clock

Bus Input

Macrocell 1

From PTSA

PTSA Bypass

Single PT

PT Clock

PT Preset

PT Reset

Shared PT Clock

Bus Input

Macrocell 2

From PTSA

PTSA Bypass

Single PT

PT Clock

PT Preset

PT Reset

Shared PT Clock

Bus Input

0

1

2

To Interconnect

From Tristate

Bus Track

To Interconnect

From Tristate

Bus Track

To Interconnect

PT 12

PT 13

PT 14

PT 15

PT 76

PT 77

PT 78

PT 79

PT 80

PT 81

Macrocell 3

From PTSA

PTSA Bypass

Single PT

PT Clock

PT Preset

PT Reset

Shared PT Clock

Bus Input

Macrocell 19

From PTSA

PTSA Bypass

Single PT

PT Clock

PT Preset

PT Reset

Shared PT Clock

Bus Input

Function Selector (E2 Cell Controlled)Note: Macrocells 9 and 10 do not support Tristate Bus Feedback.

From Tristate

Bus Track

To interconnect

3

From Tristate

Bus Track

To Interconnect

19

From Tristate Bus Track

To Output Control MUX

5

Page 6

Figure 3. ispLSI 8000V Macrocell Overview

Single PT

PTSA

PTSA Bypass

PT Clock

Global Clock Enable

Global Clock 0

Global Clock 1

Global Clock 2

PT Reset

GRST

PT Preset

Specifications ispLSI 81080V

Bus Input From Tristate

Bus Track*

Feedback to AND Array

DQ

To Big Fast Megablock

or Global Interconnect

Clk En

RP

R/L

From Macrocell

9 or 10

To Specific

Global Tristate Bus*

Reset pin

Preset/Reset Input has Global Polarity Control

GRST

To All Macrocells and I/O Cells

From PT80

: Function Selector (E2 Cell Controlled)*Not available for Macrocells 9 and 10.

6

Page 7

Figure 4. ispLSI 8000V I/O Cell

Specifications ispLSI 81080V

TOE

GLOBAL OE0

GLOBAL OE1

GLOBAL OE2

GLOBAL OE3

From Output

Control Bus

Multiplexed Output From

Big Fast Megablock or

Global Track

GLOBAL I/O CLOCK ENABLE

From Output

Control Bus

GLOBAL CLOCK0

GLOBAL CLOCK2

QUADRANT I/O CLOCK

From Output

Control Bus

DQ

CLKEN

R/L

R

P

VCCIO

Slew

Rate

VCCIO

Open

Drain

VCCIO

Big Fast Megablock I/O Pad

or Global I/O Pad

To Specific

Big Fast Megablock

or Global Tracks

To Specific

Global Tristate Bus

From Output

Control Bus

Global I/O Cell

Only

GRST

From Output

Control Bus

: Function Selector (E2 Cell Controlled)

7

Page 8

Specifications ispLSI 81080V

Output Control Organization

The Global OE signals and Test OE signal are driven

from the dedicated external control input pins.

In addition to the data input and output to the I/O cells,

each I/O cell can have up to six different I/O cell control

signals. In addition to the internal OE control, the five

control signals for each I/O cell consist of pin OE control,

clock enable, clock input, asynchronous preset and asynchronous reset. All of the I/O control signals can be driven

either from the dedicated external input pins or from the

internal control bus.

The output enable of each I/O cell can be driven by 21

different sources – 16 from the output control bus, four

from the Global OE pins and one from the Test OE pin.

The 16-bit wide output control buses are organized in four

different quadrants as shown in Figure 5. Since each

GLB is capable of generating the output control signals,

each of the output control bus signals can be driven from

a unique GLB. The 54 GLBs can generate a total of 54

unique I/O control signals. Referring to Figure 2, the GLB

generates its output control signal from control product

term (PT81).

Figure 5 also illustrates how the quadrant clocks are

routed to the appropriate quadrant I/O cells.

Figure 5. Output Control Bus and Quadrant Organization

Q

ra

, 1

d

a

t 0

u

n

B

(I/O

id

-B

it W

6

-B

0

O

e

<

8

-1

0

>

1

, Q

tp

u

t C

u

o

K

L

C

IO

s

u

l B

tro

n

)

0

s

u

l B

o

tr

n

o

t C

u

tp

u

O

e

id

it W

-B

6

, 1

t 1

n

ra

d

a

u

Q

)

1

K

L

C

IO

, Q

>

3

-2

2

1

<

5

-G

0

G

(I/O

s

u

G

B

L

G

ra

e

n

e

te

d

O

tp

u

t

u

tro

n

o

C

(se

F

e

ig

u

Q

d

a

u

ra

n

(I/O

t 2

6

, 1

B

-B

0

ro

F

m

1

8

P

l

re

2

)

-B

it W

<

8

2

1

T

id

tp

u

O

e

t C

u

o

-2

3

L

, Q

>

C

IO

s

u

l B

tro

n

)

2

K

l B

tro

n

o

t C

u

tp

u

O

e

id

it W

-B

6

, 1

t 3

n

a

r

d

a

u

Q

OE Bus/80180V

)

3

K

L

C

IO

, Q

>

1

1

-

0

<

5

-G

0

G

(I/O

8

Page 9

Figure 6. Boundary Scan Register Circuit for I/O Pins

SCANIN

(from previous

cell)

BSCAN

Registers

DQ DQ

PROG_MODE

BSCAN

Latches

Specifications ispLSI 81080V

HIGHZ

EXTEST

TOE

Normal

Function

EXTEST

PROG_MODE

OE

0

1

DQ

DQ

Shift DR

*Internal power-up reset signal. Not connected to external reset pin.

Clock DR

Update DR

DQ

Reset*

Figure 7. Boundary Scan Register Circuit for Input-Only Pins

Normal

Function

0

1

SCANOUT

(to next cell)

I/O Pin

Input Pin

SCANIN

(from previous

cell

Shift DR

Clock DR

DQ

9

SCANOUT

(to next cell)

Page 10

Specifications ispLSI 81080V

Figure 8. Boundary Scan Waveforms and Timing Specifications

TMS

TDI

T

btsu

T

btch

TCK

TDO

Data to be

captured

Data to be

driven out

SYMBOL

t

btcp TCK Clock Pulse Width — ns

t

btch

t

btcl

t

btsu

t

bth

t

rf TCK, TDI, TMS Rise and Fall Time — mV/ns

t

btco

t

btoz TAP Controller, TCK to TDO High-Impedance 25 ns—

t

btvo

t

btcpsu

t

btcph

t

btuco

t

btuoz

t

btuov

TCK Pulse Width High

TCK Pulse Width Low

TDI, TMS Setup Time to TCK

TDI, TMS Hold Time from TCK

TAP Controller, TCK to TDO Valid

TAP Controller, TCK to TDO High-Impedance to Valid Output

BSCAN Test Capture Register Setup Time

BSCAN Test Capture Register Hold Time

BSCAN Test Update Register Clock to Valid Output

BSCAN Test Update Register Clock to High-Impedance

BSCAN Test Update Register High-Impedance to Valid Output

T

btcl

T

btvo

T

btcpsu

T

btuov

PARAMETER

Data Captured

T

bth

T

btcp

T

btco

Valid Data Valid Data

T

btcph

T

btuco

Valid Data Valid Data

MIN

100

50

50

25

25

50

—

—

25

25

—

—

—

T

btoz

T

btuoz

MAX UNITS

— ns

—

—

25 ns

25

—

65

65

Table 2-0010/81080V

ns

ns

ns—

ns

ns

ns—

ns

ns

ns65

10

Page 11

Specifications ispLSI 81080V

Absolute Maximum Ratings

1,2

Supply Voltage Vcc.................................. -0.5 to +5.4V

Input Voltage Applied............................... -0.5 to +5.6V

Tri-Stated Output Voltage Applied........... -0.5 to +5.6V

Storage Temperature................................ -65 to 150°C

Case Temp. with Power Applied .............. -55 to 125°C

Max. Junction Temp. (TJ) with Power Applied ... 150°C

1. Stresses above those listed under the “Absolute Maximum Ratings” may cause permanent damage to the device. Functional

operation of the device at these or at any other conditions above those indicated in the operational sections of this specification

is not implied (while programming, follow the programming specifications).

2. Compliance with the Thermal Management section of the Lattice Semiconductor Data Book or CD-ROM is a requirement.

DC Recommended Operating Condition

SYMBOL

VCC

VCCIO

Supply Voltage Commercial T = 0°C to 70°C3.03.6V

I/O Supply Voltage

PARAMETER

MIN. MAX. UNITS

A

2.3 3.6 V

Table 2-0005/81080V

Capacitance (TA=25°C,f=1.0 MHz)

SYMBOL

C

1

C

2

C

3

I/O Capacitance

Clock Capacitance

Global Input Capacitance

PARAMETER

Erase/Reprogram Specification

PARAMETER MINIMUM MAXIMUM UNITS

Erase/Reprogram Cycles

UNITSTYPICAL TEST CONDITIONS

10

10

10

10000 – Cycles

pf V = 3.3V, V = 2.0V

pf V = 3.3V, V = 2.0V

pf V = 3.3V, V = 2.0V

CC I/O

CC CK

CC G

Table 2-0006/81080V

Table 2-0008/81080V

11

Page 12

Switching Test Conditions

R

1

V

CCIO

R

2

C

L

*

Device

Output

Test

Point

*

CL includes Test Fixture and Probe Capacitance.

0213A/81080V

Specifications ispLSI 81080V

Input Pulse Levels

Input Rise and Fall Time

Input Timing Reference Levels

Ouput Timing Reference Levels

Output Load

3-state levels are measured 0.5V from

steady-state active level.

GND to VCCIO

≤ 1.5 ns 10% to 90%

1.5V

1.5V

See Figure 9

min

Table 2-0003/81080V

Output Load Conditions (See Figure 9)

3.3V 2.5V

TEST CONDITION R1 R2

A 316Ω 348Ω

Active High

B

Active Low

Active High to Z

at V -0.5V

C

D Slow Slew

OH

Active Low to Z

at V +0.5V

OL

348Ω

∞

316Ω∞

348Ω

∞

316Ω∞

∞∞

R1 R2

511Ω 475Ω

475Ω

∞

511Ω∞

475Ω

∞

511Ω∞

∞∞

Table 2-0004A/81080V

CL

35pF

35pF

35pF

5pF

5pF

35pF

DC Electrical Characteristics for 3.3V Range

Over Recommended Operating Conditions

SYMBOL

VCCIO

VIL

VIH

VOL

VOH

I/O Supply Voltage 3.0 3.6 V

Input Low Voltage -0.3 0.8 V

Input High Voltage

Output Low Voltage

Output High Voltage

PARAMETER

= 0°C to + 70°C

T

A

I = 8 mA

OL

I = -4 mA

OH

Figure 9. Test Load

CONDITION MIN. MAX. UNITS

2.0

–

2.4

5.25

0.4

–

Table 2-0007/81080V

V

V

V

DC Electrical Characteristics for 2.5V Range

SYMBOL

V

V

V

V

V

CCIO

IL

IH

OL

OH

I/O Supply Voltage 2.3 2.7 V

Input Low Voltage

Input High Voltage

Output Low Voltage

Output High Voltage

PARAMETER

Over Recommended Operating Conditions

CONDITION MIN. MAX. UNITS

T

= 0°C to + 70°C

A

V

V

V

V

, VIN=VIH or VIL, IOL= 100µA

CCIO=min

, VIN=VIH or VIL, IOL= 2mA

CCIO=min

, VIN=VIH or VIL, IOH= -100µA

CCIO=min

, VIN=VIH or VIL, IOH= -2mA

CCIO=min

12

-0.3 0.7 V

1.7 5.25 V

– 0.2 V

– 0.7 V

2.1 – V

1.7 – V

Table 2-0007B/81080V

Page 13

DC Electrical Characteristics

Over Recommended Operating Conditions

SYMBOL

IIL

IIH

IPU

IBHL

IBHH

IBHLO

IBHLH

IBHT

ICC

Input or I/O Low Leakage Current 0V ≤ V ≤ V (Max.)

Input or I/O High Leakage Current

4

I/O Active Pullup Current

Bus Hold Low Sustaining Current

Bus Hold High Sustaining Current

Bus Hold Low Overdrive Current

Bus Hold High Overdrive Current

Bus Hold Trip Points

1,3,5

Operating Power Supply Current

1. Measured at a frequency of 1MHz using 54 20-bit counters.

2. Typical values are at V

3. Maximum I

varies widely with specific device configuration and operating frequency.

CC

4. Pullup is capable of pulling minimum voltage of V

5. Unused inputs held at GND.

PARAMETER

= 3.3V and T

CC

= 25°C.

A

IN IL

(V

-0.2)V ≤ VIN ≤ V

CCIO

V

≤ VIN ≤ 5.25V

CCIO

0V

≤ VIN ≤ V

VIN = V

IL(max)

VIN = V

IH(min)

0V ≤ VIN ≤ V

0V ≤ VIN ≤ V

V = 0.5V, V = 3.0V

IL IH

f = 1 MHz

TOGGLE

under no-load conditions.

OH

Specifications ispLSI 81080V

CONDITION MIN. TYP. MAX. UNITS

–

CCIO

–

–

IL

40

-40

CCIO

CCIO

High Speed Mode

Low Power Mode

–

–

V

IL

–

–

2

–

-10

–

–

––

10

50

-250

–

–

–

550

–

-550

–

V

590

250 –

Table 2-0007C/81080V

–

–

IH

–

µA

µA

µA

µA

µA

µA

µA

µA

V

mA

13

Page 14

Specifications ispLSI 81080V

External Switching Characteristics

1

Over Recommended Operating Conditions

PARA-

METER

t

pd1

t

pd2

f

max

t

suq

t

hq

t

coq

t

sug

t

hg

t

cog

t

su1

t

h1

t

co1

t

suceq

t

hceq

t

suceg

t

hceg

t

goe

t

rglb

t

rio

t

rw

t

wh

t

wl

1. Unless noted otherwise, all parameters use PTSA and CLK0.

2. Refer to Timing Model in this data sheet for further details.

3. Standard 20-bit counter with local feedback.

4. Refer to Switching Test Conditions section.

TEST

COND.

A

A

—

—

—

A

—

—

A

—

—

A

—

—

—

—

B/C

—

—

—

—

—

2

4

Prop Delay, BFM Input to Same BFM Output, 4 PT Bypass — 10.0 ns

1

Prop Delay, Global Input to Global Output — ns

2

Clk Frequency, Local Feedback, Same GLB 90.0 —

3

I/O Cell Reg, Data Setup Time, Quadrant I/O Clock 8.0 — ns

4

I/O Cell Reg, Data Hold Time, Quadrant I/O Clock — ns

5

I/O Cell Reg, Quadrant Clock to Output Delay 6.0 ns

6

I/O Cell Reg, Data Setup Time, Global Clock — ns

7

I/O Cell Reg, Data Hold Time, Global Clock — ns

8

I/O Cell Reg, Global Clock to Output Delay 7.5 ns

9

GLB Reg Setup, BFM Input to Same BFM GLB, 4 PT Bypass — ns

10

GLB Reg Hold Time, BFM Input to Same BFM GLB 0.0 ns

11

GLB Reg, Global Clock to Same BFM Output Delay 10.0 ns

12

I/O Cell Reg, CLKEN Setup Time, Quadrant I/O Clock 6.5 ns

13

I/O Cell Reg, CLKEN Hold Time, Quadrant I/O Clock 0.0 ns

14

GLB Reg, CLKEN Setup Time, Global Clock 4.5 ns

15

GLB Reg, CLKEN Hold Time, Global Clock 0.0 ns

16

Global Output Enable/Disable Delay — ns

17

Global Reset/Preset Time, GLB Reg — 15.0 ns

18

Global Reset/Preset Time, I/O Cell Reg — 10.0 ns

19

Global Reset/Preset Pulse Duration 6.5 — ns

20

Global or Quadrant Clock Pulse, High Duration 6.0 — ns

21

Global or Quadrant Clock Pulse, Low Duration 6.0 — ns

22

DESCRIPTION#

-125

MIN. MAX.

— 8.5

—

3

125.0

0.0

3.5

0.0

4.5

—

5.0

—

4.0

—

—

—

6.0

—

—

—

0.0

—

8.0

—

5.5

—

0.0

—

3.5

—

0.0

7.0

—

— 14.0

— 8.5

5.0 —

4.0 —

4.0 —

-90 -60

MIN. MAX.

16.014.5

0.0

—

6.0

0.0

—

7.0

—

—

—

—

—

—

10.0

UNITS

MAX.

MIN.

— 15.0

—

24.0

60.0 — MHz

12.0 —

—

0.0

9.0

—

—

9.0

0.0

10.0

—

11.0

—

—

—

0.0

—

15.0

—

9.5

—

0.0

—

6.5

—

0.0

15.0

—

— 22.0

— 15.0

9.5 —

9.0 —

9.0 —

Table 2-0030/81080V

14

Page 15

Internal Timing Parameters

Over Recommended Operating Conditions

Specifications ispLSI 81080V

PARAMETER #

I/O Cell Delay

2

DESCRIPTION

-125 -90 -60

MIN MAX MIN MAX MIN MAX UNITS

tidcom 23 Input Pad and Input Buffer, Combinatorial Input – 0.3 – 0.4 – 0.6 ns

tidreg 24 Input Pad and Input Buffer, Registered Input – 6.4 – 7.6 – 11.2 ns

tobp 25 Output Register/Latch Bypass to Output Buffer – 0.0 – 0.0 – 0.0 ns

tibp 26 Input Register/Latch Bypass to BFM Routing or GRP – 0.4 – 0.5 – 0.8 ns

tiolat 27 I/O Cell Latch, Transparent Mode – 2.0 – 2.4 – 3.6 ns

tioco 28 I/O Cell Register/Latch, Clk/Gate to Output – 0.5 – 1.2 – 1.6 ns

tiosu 29 I/O Cell Register/Latch, Setup Time 0.5 – 2.4 – 3.9 – ns

tioh 30 I/O Cell Register/Latch, Hold Time 2.5 – 3.2 – 4.7 – ns

tiorst 31 I/O Cell Register/Latch, Reset or Set Time – 1.5 – 1.7 – 2.5 ns

tiosuce 32 I/O C e l l R e g i ster/Latch, Setup Time for Clk Enable 0.9 – 1.0 – 1.2 – ns

tiohce 33 I / O c e l l R e g i ster/Latch, Hold Time for Clk Enable 4.6 – 4.6 – 6.9 – ns

todreg 34 I/O Cell Output Buffer Delay, Registered Output – 1.6 – 1.9 – 2.9 ns

todcom 35 I / O C e l l O utput Buffer Delay, Combinatorial Output – 1.6 – 1.9 – 2.9 ns

todz 36 Output Driver Disable Time – 1.4 – 1.7 – 2.6 ns

tslf 37 Slew Rate Adder, Fast Slew Rate – 0.0 – 0.0 – 0.0 ns

tsls 38 Slew Rate Adder, Slow Slew Rate – 6.2 – 7.3 – 10.9 ns

GLB / Macrocell Delay

tandhs 39 AND Array, High Speed Mode – 2.6 – 2.9 – 4.2 ns

tandlp 40 AND Array, Low Power Mode – 6.5 – 7.7 – 11.5 ns

t1pt 41 Single Product Term Bypass – 1.9 – 2.2 – 3.4 ns

t4ptcom 42 Four Product Term Bypass, Combinatorial Macrocell – 0.5 – 0.6 – 0.9 ns

t4ptreg 43 Four Product Term Bypass, Registered Macrocell – 1.4 – 1.7 – 2.2 ns

tptsa 44 Product Term Sharing Array – 2.4 – 2.7 – 4.1 ns

tmbp 45 Macrocell Register/Latch Bypass – 0.0 – 0.0 – 0.0 ns

tmlat 46 Macrocell Latch, Transparent Mode – 4.6 – 5.5 – 8.2 ns

tmco 47 Macrocell Register/Latch, Clk/Gate to Output – 0.2 – 0.8 – 0.9 ns

tmsu 48 Macrocell Register/Latch, Setup Time 2.7 – 4.5 – 6.9 – ns

tmh 49 Macrocell Register/Latch, Hold Time 1.0 – 1.2 – 1.1 – ns

tmrst 50 Macrocell Register/Latch, Reset or Set Time – 1.4 – 1.5 – 1.6 ns

tmsuce 51 Macrocell Register/Latch, Setup Time for Clk Enable 1.0 – 1.3 – 1.7 – ns

tmhce 52 Macrocell Register/Latch, Hold Time for Clk Enable 2.3 – 2.6 – 3.9 – ns

tfloc 54 Local Feedback to AND Array – 0.1 – 0.1 – 0.6 ns

tpck 55 Single Product Term, Clk 1.3 1.3 1.6 1.6 2.5 2.5 ns

tpcken 56 Single Product Term, Clk Enable – 1.7 – 2.0 – 3.1 ns

tsck 57 Shared Product Term, Clk 1.7 1.9 2.0 2.3 3.1 3.5 ns

tscken 58 Shared Product Term, Clk Enable 1.7 1.9 2.0 2.3 3.1 3.5 ns

tprst 59 Single Product Term, Reset or Set Delay – 1.5 – 1.7 – 2.6 ns

trdir 60 Macrocell Register, Direct Input from GRP – 7.2 – 8.4 – 12.7 ns

15

Page 16

Specifications ispLSI 81080V

Internal Timing Parameters

Over Recommended Operating Conditions

PARAMETER #

BFM / Global Routing Pool Delay

2

DESCRIPTION

tbfmi 61 BFM Routing Delay, Signal from I/O Cell 0.4 1.0 0.6 1.3 0.8 1.9 ns

tgrpi 62 GRP Delay, Signal from I/O Cell – 1.8 – 1.9 – 2.8 ns

tgrpiz 63 Internal Tristate Bus Enable/Disable, I/O Cell Buffer – 4.3 – 4.9 – 7.3 ns

tbfmm 64 BFM Routing Delay, Signal from Macrocell – 0.6 – 0.7 – 1.1 ns

tgrpm 65 GRP Delay, Signal from Macrocell – 2.6 – 3.0 – 4.5 ns

tgrpmz 66

Internal Tristate Bus Enable/Disable, Macrocell Buffer

tbfmg 67 BFM Routing Delay, Signal from GRP – 3.3 – 3.3 – 4.9 ns

tgrpb 68 GRP Delay, Signal from BFM Routing – 1.3 – 1.5 – 2.3 ns

tbcom 69 BFM Routing to I/O Cell, Combinatorial Path – 1.5 – 1.7 – 2.6 ns

tbreg 70 BFM Routing to I/O Cell, Registered Path – 2.3 – 2.6 – 4.0 ns

tgcom 71 GRP to I/O Cell, Combinatorial Path – 0.8 – 0.8 – 1.2 ns

tgreg 72 GRP to I/O Cell, Registered Path – 1.6 – 1.7 – 2.6 ns

I/O Control Bus Delay

tpiock 73 Product Term as I/O Cell Register Clock – 4.1 – 4.7 – 7.2 ns

tpiocken 74 Product Term as I/O Cell Register Clock Enable – 4.6 – 5.3 – 8.1 ns

tpoe 75 Product Term as Output Buffer Enable/Disable – 5.6 – 6.5 – 9.9 ns

tpiorst 76

Product Term as I/O Cell Register Reset or Set Delay

tpioz 77 Internal Tristate Bus Control Signal for I/O Cell Buffer – 3.3 – 3.8 – 5.8 ns

Global Control Delay

tgck 78 Global Macrocell Register Clk 3.9 4.1 4.3 4.9 6.6 7.5 ns

tgcken 79 Global Macrocell Register Clk Enable 6.4 6.4 7.5 7.5 11.4 11.4 ns

tgiock 80 Global I/O Register Clk 3.4 3.9 4.0 4.4 6.1 6.5 ns

tgiocken 81 Global I/O Register Clk Enable 6.5 6.5 7.5 7.5 11.4 11.4 ns

tqck 82 Quadrant I/O Register Clk 1.9 1.9 2.0 2.9 3.1 4.5 ns

tgoe 83 Global Output Enable – 5.6 – 8.3 – 12.4 ns

ttoe 84 Test Output Enable – 8.5 – 10.1 – 15.2 ns

tgmrst 85 Global GLB Register Reset – 7.6 – 7.8 – 11.8 ns

tgiorst 86 Global I/O Cell Register Reset – 5.4 – 6.4 – 9.6 ns

1. Internal Timing Parameters are not tested and are for reference only.

2. Refer to Timing Model in this data sheet for further details.

-125 -90 -60

MIN MAX MIN MAX MIN MAX UNITS

– 3.6 – 4.3 – 6.5 ns

– 4.3 – 5.0 – 7.6 ns

16

Page 17

ispLSI 81080V Timing Model

Input Buffer and I/O Cell Register

I/O register delays

t

I/O

pad

Input

pad

Input buffer

delays

t#23,

idcom

t#24,

idreg

Global control

delay

#78,

t

gck

#79,

t

gcken

t

#80,

giock

#81,

t

giocken

t

#82,

qck

#83,

t

goe

t#84,

toe

#85,

t

gmrst

#86,

t

giorst

#25,

#26,

#27,

#28,

#29,

#30,

#32,

#33,

obp

t

ibp

t

iolat

t

ioco

t

iosu

t

ioh

t#31,

iorst

t

iosuce

t

iohce

Output path

Input path

BFM Routing Pool

GLB/

Macrocell

AND array

#39,

t

andhs

#40,

t

andlp

t#61,

bfmi

t#64,

bfmm

Local feedback

t#54,

floc

PTSA

#41,

t

1pt

t

#42,

4ptcom

t

#43,

4ptreg

t

#44,

ptsa

PT Mcell controls

t

#55,

pck

#56,

t

pcken

#57,

t

sck

t

#58,

scken

t

#59,

prst

PT I/O control bus

t

#73,

piock

t

#74,

piocken

t

#75,

poe

#76,

t

piorst

t

#77,

pioz

Specifications ispLSI 81080V

t

t#67,

bfmg

Macrocell

Register

t

#45,

#46,

t

#47,

t

t

#48,

t

#49,

#50,

t

t

#51,

t

#52,

mbp

mlat

mco

msu

mh

mrst

msuce

mbce

#69,

#70,

#71,

#72,

bcom

t

breg

t

gcom

t

greg

Bus direct

Output routing

t#60,

rdir

z

Global

Routing

Plane

#62,

#63,

#65,

#66,

#68,

t

grpi

t

grpiz

t

grpm

t

grpmz

t

grpb

8840V_Model.eps

Output

delays

#34,

#35,

#36,

buffer

t

odreg

t

odcom

t

odz

slew rate

#37,

#38,

Output

adders

I/O

pad

t

slf

t

sls

17

Page 18

Specifications ispLSI 81080V

Example Timing Calculations

tpd1 = (BFM Input Path Delay) + (GLB Delay) + (Output Path Delay)

= (

tidcom + tibp + tbfmi max) + (tandhs + t4ptcom + tmbp) + (tbfmm + tbcom + tobp + todcom + tslf)

= (#23 + #26 + #61) + (#39 + #42 + #45) + (#64 + #69 + #25 + #35 + #37)

= (0.3 + 0.4 + 1.0) + (2.6 + 0.5 + 0.0) + (0.6 + 1.5 + 0.0 + 1.6 + 0.0)

= 8.5 ns

tpd (within BFM)

= (BFM Delay) + (GLB Delay)

= (

tbfmm) + (tandhs + t4ptcom + tmbp)

= (#64) + (#39 + #42 + #45)

= (0.6) + (2.6 + 0.5 + 0.0)

= 3.7 ns

tpd (between BFMs)

= (GRP Delay) + (BFM Delay) + (GLB Delay)

= (

tgrpm) + (tbfmg) + (tandhs + t4ptcom + tmbp)

= (#65) + (#67) + (#39 + #42 + #45)

= (2.6) + (3.3) + (2.6 + 0.5 + 0.0)

= 9.0 ns

BFM I/O to internal tri-state Enable/Disable

= (BFM Input Path Delay) + (GLB Delay, 1PT) + (Tri-state Control Delay)

= (

tidcom + tibp + tbfmi max) + (tandhs + t1pt + tmbp) + (tgrpmz)

= (#23 + #26 + #61) + (#39 + #41 + #45) + (#66)

= (0.3 + 0.4 + 1.0) + (2.6 + 1.9 + 0.0) + (3.6)

= 9.8 ns

tsu1 = (BFM Input Path Delay) + (GLB Setup Time) - (Min. Global Clock Delay)

= (

tidcom + tibp + tbfmi max) + (tandhs + t4ptreg + tmsu) – (tgck min)

= (#23 + #26 + #61) + (#39 + #43 + #48) – (#78)

= (0.3 + 0.4 + 1.0) + (2.6 + 1.4 + 2.7) – (3.9)

= 4.5 ns

1/

Fmax = (Global Clk to MC Output) + (Local Feedback) + (GLB Setup Time)

= (

tmco) + (tfloc) + (tandhs + tptsa + tmsu)

= (#47) + (#54) + (#39 + #44 + #48)

= (0.2) + (0.1) + (2.6 + 2.4 + 2.7)

= 8.0 ns

Fmax = 125 MHz

Note: Calculations are based upon timing specifications for the ispLSI 81080V-125L

18

Page 19

Power Consumption

Specifications ispLSI 81080V

Power consumption in the ispLSI 81080V device depends on two primary factors: the speed at which the

device is operating and the number of product terms

used. The product terms have a fuse-selectable speed/

power tradeoff setting. Each group of four product terms

has a single speed/power tradeoff control fuse that acts

on the complete group of four. The fast “high-speed”

Figure 10. Typical Device Power Consumption vs fmax

1300

1200

1100

1000

900

800

700

CC (mA)

I

600

500

400

setting operates product terms at their normal full power

consumption. For portions of the logic that can tolerate

longer propagation delays, selecting the slower “lowpower” setting will significantly reduce the power

dissipation for these product terms. Figure 10 shows the

relationship between power and operating speed.

ispLSI 81080V

Turbo

Non-Turbo

300

200

0 102030405060708090100

f

max (MHz)

Notes: Configuration of 54 20-bit counters

Typical current at 3.3V, 25¡ C

ICC can be estimated for the ispLSI 81080V using the following equation:

ICC = 45.0 + (# of Turbo PTs * 0.25) + (# of Non-Turbo PTs * 0.11) + (# of Macrocells Used * Fmax * AF * .043)

# of Turbo PTs = Number of Turbo Product Terms Used in Design

# of Non-Turbo PTs = Number of Non-Turbo Product Terms Used in Design

fmax = Maximum Operating Frequency

AF (Activity Factor) =

Note: An Activity Factor of 1.0 means all macrocell registers toggle at fmax. An Activity Factor of 0.5 means the

average macrocell register toggles at half of fmax.

The I

on average exists. These values are for estimates only. Since the value of I

and the program in the device, the actual I

estimate is based on typical conditions (VCC = 3.3V, room temperature) and an assumption of two GLB loads

CC

Average Macrocell Toggle Frequency

Fmax

should be verified.

CC

is sensitive to operating conditions

CC

110 120 130

0127/81080V

19

Page 20

Specifications ispLSI 81080V

Signal Descriptions

Signal Name Description

CLK0, CLK1, Dedicated clock input for the GLB registers only. These clock inputs are connected to one of the clock

CLK2 inputs of all GLB registers in the device.

CLKEN Dedicated clock enable input for the GLB registers only. This input is available as a clock enable for

each GLB register in the device. Use of the clock enable input eliminates the need for the user to gate

the clock to the register.

GND Ground (GND)

GOE0, GOE1, Global Output Enable inputs.

GOE2, GOE3

SET/RESET Dedicated reset/preset pin connected to ALL registers in the device, GLB registers and I/O registers.

Each register can independently choose to be reset or preset when this signal goes active. The active

polarity is user-selectable.

IOCLKEN Dedicated clock enable input for the I/O registers only. This input is available as a clock enable input for

all I/O registers in the device. Use of the clock enable input eliminates the need for the user to tie the

clock to the I/O register.

I/O Input/Output – These are the general purpose I/O used by the logic array.

EPEN Embedded Port Enable Pin – When this pin is high, the port is enabled. When this pin is low, the

state machine is held at reset asynchronously and TCK, TMS and TDI are ignored.

TMS Input – This signal is the Test Mode Select input signal.

QIOCLK0, Dedicated clock inputs for the I/O registers only. These clock inputs are connected to the I/O registers

QIOCLK1, on the same side of the device only, they are not connected to all of the I/O registers. Use of these

QIOCLK2, quadrant I/O clocks gives the fastest tco from the device.

QIOCLK3

TCK Input – This signal is the Test Clock input signal.

TDI Input – This signal is the Test Data input signal.

TDO Output – This signal is the Test Data Out Output Signal.

TOE Test Output Enable. Tristates all I/O pins when a logic low is driven.

VCC Vcc

VCCIO Power supply for the output drivers. The internal logic of the device is connected to VCC which is

always 3.3V. The output drivers are connected to VCCIO which can be equal to VCC or 2.5V. This

allows the output drivers to be powered from 2.5V, for example, to interface directly with another 2.5V

device.

1

NC

1. NC pins are not to be connected to any active signals, VCC or GND.

No connect.

20

Page 21

Signal Locations

Specifications ispLSI 81080V

Signal Name

QIOCLK0, QIOCLK1,

QIOCLK2, QIOCLK3

CLK0, CLK1, CLK2

CLKEN

IOCLKEN

EPEN

TCK

TDI

TDO

TMS

GOE0, GOE1,

GOE2, GOE3

TOE

SET/RESET

VCC

VCCIO

GND

1

NC

1. NC pins are not to be connected to any active signals, VCC or GND.

Y8, M20, C8, N2

Y9, P18, D8

V9

B9

C17

A4

U5

C4

W4

Y10, M19, C9, N1

L3

P3

D9, D10, D11, D12, J4, J17, K4, K17, L4, L17,

M4, M17, U9, U10, U11, U12

A7, A8, A20, B16, C5, C12, E4, G20, H4, M1,

N17, U2, U20, V2, V6, W7, W8, W16, W19, Y13

D4, D16, D17, J9, J10, J11, J12, K9, K10, K11,

K12, L9, L10, L11, L12, M9, M10, M11, M12,

U4, U17

A9, V17, W9

272-Ball BGA

492-Ball BGA

AE14, P22, A15, N3

AC15, R24, B15

AB17

E16

B26

A2

AF1

B3

AC4

AF15, P23, D16, N5

L5

P2

E9, E12, E15, E18, F5, F10, F17, F22, G5, G22,

K5, K22, L22, M5, N22, P5, R22, T5, U5, U22,

Y5, Y22, AA5, AA10, AA17, AA22, AB9, AB12,

AB15, AB18

E8, E13, E19, E20, F7, F8, F20, J6, J21, K3,

L24, N1, P24, T3, U25, V6, Y23, AA7, AA8,

AA20, AB8, AB14, AB19, AB20

E5, E11, E14, E22, F6, F21, L11, L12, L13, L14,

L15, L16, M11, M12, M13, M14, M15, M16, N11,

N12, N13, N14, N15, N16, P11, P12, P13, P14,

P15, P16, R11, R12, R13, R14, R15, R16, T11,

T12, T13, T14, T15, T16, AA6, AA21, AB5,

AB13, AB16, AB22

A16, C2, E17, G21, Y21, AA9, AB4, AB10,

AD15, AF25

21

Page 22

I/O Pin Locations (272-Ball BGA Package)

Specifications ispLSI 81080V

Signal BGA

I/O G0 <0> V4

I/O G0 <1> Y3

I/O G0 <2> Y2

I/O G0 <3> W3

I/O G0 <4> Y1

I/O G0 <5> W2

I/O G0 <6> W1

I/O G0 <7> V3

I/O G0 <8> V1

I/O G0 <9> U3

I/O G0 <10> R4

I/O G0 <11> T4

I/O G0 <12> U19

I/O G0 <13> R17

I/O G0 <14> V20

I/O G0 <15> V19

I/O G0 <16> U18

I/O G0 <17> V18

I/O G0 <18> T17

I/O G0 <19> W20

I/O G0 <20> Y20

I/O G0 <21> Y19

I/O G0 <22> W18

I/O G0 <23> Y18

I/O G2 <0> U1

I/O G2 <1> T3

I/O G2 <2> T2

I/O G2 <3> T1

I/O G2 <4> R3

I/O G2 <5> R2

I/O G2 <6> R1

I/O G2 <7> P4

I/O G2 <8> P2

I/O G2 <9> N4

I/O G2 <10> N3

I/O G2 <11> P1

I/O G2 <12> N18

I/O G2 <13> N19

I/O G2 <14> N20

Signal BGA

I/O G2 <15> P19

I/O G2 <16> P17

I/O G2 <17> P20

I/O G2 <18> R20

I/O G2 <19> R19

I/O G2 <20> R18

I/O G2 <21> T20

I/O G2 <22> T19

I/O G2 <23> T18

I/O G3 <0> H2

I/O G3 <1> H1

I/O G3 <2> J3

I/O G3 <3> J2

I/O G3 <4> J1

I/O G3 <5> K3

I/O G3 <6> K2

I/O G3 <7> K1

I/O G3 <8> L2

I/O G3 <9> L1

I/O G3 <10> M2

I/O G3 <11> M3

I/O G3 <12> M18

I/O G3 <13> L20

I/O G3 <14> L19

I/O G3 <15> L18

I/O G3 <16> K20

I/O G3 <17> K19

I/O G3 <18> K18

I/O G3 <19> J20

I/O G3 <20> H20

I/O G3 <21> J19

I/O G3 <22> H19

I/O G3 <23> J18

I/O G4 <0> G2

I/O G4 <1> G1

I/O G4 <2> H3

I/O G4 <3> G3

I/O G4 <4> G4

I/O G4 <5> F3

Signal BGA Signal BGA

I/O G4 <6> F1

I/O G4 <7> F2

I/O G4 <8> F4

I/O G4 <9> E1

I/O G4 <10> E2

I/O G4 <11> E3

I/O G4 <12> D20

I/O G4 <13> F17

I/O G4 <14> E19

I/O G4 <15> G17

I/O G4 <16> G18

I/O G4 <17> F18

I/O G4 <18> E20

I/O G4 <19> F19

I/O G4 <20> H17

I/O G4 <21> F20

I/O G4 <22> H18

I/O G4 <23> G19

I/O G5 <0> A3

I/O G5 <1> B2

I/O G5 <2> B3

I/O G5 <3> A2

I/O G5 <4> A1

I/O G5 <5> B1

I/O G5 <6> D3

I/O G5 <7> D2

I/O G5 <8> C3

I/O G5 <9> C2

I/O G5 <10> D1

I/O G5 <11> C1

I/O G5 <12> D19

I/O G5 <13> E18

I/O G5 <14> C20

I/O G5 <15> B20

I/O G5 <16> A19

I/O G5 <17> C19

I/O G5 <18> D18

I/O G5 <19> B19

I/O G5 <20> C18

I/O G5 <21> E17

I/O G5 <22> B18

I/O G5 <23> A18

I/O B1 <0> Y4

I/O B1 <1> V5

I/O B1 <2> W5

I/O B1 <3> Y5

I/O B1 <4> U6

I/O B1 <5> U7

I/O B1 <6> W6

I/O B1 <7> V7

I/O B1 <8> Y6

I/O B1 <9> Y7

I/O B1 <10> U8

I/O B1 <11> V8

I/O B1 <12> B8

I/O B1 <13> C7

I/O B1 <14> D7

I/O B1 <15> B7

I/O B1 <16> B6

I/O B1 <17> C6

I/O B1 <18> A6

I/O B1 <19> D6

I/O B1 <20> B5

I/O B1 <21> A5

I/O B1 <22> D5

I/O B1 <23> B4

I/O B5 <0> V10

I/O B5 <1> W10

I/O B5 <2> Y11

I/O B5 <3> W11

I/O B5 <4> V11

I/O B5 <5> Y12

I/O B5 <6> W12

I/O B5 <7> V12

I/O B5 <8> W13

I/O B5 <9> U13

I/O B5 <10> V13

I/O B5 <11> Y14

Signal BGA

I/O B5 <12> B14

I/O B5 <13> D13

I/O B5 <14> B13

I/O B5 <15> A13

I/O B5 <16> A12

I/O B5 <17> B12

I/O B5 <18> B11

I/O B5 <19> A11

I/O B5 <20> C11

I/O B5 <21> B10

I/O B5 <22> A10

I/O B5 <23> C10

I/O B7 <0> W14

I/O B7 <1> V14

I/O B7 <2> U14

I/O B7 <3> Y15

I/O B7 <4> W15

I/O B7 <5> V15

I/O B7 <6> U15

I/O B7 <7> Y16

I/O B7 <8> V16

I/O B7 <9> U16

I/O B7 <10> W17

I/O B7 <11> Y17

I/O B7 <12> B17

I/O B7 <13> A17

I/O B7 <14> C16

I/O B7 <15> D15

I/O B7 <16> C15

I/O B7 <17> A16

I/O B7 <18> B15

I/O B7 <19> D14

I/O B7 <20> C14

I/O B7 <21> A15

I/O B7 <22> A14

I/O B7 <23> C13

22

Page 23

Specifications ispLSI 81080V

I/O Pin Locations (492-Ball BGA Package)

Signal BGA Signal BGA Signal BGA Signal BGA Signal BGA

I/O G0 <0> AA4

I/O G0 <1> AA3

I/O G0 <2> AA2

I/O G0 <3> AA1

I/O G0 <4> Y4

I/O G0 <5> Y3

I/O G0 <6> Y2

I/O G0 <7> Y1

I/O G0 <8> W4

I/O G0 <9> W3

I/O G0 <10> W2

I/O G0 <11> U6

I/O G0 <12> U21

I/O G0 <13> Y26

I/O G0 <14> Y25

I/O G0 <15> Y24

I/O G0 <16> V21

I/O G0 <17> AA26

I/O G0 <18> AA25

I/O G0 <19> AA24

I/O G0 <20> AA23

I/O G0 <21> AB26

I/O G0 <22> AB25

I/O G0 <23> AB24

I/O G1 <0> T2

I/O G1 <1> W5

I/O G1 <2> U1

I/O G1 <3> U2

I/O G1 <4> U3

I/O G1 <5> U4

I/O G1 <6> V1

I/O G1 <7> V5

I/O G1 <8> V2

I/O G1 <9> V3

I/O G1 <10> V4

I/O G1 <11> W1

I/O G1 <12> W23

I/O G1 <13> W24

I/O G1 <14> W25

I/O G1 <15> W26

I/O G1 <16> V22

I/O G1 <17> V23

I/O G1 <18> V24

I/O G1 <19> V25

I/O G1 <20> V26

I/O G1 <21> W22

I/O G1 <22> U23

I/O G1 <23> U24

I/O G2 <0> T4

I/O G2 <1> T1

I/O G2 <2> W6

I/O G2 <3> R2

I/O G2 <4> R1

I/O G2 <5> R3

I/O G2 <6> R4

I/O G2 <7> R5

I/O G2 <8> P1

I/O G2 <9> P3

I/O G2 <10> P4

I/O G2 <11> N4

I/O G2 <12> P26

I/O G2 <13> P25

I/O G2 <14> R23

I/O G2 <15> T22

I/O G2 <16> R26

I/O G2 <17> R25

I/O G2 <18> T26

I/O G2 <19> T23

I/O G2 <20> W21

I/O G2 <21> T24

I/O G2 <22> T25

I/O G2 <23> U26

I/O G3 <0> K2

I/O G3 <1> K1

I/O G3 <2> L2

I/O G3 <3> H6

I/O G3 <4> L3

I/O G3 <5> L4

I/O G3 <6> L1

I/O G3 <7> M2

I/O G3 <8> M1

I/O G3 <9> M3

I/O G3 <10> M4

I/O G3 <11> N2

I/O G3 <12> N23

I/O G3 <13> N24

I/O G3 <14> N26

I/O G3 <15> N25

I/O G3 <16> M22

I/O G3 <17> M23

I/O G3 <18> M24

I/O G3 <19> M26

I/O G3 <20> H21

I/O G3 <21> M25

I/O G3 <22> L26

I/O G3 <23> L23

I/O G4 <0> K4

I/O G4 <1> H5

I/O G4 <2> J1

I/O G4 <3> J2

I/O G4 <4> J3

I/O G4 <5> J4

I/O G4 <6> H1

I/O G4 <7> J5

I/O G4 <8> H2

I/O G4 <9> H3

I/O G4 <10> H4

I/O G4 <11> K6

I/O G4 <12> H26

I/O G4 <13> J23

I/O G4 <14> J24

I/O G4 <15> J25

I/O G4 <16> J22

I/O G4 <17> J26

I/O G4 <18> K23

I/O G4 <19> K24

I/O G4 <20> K25

I/O G4 <21> H22

I/O G4 <22> K26

I/O G4 <23> L25

I/O G5 <0> E4

I/O G5 <1> E3

I/O G5 <2> E2

I/O G5 <3> E1

I/O G5 <4> F4

I/O G5 <5> F3

I/O G5 <6> F2

I/O G5 <7> F1

I/O G5 <8> G4

I/O G5 <9> G3

I/O G5 <10> G2

I/O G5 <11> G1

I/O G5 <12> K21

I/O G5 <13> H25

I/O G5 <14> H24

I/O G5 <15> H23

I/O G5 <16> G26

I/O G5 <17> G25

I/O G5 <18> G24

I/O G5 <19> G23

I/O G5 <20> F26

I/O G5 <21> F25

I/O G5 <22> F24

I/O G5 <23> F23

I/O B0 <0> Y6

I/O B0 <1> AB1

I/O B0 <2> AB2

I/O B0 <3> AB3

I/O B0 <4> AC1

I/O B0 <5> AC2

I/O B0 <6> AC3

I/O B0 <7> AD1

I/O B0 <8> AD2

I/O B0 <9> AD3

I/O B0 <10> AE1

I/O B0 <11> AB6

I/O B0 <12> E6

I/O B0 <13> A1

I/O B0 <14> C3

I/O B0 <15> D4

I/O B0 <16> G6

I/O B0 <17> F9

I/O B0 <18> B2

I/O B0 <19> B1

I/O B0 <20> D3

I/O B0 <21> C1

I/O B0 <22> D2

I/O B0 <23> D1

I/O B1 <0> AE2

I/O B1 <1> AF2

I/O B1 <2> AE3

I/O B1 <3> AF3

I/O B1 <4> AD4

I/O B1 <5> AE4

I/O B1 <6> AF4

I/O B1 <7> AC5

I/O B1 <8> AD5

I/O B1 <9> AE5

I/O B1 <10> AB7

I/O B1 <11> AF5

I/O B1 <12> B6

I/O B1 <13> E7

I/O B1 <14> C6

I/O B1 <15> D6

I/O B1 <16> A5

I/O B1 <17> B5

I/O B1 <18> C5

I/O B1 <19> D5

I/O B1 <20> A4

I/O B1 <21> B4

I/O B1 <22> C4

I/O B1 <23> A3

I/O B2 <0> AC6

I/O B2 <1> AD6

I/O B2 <2> AE6

I/O B2 <3> AF6

I/O B2 <4> AC7

I/O B2 <5> AD7

I/O B2 <6> AE7

I/O B2 <7> AF7

I/O B2 <8> AC8

I/O B2 <9> AD8

I/O B2 <10> AE8

I/O B2 <11> AF8

I/O B2 <12> B9

I/O B2 <13> C9

I/O B2 <14> D9

I/O B2 <15> A8

I/O B2 <16> B8

I/O B2 <17> C8

I/O B2 <18> D8

I/O B2 <19> A7

I/O B2 <20> B7

I/O B2 <21> C7

I/O B2 <22> D7

I/O B2 <23> A6

I/O B3 <0> AC9

I/O B3 <1> AD9

I/O B3 <2> AE9

I/O B3 <3> AF9

I/O B3 <4> AC10

I/O B3 <5> AD10

I/O B3 <6> AE10

I/O B3 <7> AF10

I/O B3 <8> AE11

I/O B3 <9> AD11

I/O B3 <10> AB11

I/O B3 <11> AC11

I/O B3 <12> A12

I/O B3 <13> E10

I/O B3 <14> B12

I/O B3 <15> A11

I/O B3 <16> D11

I/O B3 <17> C11

I/O B3 <18> B11

I/O B3 <19> A10

I/O B3 <20> B10

I/O B3 <21> C10

I/O B3 <22> D10

I/O B3 <23> A9

I/O B4 <0> AF11

I/O B4 <1> AE12

I/O B4 <2> AF12

I/O B4 <3> AD12

I/O B4 <4> AC12

I/O B4 <5> AE13

I/O B4 <6> AF13

I/O B4 <7> AD13

I/O B4 <8> AC13

I/O B4 <9> AC14

I/O B4 <10> AD14

I/O B4 <11> AF14

I/O B4 <12> C15

I/O B4 <13> D15

I/O B4 <14> B14

I/O B4 <15> A14

I/O B4 <16> C14

I/O B4 <17> D14

I/O B4 <18> D13

I/O B4 <19> C13

I/O B4 <20> A13

I/O B4 <21> B13

I/O B4 <22> D12

I/O B4 <23> C12

I/O B5 <0> AE15

I/O B5 <1> AF16

I/O B5 <2> AC16

I/O B5 <3> AD16

I/O B5 <4> AE16

I/O B5 <5> AF17

I/O B5 <6> AE17

I/O B5 <7> AD17

I/O B5 <8> AC17

I/O B5 <9> AF18

I/O B5 <10> AE18

I/O B5 <11> AD18

I/O B5 <12> B19

I/O B5 <13> A19

I/O B5 <14> D18

I/O B5 <15> C18

I/O B5 <16> B18

I/O B5 <17> A18

I/O B5 <18> D17

I/O B5 <19> C17

I/O B5 <20> B17

I/O B5 <21> A17

I/O B5 <22> B16

I/O B5 <23> C16

I/O B6 <0> AC18

I/O B6 <1> AF19

I/O B6 <2> AE19

I/O B6 <3> AA19

I/O B6 <4> AD19

I/O B6 <5> AC19

I/O B6 <6> AF20

I/O B6 <7> AE20

I/O B6 <8> AD20

I/O B6 <9> AC20

I/O B6 <10> AF21

I/O B6 <11> AE21

I/O B6 <12> A22

I/O B6 <13> D21

I/O B6 <14> C21

I/O B6 <15> B21

I/O B6 <16> A21

I/O B6 <17> D20

I/O B6 <18> C20

I/O B6 <19> B20

I/O B6 <20> A20

I/O B6 <21> F19

I/O B6 <22> D19

I/O B6 <23> C19

I/O B7 <0> AD21

I/O B7 <1> AC21

I/O B7 <2> AF22

I/O B7 <3> AE22

I/O B7 <4> AD22

I/O B7 <5> AC22

I/O B7 <6> AF23

I/O B7 <7> AE23

I/O B7 <8> AD23

I/O B7 <9> AF24

I/O B7 <10> AE24

I/O B7 <11> AD24

I/O B7 <12> A26

I/O B7 <13> D23

I/O B7 <14> B25

I/O B7 <15> A25

I/O B7 <16> B24

I/O B7 <17> A24

I/O B7 <18> C23

I/O B7 <19> B23

I/O B7 <20> A23

I/O B7 <21> D22

I/O B7 <22> C22

I/O B7 <23> B22

I/O B8 <0> AB21

I/O B8 <1> AF26

I/O B8 <2> AE25

I/O B8 <3> AC23

I/O B8 <4> AE26

I/O B8 <5> AD25

I/O B8 <6> AC24

I/O B8 <7> AD26

I/O B8 <8> AB23

I/O B8 <9> AC25

I/O B8 <10> AC26

I/O B8 <11> AA18

I/O B8 <12> E26

I/O B8 <13> E25

I/O B8 <14> E24

I/O B8 <15> E23

I/O B8 <16> D26

I/O B8 <17> D25

I/O B8 <18> D24

I/O B8 <19> C26

I/O B8 <20> C25

I/O B8 <21> C24

I/O B8 <22> E21

I/O B8 <23> F18

23

Page 24

Specifications ispLSI 81080V

Signal Configuration

ispLSI 81080V 272-Ball BGA Signal Diagram

2019181716151413121110987654321

I/O G5

I/O G5

I/O B7

I/O B7

I/O B7

I/O B7

I/O B5

I/O B5

I/O B5

VCCIO

A

B B

C C

D

E

F

G

H

J

K

L L

M M

N

P P

R R

T

U U

V

W W

Y

<16>

<23>

<13>

<17>

<21>

<22>

<15>

<16>

I/O B5

I/O B5

I/O B5

VCCIO

I/O B7

<14>

GNDGND

I/O B7

<9>

I/O B7

<8>

I/O B7

<7>

I/O B7

<18>

I/O B7

<16>

I/O B7

<15>

I/O B7

<6>

I/O B7

<5>

I/O B7

<4>

I/O B7

<3>

<17>

<14>

<12>

I/O B7

I/O B7

<20>

I/O B7

<19>

VCCIO VCCIO

<23>

I/O B5

<13>

ispLSI 81080V

Bottom View

GND GND GND GND

GND GND GND GND

GND GND GND GND

GND GND GND GND

I/O B7

I/O B5

<2>

<9>

I/O B7

I/O B5

<10>

I/O B5

<8>

VCCIO

I/O B5

<7>

I/O B5

<6>

I/O B5

<5>

<1>

I/O B7

<0>

I/O B5

<11>

I/O G5

<19>

<15>

I/O G5

I/O G5

<14>

<17>

I/O G5

I/O G4

<12>

<12>

I/O G4

I/O G4

<18>

<14>

I/O G4

I/O G4

<21>

<19>

I/O G4

VCCIO

<23>

I/O G3

I/O G3

<20>

<22>

I/O G3

I/O G3

<19>

<21>

I/O G3

I/O G3

<16>

<17>

I/O G3

I/O G3

<13>

<14>

GOE

QIOCLK

1

1

I/O G2

I/O G2

<14>

<13>

I/O G2

I/O G2

<17>

<15>

I/O G2

I/O G2

<18>

<19>

I/O G2

I/O G2

<21>

<22>

I/O G0

VCCIO VCCIO

<12>

I/O G0

I/O G0

<14>

<15>

I/O G0

<19>

I/O G0

I/O G0

<20>

<21>

<22>

I/O G5

<20>

I/O G5

<18>

I/O G5

<13>

I/O G4

<17>

I/O G4

<16>

I/O G4

<22>

I/O G3

<23>

I/O G3

<18>

I/O G3

<15>

I/O G3

<12>

I/O G2

<12>

CLK 1

I/O G2

<20>

I/O G2

<23>

I/O G0

<16>

I/O G0

<17>

I/O G0

<22>

I/O G0

<23>

<12>

EPEN

I/O G5

<21>

I/O G4

<13>

I/O G4

<15>

I/O G4

<20>

VCC

VCC

VCC

VCC

VCCIO

I/O G2

<16>

I/O G0

<13>

I/O G0

<18>

GND

NC

I/O B7

<10>

I/O B7

<11>

1

I/O B7

I/O G5

I/O G5

<19>

I/O B5

<18>

I/O B5

<20>

I/O B5

<4>

I/O B5

<3>

I/O B5

<2>

I/O B5

<22>

I/O B5

<21>

I/O B5

<23>

I/O B5

<0>

I/O B5

<1>

GOE

1

NC

VCCIO

I/O B1

IOCLKEN

<12>

GOE

QIOCLK

2

2

CLK 2

VCCVCCVCCVCC

I/O B1

<10>

I/O B1

<11>

1

VCCIOVCCIO VCCIO VCCIO

NC

QIOCLK

CLK 0

0

0

VCCIO

I/O B1

<15>

I/O B1

<13>

I/O B1

<14>

I/O B1

<5>

I/O B1

<7>

I/O B1

<9>

I/O B1

<18>

I/O B1

<16>

I/O B1

<17>

I/O B1

<19>

I/O B1

<4>

I/O B1

<6>

I/O B1

<8>

I/O B1

<21>

I/O B1

<20>

I/O B1

<22>

TDI

I/O B1

<1>

I/O B1

<2>

I/O B1

<3>

I/O G5

TCK

I/O G5

I/O B1

<23>

I/O G5

TDO

I/O G5

GND

I/O G4

VCCIO

<11>

I/O G4

I/O G4

<8>

I/O G4

I/O G4

<4>

I/O G4

VCCIO

I/O G3

VCC

I/O G3

VCC

VCC TOE

I/O G3

VCC

<11>

I/O G2

I/O G2

<9>

<10>

SET/

I/O G2

RESET

<7>

I/O G2

I/O G0

<10>

I/O G2

I/O G0

<11>

I/O G0

GNDVCC VCC VCC VCC

I/O G0

I/O G0

<0>

I/O G0

TMS

I/O G0

I/O B1

<0>

<0>

<2>

<8>

<6>

<5>

<3>

<2>

<2>

<5>

<4>

<1>

<9>

<7>

<3>

<1>

I/O G5

<3>

I/O G5

<1>

I/O G5

<9>

I/O G5

<7>

I/O G4

<10>

I/O G4

<7>

I/O G4

<0>

I/O G3

<0>

I/O G3

<3>

I/O G3

<6>

I/O G3

<8>

I/O G3

<10>

QIOCLK

3

I/O G2

<8>

I/O G2

<5>

I/O G2

<2>

VCCIOCLKEN VCCIO

I/O G0

<5>

I/O G0

<2>

I/O G5

<4>

I/O G5

<5>

I/O G5

<11>

I/O G5

<10>

I/O G4

<9>

I/O G4

<6>

I/O G4

<1>

I/O G3

<1>

I/O G3

<4>

I/O G3

<7>

I/O G3

<9>

VCCIO

GOE

3

I/O G2

<11>

I/O G2

<6>

I/O G2

<3>

I/O G2

<0>

I/O G0

<8>

I/O G0

<6>

I/O G0

<4>

A

D

E

F

G

H

J

K

N

T

V

Y

2019181716151413121110987654321

1. NCs are not to be connected to any active signals, Vcc or GND.

Note: Ball A1 indicator dot on top side of package.

24

272 BGA/81080v.eps

Page 25

Signal Configuration

ispLSI 81080V 492-Ball BGA Signal Diagram

I/O B7

I/O B7

I/O B7

I/O B7

I/O B6

I/O B6

I/O B6

I/O B5

I/O B5

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

AF

<12>

<15>

<17>

I/O B7

I/O B7

<16>

<14>

I/O B8

I/O B8

<19>

I/O B8

<16>

I/O B8

<12>

I/O G5

<20>

I/O G5

<16>

I/O G4

<12>

I/O G4

<17>

I/O G4

<22>

I/O G3

<22>

I/O G3

<19>

I/O G3

<14>

I/O G2

<12>

I/O G2

<16>

I/O G2

<18>

I/O G2

<23>

I/O G1

<20>

I/O G1

<15>

I/O G0

<13>

I/O G0

<17>

I/O G0

<21>

I/O B8

<10>

I/O B8

<7>

I/O B8

<4>

I/O B8

<1>

I/O B8

<20>

<21>

I/O B8

I/O B8

<17>

<18>

I/O B8

I/O B8

<13>

<14>

I/O G5

I/O G5

<21>

<22>

I/O G5

I/O G5

<17>

<18>

I/O G5

I/O G5

<13>

<14>

I/O G4

I/O G4

<15>

<14>

I/O G4

I/O G4

<20>

<19>

I/O G4

VCCIO

<23>

I/O G3

I/O G3

<21>

<18>

I/O G3

I/O G3

<15>

<13>

I/O G2

VCCIO GOE 1

<13>

I/O G2

<17>

I/O G2

I/O G2

<22>

<21>

I/O G1

VCCIO VCC

<23>

I/O G1

I/O G1

<19>

<18>

I/O G1

I/O G1

<14>

<13>

I/O G0

I/O G0

<14>

<15>

I/O G0

I/O G0

<18>

<19>

I/O G0

I/O G0

<22>

<23>

I/O B8

I/O B8

<9>

<6>

I/O B7

I/O B8

<11>

<5>

I/O B7

I/O B8

<10>

<2>

I/O B7

1

NC

<9>

<20>

<12>

<16>

<20>

<13>

I/O B5

I/O B6

I/O B6

I/O B7

I/O B7

<19>

I/O B7

<18>

I/O B7

<13>

I/O B8

<15>

I/O G5

<23>

I/O G5

<19>

I/O G5

<15>

I/O G4

<13>

I/O G4

<18>

I/O G3

<23>

I/O G3

<17>

I/O G3

<12>

I/O G2

<14>

I/O G2

<19>

I/O G1

<22>

I/O G1

<17>

I/O G1

<12>

VCCIO VCC NC

I/O G0

<20>

I/O G8

<8>

I/O B8

<3>

I/O B7

<8>

I/O B7

<7>

I/O B7

<6>

<15>

<23>

I/O B6

I/O B7

<14>

<22>

I/O B7

I/O B6

<21>

<13>

I/O B8

GND VCCVCCVCC

<22>

VCC

VCC NC

I/O G4

I/O G3

<21>

<20>

I/O G4

VCCIO

<16>

I/O G5

VCC

<12>

VCC

I/O G3

<16>

VCC

QIOCLK

1

VCCCLK 1

I/O G2

<15>

I/O G0

<12>

I/O G1

I/O G0

<16>

<16>

I/O G1

I/O G2

<21>

<20>

VCC VCCIO VCCGND

I/O B8

GND GNDGND

<0>

I/O B7

I/O B7

<5>

<1>

I/O B7

I/O B7

<0>

<4>

I/O B7

I/O B6

<3>

<11>

I/O B6

I/O B7

<10>

<2>

<12>

<19>

I/O B6

I/O B6

<23>

<18>

I/O B6

I/O B6

<17>

<22>

I/O B6

<21>

1

1

I/O B6

<3>

I/O B6

I/O B6

<9>

<5>

I/O B6

I/O B6

<4>

<8>

I/O B6

I/O B6

<7>

<2>

I/O B6

I/O B6

<1>

<6>

I/O B5

<17>

<21>

I/O B5

I/O B5

<20>

<16>

I/O B5

I/O B5

<19>

<15>

I/O B5

I/O B5

<14>

I/O B8

<23>

GOE 2

<18>

1

NC

IOCLKEN

VCC VCC VCCIO

ispLSI 81080V

I/O B8

<11>

CLKEN

I/O B6

I/O B5

<0>

<8>

I/O B5

I/O B5

<7>

<11>

I/O B5

I/O B5

<10>

<6>

I/O B5

I/O B5

<5>

<9>

Specifications ispLSI 81080V

I/O B4

I/O B4

I/O B3

1

QIOCLK

NC

2

<15>

<20>

I/O B4

CLK2EPEN

I/O B4

<12>

I/O B4

<13>

I/O B4

<14>

I/O B4

<16>

I/O B4

<17>

<21>

I/O B4

<19>

I/O B4

<18>

I/O B5

<22>

I/O B5

<23>

GND GND GND GND GND GND

GND GND GND GND GND GND

GND GND GND GND GND GND

GND GND GND GND GND GND

GND GND GND GND GND GND

GND GND GND GND GND GND

Bottom View

I/O B5

<2>

I/O B5

<3>

I/O B5

<4>

I/O B5

<1>

CLK 0

NC

I/O B5

<0>

GOE 0

1

I/O B4

<9>

I/O B4

<10>

QIOCLK

0

I/O B4

<11>

I/O B4

<8>

I/O B4

<7>

I/O B4

<5>

I/O B4

<6>

<12>

I/O B3

<14>

I/O B4

<23>

I/O B4

<22>

VCCVCCVCC VCCIOVCCIOVCCIO

I/O B4

<4>

I/O B4

<3>

I/O B4

<1>

I/O B4

<2>

I/O B3

<15>

I/O B3

<18>

I/O B3

<17>

I/O B3

<16>

I/O B3

<10>

I/O B3

<11>

I/O B3

I/O B3

I/O B4

<9>

<8>

<0>

I/O B3

<19>

I/O B3

<20>

I/O B3

<21>

I/O B3

<22>

I/O B3

<13>

I/O B3

<4>

I/O B3

<5>

I/O B3

<6>

I/O B3

<7>

1

234567891011121314151617181920212223242526

I/O B3

I/O B2

I/O B2

I/O B2

I/O B1

I/O B1

<23>

<15>

<19>

<23>

<16>

I/O B1

I/O B1

I/O B2

I/O B2

I/O B2

<12>

I/O B2

<13>

I/O B2

<14>

I/O R0

<17>

1

I/O B3

<0>

I/O B3

<1>

I/O B3

<2>

I/O B3

<3>

<20>

<16>

I/O B2

I/O B2

<21>

<17>

I/O B2

I/O B2

<18>

<22>

I/O B1

<13>

VCCIO VCCGNDGND VCCIO

1

I/O B1

<10>

I/O B2

I/O B2

<8>

<4>

I/O B2

I/O B2

<5>

<9>

I/O B2

I/O B2

<10>

<6>

I/O B2

I/O B2

<7>

<11>

<12>

I/O B1

<14>

I/O B1

<15>

I/O B0

<12>

I/O B0

<16>

I/O G3

<3>

VCCIO

I/O G4

<11>

I/O G0

<11>

VCCIO

I/O G2

<2>

I/O B0

<0>

GND

I/O B0

<11>

I/O B2

<0>

I/O B2

<1>

I/O B2

<2>

I/O B2

<3>

<17>

I/O B1

<18>

I/O B1

<19>

GNDVCCIOVCCIOVCCIOVCCIO VCCGNDGND

VCC

I/O G4

<1>

I/O G4

<7>

VCC

TOE

VCC

GOE 3

VCC

I/O G2

<7>

VCC

VCC

I/O G1

<7>

I/O G1

<1>

VCC

VCCVCCIOVCCIOVCC NC

GNDVCCIOVCCNC

I/O B1

<7>

I/O B1

<8>

I/O B1

<9>

I/O B1

<11>

<20>

I/O B1

<21>

I/O B1

<22>

I/O B0

<15>

I/O G5

<0>

I/O G5

<4>

I/O G5

<8>

I/O G4

<10>

I/O G4

<5>

I/O G4

<0>

I/O G3

<5>

I/O G3

<10>

I/O G2

<11>

I/O G2

<10>

I/O G2

<6>

I/O G2

<0>

I/O G1

<5>

I/O G1

<10>

I/O G0

<8>

I/O G0

<4>

I/O G0

<0>

NC

TMS

I/O B1

<4>

I/O B1

<5>

I/O B1

<6>

1

I/O B1

<23>

TDO

I/O B0

<14>

I/O B0

<20>

I/O G5

<1>

I/O G5

<5>

I/O G5

<9>

I/O G4

<9>

I/O G4

<4>

VCCIO

I/O G3

<4>

I/O G3

<9>

QIOCLK

I/O G2

<9>

I/O G2

<5>

VCCIO

I/O G1

<4>

I/O G1

<9>

I/O G0

<9>

I/O G0

<5>

I/O G0

<1>

I/O B0

<3>

I/O B0

<6>

I/O B0

<9>

I/O B1

<2>

I/O B1

<3>

I/O B0

TCK

I/O B0

<18>

1