Datasheet IDT74FCT16374ETPF, IDT74FCT16374ETPA, IDT74FCT16374ETE, IDT74FCT16374CTPVB, IDT74FCT16374CTPV Datasheet (Integrated Device Technology)

...

Integrated Device Technology, Inc.

FAST CMOS 16-BIT

REGISTER (3-STATE)

IDT54/74FCT16374T/AT/CT/ET

IDT54/74FCT162374T/AT/CT/ET

FEATURES:

• Common features:

– 0.5 MICRON CMOS Technology

– High-speed, low-power CMOS replacement for

ABT functions

– Typical t

– Low input and output leakage ≤1µA (max.)

– ESD > 2000V per MIL-STD-883, Method 3015;

> 200V using machine model (C = 200pF, R = 0)

– Packages include 25 mil pitch SSOP, 19.6 mil pitch

TSSOP, 15.7 mil pitch TVSOP and 25 mil pitch Cerpack

– Extended commercial range of -40°C to +85°C

–VCC = 5V ±10%

• Features for FCT16374T/AT/CT/ET:

– High drive outputs (-32mA IOH, 64mA IOL)

– Power off disable outputs permit “live insertion”

– Typical VOLP (Output Ground Bounce) < 1.0V at

VCC = 5V, TA = 25°C

• Features for FCT162374T/AT/CT/ET:

– Balanced Output Drivers: ±24mA (commercial),

– Reduced system switching noise

– Typical VOLP (Output Ground Bounce) < 0.6V at

VCC = 5V,TA = 25°C

SK(o) (Output Skew) < 250ps

±16mA (military)

DESCRIPTION:

The FCT16374T/AT/CT/ET and FCT162374T/AT/CT/ET

16-bit edge-triggered D-type registers are built using advanced dual metal CMOS technology. These high-speed,

low-power registers are ideal for use as buffer registers for

data synchronization and storage. The Output Enable (xOE)

and clock (xCLK) controls are organized to operate each

device as two 8-bit registers or one 16-bit register with

common clock. Flow-through organization of signal pins simplifies layout. All inputs are designed with hysteresis for

improved noise margin.

The FCT16374T/AT/CT/ET are ideally suited for driving

high-capacitance loads and low-impedance backplanes. The

output buffers are designed with power off disable capability

to allow "live insertion" of boards when used as backplane

drivers.

The FCT162374T/AT/CT/ET have balanced output drive

with current limiting resistors. This offers low ground bounce,

minimal undershoot, and controlled output fall times– reducing the need for external series terminating resistors. The

FCT162374T/AT/CT/ET are plug-in replacements for the

FCT16374T/AT/CT/ET and ABT16374 for on-board bus interface applications.

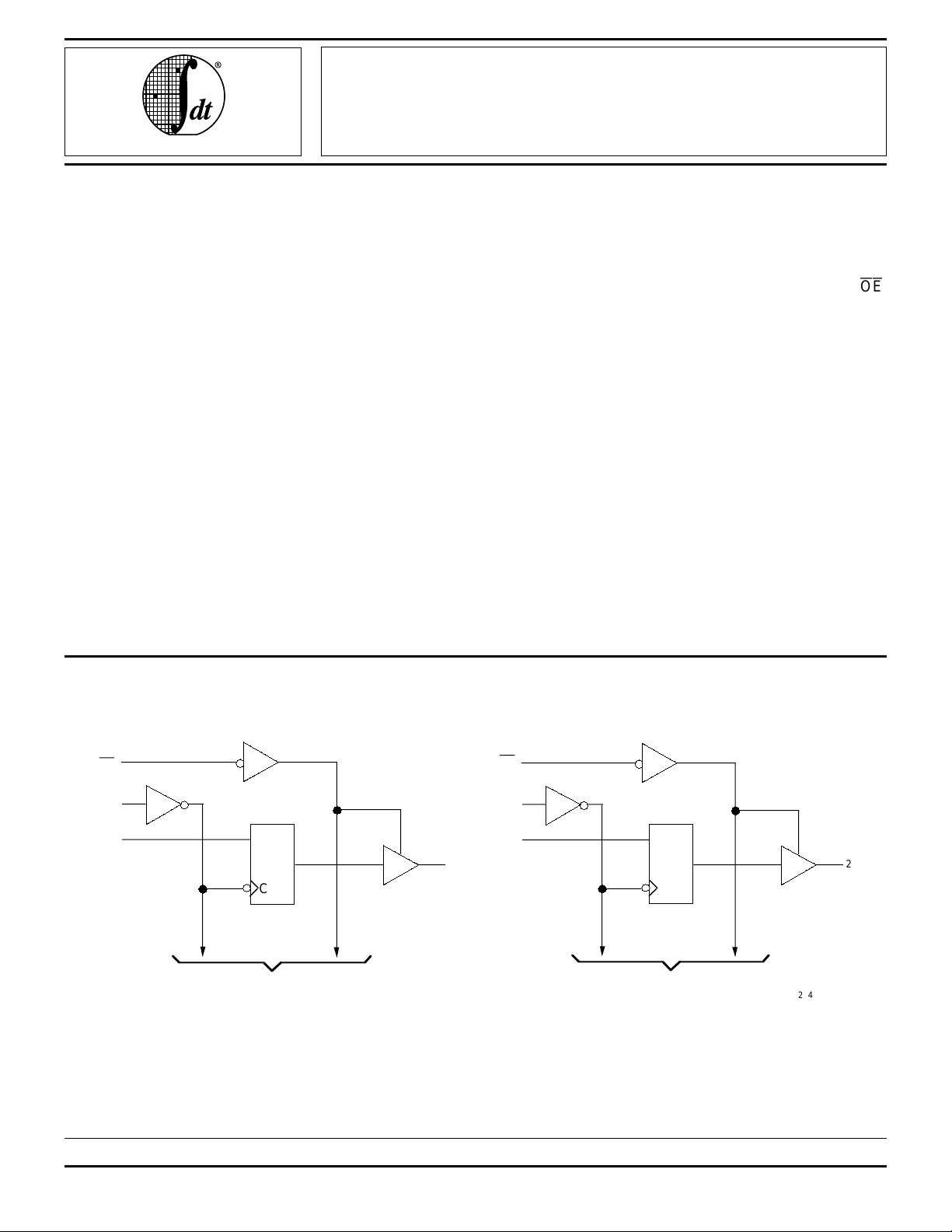

FUNCTIONAL BLOCK DIAGRAM

OE

1O1

2

2

CLK

2D1

TO 7 OTHER CHANNELS

1

D

2O1

C

2542 drw 01

OE

1

1

CLK

1D1

TO 7 OTHER CHANNELS

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

D

C

2542 drw 01

MILITARY AND COMMERCIAL TEMPERATURE RANGES AUGUST 1996

1996 Integrated Device Technology, Inc. 5.8 DSC-4230/9

IDT54/74FCT16374T/AT/CT/ET, 162374T/AT/CT/ET

FAST CMOS 16-BIT REGISTER (3-STATE) MILITARY AND COMMERCIAL TEMPERATURE RANGES

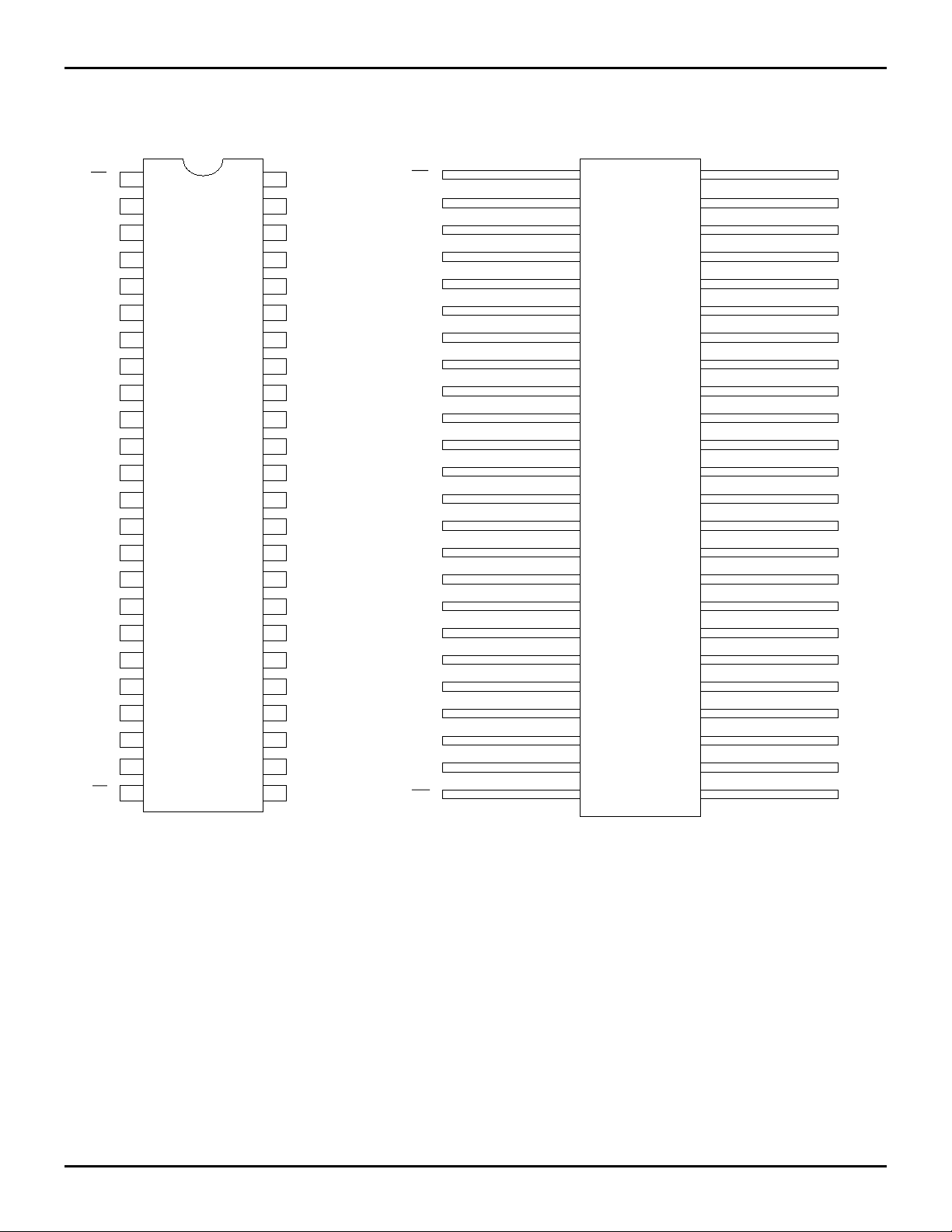

PIN CONFIGURATIONS

OE

1

1O1

1O2

GND

1O3

O4

1

VCC

O5

1

1

O6

GND

O7

1

1

O8

2

O1

2O2

GND

O3

2

2

O4

V

CC

O5

2

2

O6

GND

O7

2

2

O8

2OE

1

2

3

4

5

6

7

8

9

10

11

SO48-1

12

SO48-2

SO48-3

13

14

15

16

17

18

19

20

21

22

23

24

SSOP/

TSSOP/TVSOP

TOP VIEW

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

1CLK

1D1

1

D2

GND

1D3

1

D4

VCC

1

D5

1

D6

GND

D7

1

1

D8

2

D1

2

D2

GND

D3

2

2

D4

VCC

2

D5

2

D6

GND

D7

2

2

D8

2

CLK

2542 drw 03

OE

1

1O1

1O2

GND

1O3

1

O4

VCC

1

O5

1

O6

GND

1

O7

1

O8

2

O1

2O2

GND

2

O3

2

O4

CC

V

2

O5

O6

2

GND

2

O7

2

O8

2OE

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

CERPACK

TOP VIEW

E48-1

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

2542 drw 04

1CLK

1D1

1

D2

GND

1D3

1

D4

VCC

1

D5

1

D6

GND

1

D7

1

D8

2

D1

2

D2

GND

2

D3

2

D4

VCC

2

D5

D6

2

GND

2

D7

2

D8

2

CLK

5.8 2

IDT54/74FCT16374T/AT/CT/ET, 162374T/AT/CT/ET

FAST CMOS 16-BIT REGISTER (3-STATE) MILITARY AND COMMERCIAL TEMPERATURE RANGES

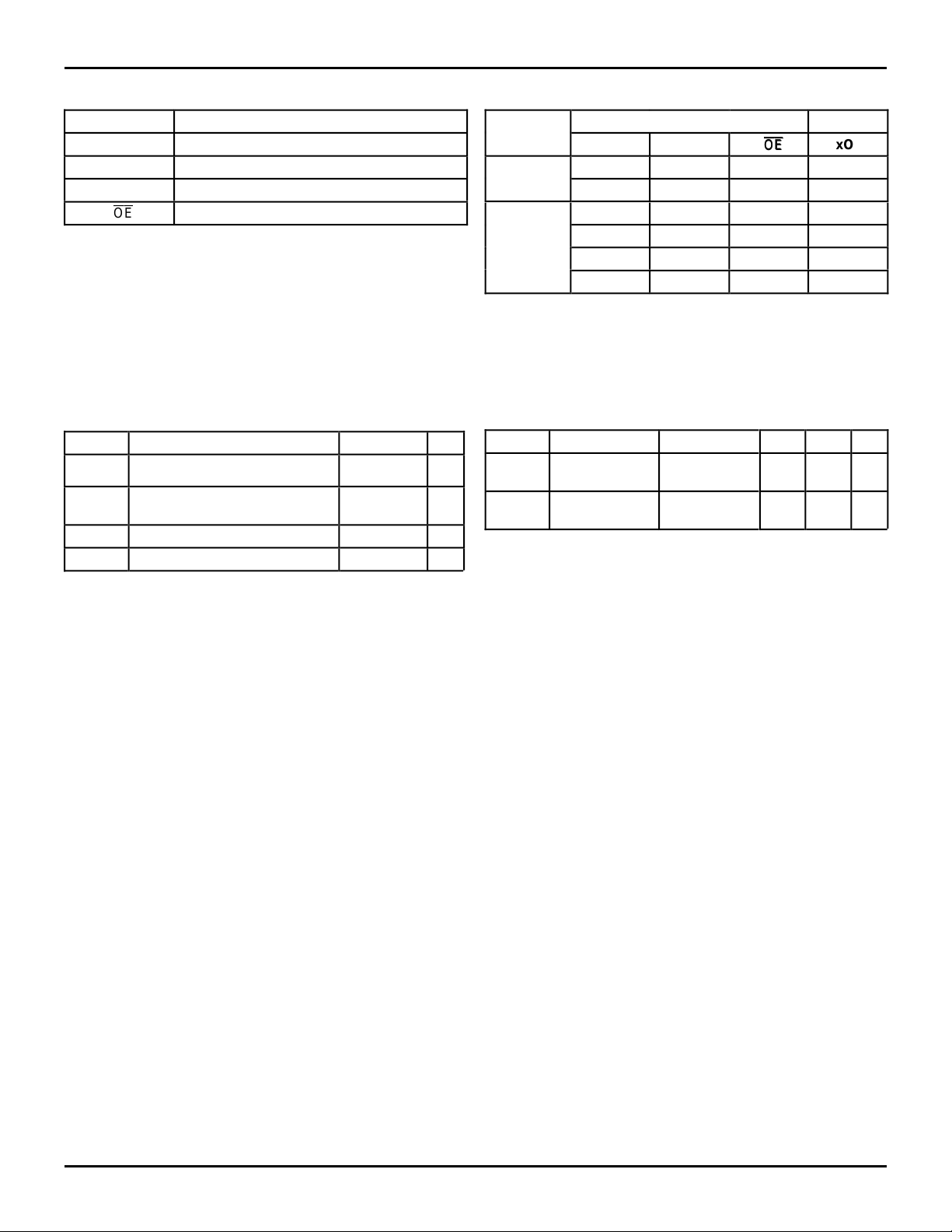

PIN DESCRIPTION

Pin Names Description

xDx Data Inputs

xCLK Clock Inputs

xOx 3-State Outputs.

x

OE

ABSOLUTE MAXIMUM RATINGS

Symbol Description Max. Unit

(2)

V

TERM

(3)

V

TERM

T

STG

I

OUT

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or any other conditions

above those indicated in the operational sections of this specification is

not implied. Exposure to absolute maximum rating conditions for

extended periods may affect reliability.

2. All device terminals except FCT162XXXT Output and I/O terminals.

3. Output and I/O terminals for FCT162XXXT.

3-State Output Enable Input (Active LOW)

2542 tbl 01

(1)

Terminal Voltage with Respect to

GND

Terminal Voltage with Respect to

GND

–0.5 to +7.0 V

–0.5 to

V

CC

+0.5

V

Storage Temperature –65 to +150°C

DC Output Current –60 to +120 mA

2542 lnk 03

FUNCTION TABLE

(1)

Inputs Outputs

Function xDx xCLK x

OE

OE

xOx

Hi-Z X L H Z

XHHZ

Load L ↑ LL

Register H ↑ LH

L↑HZ

H↑HZ

NOTE:

1. H = HIGH Voltage Level

L = LOW Voltage Level

X = Don’t Care

Z = High Impedance

2542 tbl 02

↑ = LOW-to-HIGH Transition

CAPACITANCE (TA = +25°C, f = 1.0MHz)

Symbol Parameter

CIN Input

Capacitance

CI/O I/O

Capacitance

NOTE:

1. This parameter is measured at characterization but not tested.

(1)

Conditions Typ. Max. Unit

VIN = 0V 3.5 6.0 pF

VOUT = 0V 3.5 8.0 pF

2542 lnk 04

5.8 3

IDT54/74FCT16374T/AT/CT/ET, 162374T/AT/CT/ET

FAST CMOS 16-BIT REGISTER (3-STATE) MILITARY AND COMMERCIAL TEMPERATURE RANGES

DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Commercial: TA = –40°C to +85°C, VCC = 5.0V ± 10%; Military: TA = –55°C to +125°C, VCC = 5.0V ± 10%

Symbol Parameter Test Conditions

(1)

Min. Typ.

VIH Input HIGH Level Guaranteed Logic HIGH Level 2.0 — — V

VIL Input LOW Level Guaranteed Logic LOW Level — — 0.8 V

II H Input HIGH Current (Input pins)

Input HIGH Current (I/O pins)

II L Input LOW Current (Input pins)

Input LOW Current (I/O pins)

(5)

VCC = Max. VI = VCC — — ±1 µA

(5)

(5)

VI = GND — — ±1

(5)

— — ±1

— — ±1

IOZH High Impedance Output Current VCC = Max. VO = 2.7V — — ±1 µA

IOZL (3-State Output pins)

(5)

VO = 0.5V — — ±1

VIK Clamp Diode Voltage VCC = Min., IIN = –18mA — –0.7 –1.2 V

IOS Short Circuit Current VCC = Max., VO = GND

(3)

–80 –140 –225 mA

VH Input Hysteresis — — 100 — mV

ICCL

Quiescent Power Supply Current VCC = Max., VIN = GND or VCC — 5 500 µA

ICCH

ICCZ

(2)

Max. Unit

2542 lnk 05

OUTPUT DRIVE CHARACTERISTICS FOR FCT16374T

Symbol Parameter Test Conditions

IO Output Drive Current VCC = Max., VO = 2.5V

(3)

(1)

Min. Typ.

–50 —–180 mA

VOH Output HIGH Voltage VCC = Min. IOH = –3mA 2.5 3.5 — V

VIN = VIH or VIL IOH = –12mA MIL.

VOL Output LOW Voltage VCC = Min.

IN = VIH or VIL

V

IOFF Input/Output Power Off Leakage

(5)

VCC = 0V, VIN or VO ≤ 4.5V — — ±1 µA

OH = –15mA COM'L.

I

IOH = –24mA MIL.

OH = –32mA COM'L.

I

IOL = 48mA MIL.

OL = 64mA COM'L.

I

2.4 3.5 — V

2.0 3.0 — V

(4)

— 0.2 0.55 V

(2)

Max. Unit

2542 lnk 06

OUTPUT DRIVE CHARACTERISTICS FOR FCT162374T

Symbol Parameter Test Conditions

I

ODL

I

ODH

V

OH

V

OL

NOTES:

1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at Vcc = 5.0V, +25°C ambient.

3. Not more than one output should be tested at one time. Duration of the test should not exceed one second.

4. Duration of the condition can not exceed one second.

5. The test limit for this parameter is ± 5µA at T

Output LOW Current VCC = 5V, V

Output HIGH Current VCC = 5V, V

Output HIGH Voltage VCC = Min.

IN

= V

IH

V

or V

Output LOW Voltage VCC = Min.

IN

= V

IH

V

A = –55°C.

or V

IN

= V

IH or VIL, VOUT

IN

= V

IH

IL

IL

or V

IL,

(1)

(3)

= 1.5V

= 1.5V

(3)

V

OUT

IOH = –16mA MIL.

OH

= –24mA COM'L.

I

IOL = 16mA MIL.

OL

= 24mA COM'L.

I

Min. Typ.

60 115 200 mA

–60 –115 –200 mA

2.4 3.3 — V

— 0.3 0.55 V

(2)

Max. Unit

2542 lnk 07

5.8 4

IDT54/74FCT16374T/AT/CT/ET, 162374T/AT/CT/ET

FAST CMOS 16-BIT REGISTER (3-STATE) MILITARY AND COMMERCIAL TEMPERATURE RANGES

POWER SUPPLY CHARACTERISTICS

IN = VCC

V

IN = GND

V

(1)

Min. Typ.

— 0.5 1.5 mA

— 60 100 µA/

Symbol Parameter Test Conditions

∆ICC Quiescent Power Supply Current

TTL Inputs HIGH

ICCD Dynamic Power Supply

Current

(4)

VCC = Max.

IN = 3.4V

V

(3)

VCC = Max.

Outputs Open

xOE = GND

One Input Toggling

50% Duty Cycle

IC Total Power Supply Current

(6)

VCC = Max.

Outputs Open

CP = 10MHz

f

IN = VCC

V

IN = GND

V

— 0.6 1.5 mA

50% Duty Cycle

xOE = GND

fi = 5MHz

IN = 3.4V

V

IN = GND

V

— 1.1 3.0

50% Duty Cycle

One Bit Toggling

VCC = Max.

Outputs Open

CP = 10MHz

f

IN = VCC

V

IN = GND

V

— 3.0 5.5

50% Duty Cycle

xOE = GND

Sixteen Bits Toggling

IN = 3.4V

V

IN = GND

V

— 7.5 19.0

fi = 2.5MHz

50% Duty Cycle

NOTES:

1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at V

3. Per TTL driven input (V

4. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.

5. Values for these conditions are examples of the I

C = IQUIESCENT + IINPUTS + IDYNAMIC

6. I

IC = ICC + ∆ICC DHNT + ICCD (fCPNCP/2 + fiNi)

CC = Quiescent Current (ICCL, ICCH and ICCZ)

I

CC = Power Supply Current for a TTL High Input (VIN = 3.4V)

∆I

H = Duty Cycle for TTL Inputs High

D

T = Number of TTL Inputs at DH

N

ICCD = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)

f

CP = Clock Frequency for Register Devices (Zero for Non-Register Devices)

CP = Number of Clock Inputs at fCP

N

fi = Input Frequency

i = Number of Inputs at fi

N

CC = 5.0V, +25°C ambient.

IN = 3.4V). All other inputs at VCC or GND.

CC formula. These limits are guaranteed but not tested.

(2)

Max. Unit

MHz

(5)

(5)

2542 tbl 08

5.8 5

IDT54/74FCT16374T/AT/CT/ET, 162374T/AT/CT/ET

FAST CMOS 16-BIT REGISTER (3-STATE) MILITARY AND COMMERCIAL TEMPERATURE RANGES

SWITCHING CHARACTERISTICS OVER OPERATING RANGE

FCT16374T/162374T FCT16374AT/162374AT

Com'l. Mil. Com'l. Mil.

Symbol Parameter Condition

tPLH

Propagation Delay

xCLK to xOx

tPHL

tPZH

Output Enable Time 1.5 12.5 1.5 14.0 1.5 6.5 1.5 7.5 ns

CL = 50pF

R

(1)

L = 500Ω

tPZL

tPHZ

Output Disable Time 1.5 8.0 1.5 8.0 1.5 5.5 1.5 6.5 ns

tPLZ

tSU Set-up Time HIGH

or LOW, xDx to xCLK

tH Hold Time HIGH

or LOW, xDx to xCLK

tW xCLK Pulse Width

HIGH or LOW

tSK(o) Output Skew

Symbol Parameter Condition

tPLH

Propagation Delay

xCLK to xOx

tPHL

tPZH

Output Enable Time 1.5 5.5 1.5 6.2 1.5 4.4 — — ns

(3)

CL = 50pF

R

L = 500Ω

(1)

tPZL

tPHZ

Output Disable Time 1.5 5.0 1.5 5.7 1.5 3.6 — — ns

tPLZ

tSU Set-up Time HIGH

or LOW, xDx to xCLK

tH Hold Time HIGH

or LOW, xDx to xCLK

tW xCLK Pulse Width

HIGH or LOW

tSK(o) Output Skew

NOTES:

1. See test circuit and waveforms.

2. Minimum limits are guaranteed but not tested on Propagation Delays.

3. Skew between any two outputs of the same package switching in the same direction. This parameter is guaranteed by design.

4. This limit is guaranteed but not tested.

(3)

Min.

(2)

Max. Min.

(2)

Max. Min.

(2)

Max. Min.

(2)

Max. Unit

2.0 10.0 2.0 11.0 2.0 6.5 2.0 7.2 ns

2.0 — 2.0 — 2.0 — 2.0 — ns

1.5 — 1.5 — 1.5 — 1.5 — ns

7.0 — 7.0 — 5.0 — 6.0 — ns

— 0.5 — 0.5 — 0.5 — 0.5 ns

FCT16374CT/162374CT FCT16374ET/162374ET

Com'l. Mil. Com'l. Mil.

Min.

(2)

Max. Min.

(2)

Max. Min.

(2)

Max. Min.

(2)

Max. Unit

2.0 5.2 2.0 6.2 1.5 3.7 — — ns

2.0 — 2.0 — 1.5 — — — ns

1.5 — 1.5 — 0.0 — — — ns

5.0 — 6.0 — 3.0

(4)

———ns

— 0.5 — 0.5 — 0.5 — — ns

2542 tbl 09

5.8 6

IDT54/74FCT16374T/AT/CT/ET, 162374T/AT/CT/ET

FAST CMOS 16-BIT REGISTER (3-STATE) MILITARY AND COMMERCIAL TEMPERATURE RANGES

TEST CIRCUITS AND WAVEFORMS

TEST CIRCUITS FOR ALL OUTPUTS

V

CC

7.0V

SWITCH POSITION

Test

Open Drain

Disable Low

Enable Low

All Other Tests

Generator.

Pulse

Generator

500

Ω

V

V

IN

OUT

D.U.T.

50pF

500

T

R

C

L

Ω

2542 drw 05

DEFINITIONS:

L= Load capacitance: includes jig and probe capacitance.

C

T = Termination resistance: should be equal to ZOUT of the Pulse

R

SET-UP, HOLD AND RELEASE TIMES PULSE WIDTH

DATA

INPUT

TIMING

INPUT

ASYNCHRONOUS CONTROL

PRESET

CLEAR

ETC.

SYNCHRONOUS CONTROL

PRESET

CLEAR

CLOCK ENABLE

ETC.

t

t

REM

t

H

H

t

SU

t

SU

3V

1.5V

0V

3V

1.5V

0V

3V

1.5V

0V

3V

1.5V

0V

2542 drw 06

LOW-HIGH-LOW

PULSE

HIGH-LOW-HIGH

PULSE

Switch

Closed

Open

2542 lnk 10

1.5V

t

W

1.5V

2542 drw 07

SAME PHASE

INPUT TRANSITION

OUTPUT

OPPOSITE PHASE

INPUT TRANSITION

t

PLH

t

PLH

t

t

PHL

PHL

3V

1.5V

0V

OH

V

1.5V

V

OL

3V

1.5V

0V

2542 drw 08

ENABLE AND DISABLE TIMESPROPAGATION DELAY

ENABLE DISABLE

3V

CONTROL

INPUT

t

PHZ

PLZ

t

F ≤ 2.5ns; tR ≤ 2.5ns

t

PZL

OUTPUT

NORMALLY

OUTPUT

NORMALLY

HIGH

NOTES:

1. Diagram shown for input Control Enable-LOW and input Control DisableHIGH

2. Pulse Generator for All Pulses: Rate ≤ 1.0MHz; t

LOW

SWITCH

CLOSED

t

PZH

SWITCH

OPEN

3.5V

1.5V

1.5V

0V

0.3V

0.3V

1.5V

0V

3.5V

V

OL

V

OH

0V

2542 drw 09

5.8 7

IDT54/74FCT16374T/AT/CT/ET, 162374T/AT/CT/ET

FAST CMOS 16-BIT REGISTER (3-STATE) MILITARY AND COMMERCIAL TEMPERATURE RANGES

ORDERING INFORMATION

IDT XX

Temp. Range

FCT

XXXX

Device Type

X

Package

X

Process

Blank

B

PV

PA

PF

E

16374T

16374AT

16374CT

16374ET

162374T

162374AT

162374CT

162374ET

54

74

Commercial

MIL-STD-883, Class B

Shrink Small Outline Package (SO48-1)

Thin Shrink Small Outline Package (SO48-2)

Thin Very Small Outline Package (SO48-3)

CERPACK (E48-1)

Non-Inverting 16-Bit Register

–55°C to +125°C

–40°C to +85°C

2542 drw 10

5.8 8

Loading...

Loading...