Datasheet IDT7210L55C, IDT7210L55CB, IDT7210L55F, IDT7210L55FB, IDT7210L55G Datasheet (Integrated Device Technology Inc)

...Page 1

Integrated Device Technology, Inc.

16 x 16 PARALLEL CMOS

MULTIPLIER-ACCUMULATOR

IDT7210L

FEATURES:

• 16 x 16 parallel multiplier-accumulator with selectable

accumulation and subtraction

• High-speed: 20ns multiply-accumulate time

• IDT7210 features selectable accumulation, subtraction,

rounding and preloading with 35-bit result

• IDT7210 is pin and function compatible with the TRW

TDC1010J, TMC2210, Cypress CY7C510, and AMD

AM29510

• Performs subtraction and double precision addition and

multiplication

• Produced using advanced CMOS high-performance

technology

• TTL-compatible

• Available in topbraze DIP, PLCC, Flatpack and Pin Grid

Array

• Military product compliant to MIL-STD-883, Class B

• Standard Military Drawing #5962-88733 is listed on this

function

• Speeds available:

Commercial: L20/25/35/45/55/65

Military: L25/30/40/55/65/75

DESCRIPTION:

The IDT7210 is a high-speed, low-power 16 x 16-bit parallel

multiplier-accumulator that is ideally suited for real-time digital

signal processing applications. Fabricated using CMOS

silicon gate technology, this device offers a very low-power

alternative to existing bipolar and NMOS counterparts, with

only 1/7 to 1/10 the power dissipation and exceptional speed

(25ns maximum) performance.

A pin and functional replacement for TRW’s TDC1010J the

IDT7210 operates from a single 5 volt supply and is compatible

with standard TTL logic levels. The architecture of the IDT7210

is fairly straightforward, featuring individual input and output

registers with clocked D-type flip-flop, a preload capability

which enables input data to be preloaded into the output

registers, individual three-state output ports for the Extended

Product (XTP) and Most Significant Product (MSP) and a

Least Significant Product output (LSP) which is multiplexed

with the Y input.

The X

IN and YIN data input registers may be specified

through the use of the Two’s Complement input (TC) as either

a two’s complement or an unsigned magnitude, yielding a fullprecision 32-bit result that may be accumulated to a full 35-bit

result. The three output registers – Extended Product (XTP),

Most Most Significant Product (MSP) and Least Significant

Product (LSP) – are controlled by the respective TSX, TSM

and TSL input lines. The LSP output can be routed through YIN

ports.

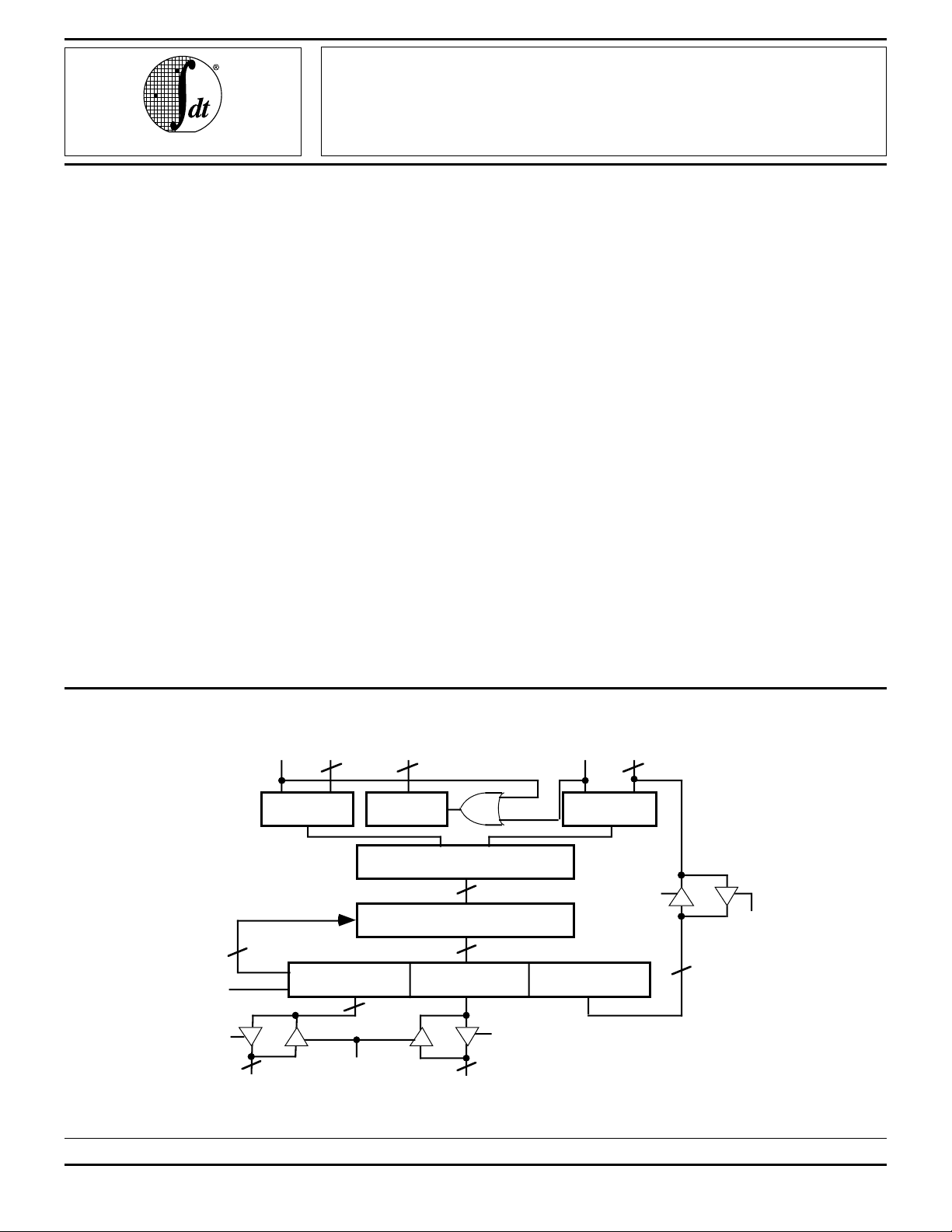

FUNCTIONAL BLOCK DIAGRAM

16

3

PREL

ACC, SUB,

416

CONTROL

REGISTER

MULTIPLIER ARRAY

ACCUMULATOR

MSP REGISTER LSP REGISTERXTP REGISTER

MSP

(P31-P16)

IDT7210

32

35

16

+

TSM

OUT

YREGISTER

IN

Y

(Y15-Y0/P15-P0)

TSL

16

2577 drw 01

PREL

1

IN

X

CLKX CLKYRND, TC

35

CLKP

TSX

3

XTPOUT

(P34-P32)

(X15-X0)

XREGISTER

+/–

MILITARY AND COMMERCIAL TEMPERATURE RANGES AUGUST 1995

1995 Integrated Device Technology, Inc. 11.2 DSC-2018/7

Page 2

IDT7210L

16 x 16 PARALLEL CMOS MULTIPLIER-ACCUMULATOR MILITARY AND COMMERCIAL TEMPERATURE RANGES

DESCRIPTION (Continued)

The Accumulate input (ACC) enables the device to perform

either a multiply or a multiply-accumulate function. In the

multiply-accumulate mode, output data can be added to or

subtracted from previous results. When the Subtraction (SUB)

input is active simultaneously with an active ACC, a subtraction

can be performed. The double precision accumulated result is

rounded down to either a single precision or single precision

plus 3-bit extended result. In the multiply mode, the Extended

Product output (XTP) is sign extended in the two’s complement

mode or set to zero in the unsigned mode. The Round (RND)

control rounds up the Most Significant Product (MSP) and the

3-bit Extended Product (XTP) outputs. When Preload input

(PREL) is active, all the output buffers are forced into a highimpedance state (see Preload truth table) and external data

can be loaded into the output register by using the TSX, TSL

and TSM signals as input controls.

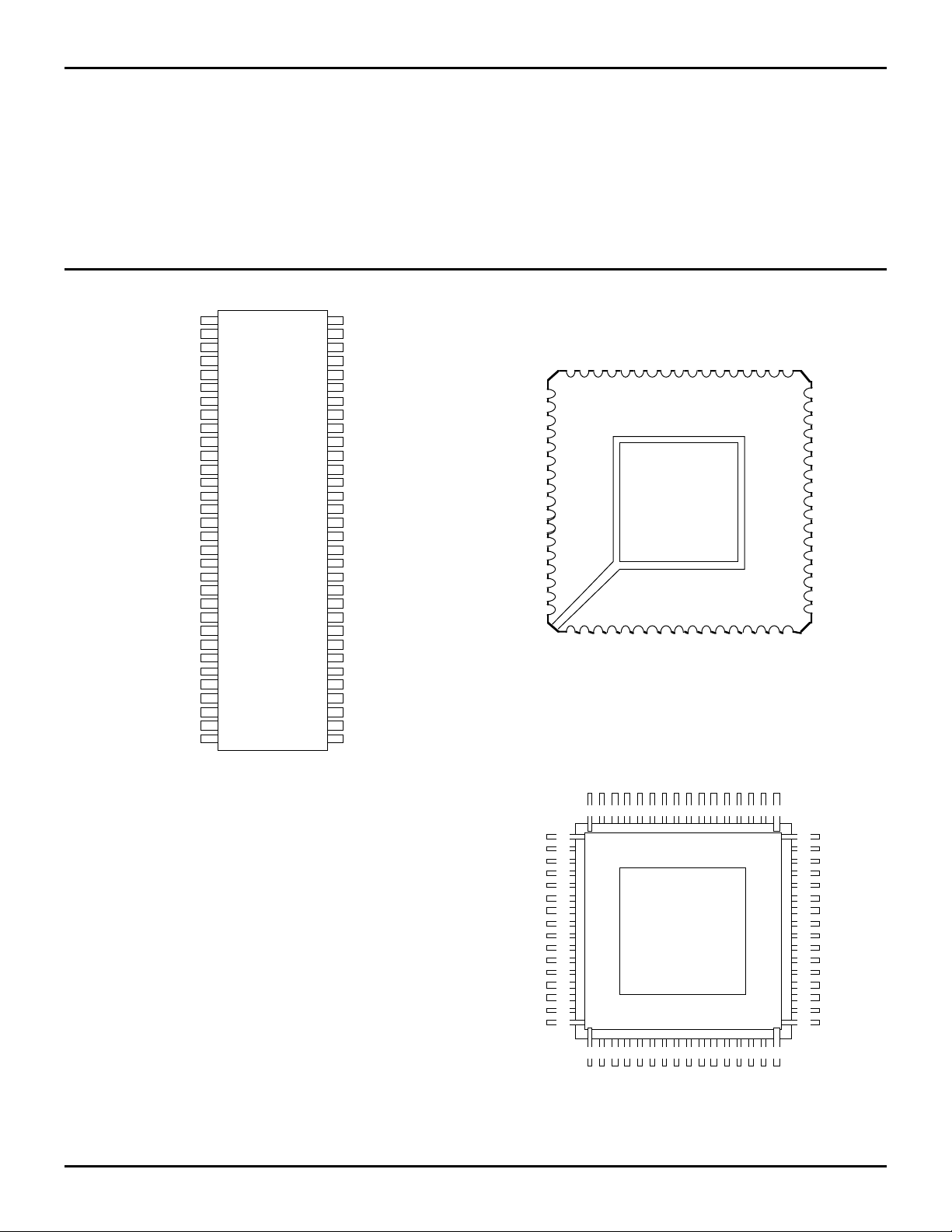

PIN CONFIGURATIONS

X

6

X

X

X

X

X

X

P

P

P

P

P

P

P

P

GND

P

P

10

P

P

11

P

12

P

13

P

14

P15,

P

16

P

17

P

18

P

19

P

20

P

21

P

22

P

23

1

5

2

4

3

3

4

2

5

1

6

0

7

0

,

8

1

,

9

2

,

10

3

,

11

4

,

12

13

5

,

14

6

,

7

,

15

16

17

18

19

20

21

22

23

C64-2

8

,

9

,

,

,

,

,

,

24

25

26

27

28

29

30

31

32

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

7

X

X

8

X

9

X

10

X

11

X

12

X

13

X

14

15

X

TSL

RND

SUB

ACC

CLKX

CLKY

CC

V

TC

TSX

PREL

TSM

CLKP

P

34

P

33

P

32

P

31

P

30

P

29

P

28

P

27

P

26

P

25

P

24

P1, Y1

P0, Y0

X0

X1

X2

X3

X4

X5

X6

X7

X8

X9

X10

X11

X12

X13

X14

7, Y7

P

P5, Y5

P4, Y4

P3, Y3

P2, Y2

6059 585756 5554 53 52515049484746 4544

61

62

63

64

65

66

67

68

1

2

3

4

5

6

7

8

9

1011121314 151617 1819 2021 2425 26

15

X

TSL

SUB

RND

P6, Y6

J68-1, L68-1

ACC

CLKX

GND

GND

J68-1

CC

V

CLKY

VCC

P9, Y9

P8, Y8

VCC

PLCC

TOP VIEW

P10, Y10

VCC

P11, Y11

P12, Y12

2223

TC

TSX

P14, Y14

P13, Y13

TSM

PREL

P16

P15, Y15

P34

CLKP

43

P17

42

P18

41

P19

40

P20

39

P21

38

P22

37

P23

36

P24

35

P25

34

P26

33

P27

32

P28

31

P29

30

P30

29

P31

28

P32

27

P33

2577 drw 03

DIP

TOP VIEW

2577 drw 02

P7, Y7

P6, Y6

F64-1

CLKY

P8, Y8

GND

CC

TC

V

P9, Y9

TSX

P10, Y10

P11, Y11

TSM

PREL

P13, Y13

P12, Y12

34

P

CLKP

P14, Y14

P15, Y15

P16

48

47

P17

46

P18

45

P19

44

P20

43

P21

42

P22

41

P23

40

P24

39

P25

38

P26

37

P27

36

P28

35

P29

34

P30

33

P31

2577 drw 04

P33

P32

P0, Y0

X0

X1

X2

X3

X4

X5

X6

X7

X8

X9

X10

X11

X12

X13

X14

P1, Y1

P3, Y3

P4, Y4

P5, Y5

P2, Y2

64636261 605958575655 545352 515049

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17181920 212223242526 272829 303132

X15

TSL

RND

SUB

ACC

CLKX

FLATPACK

TOP VIEW

11.2 2

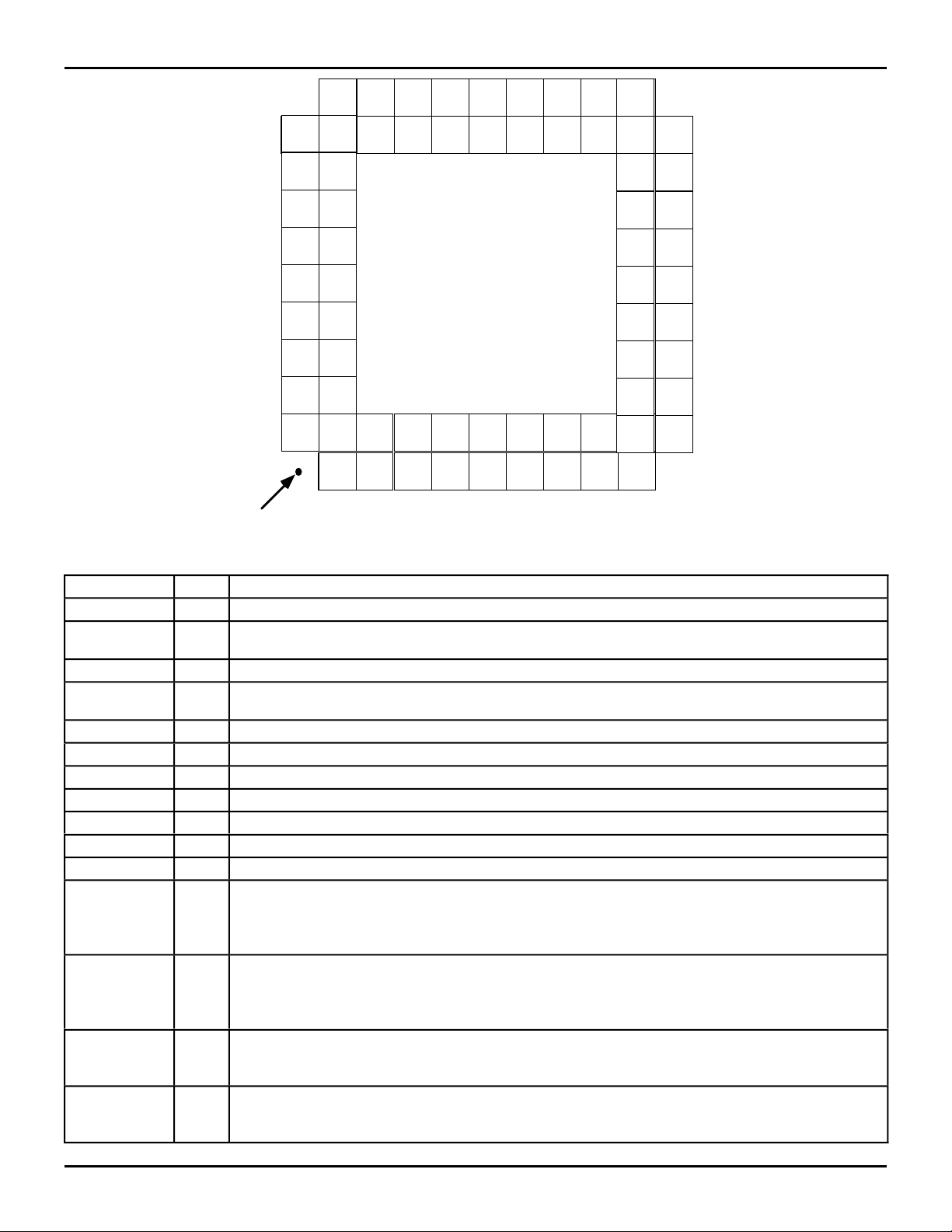

Page 3

IDT7210L

16 x 16 PARALLEL CMOS MULTIPLIER-ACCUMULATOR MILITARY AND COMMERCIAL TEMPERATURE RANGES

11

10

09

08

07

06

05

04

03

02

01

Pin 1

Designator

NC X15 RND CLKY TC PREL CLKP P33

X14 CLKX VCC TSX P34 NCX13

TSL SUB TSM

X11 X12

X9 X10

X7 X8

X5 X6

X3 X4

X1 X2

Y0,

X0

P0

Y1,P1Y3,P3Y5,P5Y7,

NC

Y2,

Y4,P4Y6,

P2

ABCDEFGHJKL

P6

ACC

G68-2

Y8,P8Y10,

P7

Y9,P9Y11,

GND

PGA

TOP VIEW

P10

P11

Y12,

P12

Y13,

P13

Y14,

P14

Y15,

P15

32

P

P30

P31

P28 P29

P26 P27

P24 P25

P22 P23

P20 P21

P18 P19

P16 P17

NC

2577 drw 05

PIN DESCRIPTIONS

Pin Name I/O Description

X0 - 15 I Data Inputs

Y0 - 15/ P0 - 15 I/O Multiplexed I/O port. Y0 - 15 are data inputs and can be used to preload LSP register on PREL = 1. P0 - 15

are LSP register outputs - enabled by TSL.

P16 - 31 I/O MSP register outputs - enabled by TSM. MSP register can be preloaded when PREL = 1.

P32 - 34 I/O XTP register outputs - enabled by TSX. XTP register can be preloaded through these inputs when

PREL = 1.

CLKX I Input data X0 - 15 loaded in X input register on CLKX rising edge.

CLKY I Input data Y0 - 15 loaded in Y input register on CLKY rising edge.

CLKP I Output data loaded into output register on rising edge of CLKP.

TSX I TSX = 0 enables XTP outputs, TSX = 1 tristates P32 - 34 lines.

TSM I TSM = 0 enables MSP outputs, TSM = 1 tristates P16 - 31 lines.

TSL I TSL = 0 enables LSP outputs, TSL = 1 tristates P0 - 15 lines.

PREL I When PREL= 1 data is input on P0 - 15 lines. When PREL = 0, inputs on these lines are ignored.

ACC I This input is loaded into the control register on the rising edge of (CLKX + CLKY).

When ACC = 1 and SUB = 0 an accumulate operation is performed. When ACC = 1 and SUB = 1, a

subtract operation is performed. When ACC = 0, the SUB input is a don't care and the device acts as a

simple multipler with no accumulation

SUB I This input is loaded into the control register on the rising edge of (CLKX + CLKY).

This input is active only when ACC = 1. When SUB = 1 the contents of the output register are subtracted

from the result and stored back in the output register. When SUB = 0 the contents of the output register

are added to the result and stored back in the output register

TC I This input is loaded into the control register on the rising edge of (CLKX + CLKY).

When TC = 1, the X and Y input are assumed to be in two's complement form. When TC = 0, X and Y

inputs are assumed to be in unsigned magnitude form

RND I This input is loaded into the control register on the rising edge of (CLKX + CLKY).

RND is inactive when low. RND = 1, adds a "1" to the most significant bit of the LSP, to round MSP and

XTP data

2577 tbl 01

11.2 3

Page 4

IDT7210L

16 x 16 PARALLEL CMOS MULTIPLIER-ACCUMULATOR MILITARY AND COMMERCIAL TEMPERATURE RANGES

PRELOAD TRUTH TABLE

PREL TSX TSM TSL XTP MSP LSP

0000QQQ

0001QQHi Z

0010QHi ZQ

0 0 1 1 Q Hi Z Hi Z

0100Hi ZQQ

0 1 0 1 Hi Z Q Hi Z

0 1 1 0 Hi Z Hi Z Q

0 1 1 1 Hi Z Hi Z Hi Z

1 0 0 0 Hi Z Hi Z Hi Z

1 0 0 1 Hi Z Hi Z PL

1 0 1 0 Hi Z PL Hi Z

1011Hi ZPLPL

1 1 0 0 PL Hi Z Hi Z

1 1 0 1 PL Hi Z PL

1 1 1 0 PL PL Hi Z

1 1 1 1 PL PL PL

NOTES: 2577 tbl 02

Hi Z = Output buffers at high impedance (output disabled)

Q = Output buffers at low impedance. Contents of output register will be

transferred to output pins.

PL = Output buffers at high impedance or output disabled. Preload data

supplied externally at output pins will be loaded into the output

register at the rising edge of CLKP.

NOTES ON TWO'S COMPLEMENT FORMATS

1. In two's complement notation, the location of the binary

point that signifies the separation of the fractional and

integer fileds is just after the sign, between the sign bit

(-2°) and the next significant bit for the multiplier inputs.

This same format is carried over to the output format,

except that the extended significance of the integer filed is

provided to extend the utility of the accumulator. In the

case of the output rotation, the output binary point is

located between the2° and 2

the binary point is arbitrary, as long as there is consistency

with both the input and output formats. The number filed

can be considered entirely integer with the binary point just

to the right of the least significant bit for the input, product

and the accumulated sum.

2. When in the non-accumulating mode, the first four bits (P

to P31) will all indicate the sign of the product. Additionally,

the P30 term will also indicate the sign with one exception,

when multiplying -1 x -1. With the additional bits that are

available in this multiplier, the –1 x –1 is a valid operation

that yields a +1 product.

3. In operations that require the accumulation of single products or sum of products, there is no change in format. To

allow for a valid summation beyond that available for a

single multiplication product, three additional significant

bits (guard bits) are provided. This is the same as if the

product was accumulated off-chip in a separate 35-bit wide

adder. Taking the sign at the most significant bit position

will guarantee that the largest number field will be used.

When the accumulated sum only occupies the right hand

portion of the accumulator, the sign will be extended into

the lesser significant bit positions.

1

bit positions. The location of

34

ABSOLUTE MAXIMUM RATINGS

Symbol Rating Commercial Military Unit

VCC Power Supply

Voltage

VTERM Terminal Voltage

with Respect to

GND

TA Operating

Temperature

TBIAS Temperature

Under Bias

TSTG Storage

Temperature

IOUT DC Output

Current

NOTE: 2577 tbl 03

1. Stresses greater than those listed under ABSOLUTE MAXIMUM

RATINGS may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or any other

conditions above those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

-0.5 to +7.0 -0.5 to +7.0 V

–0.5 to

V

CC +0.5V

0 to +70 –55 to +125 °C

–55 to +125 –65 to +135 °C

–55 to +125 –65 to +150 °C

50 50 mA

(1)

–0.5 to

VCC +0.5V

V

CAPACITANCE (TA = +25°C, f = 1.0MHz)

Symbol Parameter

CIN Input Capacitance VIN = 0V 10 pF

COUT Output Capacitance VOUT = 0V 12 pF

NOTE: 2577 tbl 04

1. This parameter is measured at characterization and not 100%tested.

(1)

Conditions Max. Unit

11.2 4

Page 5

IDT7210L

16 x 16 PARALLEL CMOS MULTIPLIER-ACCUMULATOR MILITARY AND COMMERCIAL TEMPERATURE RANGES

DC ELECTRICAL CHARACTERISTICS

(Commercial: VCC = 5.0V ± 10%, TA = 0°C to +70°C; Military: VCC = 5V ± 10%, TA = –55°C to +125°C)

Commercial Military

Symbol Parameter Test Conditions

(5)

Min. Typ.

VIH Input High Voltage Guaranteed Logic HIGH Level 2.0 — — 2.0 — — V

VIL Input Low Voltage Guaranteed Logic LOW Level — — 0.8 — — 0.8 V

|ILI| Input Leakage Current VCC = Max., VIN = 0V to VCC ——10——10µA

|ILO| Output Leakage Current VCC = Max., Outputs Disabled

OUT = 0 to VCC

V

——10——10µA

VOH Output HIGH Voltage VCC = Min., IOH = –2.0mA 2.4 — — 2.4 — — V

(4)

VOL

Output LOW Voltage VCC = Min., IOL = 4mA — — 0.4 — — 0.4 V

IOS Output Short Circuit Current VCC = Max., V0 GND -20 — -100 -20 — -100 mA

ICC

(2)

Operating Power Supply Current VCC = Max., Outputs Enabled

f= 10MHz

(2)

— 45 90 — 45 110 mA

CL = 50 pF

ICCQ1 Quiescent Power Supply Current VIN ≥ VIH, VIN ≤ VIL — 20 30 — 20 30 mA

ICCQ2 Quiescent Power Supply Current VIN ≥ VCC –0.2V, V IN ≤ 0.2V — 4 10 — 4 12 mA

(2,3)

ICC/f

Increase in Power Supply

VCC = Max., Outputs Disabled — — 6 — — 8 mA/

Current MHz

NOTES:

1. Typical implies VCC = 5V and TA = +25°C.

2. I

CC is measured at 10MHz and VIN = 0 to 3V. For frequencies greater than 10MHz, the following equation is used for the commercial range:

CC = 90+ 6(f –10)mA, where f = operating frequency in MHz. For the military range, ICC = 110 + 8(f –10). f = operating frequency in MHz, f = 1/tMA.

I

3. For frequencies greater than 10MHz, guaranteed by design, not production tested.

OL = 4mA for tMA > 55ns.

4. I

5. For conditions shown as Max. or Min., use appropriate value specified under electrical characteristics.

(1)

Max. Min. Typ.

(1)

Max.

Unit

MHz

2577 tbl 05

AC ELECTRICAL CHARACTERISTICS COMMERCIAL (VCC = 5V ± 10%, TA = 0° to +70°C)

7210L20 7210L25 7210L35 7210L45 7210L55 7210L65

Symbol Parameter Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Unit

(1)

(2)

2.0 20 2.0 25 2.0 35 2.0 45 2.0 55 2.0 65 ns

2.0 18 2.0 20 2.0 25 2.0 25 2.0 30 2.0 35 ns

— 18 – 20 – 25 – 25 – 30 – 30 ns

t

MA

t

D

t

ENA

t

DIS

t

S

t

H

t

PW

t

HCL

NOTES: 2577 tbl 06

1. Transition is measured ±500mV from steady state voltage.

2. Minimum delays guaranteed but not tested

Multiply-Accumulate Time

Output Delay

(2)

3-State Enable Time — 18 – 20 – 25 – 25 – 30 – 30 ns

3-State Disable Time

Input Register Set-up Time 10 — 12 – 12 – 15 – 20 – 25 – ns

Input Register Hold Time 3 — 3–3–3–3–3–ns

Clock Pulse Width 9 — 10 – 10 – 15 – 20 – 25 – ns

Relative Hold Time 0 — 0–0–0–0–0–ns

AC ELECTRICAL CHARACTERISTICS MILITARY (VCC = 5V ± 10%, TA = –55° to +125°C)

7210L25 7210L30 7210L40 7210L55 7210L65 7210L75

Symbol Parameter Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Unit

(1)

(2)

2.0 25 2.0 30 2.0 40 2.0 55 2.0 65 2.0 75 ns

2.0 20 2.0 20 2.0 25 2.0 30 2.0 35 2.0 35 ns

— 20 – 20 – 25 – 25 – 30 – 30 ns

t

MA

t

D

t

ENA

t

DIS

t

S

t

H

t

PW

t

HCL

NOTES: 2577 tbl 07

1. Transition is measured ±500mV from steady state voltage.

2. Minimum delays guaranteed but not tested

Multiply-Accumulate Time

Output Delay

(2)

3-State Enable Time — 20 – 20 – 25 – 30 – 30 – 35 ns

3-State Disable Time

Input Register Set-up Time 12 — 12 – 15 – 20 – 25 – 25 – ns

Input Register Hold Time 3 — 3–3–3–3–3–ns

Clock Pulse Width 10 — 10 – 15 – 20 – 25 – 25 – ns

Relative Hold Time 0 — 0–0–0–0–0–ns

11.2 5

Page 6

IDT7210L

16 x 16 PARALLEL CMOS MULTIPLIER-ACCUMULATOR MILITARY AND COMMERCIAL TEMPERATURE RANGES

INPUT

INPUT

CLOCK

OUTPUT

CLOCK

PRELOAD

THREE-STATE

CONTROL

OUTPUT

CONTROL AND

DATA

IN

tS tH

tPW

tDIS tENA

HIGH IMPEDANCE

tHCL

tMA

tPW

tDIS tS tH tENA

DATAOUT PRELOAD IN DATA DATAOUT

tD

Figure 1. Timing Diagram

11.2 6

Page 7

IDT7210L

16 x 16 PARALLEL CMOS MULTIPLIER-ACCUMULATOR MILITARY AND COMMERCIAL TEMPERATURE RANGES

DIGIT

VALUE

DIGIT

VALUE

–16

2

–15

2

–14

2

–13

2

–12

2

–11

2

–10

2

–9

2–82

–7

2

–6

2

–5

2

–4

2

–3

2

–2

2

–1

2

SIGNAL

0

–32

P

1

–31

P

2

–30

P

3

–29

P

4

–28

P

5

–27

P

6

–26

P

7

–25

P

8

–24

P

9

–23

P

10

–22

P

11

–21

P

12

–20

P

13

–19

P

14

–18

P

15

–17

P

16

–16

P

17

–15

P

18

–14

P

19

–13

P

20

–12

P

21

–11

P

22

–10

P

23

–9

P

24

–8

P

25

–7

P

26

–6

P

27

–5

P

28

–4

P

29

–3

P

30

–2

P

31

–1

P

32

0

P

33

1

P

34

2

P

=

2

2

2577 drw 11

2

2

2

2

2

2

LSP

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

MSP

Figure 3. Fractional Unsigned Mgnitude Notation

2

2

2

2

2

2

2

2

2

2

XTP

2

SIGNAL

0

X

1

X

2

X

3

X

4

X

5

X

6

X

7

X

8

X

9

X

10

X

11

X

12

X

13

X

14

X

15

X

BINARY POINT

DIGIT

VALUE

–15

2

–14

2

–13

2

–12

2

–11

2

–10

2

–9

2

–8

2

–7

2

–6

2

–5

2

–4

2

–3

2

–2

2

–1

2

0

–2

DIGIT

SIGNAL

0

–15

Y

1

–14

Y

2

–13

Y

3

–12

Y

4

–11

Y

5

–10

Y

6

–9

Y

7

–8

Y

8

–7

Y

9

–6

Y

10

–5

Y

11

–4

Y

12

–3

Y

13

–2

Y

14

–1

Y

0

15

Y

X

VALUE

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

–2

DIGIT

SIGNAL

0

–30

P

1

–29

P

2

–28

P

3

–27

P

4

–26

P

5

–25

P

6

–24

P

7

–23

P

8

–22

P

9

–21

P

10

–20

P

11

–19

P

12

–18

P

13

–17

P

14

–16

P

15

–15

P

16

–14

P

17

–13

P

18

–12

P

19

–11

P

20

–10

P

21

–9

P

22

–8

P

23

–7

P

24

–6

P

25

–5

P

26

–4

P

27

–3

P

28

–2

P

29

–1

P

30

0

P

31

1

P

32

2

P

33

3

P

4

34

P

=

VALUE

2

2

2

2

2

2

2

2

LSP

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

XTP MSP

–2

2577 drw 10

SIGNAL

1 X0

X

3 X2

X

5 X4

X

Figure 2. Fractional Two’s Complement Notation.

7 X6

X

9 X8

X

11 X 10

X

13 X 12

X

15 X14

X

BINARY POINT

DIGIT

VALUE

–16

2

–15

2

–14

2

–13

2

–12

2

–11

2

–10

2

–9

2–82

–7

2

–6

2

–5

2

–4

2

–3

2

–2

2

–1

2

SIGNAL

0

Y

1

Y

2

Y

3

Y

4

Y

5

Y

6

Y

7

Y

8

Y

9

Y

10

Y

11

Y

12

Y

13

Y

14

Y

15

Y

X

11.2 7

Page 8

IDT7210L

16 x 16 PARALLEL CMOS MULTIPLIER-ACCUMULATOR MILITARY AND COMMERCIAL TEMPERATURE RANGES

SIGNAL

0

X

BINARY POINT

1

X

2

X

3

X

4

X

5

X

6

X

7

X

8

X

9

X

10

X

11

X

12

X

13

X

14

X

15

X

DIGIT

VALUE

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

2

10

2

11

2

12

2

13

2

14

2

15

–2

SIGNAL

DIGIT

0

0

Y

1

1

Y

2

2

Y

3

3

Y

4

4

Y

5

5

Y

6

6

Y

7

7

Y

8

8

Y

9

9

Y

10

10

Y

11

11

Y

12

12

Y

13

13

Y

14

14

Y

15

15

Y

X

VALUE

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

–2

SIGNAL

DIGIT

0

0

P

1

1

P

2

2

P

3

3

P

4

4

P

5

5

P

6

6

P

7

7

P

8

8

P

9

9

P

10

10

P

11

11

P

12

12

P

13

13

P

14

14

P

15

15

P

16

16

P

17

17

P

18

18

P

19

19

P

20

20

P

21

21

P

22

22

P

23

23

P

24

24

P

25

25

P

26

26

P

27

27

P

28

28

P

29

29

P

30

30

P

31

31

P

32

32

P

33

33

P

34

34

P

=

VALUE

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

XTP MSP LSP

–2

2577 drw 12

BINARY POINT

Figure 4. Integer Two's Complement Notation

SIGNAL

DIGIT

0

0

X

1

1

X

2

2

X

3

3

X

4

4

X

5

5

X

6

6

X

7

7

X

8

8

X

9

9

X

10

10

X

11

11

X

12

12

X

13

13

X

14

14

X

15

15

X

VALUE

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

SIGNAL

DIGIT

0

0

Y

1

1

Y

2

2

Y

3

3

Y

4

4

Y

5

5

Y

6

6

Y

7

7

Y

8

8

Y

9

9

Y

10

10

Y

11

11

Y

12

12

Y

13

13

Y

14

14

Y

15

15

Y

X

VALUE

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

DIGIT

SIGNAL

0

0

P

1

1

P

2

2

P

3

3

P

4

4

P

5

5

P

6

6

P

7

7

P

8

8

P

9

9

P

10

10

P

11

11

P

12

12

P

13

13

P

14

14

P

15

15

P

16

16

P

17

17

P

18

18

P

19

19

P

20

20

P

21

21

P

22

22

P

23

23

P

24

24

P

25

25

P

26

26

P

27

27

P

28

28

P

29

29

P

30

30

P

31

31

P

32

32

P

33

33

P

34

34

P

=

VALUE

2

2

2

2

2

2

2

2

LSP

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

XTP MSP

2

2577 drw 13

Figure 5. Integer Unsigned Magnitude Notation

11.2 8

Page 9

IDT7210L

16 x 16 PARALLEL CMOS MULTIPLIER-ACCUMULATOR MILITARY AND COMMERCIAL TEMPERATURE RANGES

TEST CIRCUITS AND WAVEFORMS

TEST CIRCUITS FOR ALL OUTPUTS

V

CC

V

OUT

50pF

C L

Pulse

Generator

V

IN

D.U.T.

T

R

7.0V

500Ω

500Ω

2577 drw 06

SWITCH POSITION

Test

Open Drain

Disable Low

Enable Low

All Other Tests

DEFINITIONS:

L= Load capacitance: includes jig and probe capacitance.

C

R

T = Termination resistance: should be equal to ZOUT of the Pulse

Generator.

Switch

Closed

Open

2577 lnk 09

SET-UP, HOLD AND RELEASE TIMES

DATA

INPUT

TIMING

tSU

tH

INPUT

ASYNCHRONOUS CONTROL

PRESET

tREM

CLEAR

ETC.

SYNCHRONOUS CONTROL

PRESET

CLOCK ENABLE

CLEAR

tSU

tH

ETC.

PROPAGATION DELAY

SAME PHASE

INPUT TRANSITION

tPLH

OUTPUT

tPLH tPHL

OPPOSITE PHASE

INPUT TRANSITION

tPHL

3V

1.5V

0V

3V

1.5V

0V

3V

1.5V

0V

3V

1.5V

0V

2577 drw 07

3V

1.5V

0V

V

OH

1.5V

VOL

3V

1.5V

0V

2577 drw 09

PULSE WIDTH

LOW-HIGH-LOW

PULSE

tW

HIGH-LOW-HIGH

PULSE

1.5V

1.5V

2577 drw 08

ENABLE AND DISABLE TIMES

ENABLE DISABLE

3V

CONTROL

INPUT

PLZtPZL

t

OUTPUT

NORMALLY

LOW

SWITCH

CLOSED

3.5V

1.5V

tPZH tPHZ

OUTPUT

NORMALLY

HIGH

NOTES:

1. Diagram shown for input Control Enable-LOW and input Control DisableHIGH

2. Pulse Generator for All Pulses: Rate ≤ 1.0MHz; t

SWITCH

OPEN

1.5V

0V

F ≤ 2.5ns; tR ≤ 2.5ns

0.3V

0.3V

1.5V

0V

3.5V

VOL

VOH

0V

2577 drw 10

11.2 9

Page 10

IDT7210L

16 x 16 PARALLEL CMOS MULTIPLIER-ACCUMULATOR MILITARY AND COMMERCIAL TEMPERATURE RANGES

ORDERING INFORMATION

IDT

Device Type

XXXX A

Power

999

Speed

A

Package

X

Process/

Temperature

Range

Blank

B

C

J

F

G

L

7210

Commercial (0°C to +70°C)

Military (–55

°

C to +125°C)

Compliant to MIL-STD-883, Class B

Topbraze DIP

Plastic Leaded Chip Carrier

Flatpack

Pin Grid Array

Com'l.

20

25

35

45

55

65

Mil.

25

30

40

55

65

75

Speed in Nanoseconds

Low Power

16 x 16 Parallel Multiplier Accumulator

2577 drw 11

11.2 10

Loading...

Loading...