Page 1

Integrated

Circuit

Systems, Inc.

ICS9248-114

Third party brands and names are the property of their respective owners.

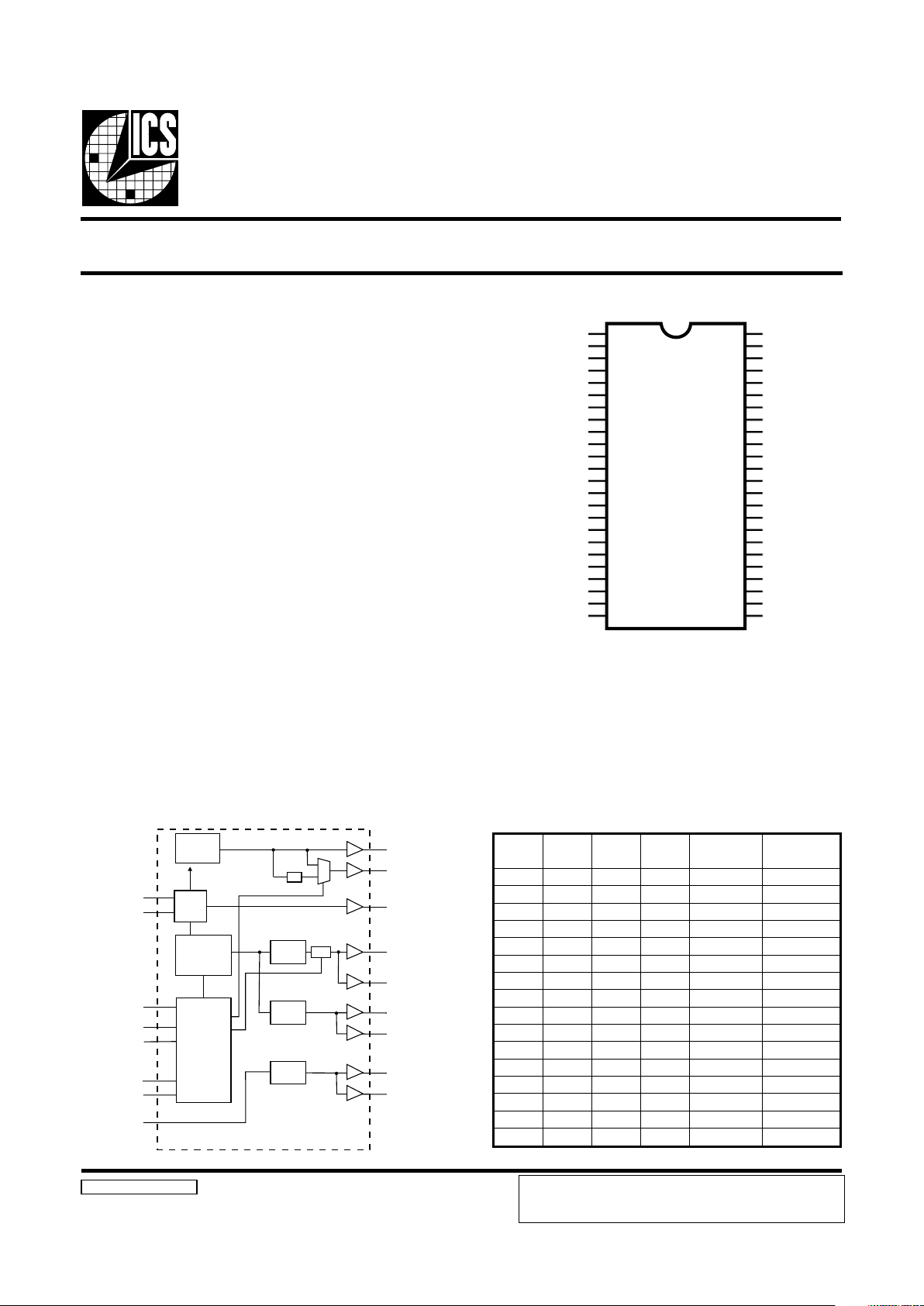

Block Diagram

9248-114 Rev C 01/24/01

Functionality

Pin Configuration

48-Pin 300mil SSOP

Recommended Application:

VIA K7 style chipset

Output Features:

• 1 - Differential pair open drain CPU clocks

• 1 - Single-ended open drain CPU clock

• 13 - SDRAM @ 3.3V

• 6 - PCI @3.3V,

• 1 - 48MHz, @3.3V fixed.

• 1 - 24/48MHz @ 3.3V

• 2 - REF @3.3V, 14.318MHz.

Features:

• Up to 155MHz frequency support

• Support power management: CPU stop and Power down

Mode from I

2

C programming.

• Spread spectrum for EMI control (0 to -0.5% down

spread, ± 0.25% center spread).

• Uses external 14.318MHz crystal

Skew Specifications:

• CPUT – CPUC: <200ps

• PCI – PCI: <500ps

• CPU – PCI: <500ps

AMD - K7™ System Clock Chip

* Internal Pull-up Resistor of 120K to VDD

VDD1

REF0/CPU_STOP#*

GND

X1

X2

VDD2

*MODE/PCICLK_F

*FS3/PCICLK0

GND

*SEL24_48#/PCICLK1

PCICLK2

PCICLK3

PCICLK4

VDD2

BUFFER IN

GND

SDRAM11

SDRAM10

VDD3

SDRAM9

SDRAM8

GND

S DATA

SCLK

REF1/FS2*

GND

CPUCLKT1

GND

CPUCLKC0

CPUCLKT0

VDDL

PD#*

SDRAM_OUT

GND

SDRAM0

SDRAM1

VDD3

SDRAM2

SDRAM3

GND

SDRAM4

SDRAM5

VDD3

SDRAM6

SDRAM7

VDD4

48MHz/FS0*

24/48MHz/FS1*

ICS9248-114

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

SEL24_48#

BUFFER IN

PLL2

PLL1

Spread

Spectrum

48MHz

24_48MHz

SDRAM (11:0)

PCICLK (4:0)

PCICLK_F

SDRAM_OUT

CPUCLKT (1:0)

CPUCLKC0

X1

X2

XTAL

OSC

CPU

DIVDER

PCI

DIVDER

Stop

S DATA

SCLK

FS (3:0)

PD#

CPU_STOP#

Control

Logic

Config.

Reg.

/ 2

REF (1:0)

SDRAM

DRIVER

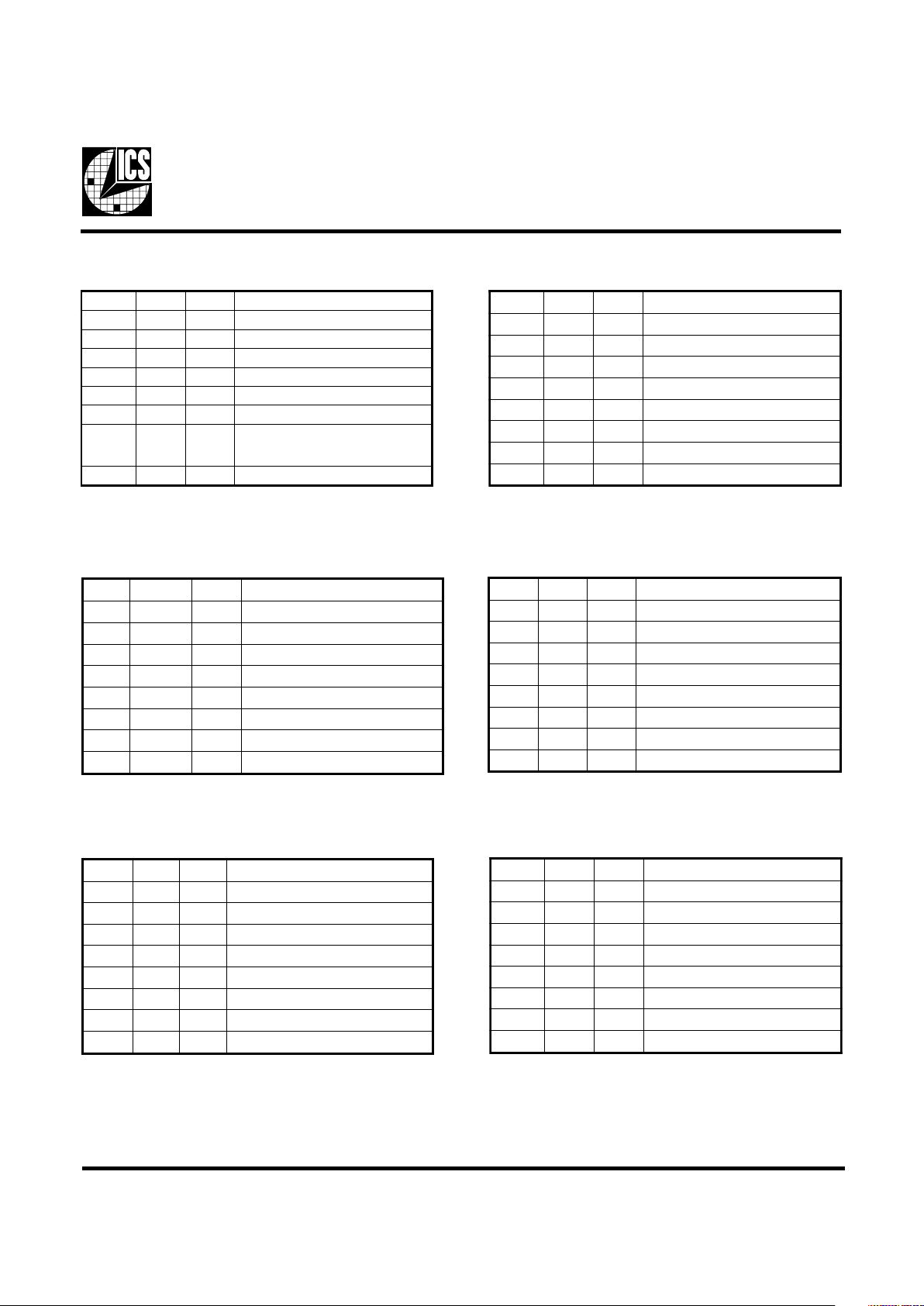

3SF2SF1SF0SF

UPC

)zHM(

KLCICP

)zHM(

0000 00.42133.14

0001 00.5705.73

0010 03.3856.14

0011 08.6604.33

0100 00.30133.43

0101 00.21133.73

0110 03.33134.44

0111 00.00133.33

1000 00.02100.04

100 1 00.51133.83

10 10 00.01176.63

10 11 00.50100.53

1100 00.04100.53

110 1 00.05105.73

1110 00.42100.13

1111 03.33133.33

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

Page 2

2

ICS9248-114

Third party brands and names are the property of their respective owners.

Pin Descriptions

Notes:

1: Internal Pull-up Resistor of 120K to 3.3V on indicated inputs

2: Bidirectional input/output pins, input logic levels are latched at internal power-on-reset. Use 10Kohm resistor

to program logic Hi to VDD or GND for logic low.

REBMUNNIPEMANNIPEPYTNOITPIRCSED

11DDVRWPV3.3lanimon,ylppusrewopLATX,FER

2

0FERTUO

REGNORTSehtsituptuoFERsihT.kcolcecnereferzhM813.41

sdaolSUBASIrofreffub

#POTS_UPC

2,1

NI

taMARDS&CKLCUPC,TKLCUPCstlahtupnisuonorhcnysasihT

.wolnevirdnehwlevel"0"cigol

,22,61,9,3

74,54,93,33

DNGRWPdnuorG

41XNI

kcabdeefdna)Fp63(pacdaollanretnisah,tupnilatsyrC

2Xmorfrotsiser

52XTUO

daollanretnisaH.zHM813.41yllanimon,tuptuolatsyrC

)Fp63(pac

41,62DDVRWPV3.3lanimon,KLCICPdnaF_KLCICProfylppuS

7

F_KLCICPTUO

rewoprof#POTS_ICPybdetceffatonkcolcICPgninnureerF

.tnemeganam

EDOM

2,1

NI

.edoMeliboM=0,edoMpotkseD=1,niptcelesnoitcnuf2niP

.tupnIdehctaL

8

3SF

2,1

NIDNGotnwod-lluPlanretnI.tupnIdehctaL.niptcelesycneuqerF

0KLCICPTUOtuptuokcolcICP

01

#84_42LES

2,1

NItuptuo52niprofzHM84ro42tcelesottupnicigoL

1KLCICPTUO.tuptuokcolcICP

11,21,31)2:4(KLCICPTUO.stuptuokcolcICP

51NIREFFUBNI.stuptuoMARDSrofsreffuBtuonaFottupnI

,12,02,81,71

,23,13,92,82

83,73,53,43

)0:11(MARDSTUO

nipNIREFFUBmorfstuptuoreffuBtuonaF,stuptuokcolcMARDS

.)tespihcybdellortnoc(

63,03,913DDVRWP.V3.3lanimonMARDSrofylppuS

32ATADSNIIroftupniataD

2

tupnitnarelotV5,tupnilairesC

42KLCSNIIfotupnikcolC

2

tupnitnarelotV5,tupniC

52

zHM84_42TUOtuptuokcolczHM84/zHM42

1SF

2,1

NI.tupnIdehctaL.niptcelesycneuqerF

62

zHM84TUOkcolctuptuozHM84

0SF

2,1

NItupnIdehctaL.niptcelesycneuqerF

724DDVRWP.erocLLPdexifdnasreffubtuptuozHM84&42rofrewoP

04TUO_MARDSTUOreffubyaledorezMARDSrofkcolcecnerefeR

14#DP

2,1

NIwolevitca,pihcnwodsrewoP

24DDVRWPV3.3erocrofylppuS

34,64)0:1(TKLCUPCTUO

niardnepoesehT.stuptuoUPCriaplaitnereffidfoskcolc"eurT"

.pu-llupV5.1lanretxenadeenstuptuo

440CKLCUPCTUO

esehT.stuptuoUPCriaplaitnereffidfoskcolc"yrotnemelpmoC"

.pu-llupV5.1lanretxenadeenstuptuoniardnepo

84

1FERTUO.kcolcecnereferzHM813.41

2SF

2,1

NItupnIdehctaL.niptcelesycneuqerF

Page 3

3

ICS9248-114

Third party brands and names are the property of their respective owners.

General Description

The ICS9248-114 is a main clock synthesizer chip for AMD-K7 based systems with VIA style chipset. This provides all clocks

required for such a system.

Spread spectrum may be enabled through I2C programming. Spread spectrum typically reduces system EMI by 8dB to 10dB.

This simplifies EMI qualification without resorting to board design iterations or costly shielding. The ICS9248-114

employs a proprietary closed loop design, which tightly controls the percentage of spreading over process and temperature

variations.

Serial programming I

2

C interface allows changing functions, stop clock programming and frequency selection.

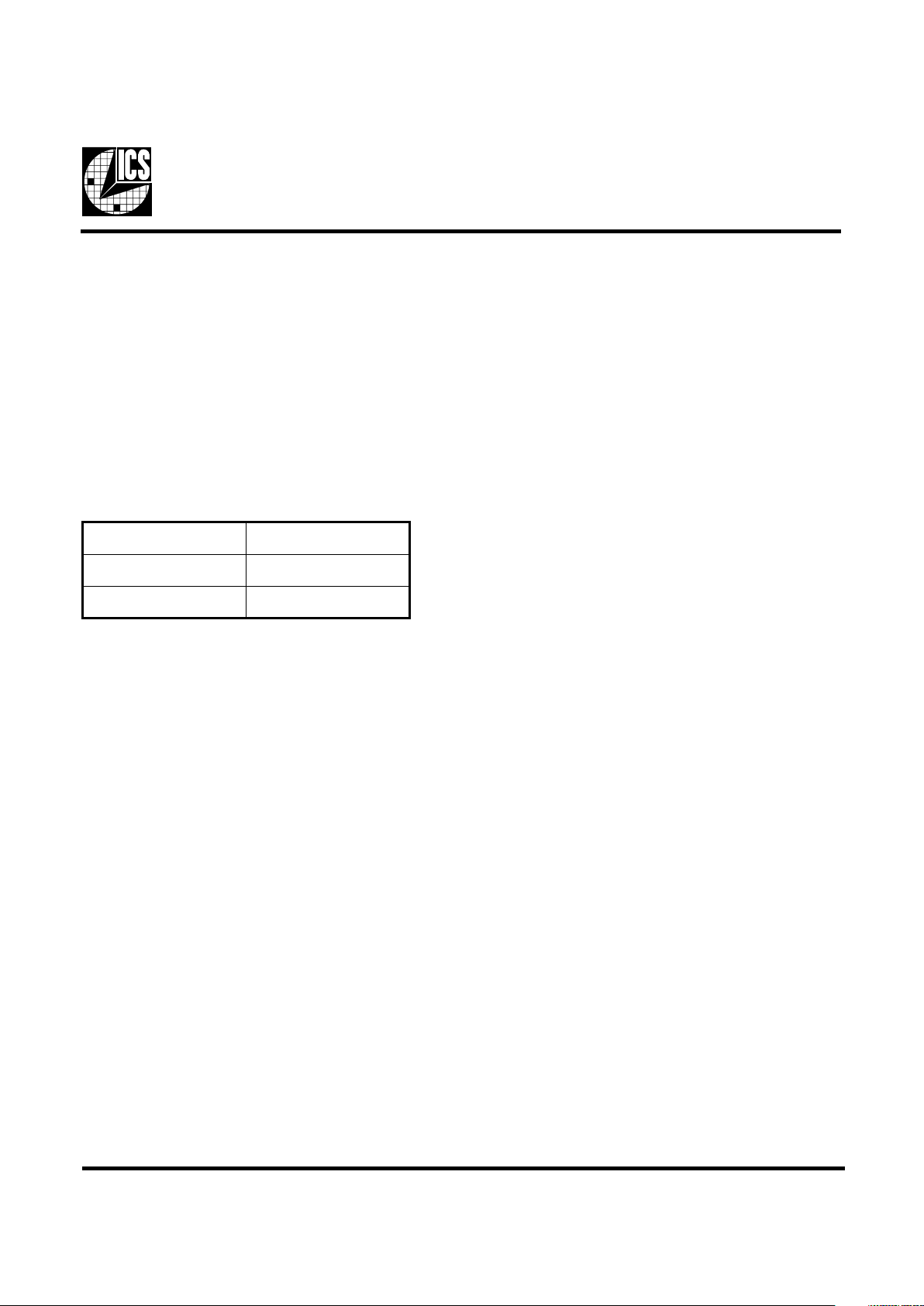

Mode Pin - Power Management Input Control

7niP,EDOM

)tupnIdehctaL(

2niP

0

#POTS_UPC

)tupnI(

1

0FER

)tuptuO(

Page 4

4

ICS9248-114

Third party brands and names are the property of their respective owners.

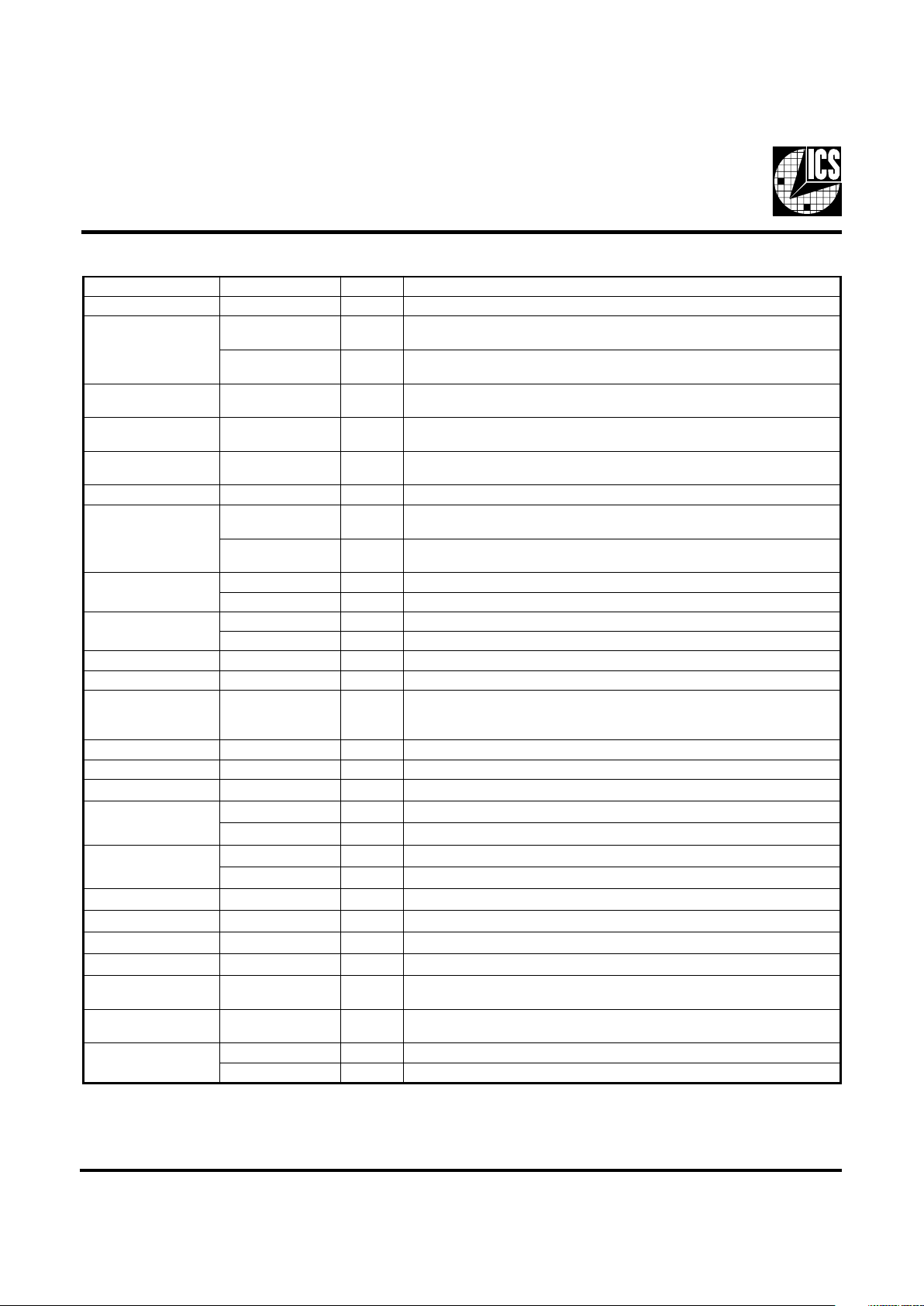

Byte0: Functionality and Frequency Select Register (default = 0)

Serial Configuration Command Bitmap

Note1: Default at power-up will be for latched logic inputs to define frequency, as displayed by Bit 3.

The I

2

C readback of the power up default could indicate the manufacture ID in bits 2, 7:4 as shown.

tiBnoitpircseDDWP

,2tiB

4:7tiB

)4,5,6,7,2(tiB

KLCUPC

)zHM(

KLCICP

)zHM(

daerpS

egatnecerP

00100

1etoN

00000 00.42133.14daerpSretneC%52.0±

00001 00.5705.73daerpSretneC%52.0±

00010 03.3856.14daerpSretneC%52.0±

00011 08.6604.33daerpSretneC%52.0±

00100 00.30133.43daerpSretneC%52.0±

0010 1 00.21133.73daerpSretneC%52.0±

00110 03.33134.44daerpSretneC%52.0±

00111 00.00133.33daerpSretneC%52.0±

01000 00.02100.04daerpSretneC%52.0±

01001 00.51133.83daerpSretneC%52.0±

01010 00.01176.63daerpSretneC%52.0±

01011 00.50100.53daerpSretneC%52.0±

01100 00.04100.53daerpSretneC%52.0±

01101 00.05105.73daerpSretneC%52.0±

01110 00.42100.13daerpSretneC%52.0±

01111 03.33133.33daerpSretneC%52.0±

10000 00.0900.03daerpSretneC%52.0±

1000 1 05.2938.03daerpSretneC%52.0±

100 10 00.5976.13daerpSretneC%52.0±

100 1 1 05.7905.23daerpSretneC%52.0±

10 100 05.10138.33daerpSretneC%52.0±

10 10 1 00.72133.24daerpSretneC%52.0±

10 110 05.63131.43daerpSretneC%52.0±

10 111 00.00133.33daerpSnwoD%5.011000 00.02100.04daerpSnwoD%5.01100 1 05.71171.93daerpSretneC%52.0±

110 10 00.22176.04daerpSretneC%52.0±

110 11 05.70138.53daerpSretneC%52.0±

11100 00.54152.63daerpSretneC%52.0±

1110 1 00.55157.83daerpSretneC%52.0±

11110 00.03105.23daerpSretneC%52.0±

11111 03.33123.33daerpSnwoD%5.0-

3tiB

stupnIdehctaL,tceleserawdrahybdetcelessiycneuqerF-0

4:7,2tiBybdetcelessiycneuqerF-1

0

1tiB

lamroN-0

delbanEmurtcepSdaerpS-1

1

0tiB

gninnuR-0

stuptuollaetatsirT-1

0

Page 5

5

ICS9248-114

Third party brands and names are the property of their respective owners.

Byte 1: CPU, Active/Inactive Register

(1= enable, 0 = disable)

TIB#NIPDWPNOITPIRCSED

7tiB-X#2SF

6tiB-1 )devreseR(

5tiB-1 )devreseR(

4tiB-X#3SF

3tiB041 TUO_MARDS

2tiB-X #)#84_42LES(

1tiB44,341

htob(elbane0KLCUPC

dna"eurT".riaplaitnereffid

)"yratnemilpmoC

0tiB641 elbaneTKLCUPC

Byte 2: PCI, Active/Inactive Register

(1= enable, 0 = disable)

TIB#NIPDWPNOITPIRCSED

7tiB-X#0SF

6tiB71 F_KLCICP

5tiB-1 )devreseR(

4tiB311 4KLCICP

3tiB211 3KLCICP

2tiB111 2KLCICP

1tiB011 1KLCICP

0tiB81 0KLCICP

Notes:

1. Inactive means outputs are held LOW and are disabled

from switching.

2. Latched Frequency Selects (FS#) will be inverted logic

load of the input frequency select pin conditions.

TIB#NIPDWPNOITPIRCSED

7tiB821 7MARDS

6tiB921 6MARDS

5tiB131 5MARDS

4tiB231 4MARDS

3tiB431 3MARDS

2tiB531 2MARDS

1tiB731 1MARDS

0tiB831 0MARDS

Byte 4: SDRAM , Active/Inactive Register

(1= enable, 0 = disable)

TIB#NIPDWPNOITPIRCSED

7tiB-1 )devreseR(

6tiB-1 )devreseR(

5tiB-1 )devreseR(

4tiB-X #EDOM

3tiB-X#1SF

2tiB-1 )devreseR(

1tiB841 1FER

0tiB210FER

Byte 5: Peripheral , Active/Inactive Register

(1= enable, 0 = disable)

Byte 3: SDRAM, Active/Inactive Register

(1= enable, 0 = disable)

TIB#NIPDWPNOITPIRCSED

7tiB-0 )etoN(devreseR

6tiB-0 )etoN(devreseR

5tiB-0 )etoN(devreseR

4tiB-0 )etoN(devreseR

3tiB-0 )etoN(devreseR

2tiB-1 )etoN(devreseR

1tiB-1 )etoN(devreseR

0tiB-0 )etoN(devreseR

Byte 6: Peripheral , Active/Inactive Register

(1= enable, 0 = disable)

Note: Don’t write into this register, writing into this

register can cause malfunction

TIB#NIPDWPNOITPIRCSED

7tiB-1 )devreseR(

6tiB-1 )devreseR(

5tiB621 zHM84

4tiB521 zHM84_42

3tiB711 11MARDS

2tiB811 01MARDS

1tiB021 9MARDS

0tiB121 8MARDS

Page 6

6

ICS9248-114

Third party brands and names are the property of their respective owners.

Absolute Maximum Ratings

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.5 V

Logic Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . GND –0.5 V to V

DD

+0.5 V

Ambient Operating Temperature . . . . . . . . . . . . . 0°C to +70°C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are

stress specifications only and functional operation of the device at these or any other conditions above those listed in the

operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods

may affect product reliability.

Electrical Characterist ics - Input/Supply/Common Output Parameters

TA = 0 - 70C; Supply Voltage VDD = 3.3 V +/-5% (unless otherwise stated)

PARAMETER SYMBOL CONDITIONS MI

N

TYP MAX UNITS

Input High Voltage V

IH

2V

DD

+0.3 V

Input Low Voltage V

IL

VSS-0.3 0.8 V

Input High Current I

IH

VIN = V

DD

5

µ

A

Input Low Current I

IL1

VIN = 0V; Inputs with no pull-up resis to rs -5

µ

A

Input Low Current I

IL2

VIN = 0V; Inputs with pull-up resistors -200

µ

A

I

DD3.3OP66

CL = 0 pF; Select @ 66 MHz 180 mA

I

DD3.3OP100

CL = 0 pF; Select @ 100 MHz 180 mA

I

DD3.3OP133

CL = 0 pF; Select @ 133 MHz 180 mA

Powerdown Current

I

DD3.3PD

CL = 0 pF; Input address to VDD or GND

600

µ

A

Input Frequency F

i

VDD = 3.3 V 12 14.318 16 MHz

C

IN

Logic Inputs 5 pF

C

INX

X1 & X2 pins 27 45 pF

Clk Stabilization

1

T

STAB

From VDD = 3.3 V to 1% target frequency 3 ms

T

CPU-PC

I

CPU VT = VX, PCI VT = 1.5V, CPU=66MHz - 1 00 -5509 100 ps

T

CPU-PC

I

CPU VT = VX, PCI VT = 1.5V, CPU=100MHz-100 -2946 100 ps

T

CPU-PCI

CPU VT = VX, PCI VT = 1.5V, CPU= 13 3MH

z

-100 -1637 100 ps

1

Guaranteed by design, not 100% tested in production.

Input Capacitance

1

Operating Supply

Current

Skew

1

Page 7

7

ICS9248-114

Third party brands and names are the property of their respective owners.

Electrical Characteristics - CPUCLK (Open Drain)

TA = 0 - 70º C; VDD = 3.3 V +/-5%; CL = 20 pF (unless otherwise stated).

PARAM ETER SYM BOL CONDITIONS MIN TYP MAX UNITS

Output Impedance Z

O

1

VO = V

X

60

Ω

Output High Voltage V

OH2 B

Termination to V

pull-up (external)

11.2V

Output Low Voltag e V

OL2B

Termination to V

pull-up (external)

0.4 V

Output Low Current I

OL2 B

VOL = 0.3 V 18

mA

Rise Time

t

r2B

1

VOL = 0.3 V, VOH = 1.2 V 1.93 2.6 ns

Fall Time

t

f2B

1

VOH = 1.2 V, VOL = 0.3 V 0.81 2.6 ns

Duty C ycle

d

t2B

1

VT = V

X

45 49.3 55 %

Differential

Voltage-AC

V

DIF

1

Note 2 0.4 1.18 V

pull-up (external)

+ 0.6 V

Differential

Voltage-DC

V

DIF

1

Note 2 0 .2 V

pull-up (external)

+ 0.6 V

Differential

Crossover Voltage

V

X

1

Note 3 550 958 1100 mV

Skew

t

sk2B

1

VT = 1.5 V 94 200 ps

Jitter, Cycle-to- cycle

t

jcyc-cyc2B

1

VT = V

X

158 250 ps

Notes:

1 - Guaranteed by design, not 100% tested in production.

3 - Vpull-up(external) = 1.5V, Min = (V

pull-up(external)

/2) - 150mV; Max = (V

pull-up(external)

/2) + 150mV

2 - V

DIF

specifies the minimum input differential voltages (VTR-VCP) required for switching, where VTR is the "true"

input level and V

CP

is the "complement" input level.

Electrical Characteristics - SDRAM

TA = 0 - 70C; V

DD

= 3.3V +/-5%; CL = 30 pF (unless otherwise stated)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Output High Voltage V

OH3

IOH = -28 mA 2.4 3 V

Output Low Voltage V

OL3

IOL = 20 mA 0.18 0.4 V

Output H igh Current

I

OH3

VOH = 2.0 V -110 -40

mA

Output Low Current

I

OL3

V

O

L

= 0.8 V 41 86

mA

Rise Time

1

t

r3

V

O

L

= 0.4 V, VOH = 2.4 V 1.42 2 ns

Fall Time

1

t

f3

VOH = 2.4 V, VOL = 0.4 V 1.78 2 ns

Duty Cycle

1

d

t3

VT = 1.5 V 45 56.7 55 %

Skew window

1

t

sk3

VT = 1.5 V 225 250 ps

1

Guaranteed by design, not 100% tested in production.

3.41 ns

Propagation Time

1

(Buffer In to Outp ut)

Tprop

V

T

= 1.5 V

Page 8

8

ICS9248-114

Third party brands and names are the property of their respective owners.

Electrical Characteristics - PCICLK

TA = 0 - 70C; V

DD

= 3.3V +/-5%; CL = 30 pF (unless otherwise stated)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Output High Voltage V

OH1

IOH = -11 mA 2.4 3.15 V

Output Low Voltage V

OL1

IOL = 9.4 mA 0.13 0.4 V

Output H igh Curren t

I

OH1

VOH = 2.0 V -97 -40

mA

Output Low Current

I

OL1

V

O

L

= 0.8 V 41 69

mA

Rise Time

1

t

r1

V

O

L

= 0.4 V, VOH = 2.4 V 1.69 2.0 ns

Fall Time

1

t

f1

VOH = 2.4 V, VOL = 0.4 V 1.75 2.0 ns

Duty Cycle

1

d

t1

VT = 1.5 V 45 51.7 55 %

Skew window

1

t

sk1

VT = 1.5 V 400 500 ps

Jitter,

Cycle-to-Cycle

1

t

jcyc-cyc1

VT = 1.5 V

-500 135 500 ps

1

Guaranteed by design, not 100% tested in production.

Electrical Characteristics - PCICLK_F

TA = 0 - 70C; V

DD

= 3.3V +/-5%; CL = 30 pF (unless otherwise stated)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Output High Voltage V

OH1

IOH = -11 mA 2.4 3.15 V

Output Low Voltage V

OL1

IOL = 9.4 mA 0.13 0.4 V

Output H igh Curren t

I

OH1

VOH = 2.0 V -97 -40

mA

Output Low Current

I

OL1

V

O

L

= 0.8 V 41 69

mA

Rise Time

1

t

r1

V

O

L

= 0.4 V, VOH = 2.4 V 1.90 2.0 ns

Fall Time

1

t

f1

VOH = 2.4 V, VOL = 0.4 V 1.79 2.0 ns

Duty Cycle

1

d

t1

VT = 1.5 V 45 49.9 55 %

Skew window

1

t

sk1

VT = 1.5 V 400 500 ps

Jitter,

Cycle-to-Cycle

1

t

jcyc-cyc1

VT = 1.5 V

-500 110 500 ps

1

Guaranteed by design, not 100% tested in production.

Page 9

9

ICS9248-114

Third party brands and names are the property of their respective owners.

Electrical Characteristics - REF, 48MHz, 24MHz

TA = 0 - 70C; V

DD

= 3.3V +/-5%; CL = 20 pF (unless otherwise stated)

PARAMETER SYMBOL CONDITIONS MI

N

TYP MAX UNITS

Output High Volt age V

OH5

IOH = -16 mA 2.4 3 .03 V

Output Low Voltage V

OL5

IOL = 9 mA 0.23 0.4 V

Output High Current

I

OH5

VOH = 2.0 V -50 -22

mA

Output Low Current

I

OL5

V

O

L

= 0.8 V 16 40

mA

Rise Time

1

t

r5

V

O

L

= 0.4 V, VOH = 2.4 V 1.47 4.0 ns

Fall Time

1

t

f5

VOH = 2.4 V, VOL = 0.4 V 1.98 4.0 ns

Duty Cycle

1

d

t5

VT = 1.5 V 45 54.4 55 %

Jitter,

Cycle-to-Cycle

1

t

jcy

c-cyc5, Ref

VT = 1.5 V 552 1000 ps

Jitter,

Cycle-to-Cycle

1

t

jcyc-cyc5, Fixed

VT = 1.5 V

-1 421 500 ps

1

Guaranteed by design, not 100% tested in production.

Page 10

10

ICS9248-114

Third party brands and names are the property of their respective owners.

1. The ICS clock generator is a slave/receiver, I2C component. It can read back the data stored in the latches for

verification. Read-Back will support Intel PIIX4 "Block-Read" protocol.

2. The data transfer rate supported by this clock generator is 100K bits/sec or less (standard mode)

3. The input is operating at 3.3V logic levels.

4. The data byte format is 8 bit bytes.

5. To simplify the clock generator I

2

C interface, the protocol is set to use only "Block-Writes" from the controller. The

bytes must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte

has been transferred. The Command code and Byte count shown above must be sent, but the data is ignored for those

two bytes. The data is loaded until a Stop sequence is issued.

6. At power-on, all registers are set to a default condition, as shown.

General I2C serial interface information

The information in this section assumes familiarity with I2C programming.

For more information, contact ICS for an I

2

C programming application note.

How to Write:

• Controller (host) sends a start bit.

• Controller (host) sends the write address D2

(H)

• ICS clock will acknowledge

• Controller (host) sends a dummy command code

• ICS clock will acknowledge

• Controller (host) sends a dummy byte count

• ICS clock will acknowledge

• Controller (host) starts sending first byte (Byte 0)

through byte 5

• ICS clock will acknowledge each byte one at a time.

• Controller (host) sends a Stop bit

How to Read:

• Controller (host) will send start bit.

• Controller (host) sends the read address D3

(H)

• ICS clock will acknowledge

• ICS clock will send the byte count

• Controller (host) acknowledges

• ICS clock sends first byte (Byte 0) through byte 5

• Controller (host) will need to acknowledge each byte

• Controller (host) will send a stop bit

Notes:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D3

(H)

A

CK

Byte Count

ACK

Byte 0

ACK

Byte 1

ACK

Byte 2

ACK

Byte 3

ACK

Byte 4

ACK

Byte 5

ACK

Stop Bit

How to Read:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D2

(H)

A

CK

Dummy Command Code

A

CK

Dummy Byte Count

A

CK

Byte 0

A

CK

Byte 1

ACK

Byte 2

A

CK

Byte 3

A

CK

Byte 4

A

CK

Byte 5

A

CK

Stop Bit

How to Write:

Page 11

11

ICS9248-114

Third party brands and names are the property of their respective owners.

Fig. 1

Shared Pin Operation Input/Output Pins

The I/O pins designated by (input/output) on the ICS9248114 serve as dual signal functions to the device. During initial

power-up, they act as input pins. The logic level (voltage)

that is present on these pins at this time is read and stored

into a 5-bit internal data latch. At the end of Power -On reset,

(see AC characteristics for timing values), the device changes

the mode of operations for these pins to an output function.

In this mode the pins produce the specified buffered clocks

to external loads.

T o program (load) the internal configuration register for these

pins, a resistor is connected to either the VDD (logic 1) power

supply or the GND (logic 0) voltage potential. A 10 Kilohm

(10K) resistor is used to provide both the solid CMOS

programming voltage needed during the power-up

programming period and to provide an insignificant load on

the output clock during the subsequent operating period.

Via to

VDD

Clock trace to load

Series Term. Res.

Programming

Header

Via to Gnd

Device

Pad

2K

8.2K

Figure 1 shows a means of implementing this function when

a switch or 2 pin header is used. With no jumper is installed

the pin will be pulled high. With the jumper in place the pin

will be pulled low. If programmability is not necessary, than

only a single resistor is necessary. The programming resistors

should be located close to the series termination resistor to

minimize the current loop area. It is more important to locate

the series termination resistor close to the driver than the

programming resistor.

Page 12

12

ICS9248-114

Third party brands and names are the property of their respective owners.

CPU_STOP# Timing Diagram

CPU_STOP# is an asychronous input to the clock synthesizer. It is used to turn off the CPU clocks for low power operation.

CPU_STOP# is synchronized by the ICS9248-114. The minimum that the CPU clock is enabled (CPU_STOP# high pulse) is

100 CPU clocks. All other clocks will continue to run while the CPU clocks are disabled. The CPU clocks will always be stopped

in a low state and start in such a manner that guarantees the high pulse width is a full pulse. CPU clock on latency is less than

4 CPU clocks and CPU clock off latency is less than 4 CPU clocks.

Notes:

1. All timing is referenced to the internal CPU clock.

2. CPU_STOP# is an asynchronous input and metastable conditions may exist. This signal is synchronized

to the CPU clocks inside the ICS9248-114.

3. All other clocks continue to run undisturbed.

PCICLK

CPUCLKT (1:0)

CPUCLKC0

PD# (High)

CPU_STOP#

INTERNAL

CPUCLK

Page 13

13

ICS9248-114

Third party brands and names are the property of their respective owners.

PD# Timing Diagram

The power down selection is used to put the part into a very low power state without turning off the power to the part. PD# is

an asynchronous active low input. This signal needs to be synchronized internal to the device prior to powering down the clock

synthesizer.

Internal clocks are not running after the device is put in power down. When PD# is active low all clocks need to be driven to a

low value and held prior to turning off the VCOs and crystal. The power up latency needs to be less than 3 mS. The power down

latency should be as short as possible but conforming to the sequence requirements shown below. PCI_STOP# and

CPU_STOP# are considered to be don't cares during the power down operations. The REF and 48MHz clocks are expected to

be stopped in the LOW state as soon as possible. Due to the state of the internal logic, stopping and holding the REF clock

outputs in the LOW state may require more than one clock cycle to complete.

Notes:

1. All timing is referenced to the Internal CPUCLK (defined as inside the ICS9248-1 14 device).

2. As shown, the outputs Stop Low on the next falling edge after PD# goes low.

3. PD# is an asynchronous input and metastable conditions may exist. This signal is synchronized inside this part.

4. The shaded sections on the VCO and the Crystal signals indicate an active clock.

5. Diagrams shown with respect to 133MHz. Similar operation when CPU is 100MHz.

CPUCLKT

CPUCLKC

PCICLK

VCO

Crystal

PD#

Page 14

14

ICS9248-114

Third party brands and names are the property of their respective owners.

Ordering Information

ICS9248yF-114-T

Designation for tape and reel packaging

Pattern Number (2 or 3 digit number for parts with ROM code patterns)

Package Type

F=SSOP

Revision Designator (will not correlate with datasheet revision)

Device Type (consists of 3 or 4 digit numbers)

Prefix

ICS, AV = Standard Device

Example:

ICS XXXX y F - PPP - T

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

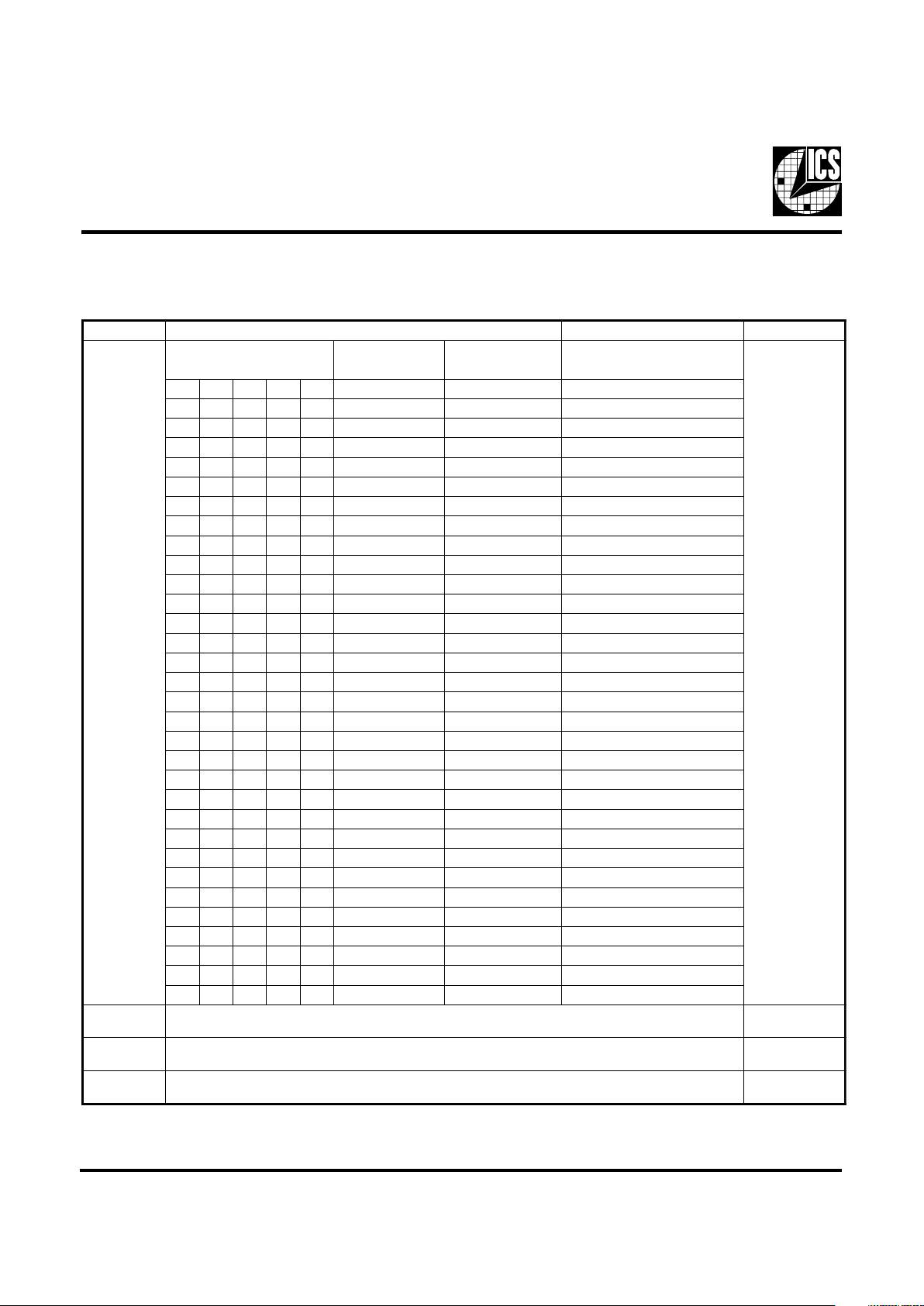

MIN MAX MIN MAX

A 2.413 2.794 .095 .110

A1 0.203 0.406 .008 .016

b 0.203 0.343 .008 .0135

c 0.127 0.254 .005 .010

D

E 10.033 10.668 .395 .420

E1 7.391 7.595 .291 .299

e 0.635 BASIC 0.025 BASIC

h 0.381 0.635 .015 .025

L 0.508 1.016 .020 .040

N

α

0° 8° 0° 8°

VARIATIONS

MIN MAX MIN MAX

48 15.748

16.002

.620 .630

JEDEC MO-118

DOC# 10-0034

6/1/00

REV B

N

D mm.

D (inch)

SEE VARIATIONS

SYMBOL

SEE VARIATIONS

SEE VARIATIONS

In Millimeters

COMMON DIMENSIONS

In Inches

COMMON DIMENSIONS

SEE VARIATIONS

Loading...

Loading...