Page 1

ICS552-03

LOW SKEW 1 TO 8 CLOCK BUFFER (4 AT 1X, 4 AT 1/2X)

Description

The ICS552-03 is a low skew, single input to eight

output clock buffer. Four of the outputs are exact copies

of the input, while the other four are divide by 2 copies

of the input. It is part of ICS’ Clock Blocks

the ICS553 for a 1 to 4 low skew buffer , or the

ICS552-02 for a 1 to 8 low skew buffer without divide by

2. For more than 8 outputs see the MK74CBxxx

Buffalo

ICS makes many non-PLL and PLL based low skew

output devices as well as Z ero Delay Buffers to

synchronize clocks. Contact us for all of your clocking

needs.

TM

series of cloc k drivers.

TM

family. See

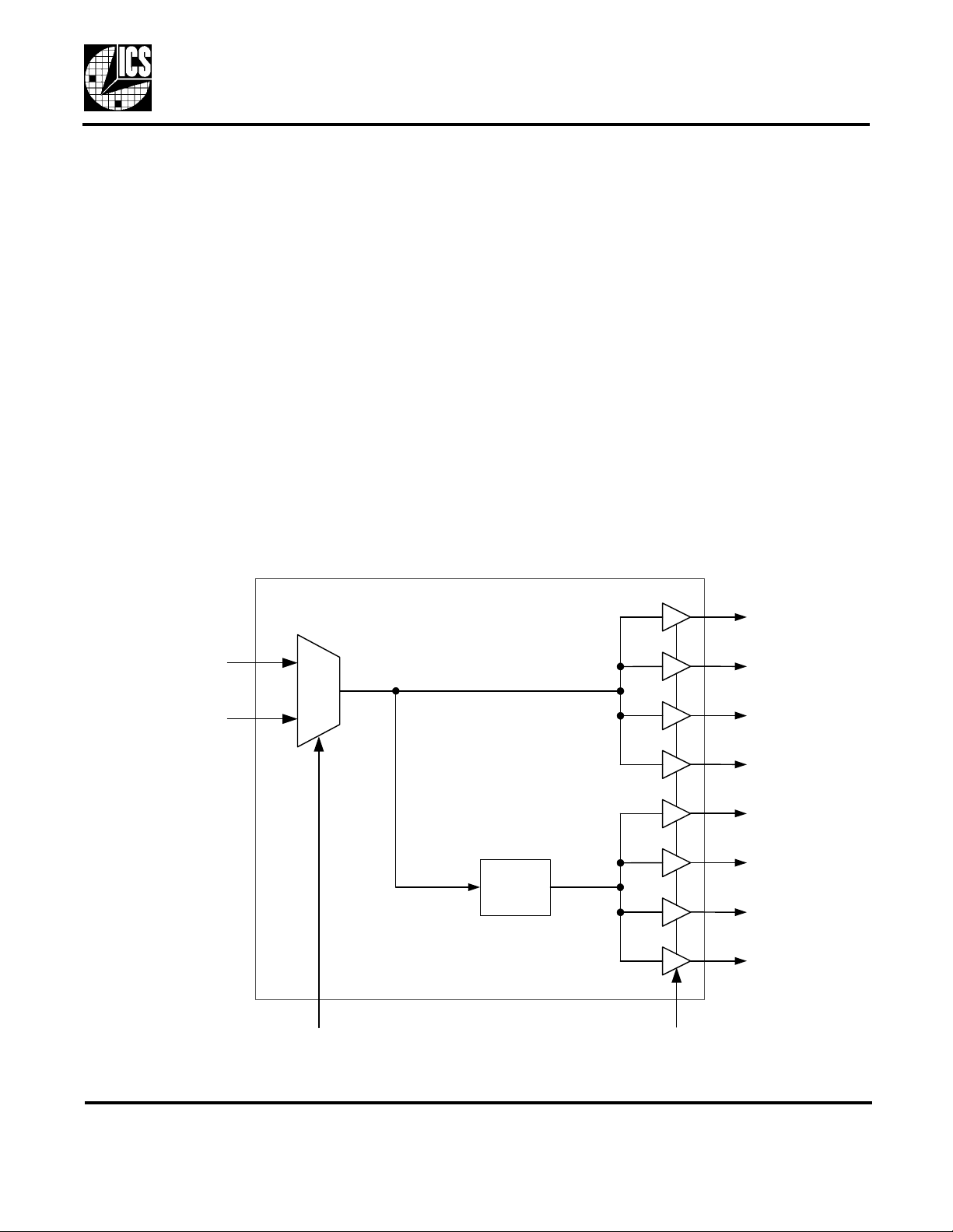

Block Diagram

Features

• Low skew outputs (50 ps maximum)

• Packaged in 16 pin TSSOP

• Low power CMOS technology

• Operating Voltages of 2.5 V to 5 V

• Output Enable pin tri-states outputs

• Low skew between 1X and 1/2X outputs (100 ps

maximum)

• One bank of 4 outputs at 1X

• One bank of 4 outputs at 1/2X

• 5V tolerant input clocks

• Input clock multiplexer

Q0

IN A

IN B

1

0

SELA

Q1

Q2

Q3

P0

P1

Divide

by 2

P2

P3

OE

MDS 552-03 B 1 Revision 052501

Integrated Circuit Systems ● 525 Race Street, San Jose, CA 95 126 ● tel (408) 295-9800 ● www.icst.com

Page 2

LOW SKEW 1 TO 8 CLOCK BUFFER (4 AT 1X, 4 AT 1/2X)

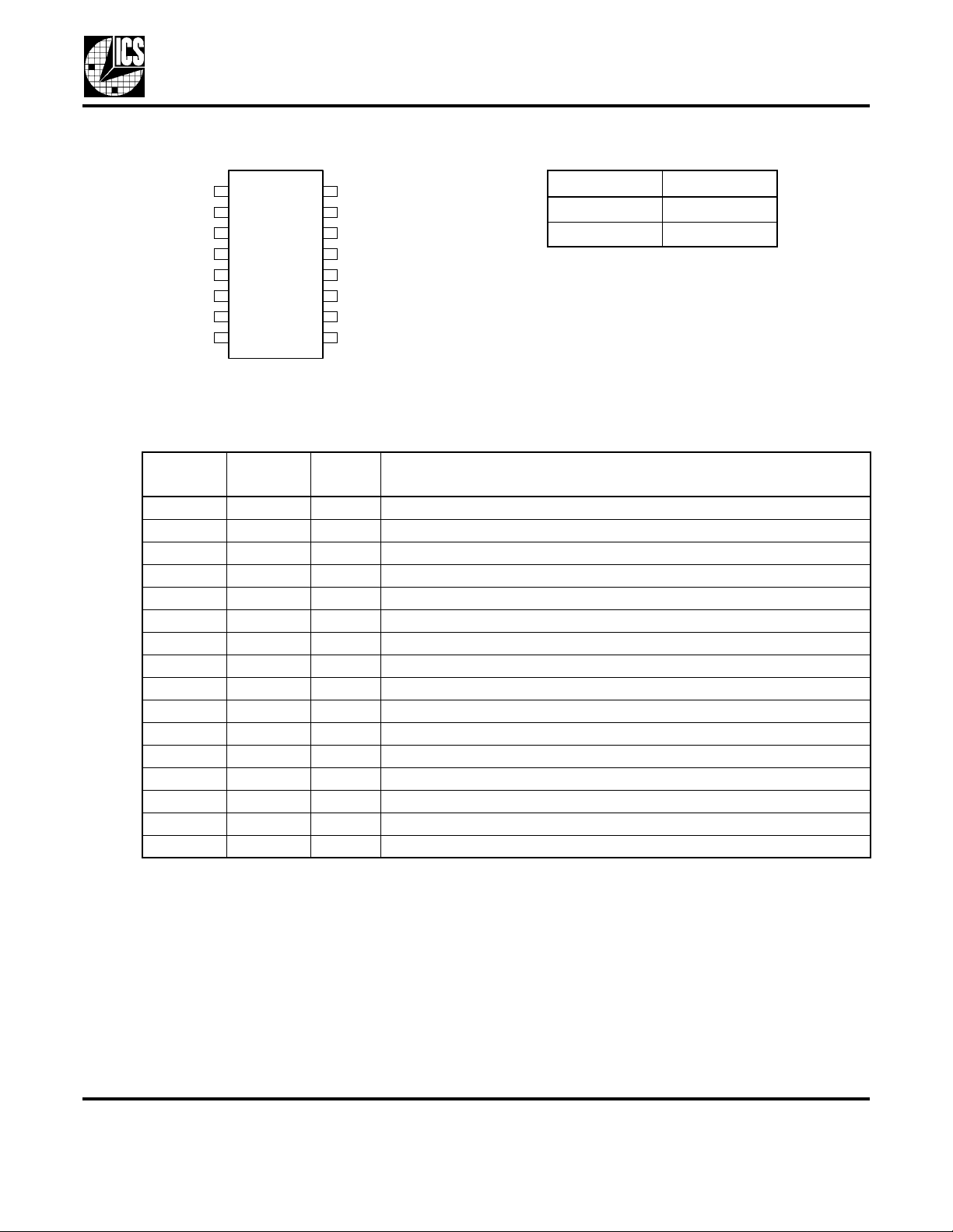

Pin Assignment Input Source Select

ICS552-03

OE

VDD

Q0

Q1

Q2

Q3

GND GND

INB

1

2

3

4

5

6

7

8

16 Pin 173 Mil (0.65mm) TSSOP

Pin Descriptions

Pin

Number

1 OE Input Output Enable. Tri-states outputs when low.Internal Pull-up resistor

2 VDD Power Connect to +2.5 V, +3.3 V or +5.0 V. Must be the same as pin 15

3 Q0 Output Clock Output Q0

4 Q1 Output Clock Output Q1

5 Q2 Output Clock Output Q2

6 Q3 Output Clock Output Q3

7 GND Power Ground

8 INB Input Clock Input B. 5 V tolerant input

9 INA Input Clock Input A. 5 V tolerant input

10 GND Power Ground

11 P0 Output Clock Output P0

12 P1 Output Clock Output P1

13 P2 Output Clock Output P2

14 P3 Output Clock Output P3

15 VDD Power Connect to +2.5 V, +3.3 V or +5.0 V. Must be the same as pin 2

16 SELA Input Selects either INA or INB. Internal pull-up resistor

Pin

Name

16

15

14

13

12

11

10

9

SELA

VDD

P3

P2

P1

P0

INA

Pin

Type

SELA Input

0INB

1INA

Pin Description

External Components

A minimum number of external components are required for proper operation. Decoupling capacitors of

0.01 µF should be connected between VDD on pin 2 and GND on pin 7,and between VDD on pin 15 and

GND on pin 10, as close to the device as possible. A 33 Ω series terminating resistor should be used on

each clock output if the trace is longer than 1 inch.

To achieve the low output skews that the ICS552-03 is capable of, careful attention must be paid to board

layout. Essentially, all 8 outputs must have identical terminations, identical loads, and identical trace

geometries. If they do not, the output skew will be degraded. For example, using a 30Ω series termination

on one output (with 33Ω on the others) will cause at least 15 ps of skew.

MDS 552-03 B 2 Revision 052501

Integrated Circuit Systems ● 525 Race Street, San Jose, CA 95126 ● tel (408) 295-9800 ● www.icst.com

Page 3

Absolute Maximum Ratings

Stresses above the ratings listed below can cause permanent damage to the ICS552-03. These ratings,

which are standard values for ICS commercially rated parts, are stress ratings only . Functional operation of

the device at these or any other conditions above those indicated in the operational sections of the

specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can

affect product reliability. Electrical parameters are guaranteed only over the recommended operating

temperature range.

Item Rating

Supply Voltage, VDD 7 V

All Inputs and Outputs -0.5 V to VDD+0.5 V

Ambient Operating Temperature 0 to +70 °C

Storage Temperature -65 to +150 °C

Junction Temperature 175 °C

Soldering Temperature 260 °C

ICS552-03

LOW SKEW 1 TO 8 CLOCK BUFFER (4 AT 1X, 4 AT 1/2X)

Recommended Operation Conditions

Parameter Min. Typ. Max. Units

Ambient Operating Temperature 0 –+70°C

Power Supply Voltage (measured in respect to GND) +2.375 +5.25 V

DC Electrical Characteristics

VDD=2.5V ±5%, Ambient temperature 0 to +70

Parameter Symbol Conditions Min. Typ. Max. Units

Operating Voltage VDD 2.375 2.625 V

Input High Voltage, INA, INB V

Input Low Voltage, INA, INB V

Input High Voltage, OE, SELA V

Input Low Voltage, OE, SELA V

Output High Voltage V

Output Low Voltage V

Operating Supply Current IDD No load, 100 MHz 20 mA

Short Circuit Current I

OH

OS

IH

IL

IH

IL

OL

Note 1 VDD/2+0.5 5.5 V

Note 1 VDD/2-0.5 V

I

OH

IOL = 16 mA 0.8 V

Each output 60 mA

C, unless stated otherwise

°

2VDDV

0.4 V

= -16 mA 2.4 V

MDS 552-03 B 3 Revision 052501

Integrated Circuit Systems ● 525 Race Street, San Jose, CA 95126 ● tel (408) 295-9800 ● www.icst.com

Page 4

LOW SKEW 1 TO 8 CLOCK BUFFER (4 AT 1X, 4 AT 1/2X)

DC Electrical Characteristics (continued)

VDD=3.3V ±5%, Ambient temperature 0 to +70

Parameter Symbol Conditions Min. Typ. Max. Units

Operating Voltage VDD 3.135 3.465 V

Input High Voltage, INA, INB V

Input Low Voltage, INA, INB V

Input High Voltage, OE, SELA V

Input Low Voltage, OE, SELA V

Output High Voltage V

Output Low Voltage V

Operating Supply Current IDD No load, 100 MHz 25 mA

Short Circuit Current I

IH

IL

IH

IL

OH

OL

OS

C, unless stated otherwise

°

Note 1 VDD/2+0.7 5.5 V

Note 1 VDD/2-0.7 V

I

= -25 mA 2.4 V

OH

IOL = 25 mA 0.8 V

Each output 80 mA

ICS552-03

2VDDV

0.4 V

VDD=5V ±5%, Ambient temperature 0 to +70

Parameter Symbol Conditions Min. Typ. Max. Units

Operating Voltage VDD 4.75 5 .25 V

Input High Voltage, INA, INB V

Input Low Voltage, INA, INB V

Input High Voltage, OE, SELA V

Input Low Voltage, OE, SELA V

Output High Voltage V

Output Low Voltage V

Operating Supply Current IDD No load, 100 MHz 45 mA

Short Circuit Current I

Notes: 1. Nominal switching threshold is VDD/2

AC Electrical Characteristics

VDD = 2.5V ±5%, Ambient Temperature 0 to +70

Parameter Symbol Conditions Min. Typ. Max. Units

Input Frequency 0 160 MHz

Output Rise Time t

Output Fall Time t

Propagation Delay Note 1 6.5 ns

Output to output skew . Between

any two Q outputs

Output to output skew . Between

any two P outputs

Output to output skew . Between

any P to any Q output

Input A to Input B skew. Note 3 0 50 ps

C, unless stated otherwise

°

Note 1 VDD/2+1 5.5 V

IH

Note 1 VDD/2-1 V

IL

2VDDV

0.4 V

OH

OL

OS

IH

IL

I

= -45 mA 2.4 V

OH

IOL = 45 mA 0.8 V

Each output 100 mA

C, unless stated otherwise

°

OR

OF

0.8 to 2.0 V, CL=15 pF 1.5 ns

2.0 to 0.8 V, CL=15 pF 1.5 ns

Note 2 Rising edges at VDD/2 0 50 ps

Note 2 Rising edges at VDD/2 0 50 ps

Note 2 Rising edges at VDD/2 0 100 ps

MDS 552-03 B 4 Revision 052501

Integrated Circuit Systems ● 525 Race Street, San Jose, CA 95126 ● tel (408) 295-9800 ● www.icst.com

Page 5

LOW SKEW 1 TO 8 CLOCK BUFFER (4 AT 1X, 4 AT 1/2X)

AC Electrical Characteristics (continued)

ICS552-03

VDD = 3.3V ±5%, Ambient Temperature 0 to +70

C, unless stated otherwise

°

Parameter Symbol Conditions Min. T yp. Max. Units

Input Frequency 0 200 MHz

Output Rise Time t

Output Fall Time t

Propagation Delay Note 1 5 ns

Output to output skew . Between

any two Q outputs

Output to output skew . Between

any two P outputs

Output to output skew . Between

any P to any Q output

Input A to Input B skew Note 3 0 50 ps

OR

OF

Note 2 Rising edges at VDD/2 0 50 ps

Note 2 Rising edges at VDD/2 0 50 ps

Note 2 Rising edges at VDD/2 0 100 ps

VDD = 5.0V ±5%, Ambient Temperature 0 to +70

0.8 to 2.0 V, CL=15 pF 1.0 ns

2.0 to 0.8 V, CL=15 pF 1.0 ns

C, unless stated otherwise

°

Parameter Symbol Conditions Min. Typ. Max. Units

Input Frequency 0 160 MHz

Output Rise Time t

Output Fall Time t

Propagation Delay Note 1 4 ns

Output to output skew . Between

any two Q outputs

Output to output skew . Between

any two P outputs

Output to output skew . Between

any P to any Q output

Input A to Input B skew Note 3 0 50 ps

OR

OF

Note 2 Rising edges at VDD/2 0 50 ps

Note 2 Rising edges at VDD/2 0 50 ps

Note 2 Rising edges at VDD/2 0 100 ps

0.8 to 2.0 V, CL=15 pF 0.7 ns

2.0 to 0.8 V, CL=15 pF 0.7 ns

Notes: 1. With rail to rail input clock

2. Between any two outputs with equal loading

3. Propagation delay matching through the part

4. Duty cycle on outputs will match incoming clock duty cycle. Consult ICS for tight duty cycle clock

generators.

MDS 552-03 B 5 Revision 052501

Integrated Circuit Systems ● 525 Race Street, San Jose, CA 95126 ● tel (408) 295-9800 ● www.icst.com

Page 6

ICS552-03

LOW SKEW 1 TO 8 CLOCK BUFFER (4 AT 1X, 4 AT 1/2X)

Package Outline and Package Dimensions (16 pin TSSOP, 173 Mil. Body)

Package dimensions are kept current with JEDEC Publication No. 95

Millimeters Inches

Symbol MinMaxMinMax

A -- 1.20 -- 0.047

a 0.05 0.15 0.002 0.006

b 0.19 0.30 0.007 0.012

Index

Area

E

H

c 0.09 0.20 0.0035 0.008

D 4.90 5.10 0.193 0.201

E 4.30 4.50 0.169 0.177

e 0.65 Basic 0.0256 Basic

H 6.40 Basic 0.252 Basic

L 0.45 0.75 0.018 0.030

Pin 1

D

a

be

c

L

A

Ordering Information

Part / Order Number Marking (both) Shipping

packaging

ICS552G-03 ICS (top line) Tubes 16 pin TSSOP 0 to +70 °C

ICS552G-03T 552G-03 (2nd line) Tape and Reel 16 pin TSSOP 0 to +70 °C

While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems (ICS)

assumes no responsibility for either its use or for the infringement of any patent s or other rights of t hird parties, which would

result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial

applications. Any oth er ap pl ic ations such as those req uiri ng extended tempera ture ran ge, high reliabilit y, or other extraordinary

environmental requirements are not recommended without additional processing by ICS. ICS reserves the right to change any

circuitry or specifications without notice. ICS does not authorize or warrant any ICS product for use in life support devices or

critical medical instruments.

Package Temperature

MDS 552-03 B 6 Revision 052501

Integrated Circuit Systems ● 525 Race Street, San Jose, CA 95126 ● tel (408) 295-9800 ● www.icst.com

Loading...

Loading...