Page 1

PRELIMINARY INFORMATION

ICS551

1 to 4 Clock Buffer

Description

The ICS551 is a low cost, high speed single input

to four output clock buffer. Part of ICS’ Clock

BlocksTM family, this is our lowest cost, small clock

buffer. See the ICS552-01B for a monolithic dual

version of the ICS551 in a 20 pin QSOP.

ICS makes many non-PLL and PLL based low

skew output devices, as well as Zero Delay Buffers

to synchronize clocks. Contact us for all of your

clocking needs.

Features

• Packaged in 8 pin SOIC

• Low cost clock buffer

• Low skew (250ps) outputs

• Input/output clock frequency up to 160 MHz

• Operating voltages of 3.0 to 5.5 V

• Non-inverting

• Ideal for networking clocks

• Output Enable mode tri-states outputs

• Full CMOS clock swings with 25mA drive

capability at TTL levels

• Advanced, low power CMOS process

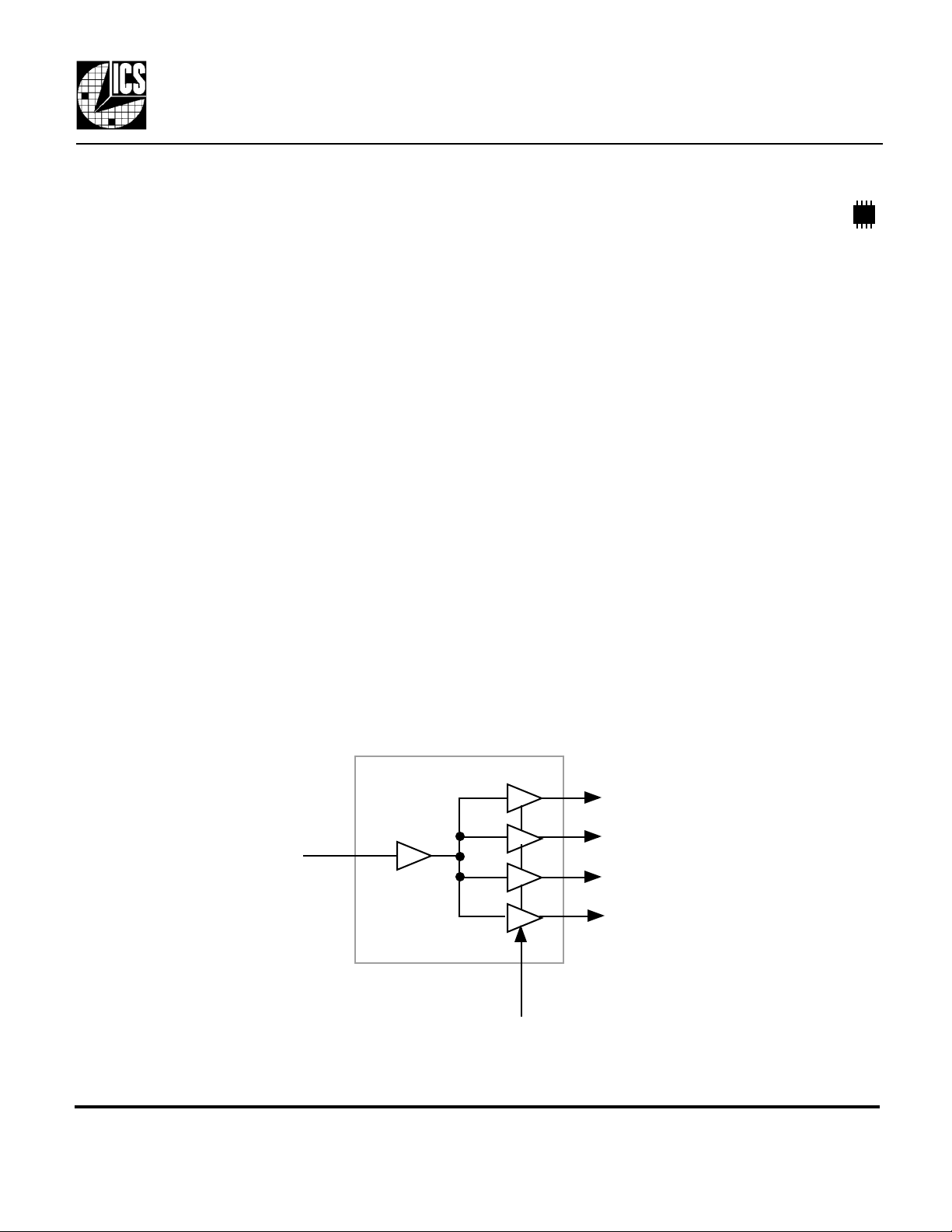

Block Diagram

Q1

Q2

ICLK

Q3

Q4

Output Enable

MDS 551 B 1 Revision 091200 Printed 11/14/00

Integrated Circuit Systems, Inc.•525 Race Street•San Jose•CA•95126•(408)295-9800tel•(408)295-9818fax

Page 2

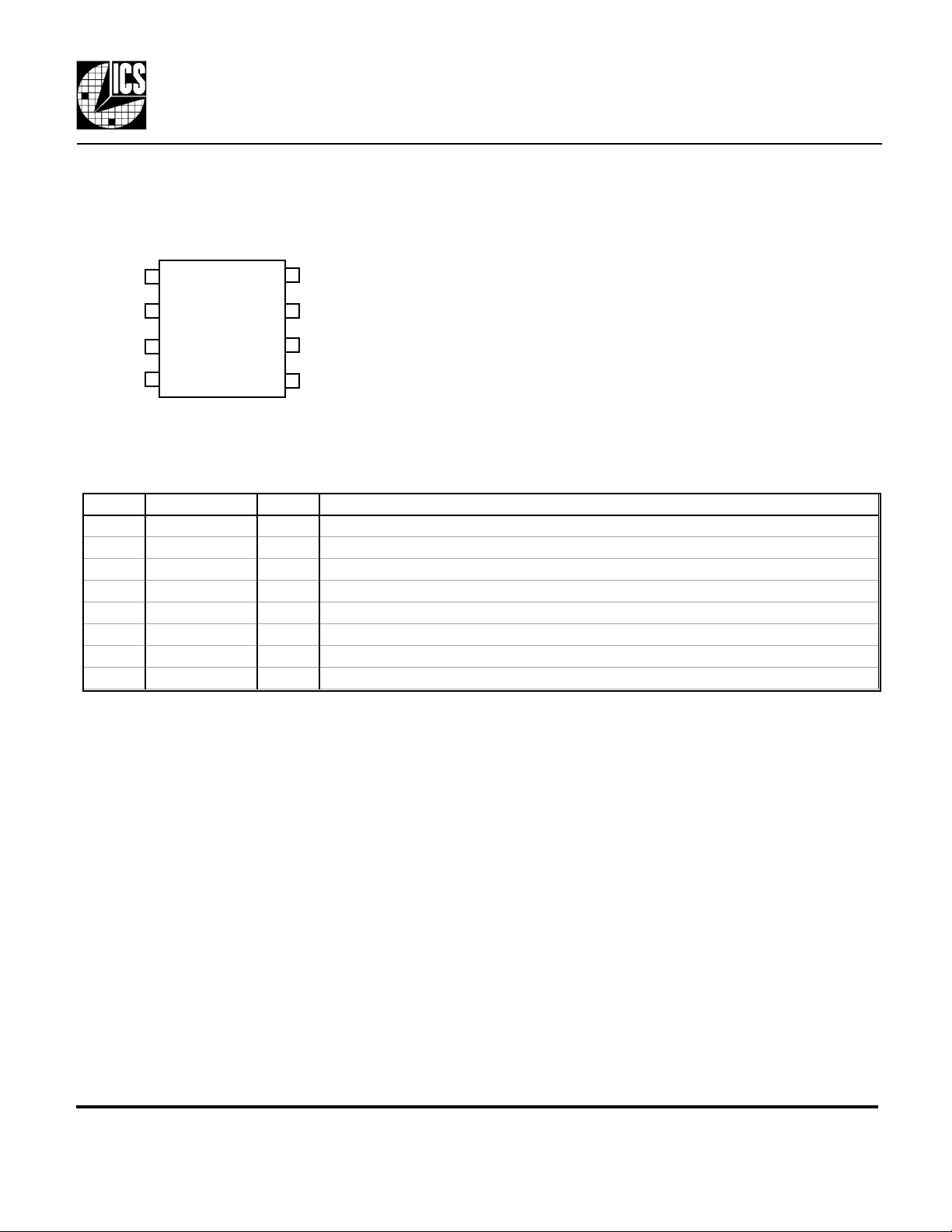

Pin Assignment

PRELIMINARY INFORMATION

ICS551

1 to 4 Clock Buffer

ICLK

Q1

Q2

Q3

1 8

2

3

4

OE

7

VDD

6

GND

5

Q4

8 pin SOIC

Pin Descriptions

Number Name Type Description

1 ICLK CI Clock input. Internal pull-up resistor.

2 Q1 O Clock Output 1.

3 Q2 O Clock Output 2.

4 Q3 O Clock Output 3.

5 Q4 O Clock Output 4.

6 GND P Connect to ground.

7 VDD P Connect to +3.3 V or +5.0 V.

8 OE I Output Enable. Tri-states outputs when low. Internal pull-up resistor.

Key: CI = clock input, I = input, O = output, P = power supply connection

External Components

A minimum number of external components are required for proper operation. A decoupling capacitor of

0.01 µF should be connected between VDD on pin 7 and GND on pin 6, and a 33 Ω terminating resistor

may be used on each clock output if the trace is longer than 1 inch.

MDS 551 B 2 Revision 091200 Printed 11/14/00

Integrated Circuit Systems, Inc.•525 Race Street•San Jose•CA•95126•(408)295-9800tel•(408)295-9818fax

Page 3

PRELIMINARY INFORMATION

exposure to levels above the operating limits but below the Absolute Maximums may affect device reliability.

2. Duty cycle on outputs will match incoming clock duty cycle. Consult ICS for tight duty cycle clock generators.

3. With external series resistor of 33 Ω positioned close to each output pin.

ABSOLUTE MAXIMUM RATINGS (note 1)

ICS551

1 to 4 Clock Buffer

Electrical Specifications

Parameter Conditions Minimum Typical Maximum Units

Supply voltage, VDD Referenced to GND 7 V

Inputs and Clock Outputs Referenced to GND -0.5 VDD+0.5 V

Ambient Operating Temperature 0 70 °C

Soldering Temperature Max of 20 seconds 260 °C

Storage temperature -65 150 °C

DC CHARACTERISTICS

Operating Voltage, VDD 3 5.5 V

Input High Voltage, VIH, IN Clock input VDD/2 + 1 VDD/2 V

Input Low Voltage, VIL, In Clock input VDD/2 VDD/2 - 1 V

Input High Voltage, VIH, OE 2 V

Input Low Voltage, VIL, OE 0.8 V

Output High Voltage, VOH, 5V IOH=-25mA 2.4 V

Output Low Voltage, VOL, 5V IOL=25mA 0.4 V

Output High Voltage, VOH, CMOS level IOH=-8mA VDD-0.4 V

Operating Supply Current, IDD, 3.3V No load, 135 MHz 18 mA

Short Circuit Current, 3.3 V Each output ±50 mA

Internal pull-up resistor All inputs 200 kΩ

AC CHARACTERISTICS

Input Frequency 0 160 MHz

Output Frequency, 3.3 V 15 pF load. Note 3. 160 MHz

Output Frequency, 5 V 15 pF load. Note 3. 135 MHz

Output Clock Rise Time 0.8 to 2.0V 1.5 ns

Output Clock Fall Time 2.0 to 0.8V 1.5 ns

Propagation Delay At 3.3 V 2 4 8 ns

At 5.0 V 1.5 3 6 ns

Output to output skew Rising edges at VDD/2 250 ps

Notes: 1. Stresses beyond those listed under Absolute Maximum Ratings could cause permanent damage to the device. Prolonged

MDS 551 B 3 Revision 091200 Printed 11/14/00

Integrated Circuit Systems, Inc.•525 Race Street•San Jose•CA•95126•(408)295-9800tel•(408)295-9818fax

Page 4

PRELIMINARY INFORMATION

Inches

Millimeters

Package Outline and Package Dimensions

E H

ICS551

1 to 4 Clock Buffer

8 pin SOIC

Q

Pin 1

e

D

Symbol Min Max Min Max

A 0.055 0.068 1.397 1.7272

b 0.013 0.019 0.330 0.483

D 0.185 0.200 4.699 5.080

h x 45°

A

c

b

L

E 0.150 0.160 3.810 4.064

H 0.225 0.245 5.715 6.223

e

h 0.015 0.381

L 0.016 0.035 0.406 0.889

Q 0.004 0.01 0.102 0.254

MDS 551 B 4 Revision 091200 Printed 11/14/00

Integrated Circuit Systems, Inc.•525 Race Street•San Jose•CA•95126•(408)295-9800tel•(408)295-9818fax

Ordering Information

Part/Order Number Marking Package Temperature

ICS551M ICS551M 8 pin SOIC 0 to 70 °C

ICS551MT ICS551M 8 pin SOIC on tape and reel 0 to 70 °C

While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems (ICS) assumes no responsibility for either its use or for the

infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in

normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements

are not recommended without additional processing by ICS. ICS reserves the right to change any circuitry or specifications without notice. ICS does not authorize or warrant any

ICS product for use in life support devices or critical medical instruments.

ClockBlocks is a trademark of ICS

Loading...

Loading...