Page 1

August 1997

ICM7231, ICM7232

Numeric/Alphanumeric Triplexed

LCD Display Drivers

Features

• ICM7231 Drives 8 Digits of 7 Segments with Two

Independent Annunciators Per Digit Address and Data

Input in Parallel Format

• ICM7232 Drives 10 Digits of 7 Segments with Two

Independent Annunciators Per Digit Address and Data

Input in Serial Format

• All Signals Required to Drive Rows and Columns of

Triplexed LCD Display are Provided

• Display Voltage Independent of Power Supply

• On-Chip Oscillator Provides All Display Timing

• Total Power Consumption Typically 200µW, Maximum

500µW at 5V

• Low-Power Shutdown Mode Retains Data With 5µW

Typical Power Consumption at 5V, 1µW at 2V

• Direct Interface to High-Speed Microprocessors

Description

The ICM7231 and ICM7232 family of integrated circuits are

designed to generate the voltage levels and switching waveforms required to drive triplexed liquid-crystal displays.

These chips also include input buffer and digit address

decoding circuitry allowing six bits of input data to be

decoded into 64 independent combinations of the output

segments of the selected digit.

The family is designed to interface to modern highperformance microprocessors and microcomputers and

ease system requirements for ROM space and CPU time

needed to service a display.

Ordering Information

PART NUMBER TEMP. RANGE (oC) PACKAGE NUMBER OF DIGITS INPUT FORMAT PKG. NO.

ICM7231BFIJL -25 to 85 40 Ld CERDIP 8 Digit Parallel F40.6

ICM7231BFIPL -25 to 85 40 Ld PDIP 8 Digit Parallel E40.6

ICM7232BFIPL -25 to 85 40 Ld PDIP 10 Digit Serial E40.6

ICM7232CRIPL -25 to 85 40 Ld PDIP 10 Digit Serial E40.6

NOTE:

All versions intended for triplexed LCD displays.

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

9-19

File Number 3161.1

Page 2

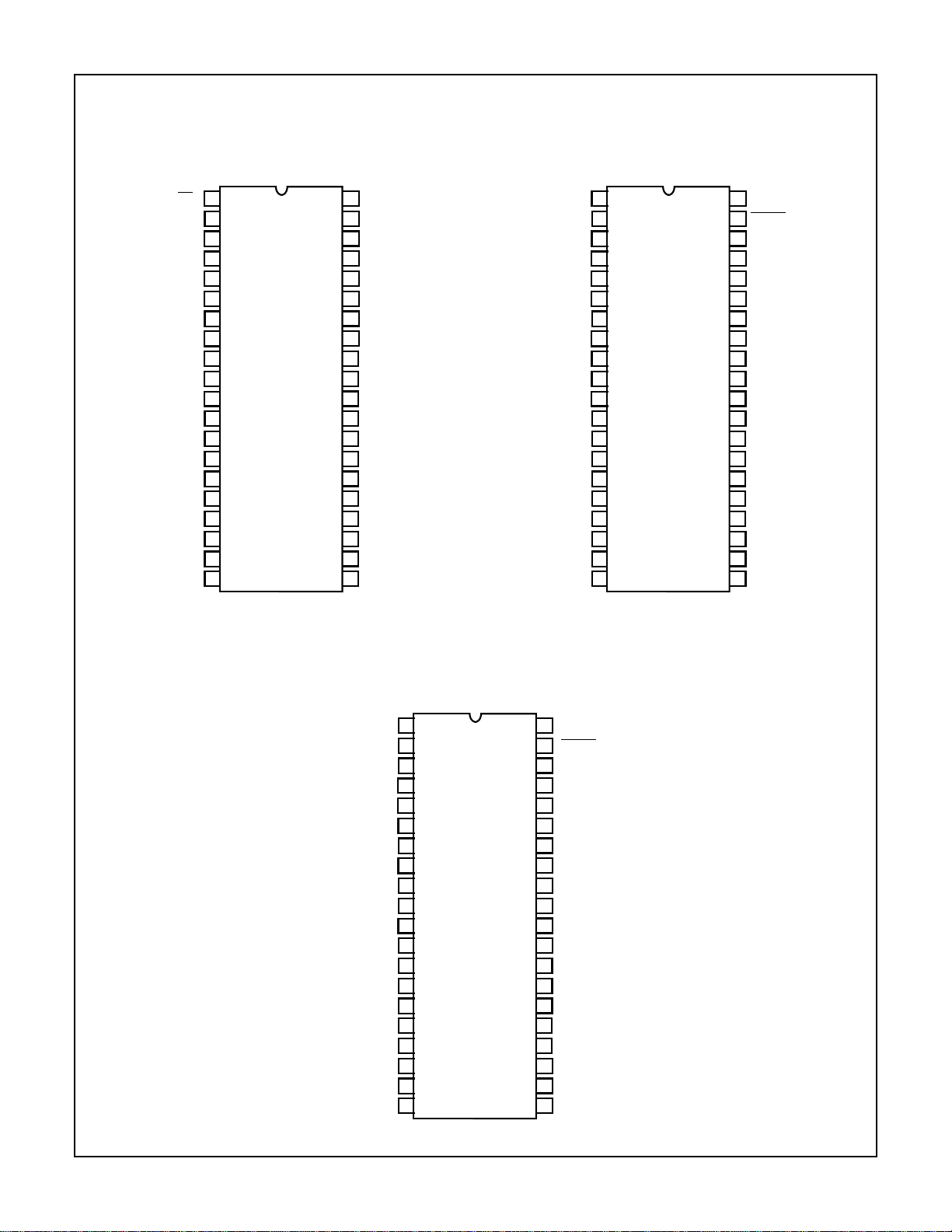

Pinouts

ICM7231BF

(PDIP, CERDIP)

TOP VIEW

ICM7231, ICM7232

ICM7232AF, BF

(PDIP, CERDIP)

TOP VIEW

CS

V

DISP

BP1

BP2

BP3

b1, c1, an11

a1, g1, d1

f1, e1, an21

b2, c2, an12

a2, g2, d2

f2, e2, an22

b3, c3, an13

a3, g3, d3

f3, e3, an23

b4, c4, an14

a4, g4, d4

f4, e4, an24

b5, c5, an15

a5, g5, d5

f5, e5, an25

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

V

DD

A2

39

A1

38

A0

37

V

36

SS

BD3

35

BD2

34

BD1

33

BD0

32

AN2

31

AN1

30

f8, a8, an28

29

a8, g8, d8

28

b8, c8, an18

27

f7, e7, an27

26

a7, g7, d7

25

b7, c7, an17

24

f6, e6, an26

23

a6, g6, d6

22

b6, c6, an16

21

DATA CLOCK

INPUT

V

DISP

BP1

BP2

BP3

b1, c1, an11

a1, g1, d1

f1, e1, an21

b2, c2, an12

a2, g2, d2

f2, e2, an22

b3, c3, an13

a3, g3, d3

f3, e3, an23

b4, c4, an14

a4, g4, d4

f4, e4, an24

b5, c5, an15

a5, g5, d5

f5, e5, an25

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

V

DD

WRITE INPUT

39

DATA INPUT

38

DATA ACCEPTED

37

OUTPUT

36

V

SS

35

f10, e10, an210

34

a10, g10, d10

33

b10, c10, an110

32

f9, e9, an29

31

a9, g9, d9

30

b9, c9, an19

29

f8, a8, an28

a8, g8, d8

28

b8, c8, an18

27

f7, e7, an27

26

25

a7, g7, d7

24

b7, c7, an17

23

f6, e6, an26

22

a6, g6, d6

21

b6, c6, an16

DATA CLOCK

INPUT

V

DISP

BP1

BP2

BP3

b1, c1, an11

a1, g1, d1

f1, e1, an21

b2, c2, an12

a2, g2, d2

f2, e2, an22

b3, c3, an13

a3, g3, d3

f3, e3, an23

b4, c4, an14

a4, g4, d4

f4, e4, an24

b5, c5, an15

a5, g5, d5

f5, e5, an25

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

ICM7232CR

(PDIP)

TOP VIEW

40

V

DD

WRITE INPUT

39

DATA INPUT

38

DATA ACCEPTED

37

OUTPUT

36

V

SS

b6, c6, an16

35

a6, g6, d6

34

f6, e6, an26

33

b7, c7, an17

32

a7, g7, d7

31

30

f7, e7, an27

29

b8, c8, an18

28

a8, g8, d8

27

f8, a8, an28

26

b9, c9, an19

a9, g9, d9

25

f9, e9, an29

24

b10, c10, an110

23

a10, g10, d10

22

f10, e10, an210

21

9-20

Page 3

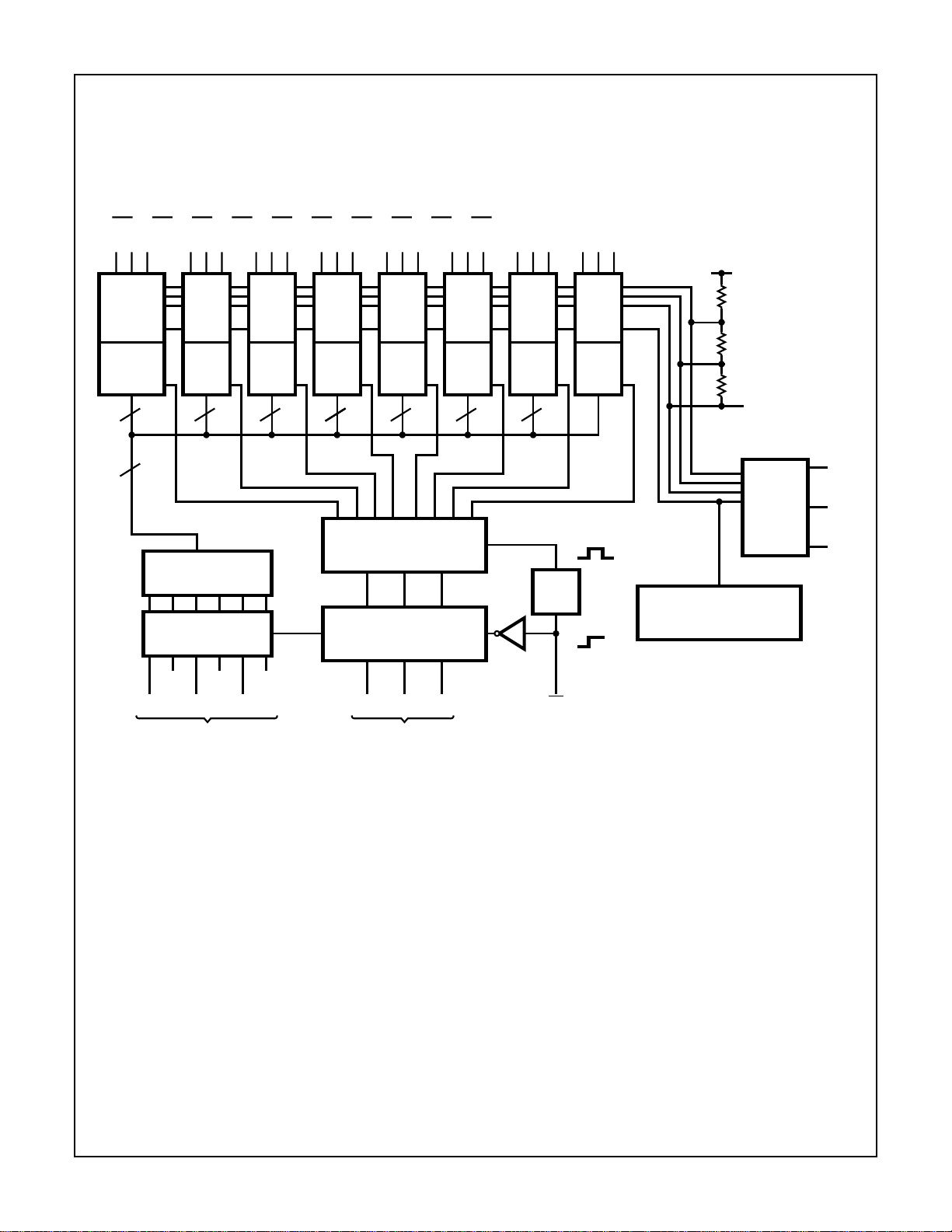

ICM7231, ICM7232

Functional Block Diagrams

ICM7231

D8 D7 D6 D5 D4 D3 D2 D1

f2, e2, an22

SEGMENT

LINE

DRIVERS

3 WIDE

OUTPUT

LATCHES

9 WIDE

99

9 999999

a2, g2, d2

b2, c2, an12

f1, e1, an21

a1, g1, d1

b1, c1, an11

V

DD

ON CHIP

DISPLAY

V

H

VOLTAGE

LEVEL

GENERATOR

V

L

V

DISP

PIN 2 (INPUT)

9

ADDRESS

DAT A

DECODER

DATA INPUT

LATCHES

AN2 BD1 BD3

AN1 BD0 BD2

EN

DECODER

ADDRESS

LATCHES

ADDRESS INPUTSDATA INPUTS

NOTE: See Figure 13 for display segment connections.

DIGIT

INPUT

BP1

COMMON

LINE

DRIVERS

EN

ONE

SHOT

EN

A2A1A0

CS

DISPLAY

TIMING

GENERATOR

BP2

BP3

9-21

Page 4

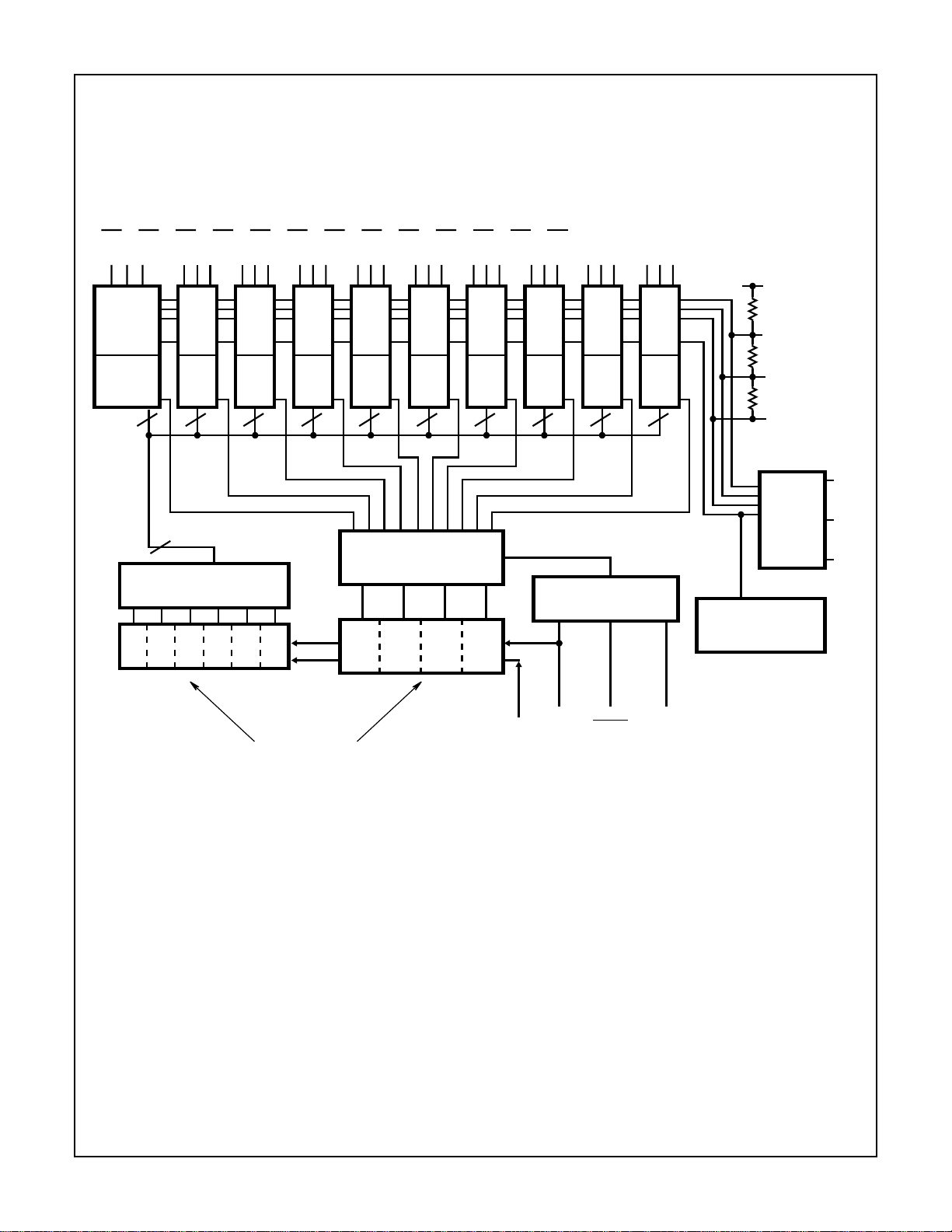

ICM7231, ICM7232

Functional Block Diagrams

(Continued)

ICM7232

9

9

D9 D8

f2, e2, an22

a2, g2, d2

9 9 9 9 9 9 9 9 9

DAT A

DECODER

DIGIT

ADDRESS

DECODER

A2A1A0 A3

EN

SERIAL INPUT

CONTOL LOGIC

CLOCK

DAT A

D10 D7 D6 D5 D4 D3 D2 D1

SEGMENT

LINE

DRIVERS

3 WIDE

OUTPUT

LATCHES

9 WIDE

AN1 BD0 BD2AN2 BD1 BD3

b2, c2, an12

f1, e1, an21

a1, g1, d1

b1, c1, an11

V

DD

ON CHIP

DISPLAY

V

H

VOLTAGE

LEVEL

GENERATOR

V

L

V

DISP

PIN 2 (INPUT)

BP1

COMMON

LINE

DRIVERS

DISPLAY

TIMING

GENERATOR

BP2

BP3

SHIFT REGISTER

SHIFTS RIGHT TO LEFT

ON RISING EDGE OF DATA CLOCK

NOTE: See Figures 13 and 14 for display segment connections.

DAT A

DAT A

INPUT

CLOCK

INPUT OUTPUT

WRITE

INPUT

DAT A

ACCEPTED

9-22

Page 5

ICM7231, ICM7232

Absolute Maximum Ratings Thermal Information

Supply Voltage (VDD - VSS). . . . . . . . . . . . . . . . . . . . . . . . . . . .6.5V

Input Voltage (Note 1). . . . . . . . . . . . . . . . . . . .VSS - 0.3 ≤ VIN≤ 6.5

Display Voltage (Note 1). . . . . . . . . . . . . . . . . . . .0.3 ≤ V

DISP

≤ +0.3

Operating Conditions

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . -25oC to 85oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. Due to the SCR structure inherent in these devices, connecting any displa y terminal or the displa y voltage terminal to a voltage outside

the power supply to the chip may cause destructive device latchup. The digital inputs should never be connected to a voltage less than

-0.3V below ground, but maybe connected to voltages above VDD but not more than 6.5V above VSS.

2. θJA is measured with the component mounted on an evaluation PC board in free air.

Thermal Resistance (Typical, Note 2) θJA (oC/W) θJC (oC/W)

PDIP Package. . . . . . . . . . . . . . . . . . . 60 N/A

CERDIP Package . . . . . . . . . . . . . . . . 50 12

Maximum Junction Temperature

Ceramic Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175oC

Plastic Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150oC

Maximum Storage Temperature Range . . . . . . . . . .-65oC to 150oC

Maximum Lead Temperature (Soldering, 10s) . . . . . . . . . . . .300oC

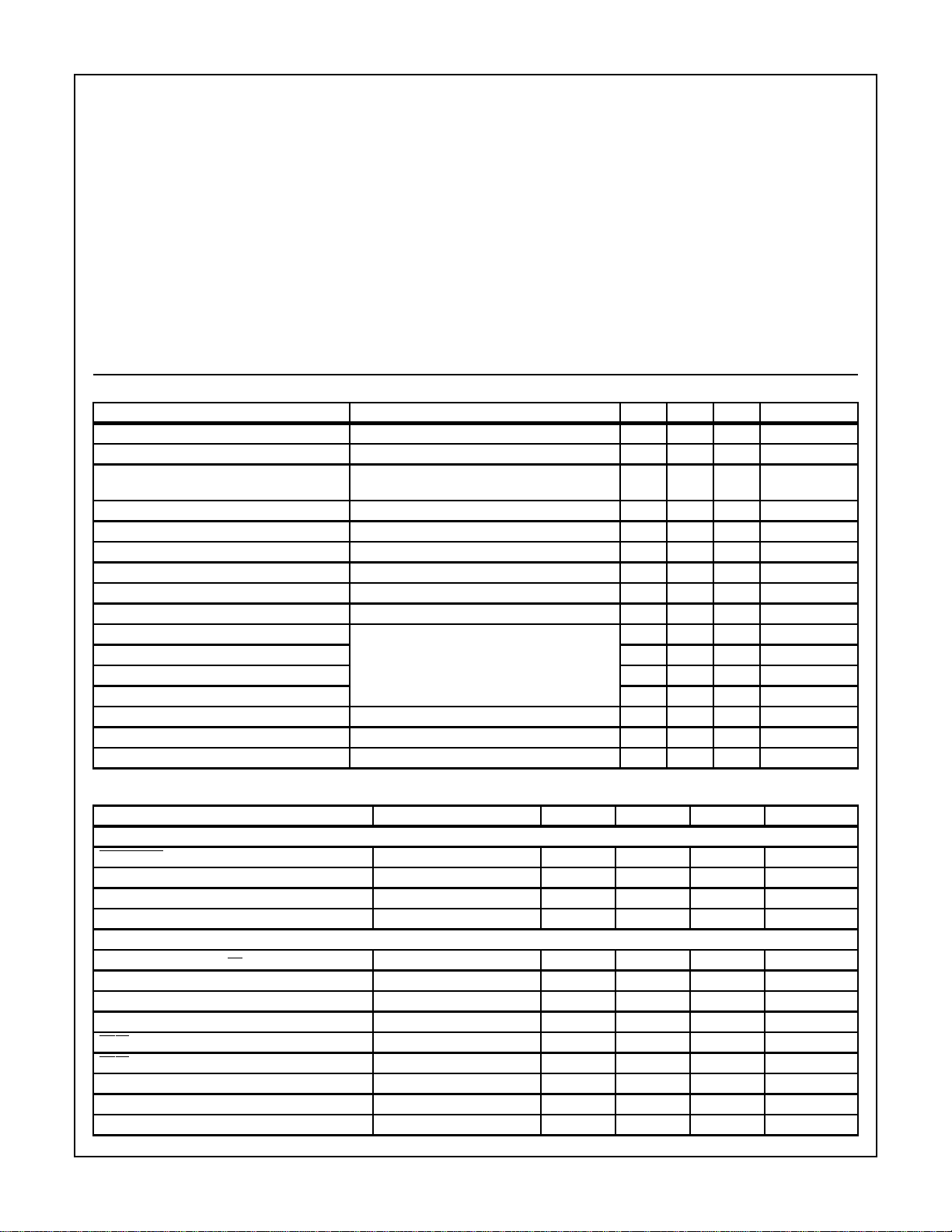

Electrical Specifications V+ = 5V +10%, V

= 0V, TA = -25oC to 85oC, Unless Otherwise Specified

SS

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

Power Supply Voltage, V

Data Retention Supply Voltage, V

Logic Supply Current, I

Shutdown Total Current, I

Display Voltage Range, V

Display Voltage Setup Current, I

Display Voltage Setup Resistor Value, R

DD

DD

S

DISP

DD

DISP

Guaranteed Retention at 2V 2 1.6 - V

Current from VDDto Ground Excluding Display.

V

= 2V

DISP

V

Pin 2 Open - 1 10 µA

DISP

VSS ≤ V

V

DISP

One of Three Identical Resistors in String 40 75 - kΩ

DISP

≤ V

DISP

DD

= 2V, Current from VDDto V

On-Chip - 15 30 µA

DISP

DC Component of Display Signals (Sample Test Only) Display Frame Rate, f

Input Low Level, V

Input High Level, V

Input Leakage, I

Input Capacitance, C

Output Low Level, V

Output High Level, V

DISP

IL

IH

ILK

IN

OL

OH

Operating Temperature Range, T

AC Specifications V

DD

OP

= 5V +10% VSS = 0V, -25oC to 85oC

See Figure 5 60 90 120 Hz

ICM7231, Pins 30 - 35, 37 - 39, 1

ICM7232, Pins 1, 38, 39 (Note 2)

Pin 37, ICM7232, IOL = 1mA - - 0.4 V

VDD = 4.5V, IOH = -500µA 4.1 - - V

Industrial Range -25 - +85

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

PARALLEL INPUT (ICM7231) See Figure 1

Chip Select Pulse Width, t

Address/Data Setup Time, t

Address/Data Hold Time, t

Inter-Chip Select Time, t

ICS

CS

DS

DH

(Note 1) 500 350 - ns

(Note 1) 200 - - ns

(Note 1) 0 -20 - ns

(Note 1) 3 - - µs

SERIAL INPUT (ICM7232) See Figures 2, 3

Data Clock Low Time, t

Data Clock High Time, t

Data Setup Time, t

Data Hold Time, t

Write Pulse Width, t

CL

CL

DS

DH

WP

Write Pulse to Clock at Initialization, t

Data Accepted Low Output Delay, t

Data Accepted High Output Delay, t

Write Delay After Last Clock, t

CWS

WLL

ODL

ODH

(Note 1) 350 - - ns

(Note 1) 350 - - ns

(Note 1) 200 - - ns

(Note 1) 0 -20 - ns

(Note 1) 500 350 - ns

(Note 1) 1.5 - - µs

(Note 1) - 200 400 ns

(Note 1) - 1.5 3 µs

(Note 1) 350 - - ns

4.5 >4 5.5 V

- 30 100 µA

0-VDDV

1

/

1% (VDD - V

4

DISP

- - 0.8 V

2.0 - - V

- 0.1 1 µA

-5- pF

o

C

)

9-23

Page 6

ICM7231, ICM7232

Table of Features

TYPE NUMBER OUTPUT CODE ANNUNCIATOR LOCATIONS INPUT OUTPUT

ICM7231BF Code B Both Annunciators on BP3 Parallel Entry, 4-bit Data, 2-bit

Annunciators, 3-bit Address

ICM7232AF Hexadecimal Both Annunciators on BP3 Serial Entry, 4-bit Data, 2-bit

ICM7232BF Code B

ICM7232CR Code B 1 Annunciator BP1

1 Annunciator BP3

Annunciators, 4-bit Address

Terminal Definitions

TERMINAL PIN NO. DESCRIPTION FUNCTION

ICM7231 PARALLEL INPUT NUMERIC DISPLAY

AN1 30 Annunciator 1 Control Bit High = ON

AN2 31 Annunciator 2 Control Bit Low = OFF See Table 3

BD0 32 Least Significant

BD1 33

BD2 34

BD3 35 Most Significant

A0 37 Least Significant

A1 38

A2 39 Most Significant

CS 1 Data Input Strobe/Chip Select (Note 2) Trailing (Positive going) edge latches data, causes data input to be

ICM7232 SERIAL DATA AND ADDRESS INPUT

Data Input 38 Data+ Address Shift Register Input HIGH = Logical One (1)

WRITE Input 39 Decode, Output, and Reset Strobe When DA TA ACCEPTED Output is LOW, positive going edge ofWRITE

Data Clock

Input

DATA

ACCEPTED

Output

ALL DEVICES

Display

Voltage

V

DlSP

Common

Line Driver

Outputs

Segment

Line Driver

Outputs

V

DD

V

SS

NOTES:

1. For Design reference only, not 100% tested.

2. CS has a special “mid-level” sense circuit that establishes a test mode if it is held near 3V for several ms. Inadvertent triggering of this

mode can be avoided by pulling it high when inactive, or ensuring frequent activity.

1 Data Shift Register and Control Logic

Clock

37 Handshake Output Output LOW when correct number of bits entered into shift register.

2 Negative end of on-chip resistor string

used to generate intermediate voltage

levels for display. Shutdown Input.

3, 4, 5 Drive display commons, or rows

6 - 29

6 - 35

(On ICM7231)

(On ICM7232)

40 Chip Positive Supply

36 Chip Negative Supply

4-bit Binary

Data Inputs

3-bit Digit

Address Inputs

Input

Data

(See Table 1)

Input

Address

(See Table 2)

decoded and sent out to addressed digit

LOW = Logical Zero (O)

causes data in shift register to be decoded and sent to addressed digit,

then shift register and control logic to be reset. When DAT A A CCEPTED

Output is HIGH, positive going edge of WRITE triggers reset only.

Positive going edge advances data in shift register. ICM7232: Eleventh edge resets shift register and control logic.

Display voltage control. When open (or less than 1V from VDD) chip

is shutdown; oscillator stops, all display pins to VDD.

Drive display segments, or columns.

HIGH = Logical One (1)

LOW = Logical Zero (0)

8 Digits plus

16 Annunciators

10 Digits plus

20 Annunciators

9-24

Page 7

Timing Diagrams

CS

INPUT

ICM7231, ICM7232

t

CS

t

ICS

DAT A

ADDRESS

INPUT

DAT A

CLOCK

INPUT

(PER BIT

OF DATA)

DAT A

INPUT

DAT A

ACCEPTED

OUTPUT

WRITE

INPUT

t

WLL

ADDRESS

AND DATA

INPUTS VALID

t

DS

t

DH

ADDRESS

AND DATA

INPUTS VALID

DO NOT CARE

FIGURE 1. ICM7231 INPUT TIMING DIAGRAM

ELEVENTH CLOCK

WITH NO

t

CI

t

CI

1 2 3 8 9 10

AN1

DATA

VALID

t

DS

t

WP

AN2

DATA

VALID

t

DH

BD0

DATA

VALID

t

ODL

A1

DATA

VALID

WRITE PULSE

RESETS SR + LOGIC

A2

DATA

VALID

t

CWS

DATA

VALID

A3

t

ODH

t

ODL

t

WP

RESETS SHIFT REGISTER

AND INPUT CONTROL

LOGIC WHEN DATA

ACCEPTED HIGH

DO NOT CARE

DECODES AND STORES

DATA, RESETS SHIFT

REGISTER AND LOGIC

WHEN DATA ACCEPTED

IS LOW

FIGURE 2. ICM7232 ONE DIGIT INPUT TIMING DIAGRAM, WRITING BOTH ANNUNCIATORS

9-25

Page 8

Timing Diagrams

ICM7231, ICM7232

DAT A

CLOCK

INPUT

DAT A

INPUT

DAT A

ACCEPTED

OUTPUT

WRITE

INPUT

t

WLL

AN1

ENTER

FIRST

t

CI

t

DS

AN2 BD0 BD1 BD2 BD3 A0 A1 A2 A3

ICM7232 WRITE ORDER

t

CI

1 2 3 7 8

t

DH

BD0

DATA

VALID

t

WP

RESETS SHIFT REGISTER

AND INPUT CONTROL

LOGIC WHEN DATA

ACCEPTED HIGH

BD1

DATA

VALID

BD2

DATA

VALID

DO NOT CARE

A2

DATA

VALID

t

t

ODI

CWS

A3

DATA

VALID

t

ENTER

LAST

t

ODH

WP

DECODES AND STORES

DATA, RESETS SHIFT

REGISTER AND LOGIC

WHEN DATA ACCEPTED

IS LOW

FIGURE 3. ICM7232 INPUT TIMING DIAGRAM, LEAVING BOTH ANNUNCIATORS OFF

ICM7231 Family Description

The ICM7231 drives displays with 8 sev en-segment digits with

two independent annunciators per digit, accepting six data

bits and three digit address bits from parallel inputs controlled

by a chip select input. The data bits are subdivided into four

binary code bits and two annunciator control bits.

The ICM7232 drives 10 seven-segment digits with two independent annunciators per digit. To write into the display, six

bits of data and four bits of digit address are clocked serially

into a shift register, then decoded and written to the display.

Input levels are TTL compatible, and the DATA ACCEPTED

output on the serial input devices will drive one LSTTL load.

The intermediate voltage levels necessary to drive the display properly are generated by an on-chip resistor string,

and the output of a totally self-contained on-chip oscillator is

used to generate all display timing. All devices in this family

have been fabricated using Intersil’ MAXCMOS process

and all inputs are protected against static discharge.

Triplexed (

Figure 4 shows the connection diagram for a typical

7-segment display with two annunciators such as would be

used with an ICM7231 or ICM7232 numeric display driver.

Figure 5 shows the voltage waveforms of the common lines

1

/3 Multiplexed) Liquid Crystal Displays

and one segment line, chosen for this example to be the “a,

g, d” segment line. This line intersects with BP1 to form the

“a” segment, BP2 to form the “g” segment and BP3 to form

the “d” segment. Figure 5 also shows the wav ef orm of the “a,

g, d” segment line for four different ON/OFF combinations of

the “a”, “g” and “d” segments. Each intersection (segment or

annunciator) acts as a capacitance from segment line to

common line, shown schematically in Figure 6. Figure 7

shows the voltage across the “g” segment for the same four

combinations of ON/OFF segments used in Figure 5.

SEGMENT LINES

BP1

a

f

b

g

e

c

d

an2 an1

SEGMENT LINE CONNECTIONS

BP2

an2 an1

BP3

BACKPLANE CONNECTIONS

FIGURE 4. CONNECTION DIAGRAMS FOR TYPICAL

7-SEGMENT DISPLAYS

a

f

b

g

e

c

d

MAXCMOS is a registered trademark of Intersil Corporation.

9-26

Page 9

ICM7231, ICM7232

φ1 φ2 φ3 φ1´ φ2´ φ3´

V

DD

V

BP1

BP2

BP3

SEGMENT

LINE

ALL OFF

a SEGMENT

ON

a, d OFF

a, g ON

d OFF

ALL ON

NOTES:

1. φ1, φ2, φ3, - BP High with Respect to Segment.

2. φ1´, φ2´, φ3´, - BP Low with Respect to Segment.

3. BP1 Active during φ1, and φ1´.

4. BP2 Active during φ2, and φ2´.

5. BP3 Active during φ3, and φ3´.

FIGURE 5. DISPLAY VOLTAGE WAVEFORMS

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

H

L

DISP

DD

H

L

DISP

DD

H

L

DISP

DD

H

L

DISP

DD

H

L

DISP

DD

H

L

DISP

DD

H

L

DISP

V

P

COMMON LINE

WAVEFORMS

ON CHIP

RESISTOR

STRING

V

DD

~75kΩ

V

H

~75kΩ

V

L

~75kΩ

PIN 2

V

DISP

INPUT

TYPICAL

SEGMENT LINE

WAVEFORMS

BP1

BP2

BP3

f

e

an2

a

g

d

FIGURE 6. DISPLAY SCHEMATIC

VP = (V+) - VDISP

φ1 φ2 φ3 φ1´ φ2´ φ3´

ALL OFF

RMS

VP

------- - V

3

11

----------

3

a SEGMENT

ON

a, d OFF

a, g ON

d OFF

ALL ON

V

V

RMS

b

c

an1

RMS

VP

--------

× V

3

SEGMENT

LINES

OFF==

ON==

RMS

+VP

0

-VP

+VP

0

-VP

+VP

0

-VP

+VP

0

-VP

The degree of polarization of the liquid crystal material and

thus the contrast of any intersection depends on the RMS

voltage across the intersection capacitance. Note from

Figure 7 that the RMS OFF voltage is always V

the RMS ON voltage is always 1.92V

1

For a

/3 multiplexed LCD, the ratio of RMS ON to OFF

PEAK

/3.

/3 and that

P

voltages is fixed at 1.92, achieving adequate display contrast

with this ratio of applied RMS voltage makes some demands

on the liquid crystal material used.

Voltage Contrast Ratio

V

RMS

----------------------------- -

OFF

V

RMS

11

---------- 1.92===

3

ON

NOTES:

1. φ1, φ2, φ3, - BP High with Respect to Segment.

2. φ1´, φ2´, φ3´, - BP Low with Respect to Segment.

3. BP1 Active during φ1, and φ1´.

4. BP2 Active during φ2, and φ2´.

5. BP3 Active during φ3, and φ3´.

FIGURE 7. VOLTAGE WAVEFORMS ON SEGMENT g(VG)

9-27

Page 10

ICM7231, ICM7232

Figure 8 shows the curve of contrast versus applied RMS voltage for a liquid crystal material tailored for V

typical value for

that the RMS OFF voltage V

1

/3 multiplexed displays in calculators. Note

/3 ≈ 1V is just below the

PEAK

PEAK

= 3.1V, a

“threshold” voltage where contrast begins to increase. This

places the RMS ON voltage at 2.1V, which provides about

85% contrast when viewed straight on.

0+

0-

100

T

= 25oC

A

90

80

V

1.1V

θ = -30

=

OFF

RMS

APPLIED VOLTAGE (V

70

60

50

40

CONTRAST (%)

30

20

10

0

01234

FIGURE 8. CONTRAST vs APPLIED RMS VOLTAGE

θ = -10

o

o

θ = +10

θ = 0

o

VON = 2.1V

)

RMS

All members of the ICM7231 and ICM7232 family use an internal

resistor string of three equal value resistors to generate the voltages used to drive the display. One end of the string is connected

on the chip to V

pin 2 (V

DISP

(V

) to be optimized for the particular liquid crystal material

DISP

used. Remember that V

and the other end (user input) is available at

DD

) on each chip. This allows the display voltage input

PEAK

= VDD - V

and should be

DISP

three times the threshold voltage of the liquid crystal material

used. Also it is very important that pin 2 never be driven below

V

. This can cause device latchup and destruction of the chip.

SS

Temperature Effects and Temperature Compensation

The performance of the LCD material is affected by temperature in two ways. The response time of the display to changes

of applied RMS voltage gets longer as the display temperature drops. At very low temperatures (-20oC) some displays

may take se v eral seconds to change a ne w character after the

new information appears at the outputs. However, for most

applications above 0

o

C this will not be a problem with available multiplexed LCD materials, and for low-temperature

applications, high-speed liquid crystal materials are available.

At high temperature, the effect to consider deals with plastic

materials used to make the polarizer.

Some polarizers become soft at high temperatures and permanently lose their polarizing ability, thereby seriously

degrading display contrast. Some displays also use sealing

materials unsuitable for high temperature use. Thus, when

specifying displays the following must be kept in mind: liquid

crystal material, polarizer, and seal materials.

A more important effect of temperature is the variation of

threshold voltage. For typical liquid crystal materials suitable for

multiplexing, the peak voltage has a temper ature coefficient of -7

to -14mV/

old voltage goes down. Assuming a fixed value for V

threshold voltage drops below V

o

C. This means that as temperature rises, the thresh-

, when the

/3 OFF segments begin to

PEAK

P

be visible. Figure 9 shows the temperature dependence of peak

voltage for the same liquid crystal material of Figure 8.

6

5

4

3

2

PEAK VOLTAGE

1

0

-100 1020304050

FIGURE 9. TEMPERATURE DEPENDENCE OF LC THRESHOLD

PEAK VOLTAGE FOR

10% CONTRAST (OFF)

PEAK VOLTAGE FOR

90% CONTRAST (ON)

AMBIENT TEMPERATURE (oC)

For applications where the display temperature does not

vary widely, V

make the RMS OFF voltage, V

may be set at a fixed voltage chosen to

PEAK

/3, just below the thresh-

PEAK

old voltage at the highest temperature expected. This will

prevent OFF segments turning ON at high temperature (this

at the cost of reduced contrast for ON segments at low

temperatures).

For applications where the display temperature may vary to

wider extremes, the display voltage V

(and thus V

DISP

PEAK

may require temperature compensation to maintain sufficient

contrast without OFF segments becoming visible.

Display Voltage and Temperature Compensation

These circuits allow control of the display peak voltage by

bringing the bottom of the voltage divider resistor string out at

pin 2. The simplest means for generating a display voltage

suitable to a particular display is to connect a potentiometer

from pin 2 to V

as shown in Figure 10. A potentiometer with

SS

a maximum value of 200kΩ should give sufficient range of

adjustment to suit most displays. This method for generating

display voltage should be used only in applications where the

temperature of the chip and display won’t vary more than

o

±5

C (±9oF), as the resistors on the chip have a positive temperature coefficient, which will tend to increase the display

peak voltage with an increase in temperature. The display

voltage also depends on the power supply voltage, leading to

tighter tolerances for wider temperature ranges.

)

9-28

Page 11

ICM7231, ICM7232

OPEN

200kΩ

FIGURE 10. SIMPLE DISPLAY VOLTAGE ADJUSTMENT

240

V

DISP

10nF

ICM7231

ICM7232

+5

36

Figure 11A shows another method of setting up a display

voltage using five silicon diodes in series. These diodes,

1N914 or equivalent, will each have a forward drop of

approximately 0.65V, with approximately 20µA flowing

through them at room temperature. Thus, 5 diodes will give

3.25V, suitable for a 3V display using the material properties

shown in Figures 4 and 5. For higher voltage displays, more

diodes may be added. This circuit provides reasonable

temperature compensation, as each diode has a negative

temperature coefficient of -2mV/

o

-10mV/

C, not far from optimum for the material described.

o

C; five in series gives

The disadvantage of the diodes in series is that only integral

multiples of the diode voltage can be achieved. The diode

voltage multiplier circuit shown in Figure 11B allows finetuning the display voltage by means of the potentiometer ; it

likewise provides temperature compensation since the temperature coefficient of the transistor base-emitter junction

(about -2mV/

o

C) is also multipled. The transistor should have

a beta of at least 100 with a collector current of 10µA. The

inexpensive 2N2222 shown in the figure is a suitable device.

V

DD

1N914

DIODES

40kΩ

FIGURE 11A. STRING OF DIODES

V

DD

POTENTIOMETER

200kΩ

FIGURE 11B. TRANSISTOR-MULTIPLIER

FIGURE 11. DIODE-BASED TEMPERATURE COMPENSATION

2N2222

40kΩ

240

V

DISP

ICM7231

ICM7232

10nF

240

10nF

36

V

DISP

ICM7231

ICM7232

+5

+5

36

For battery operation, where the display voltage is gener ally the

same as the battery voltage (usually 3 - 4.5V), the chip may be

operated at the display voltage, with V

connected to VSS.

DlSP

The inputs of the chip are designed such that they may be

driven above V

without damaging the chip. This allows, for

DD

example, the chip and display to oper ate at a regulated 3V, and

a microprocessor driving its inputs to operate with a less well

controlled 5V supply. (The inputs should not be driven more

than 6.5V above GND under any circumstances.) This also

allows temperature compensation with the ICL7663S, as

shown in Figure 12. This circuit allows independent adjustment

of both voltage and temperature compensation.

+5V

VIN+

V

OUT1

V

LOGIC

SYSTEM

PROCESSOR,

ETC.

FIGURE 12. FLEXIBLE TEMPERATURE COMPENSATION

OUT2

ICL7663S

V

SET

V

GND

1.8MΩ

300kΩ

TC

2.7MΩ

DATA BUS

V

DD

ICM7233

V

DISP

GND

Description Of Operation

Parallel Input Of Data And Address (ICM7231)

The parallel input structure of the ICM7231 device is

organized to allow simple, direct interfacing to all microprocessors, (see the Functional Block Diagram). In the

ICM7231, address and data bits are written into the input

latches on the rising edge of the Chip Select input.

The rising edge of the Chip Select also triggers an on-chip

pulse which enables the address decoder and latches the

decoded data into the addressed digit/character outputs. The

timing requirements for the parallel input device are shown in

Figure 1, with the values for setup , hold, and pulse width times

shown in the AC Specifications section. Note that there is a

minimum time between Chip Select pulses; this is to allow sufficient time for the on-chip enable pulse to deca y, and ensures

that new data doesn’t appear at the decoder inputs before the

decoded data is written to the outputs.

Serial Input Of Data And Address (ICM7232)

The ICM3232 trades six pins used as data inputs on the

ICM7231 for six more segment lines, allowing two more

9-segment digits. This is done at the cost of ease in interfacing, and requires that data and address information be

entered serially. Refer to Functional Block Diagram and timing diagrams, Figures 2 and 3. The interface consists of four

pins: DATA Input, DATA CLOCK Input,

DATA ACCEPTED Output. The data present at the DATA

Input is clocked into a shift register on the rising edge of the

WRITE Input and

9-29

Page 12

ICM7231, ICM7232

DATA CLOCK Input signal, and when the correct number of

bits has been shifted into the shift register (8 in the

ICM7232), the DATA ACCEPTED Output goes low . F ollo wing

this, a low-going pulse at the

WRITE input will trigger the

chip to decode the data and store it in the output latches of

the addressed digit/character. After the data is latched at the

outputs, the shift register and the control logic are reset,

returning the DATA ACCEPTED Output high. After this occurs,

a pulse at the WRITE input will not change the outputs, but

will reset the control logic and shift register, assuring that each

data bit will be entered into the correct position in the shift register depending on subsequent DATA CLOCK inputs.

The shift register and control logic will also be reset if too

many DATA CLOCK INPUT edges are received; this prevents incorrect data from being decoded. In the ICM7232,

the eleventh clock resets the shift register and control logic.

The recommended procedure for entering data is shown in

the serial input timing diagram, Figure 2. First, when DATA

ACCEPTED is high, send a

WRITE pulse. This resets the

shift register and control logic and initializes the chip for the

data input sequence. Next clock in the appropriate number

of correct data and address bits. The DATA ACCEPTED Output may be monitored if desired, to determine when the chip

is ready to output the decoded data. When the correct number of bits has been entered, and the DATA ACCEPTED Output is low, a pulse at

WRITE will cause the data to be

decoded and stored in the latches of the addressed

digit/character. The shift register and control logic are reset,

causing DATA ACCEPTED to return high, and leaving the

chip ready to accept data for the next digit/character.

Note that for the ICM7232 the eleventh clock resets the shift

register and control logic, but the DATA ACCEPTED Output

goes low after the eighth clock. This allows the user to

abbreviate the data to eight bits, which will write the correct

character to the 7-segment display, but will leave the annunciators off, as shown in Figure 3.

If only AN2 is to be turned on, nine bits are clocked in; if AN1

is to be turned on, all ten bits are used.

The DATA ACCEPTED Output will drive one low-power

Schottky TTL input, and has equal current drive capability

pulling high or low.

Note that in the serial Input devices, it is possible to address

digits/characters which don’t exist. As shown in Table 2

when an incorrect address is applied together with a

WRITE

pulse, none of the outputs will be changed.

Display Fonts and Output Codes

The standard versions of the ICM7231 and ICM7232 chips are

programmed to drive a 7-segment display plus two annunciators per digit. See Table 3 for annunciator input controls.

The “A” and “B” suffix chips place both annunciators on BP3.

The display connections for one digit of this display are

shown in Figure 13. The “A” devices decode the input data

into a hexadecimal 7-segment output, while the “B” devices

supply Code B outputs (see Table 1).

The “C” devices place the left hand annunciator on BP1 and

the right hand annunciator (usually a decimal point) on BP3.

(See Figure 14). The “C” devices provide only a “Code B”

output for the 7 segments.

TABLE 1. BlNARY DATA DECODING ICM7231 AND ICM7232

CODE INPUT DISPLAY OUTPUT

BD3 BD2 BD1 BD0 HEX CODE B

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111 BLANK

9-30

Page 13

ICM7231, ICM7232

TABLE 2. ADDRESS DECODING (ICM7231 AND ICM7232)

DISPLAY

CODE INPUT

OUTPUT

ICM7232

ONLY

A3 A2 A1 A0

DIGIT

SELECTED

0 000 D1

0 001 D2

0 010 D3

0 011 D4

0 100 D5

0 101 D6

0 110 D7

0 111 D8

1 000 D9

1 0 0 1 D10

1 0 1 0 NONE

1 0 1 1 NONE

1 1 0 0 NONE

1 1 0 1 NONE

1 1 1 0 NONE

1 1 1 1 NONE

SEGMENT LINES

SEGMENT LINE CONNECTIONS

a

BP1

f

b

g

BP2

an2 an1

BP3

BACKPLANE CONNECTIONS

e

c

d

FIGURE 13. ICM7231 AND ICM7232 DISPLAY FONTS (“A” AND

)

“B” SUFFIX VERSIONS

SEGMENT LINES

(NOTE 1)

TABLE 3. ANNUNClATOR DECODING

CODE

INPUT DISPLAY OUTPUT

ICM7231A AND

ICM7231B

ICM7232A AND

ICM7232B

BOTH

ANNUNCIATORS

AN2 AN1

ON BP3

00

01

10

11

ICM7231C

ICM7232C

an2

ANNUNCIATOR

BP1

an1

ANNUNClATOR

BP3

SEGMENT LINE CONNECTIONS

SEGMENT LINES

BP1

BP2

an2

(NOTE 1)

a

f

b

g

e

c

d

BP3

NOTE:

1. Annunciators can be: , , , -arrows that

BACKPLANE CONNECTIONS

STOP GO

an1

point to information printed around the display opening etc.,

whatever the designer display opening etc., whatever the designer chooses to incorporate in the liquid crystal display.

FIGURE 14. ICM7231 DISPLAY FONTS (“C” SUFFIX VERSIONS)

Compatible Displays

Compatible displays are manufactured by: G.E. Displays

Inc., Beechwood, Ohio (216) 831-8100 (#356E3R99HJ)

Epson America Inc., Torrance CA

(Model Numbers LDB726/7/8).

Seiko Instruments USA Inc., Torrance CA

(Custom Displays)

Crystaloid, Hudson, OH

9-31

Page 14

Typical Applications

ICM7231, ICM7232

PERIOD INTERVAL TEST FREQ. RATIO FREQUENCYUNIT

OVER

RANGE

27

ICM7231CF

Q0 Q1 Q2 E1 V+

CD4532

D0 - D7

CS

+5V

10K

1µF

GS

INPUT A

INPUT B

BCD

ICM7226A

D1 - D8

BD0 - 3

AN2 AN1 A0 A1 A2

DP

FUNCTION

RANGE

NOTE: The annunciators show function and the decimal points indicate the range of the current operation. the system can be efficiently

battery operated.

FIGURE 15. 10MHz FREQUENCY/PERIOD POINTER WITH LCD DISPLAY

9-32

Page 15

ICM7231, ICM7232

Typical Applications

D8 D7 D6 D5 D4 D3 D2 D1

X YZ X YZ X YZ X YZ X YZ X YZ X YZX YZ

(Continued)

COM 1

COM 2

COM 3

ICM7231AF AND ICM7231BF

TOP VIEW

TO INPUT

SELECT

FIGURE 16. “FORWARD” PIN ORIENTATION AND DISPLAY CONNECTIONS

D9D10

NO FORWARD STOP

X YZX YZ

D8 D7 D6 D5 D4 D3 D2 D1

X YZ X YZ X YZ X YZ X YZ X YZ X YZX YZ

ICM7232CR

TOP VIEW

WAIT GO

COM 1

COM 2

COM 3

PCB TRACES UNDER PACKAGE

FIGURE 17. “REVERSE” PIN ORIENTATION AND DISPLAY CONNECTIONS

TO INPUT

9-33

Page 16

ICM7231, ICM7232

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Cor poration reserves the right to make changes in circuit design and/or specifications at any time without

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate

and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which

may result from its use. No license is granted by implication or otherwise under an y patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

Sales Office Headquarters

NORTH AMERICA

Intersil Corporation

P. O. Box 883, Mail Stop 53-204

Melbourne, FL 32902

TEL: (407) 724-7000

FAX: (407) 724-7240

EUROPE

Intersil SA

Mercure Center

100, Rue de la Fusee

1130 Brussels, Belgium

TEL: (32) 2.724.2111

FAX: (32) 2.724.22.05

9-34

ASIA

Intersil (Taiwan) Ltd.

Taiwan Limited

7F-6, No. 101 Fu Hsing North Road

Taipei, Taiwan

Republic of China

TEL: (886) 2 2716 9310

FAX: (886) 2 2715 3029

Loading...

Loading...