Page 1

Page 1 of 10

IA16450 Preliminary Data Sheet

Universal Asynchronous Receiver/Transmitter

FEATURES

• Form, Fit, and Function Compatible with the National NS16450

• Packaging options available: 40 Pin Plastic or 44 Pin Plastic Leaded Chip

Carrier

• Programmable Word Length, Stop Bits, and Parity

• Full Duplex Operation

• Programmable Baud Rate Generator

- Division of any input clock by 1 to (216 –1)

- Generates Internal 16 x clock

• Programmable Serial-Interface

- 5-, 6-, 7- or 8-bit characters

- Even, Odd, or No-Parity Bit Generation and Detection

- 1-, 1 ½-, or 2-Stop Bit Generation

- Baud Generation of DC to 56k

• Prioritized Interrupt Control

• Internal Diagnostic/Loopback Capabilities

The IA16450 uses innovASIC’s innovative new f 3 Program to provide industry with parts that

other vendors have declared obsolete. By specifying parts through this program a customer is

assured of never having a component become obsolete again. This advanced information sheet

assumes the original part has been designed in, and so provides a summary of capabilities only. For

new designs contact innovASIC for more detailed information.

National is a copyright trademark of National Semiconductor Corporation

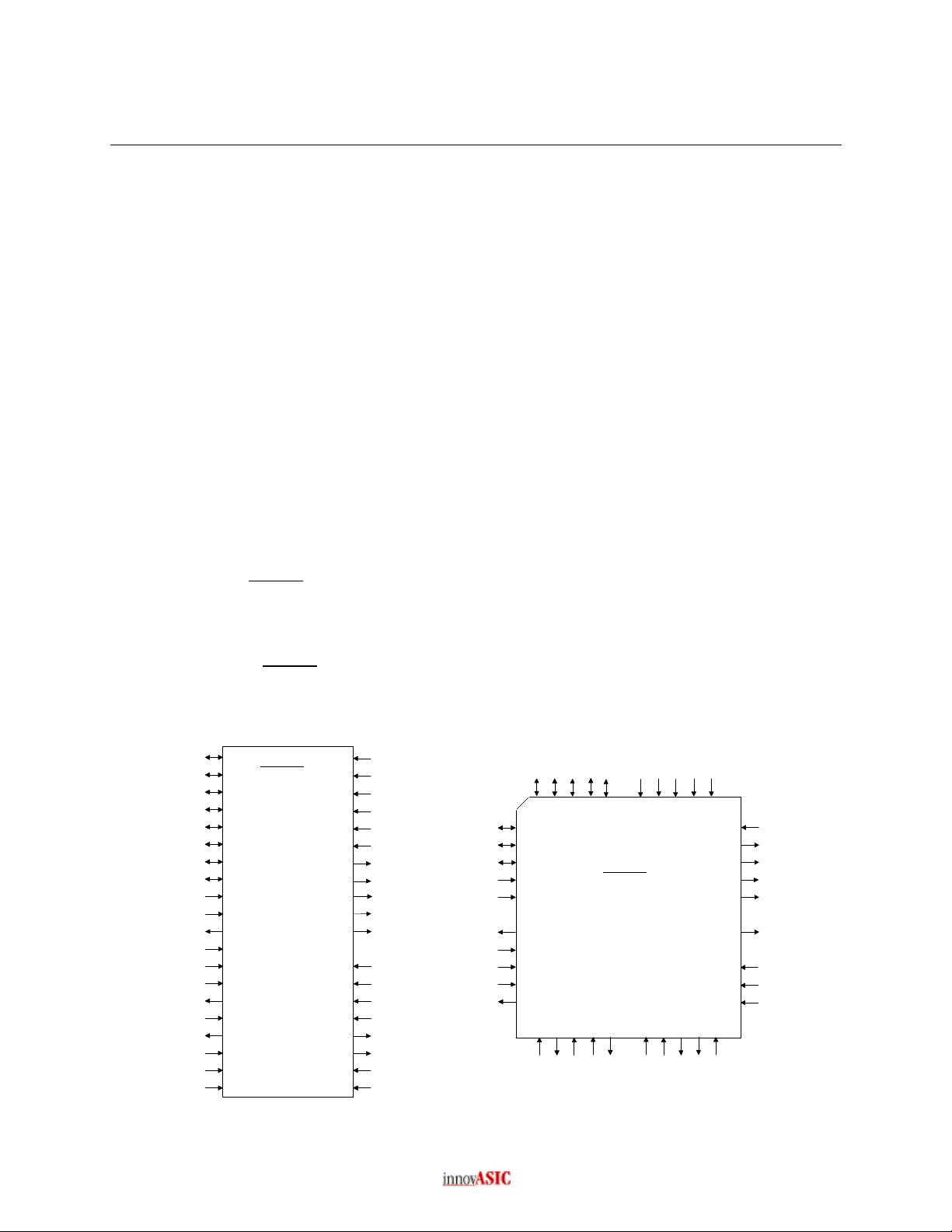

Package Pinout

D0

D1

D2

D3

D4

D5

D6

D7

CS2_n

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)RCLK

(10)SIN

(11)SOUT

(12)CS0

(13)CS1

(14)

(15)BAUDOUT_n

(16)XIN

(17)XOUT

(18)WR_n

(19)WR

(20)VSS

IA16450

40 Pin DIP

(40)

(39)

(38)

(37)

(36)

(35)

(34)

(33)

(32)

(31)

(30)

(29)

(28)

(27)

(26)

(25)

(24)

(23)

(22)

(21)

VCC

RI_n

DCD_n

DSR_n

CTS_n

MR

OUT1_n

DTR_n

RTS_n

OUT2_n

INTR

N. C.

A0

A1

A2

ADS_n

CSOUT

DDIS

RD

RD_n

D3

D4

D2

D1

(6)

(5)

(4)

(19)

XOUT

(3)

44 Pin LCC

(20)

(21)

WR

WR_n

(7)D5

(8)D6

(9)D7

(10)RCLK

(11)SIN

(12)N. C.

(13)SOUT

(14)CS0

(15)CS1

(16)CS2_n

(17)BAUDOUT_n

(18)

XIN

D0

N. C.

(2)

(1)

IA16450

(22)

(23)

VSS

N. C.

VCC

(44)

(24)

RD_n

RI_n

(43)

(25)

RD

(42) DCD_n

(41) DSR_n

(26)

DDIS

(40) CTS_n

(39)

(38)

(37)

(36)

(35)

(34)

(33)

(32)

(31)

(30)

(29)

(27)

(28)

ADS_n

CSOUT

MR

OUT1_n

DTR_n

RTS_n

OUT2_n

N. C.

INTR

N. C.

A0

A1

A2

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

Page 2

Page 2 of 10

IA16450 Preliminary Data Sheet

Universal Asynchronous Receiver/Transmitter

The IA16450 is a form, fit and function compatible part to the National NS16450 Univeral

Asynchronous Receiver/Transmitter. The IA16450 function receives and transmits data in a variety

of configurations including 5, 6, 7 or 8 bit data words, odd, even or no parity, and 1, 1.5, and 2 stop

bits. This megafunction includes an internal Baud Rate Generator and Interrupt Control. A block

diagram is shown in Figure 1.

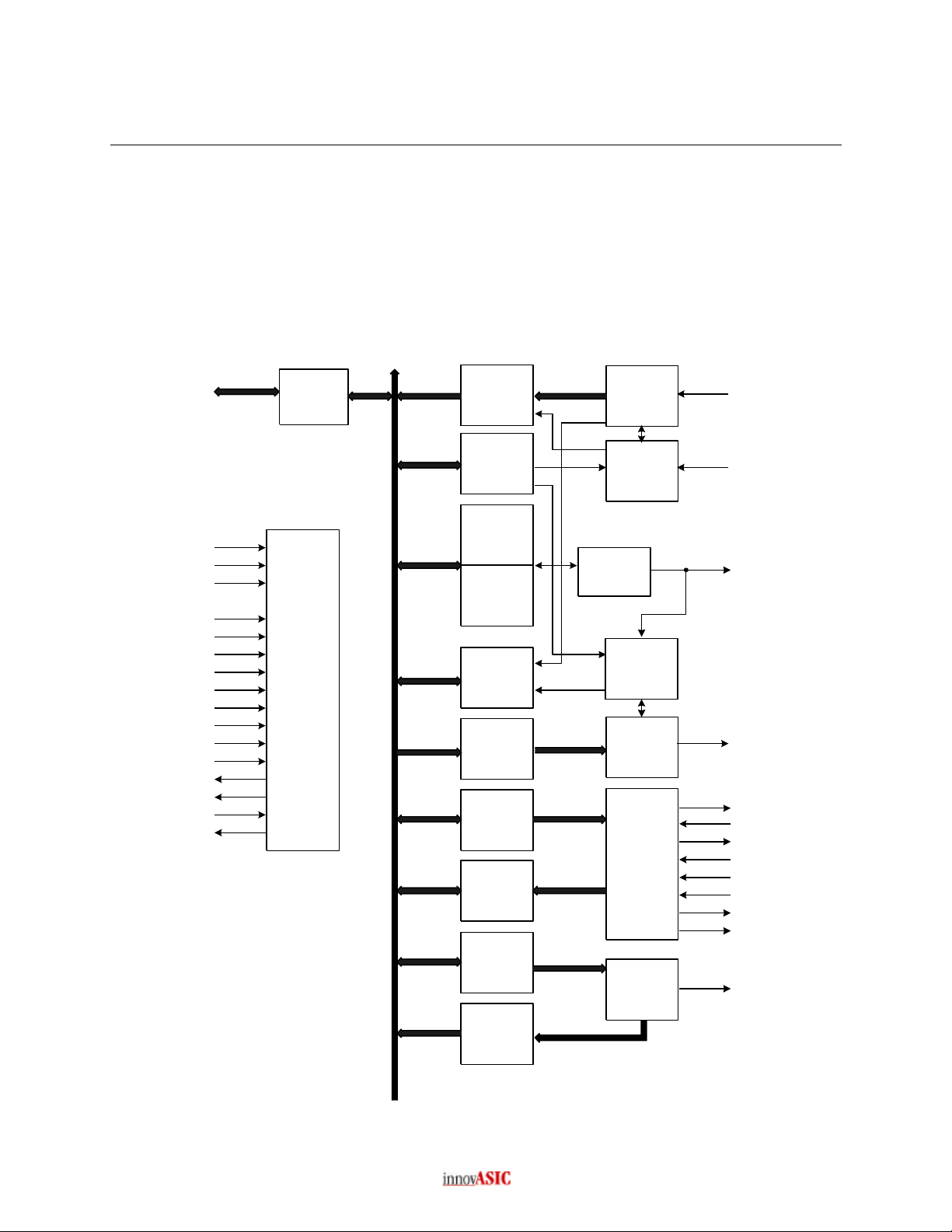

Functional Block Diagram

Figure 1

INTERNAL DATA

BUS

D7:D0

DATA BUS

BUFFER

RECEIVER

BUFFER

REGISTER

RECEIVER

SHIFT

REGISTER

SIN

A0

A1

A2

CS0

CS1

CS2_n

ADS_n

MR

RD

RD_n

WR

WR_n

DDIS

CSOUT

XIN

XOUT

DECODE

AND

CONTROL

LOGIC

LINE CONTROL

REGISTER

DIVISOR LATCH

(LSB)

DIVISOR LATCH

(MSB)

LINE STATUS

REGISTER

TRANSMITTER

HOLDING

REGISTER

MODEM

CONTROL

REGISTER

MODEM STATUS

REGISTER

RECEIVER

CONTROL

BAUD

GENERATOR

TRANSMITTER

TIMING

CONTROL

TRANSMITTER

REGISTER

MODEM

CONTROL

TIMING

&

&

SHIFT

LOGIC

RCLK

BAUDOUT_n

SOUT

RTS_n

CTS_n

DTR_n

DSR_n

DCD_n

RI

OUT1_n

OUT2_n

INTERRUPT

ENABLE

REGISTER

INTERRUPT ID

REGISTER

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

INTERRUPT

CONTROL

LOGIC

INTR

Page 3

Page 3 of 10

IA16450 Preliminary Data Sheet

Universal Asynchronous Receiver/Transmitter

I/O Signal Description

Table 1 below describes the I/O characteristics for each signal on the IC. The signal names

correspond to the signal names on the pinout diagrams provided. Table 2 refers to the address

register map. Table 3 refers to the Preliminary A. C. Characteristics. Figure 2 illustrates the

Preliminary Timing Waveforms for this device. Environmental/Qualification Levels are listed in

Table 4.

Table 1

Name Type Description

MR I Master Reset - Active high - Clears all registers (except the

receiver buffer, transmitter holding and divisor latches) to their

initial state. Resets internal control logic to its initial state

A(2:0) I Register Address - Active high - This bus selects one of the

internal UART registers (refer to table 1). Note the state of the

divisor latch access bit (DLAB - the msb of the line control

register) must be set high to access the divisor latches and low

to access the receiver buffer or the interrupt enable register.

DIN(7:0) I Data Input Bus - Active high - Serves as input data when

writing to internal UART registers.

CS0 I Chip Select 0 - Active high - When CS0, CS1 and CS2 are active

the megafunction is selected. Read and write transactions to

internal UART registers are then possible.

CS1 I Chip Select 1 - Active high - When CS0, CS1 and CS2 are active

the megafunction is selected. Read and write transactions to

internal UART registers are then possible.

CS2_n I Chip Select 2 - Active low - When CS0, CS1 and CS2 are active

the megafunction is selected. Read and write transactions to

internal UART registers are then possible.

ADS_n I Address Strobe - Active low - Gating signal to the Address

input latch. The positive edge of ADS_n latches the state of the

register address bus into the Address input latch. If address

signals are guaranteed to be stable for the duration of a read or

write cycle, ADS_n may be tied low thus forcing the Address

input latch to be transparent.

RD I Read Control - Active High - when RD is high or RD_n is low

and the UART is selected, read transactions from internal

UART registers are possible.

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

Page 4

Page 4 of 10

IA16450 Preliminary Data Sheet

Universal Asynchronous Receiver/Transmitter

Name Type Description

RD_n I Read Control - Active low - when RD is high or RD_n is low

and the UART is selected, read transactions from internal

UART registers are possible.

WR I Write Control - Active High - when WR is high or WR_n is low

and the UART is selected, write transactions to internal UART

registers are possible.

WR_n I Write Control - Active low - when WR is high or WR_n is low

and the UART is selected, write transactions to internal UART

registers are possible.

SIN I Serial Data Input - Active High - Receive data to the UART

RCLK I Receive Clock - The 16x baud rate clock used by the receiver

section of the UART.

CTS_n I Clear To Send - Active Low - Active state indicates that the

MODEM or data set is ready to exchange data. A change in

state of this input is recorded in the DCTS bit (bit 0) of the

MODEM Status register. Whenever CTS_n changes state, an

interrupt is generated if the MODEM Status interrupt is

enabled. The complement of this input is recorded in the CTS

(bit 4) bit of the MODEM Status register

DSR_n I Data Set Ready - Active Low - Active state indicates that the

MODEM or data set is ready to establish the communications

link with the UART. A change in state of this input is recorded

in the DDSR bit (bit 1) of the MODEM Status register.

Whenever DSR_n changes state, an interrupt is generated if the

MODEM Status interrupt is enabled. The complement of this

input is recorded in the DSR (bit 5) bit of the MODEM Status

register

DCD_n I Data Carrier Detect - Active Low - Active state indicates that

the data carrier has been detected by the MODEM or data set.

A change in state of this input is recorded in the DDCD bit (bit

3) of the MODEM Status register. Whenever DCD_n changes

state, an interrupt is generated if the MODEM Status interrupt

is enabled. The complement of this input is recorded in the

DCD (bit 7) bit of the MODEM Status register

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

Page 5

Page 5 of 10

IA16450 Preliminary Data Sheet

Universal Asynchronous Receiver/Transmitter

Name Type Description

RI_n I Ring Indicator - Active Low - Active state indicates that the ring

signal has been detected by the MODEM or data set. A change

in state of this input is recorded in the TERI bit (bit 2) of the

MODEM Status register. Whenever DSR_n changes state, an

interrupt is generated if the MODEM Status interrupt is

enabled. The complement of this input is recorded in the RI

(bit 6) bit of the MODEM Status register

DOUT(7:0) O Data Output Bus - Active high - Serves as output data when

reading from internal UART registers.

DDIS O Driver Disable - Active High - Active State indicates that the

CPU is reading data from the UART. This output is intended as

a disable or direction control between the UART and CPU.

CSOUT O Chip Select Output - Active High - Active State indicates that

the megafunction has been selected by use of the CS0, CS1 and

CS2_n inputs.

SOUT O Serial Data Out - Active High - Serial (transmit) data out. This

signal is set to the marking (logic 1) state upon master reset.

BAUDOUT_n O Baud Out - Active Low - The 16x baud rate clock used by the

transmitter section of the UART. This output is controlled by

the programmable baud rate generator.

RTS_n O Request to Send - Active Low - This output indicates that the

UART is ready to exchange data. This output is controlled by

writing to the RTS (bit 1) bit of the control register.

DTR_n O Data Terminal Ready - Active Low - This output indicates that

the UART is ready to establish a communications link. This

output is controlled by writing to the DTR (bit 0) bit of the

control register.

OUT1_n O Discrete Output - Active Low - One of two user-programmable

discrete outputs. This output is controlled by writing to the

OUT1 (bit 2) bit of the control register.

OUT2_n O Discrete Output - Active Low - One of two user-programmable

discrete outputs. This output is controlled by writing to the

OUT2 (bit 3) bit of the control register.

INTR O Interrupt - Active High - Indicates that an enabled interrupt has

had its interrupt condition met.

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

Page 6

Page 6 of 10

DATA

IA16450 Preliminary Data Sheet

Universal Asynchronous Receiver/Transmitter

Name Type Description

XIN I External Crystal Input. This signal iniput is used in conjuction

with XOUT to form a feedback circuit for the baud rate

generator’s oscillator. If a clock signal will be generated off-

chip, then it should drive the baud rate generator through this

pin

XOUT O External Crystal Output. This signal output is used in

conjuction with XIN to form a feedback circuit for the baud

rate generator’s oscillator. If the clock signal will be generated

off-chip, then this pin is unused.

VSS P Ground.

VCC P +5V power.

IA16450 Register Address Map

Table 2

DLAB A2 A1 A0 REGISTER DESCRIPTION

0 0 0 0 Receiver Buffer - Read Only

Transmitter Holding Register - Write Only

1 0 0 0 Divisor Latch (LSB)

0 0 0 1 Interrupt Enable Register

1 0 0 1 Divisor Latch (MSB)

X 0 1 0 Interrupt ID Register

X 0 1 1 Line Control Register

X 1 0 0 MODEM Control Register

X

1 0 1 Line Status Register

X 1 1 0 MODEM Status Register

X 1 1 1 Scratch

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

Page 7

Page 7 of 10

IA16450 Preliminary Data Sheet

Universal Asynchronous Receiver/Transmitter

AC Electrical Characteristics

Table 3

Symbol Min Max

t

ADS

t

AH

t

AR

t

AS

t

AW

t

CH

t

CS

t

CSC

t

CSR

t

CSW

t

DH

t

DS

t

HZ

t

RA

t

RC

t

RCS

t

RD

t

RDD

t

RVD

t

WA

t

WC

t

WCS

t

WR

RC

WC

Parameter

Address Strobe Width

Address Hold Time

RD, RD_n Delay from Address (Note 1)

Address Setup Time

WR, WR_n Delay from Address (Note 1)

Chip Select Hold Time

Chip Select Setup Time

Chip Select Output Delay from Select (Note 1)

RD, RD_n Delay fron Select (Note 1)

WR, WR_n Delay fron Select (Note 1)

Data Hold Time

Data Setup Time

RD, RD_n to Floating Data Delay

Address Hold Time from RD, RD_n (Note 1)

Read Cycle Delay

Chip Select Hold Time from RD, RD_n (Note 1)

RD, RD_n Strobe Width

RD, RD_n to Driver Disable Delay

Delay from RD, RD_n to Data

Address Hold Time from WR, WR_n

Write Cycle Delay

Chip Select Hold Time from WR, WR_n (Note 1)

WR, WR_n Strobe Width

Read Cycle = tAR + tRD + t

Write Cycle = tAW + tWR +t

RC

WC

25

0

20

25

20

0

25

33

20

20

10

20

0 25

0

36

0

60

20

31

0

36

0

60

115

115

Note 1: Applicable only when ADS_n is tied low.

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

Page 8

Page 8 of 10

IA16450 Preliminary Data Sheet

Universal Asynchronous Receiver/Transmitter

Timing Waveforms

Figure 2

ADS_n

A2,A1,A0

CS2_n,CS1,CS0

CSOUT

WR_n,WR

RD_n,RD

DATA,D0:D7

ADS_N

A2,A1,A0

CS2_n,CS1,CS0

CSOUT

RD_n,RD

WR_n,WR

DDIS

DATA,D0:D7

t

ADS

t

AS

VALID

t

CS

VALID

t

ADS

t

AS

VALID

t

CS

VALID

Write Cycle

t

AH

t

CH

t

CSC

t

CSW

t

AW

t

WR

ACTIVE

t

DS

t

WA

t

WCS

t

WC

WC

ACTIVE

ACTIVE

t

DH

VALID DATAVALID DATA

Read Cycle

t

AH

t

CH

t

CSC

t

CSR

t

AR

t

RD

ACTIVE

t

RDD

t

RVD

VALID DATAVALID DATA

t

RA

t

RCS

RC

t

RC

ACTIVE

ACTIVE

t

RDD

t

HZ

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

Page 9

Page 9 of 10

IA16450 Preliminary Data Sheet

Universal Asynchronous Receiver/Transmitter

Qualification Levels

Table 4

Part Number Environmental/ Qual Level

IA16450-PDW40C Commercial

IA16450-PLC44C Commercial

IA16450-PDW40I Industrial

IA16450-PLC44I Industrial

The following diagram depicts the innovASIC Product Identification Number.

IAXXXXX-PPPPNNNT/SP

Special Processing:

S = Space

Q = MIL-STD-883

Temperature:

C = Commercial

I = Industrial

M = Military

Number of Leads

Package Type:

Per Package Designator Table

IC Base Number

innovASIC Designator

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

Page 10

Page 10 of 10

IA16450 Preliminary Data Sheet

Universal Asynchronous Receiver/Transmitter

Package Designator Table

Package Type

innovASIC

Designator

Ceramic side brazed Dual In-line CDB

Cerdip with window CDW

Ceramic leaded chip carrier CLC

Cerdip without window CD

Ceramic leadless chip carrier CLL

PLCC PLC

Plastic DIP standard (300 mil) PD

Plastic DIP standard (600 mil) PDW

Plastic metric quad flat pack PQF

Plastic thin quad flat pack PTQ

Skinny Cerdip CDS

Small outline plastic gull-wing(150 mil body) PSO

Small outline medium plastic gull-wing (207 mil body) PSM

Small outline narrow plastic gull wing (150 mil body) PSN

Small outline wide plastic gull wing (300 mil body) PSW

Skinny Plastic Dip PDS

Shrink small outline plastic (5.3mm .208 body) PS

Thin shrink small outline plastic PTS

Small outline large plastic gull wing (330 mil body) PSL

Thin small outline plastic gull-wing (8 x 20mm) [TSOP] PST

PGA CPGA

BGA CBGA

Contact innovASIC for other package and processing options.

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

Loading...

Loading...