Page 1

DATA SH EET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF4512B

MSI

8-input multiplexer with 3-state

output

For a complete data sheet, please also download:

•The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

•The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

Page 2

January 1995 2

Philips Semiconductors Product specification

8-input multiplexer with 3-state output

HEF4512B

MSI

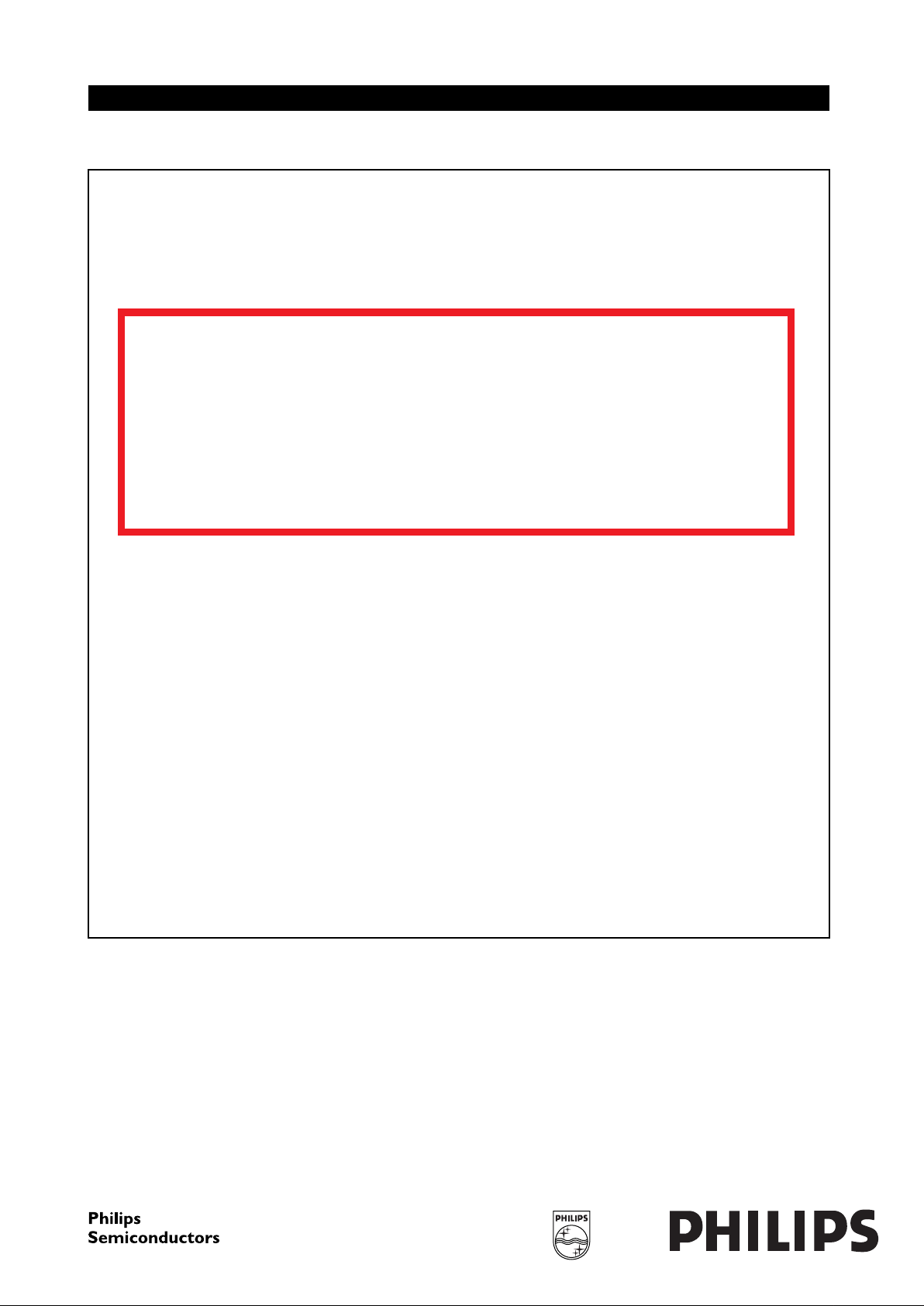

DESCRIPTION

The HEF4512B is an 8-input multiplexer with 8 binary

inputs (I0to I7), an enable input (E) and an output enable

input (EO). One of eight binary inputs is selected by select

inputs S0, S1and S2, and is routed to the output O. A HIGH

on EO causes O to assume a high impedance OFF-state,

regardless of other input conditions. This allows the output

to interface directly with bus oriented systems (3-state).

When the active LOW enable (

E) is HIGH, it forces the

output LOW provided EO is LOW. By proper manipulation

of the inputs, the device can provide any logic functions of

four variables. It cannot be used to multiplex analogue

signals.

Fig.1 Functional diagram.

HEF4512BP(N): 16-lead DIL; plastic

(SOT38-1)

HEF4512BD(F): 16-lead DIL; ceramic (cerdip)

(SOT74)

HEF4512BT(D): 16-lead SO; plastic

(SOT109-1)

( ): Package Designator North America

Fig.2 Pinning diagram.

PINNING

FAMILY DATA, I

DD

LIMITS category MSI

See Family Specifications

S

0,S1

, S

2

select inputs

EO output enable (active LOW)

E enable (active LOW)

I

0

to I

7

multiplexer inputs

O multiplexer output

Page 3

January 1995 3

Philips Semiconductors Product specification

8-input multiplexer with 3-state output

HEF4512B

MSI

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

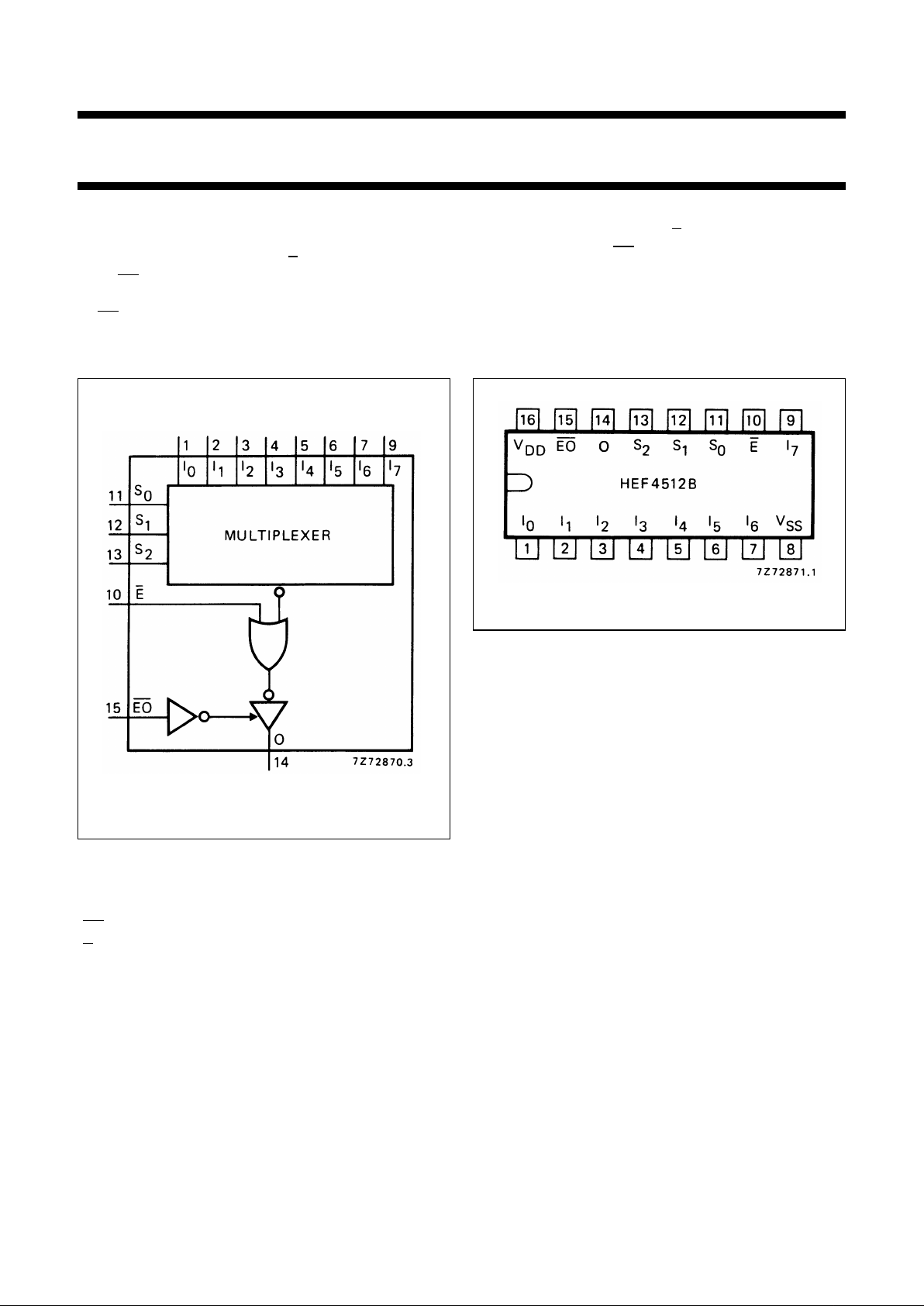

Fig.3 Logic diagram.

Page 4

January 1995 4

Philips Semiconductors Product specification

8-input multiplexer with 3-state output

HEF4512B

MSI

TRUTH TABLE

Notes

1. H = HIGH state (the more positive voltage)

L = LOW state (the less positive voltage)

X = state is immaterial

Z = high impedance OFF-state

AC CHARACTERISTICS

V

SS

= 0 V; T

amb

=25°C; input transition times ≤ 20 ns

INPUTS OUTPUT

EO ES

2

S

1

S

0

I

0

I

1

I

2

I

3

I

4

I

5

I

6

I

7

O

LHX X X X X X X X X X X L

LLL L L LX X XXX X X L

LLL L L HX X X XX X X H

LLL L H XL X XXX X X L

LLL L H XH X X XX X X H

LLLH L XX L XXX X X L

LLLH L XX H X XX X X H

LLLH H XX X L XX X X L

LLLH H XX X HXX X X H

LLH L L XX X X LX X X L

LLH L L XX X X HX X X H

LLH L H XX X X X L X X L

LLH L H XX X X XH X X H

LLHH L XX X X XX L X L

LLHH L XX X X XX H X H

LLHH H XX X X XX X L L

LLHH H XX X X XX X H H

HXX X X X X X X X X X X Z

V

DD

V

TYPICAL FORMULA FOR P (µW)

Dynamic power 5 500 f

i

+∑(foCL) × V

DD

2

where

dissipation per 10 2100 f

i

+∑(foCL) × V

DD

2

fi= input freq. (MHz)

package (P) 15 5800 f

i

+∑(foCL) × V

DD

2

fo= output freq. (MHz)

C

L

= load capacitance (pF)

∑ (f

oCL

) = sum of outputs

V

DD

= supply voltage (V)

Page 5

January 1995 5

Philips Semiconductors Product specification

8-input multiplexer with 3-state output

HEF4512B

MSI

AC CHARACTERISTICS

V

SS

= 0 V; T

amb

=25°C; CL= 50 pF; input transition times ≤ 20 ns

V

DD

V

SYMBOL TYP. MAX.

TYPICAL EXTRAPOLATION

FORMULA

Propagation delays

In→ O 5 100 200 ns 73 ns + (0,55 ns/pF) C

L

HIGH to LOW 10 t

PHL

40 80 ns 29 ns + (0,23 ns/pF) C

L

15 30 60 ns 22 ns + (0,16 ns/pF) C

L

5 100 200 ns 73 ns + (0,55 ns/pF) C

L

LOW to HIGH 10 t

PLH

40 80 ns 29 ns + (0,23 ns/pF) C

L

15 30 60 ns 22 ns + (0,16 ns/pF) C

L

Sn→ O 5 140 280 ns 113 ns + (0,55 ns/pF) C

L

HIGH to LOW 10 t

PHL

55 110 ns 44 ns + (0,23 ns/pF) C

L

15 40 80 ns 32 ns + (0,16 ns/pF) C

L

5 150 300 ns 123 ns + (0,55 ns/pF) C

L

LOW to HIGH 10 t

PLH

60 120 ns 49 ns + (0,23 ns/pF) C

L

15 40 80 ns 32 ns + (0,16 ns/pF) C

L

E → O 5 60 120 ns 33 ns + (0,55 ns/pF) C

L

HIGH to LOW 10 t

PHL

25 50 ns 14 ns + (0,23 ns/pF) C

L

15 20 40 ns 12 ns + (0,16 ns/pF) C

L

5 55 110 ns 28 ns + (0,55 ns/pF) C

L

LOW to HIGH 10 t

PLH

25 50 ns 14 ns + (0,23 ns/pF) C

L

15 20 40 ns 12 ns + (0,16 ns/pF) C

L

Output transition times 5 60 120 ns 10 ns + (1,0 ns/pF) C

L

HIGH to LOW 10 t

THL

30 60 ns 9 ns + (0,42 ns/pF) C

L

15 20 40 ns 6 ns + (0,28 ns/pF) C

L

5 60 120 ns 10 ns + (1,0 ns/pf) C

L

LOW to HIGH 10 t

TLH

30 60 ns 9 ns + (0,42 ns/pF) C

L

15 20 40 ns 6 ns + (0,28 ns/pF) C

L

3-state propagation delays

Output disable times

EO → O 5 35 70 ns

HIGH 10 t

PHZ

20 40 ns

15 15 30 ns

53570ns

LOW 10 t

PLZ

15 30 ns

15 10 20 ns

Output enable times

EO → O 5 35 70 ns

HIGH 10 t

PZH

15 30 ns

15 10 20 ns

Page 6

January 1995 6

Philips Semiconductors Product specification

8-input multiplexer with 3-state output

HEF4512B

MSI

APPLICATION INFORMATION

Some examples of applications for the HEF4512B are:

• Signal gating

• Digital multiplexing

• Number sequence generation

53570ns

LOW 10 t

PZL

20 40 ns

15 15 30 ns

V

DD

V

SYMBOL TYP. MAX.

TYPICAL EXTRAPOLATION

FORMULA

Page 7

January 1995 7

Philips Semiconductors Product specification

8-input multiplexer with 3-state output

HEF4512B

MSI

TRUTH TABLE for Fig. 4

A

4

A

3

A

2

A

1

A

0

INPUT CONN.

TO OUTPUT

LLLLL 0

via

IC

0

LLLLH 1

LLLHL 2

LLLHH 3

LLHLL 4

LLHLH 5

LLHHL 6

LLHHH 7

LHLLL 8

via

IC

1

LHLLH 9

LHLHL 10

LHLHH11

LHHLL 12

LHHLH13

LHHHL 14

LHHHH15

HLLLL16

via

IC

2

HLLLH17

HLLHL 18

HLLHH19

HLHLL 20

HLHLH21

HLHHL22

HLHHH23

HHLL L 24

via

IC

3

HHLLH25

HHLHL 26

HHLHH 27

HHHL L 28

HHHLH 29

HHHHL 30

HHHHH 31

Fig.4 32-input multiplexer using 4 × HEF4512B

and 1 × HEF4011B. The input is selected

by 5-bit address (A4to A0) and presented at

the output.

Loading...

Loading...