Page 1

DATA SH EET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF4043B

MSI

Quadruple R/S latch with 3-state

outputs

For a complete data sheet, please also download:

•The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

•The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

Page 2

January 1995 2

Philips Semiconductors Product specification

Quadruple R/S latch with 3-state outputs

HEF4043B

MSI

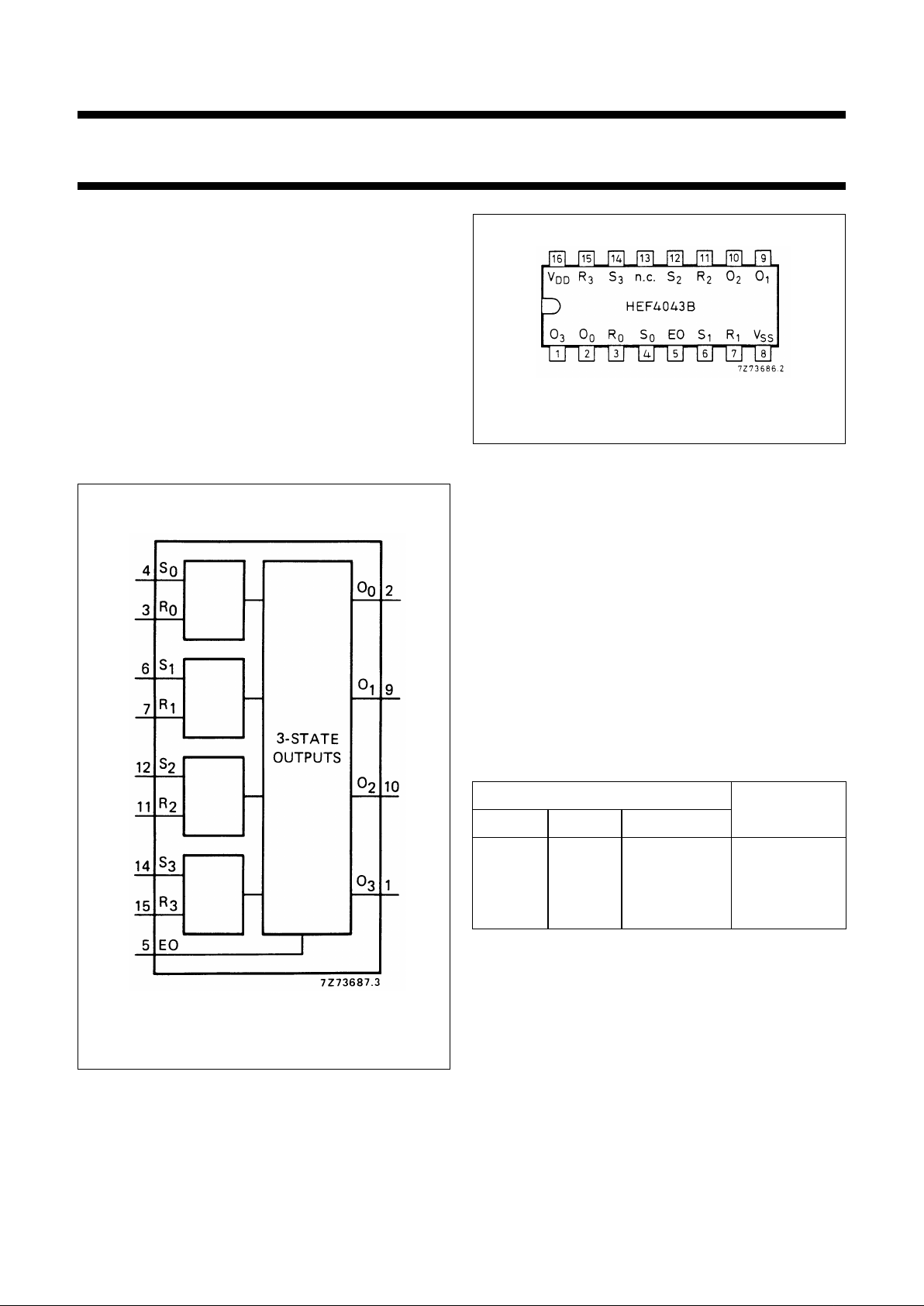

DESCRIPTION

The HEF4043B is a quadruple R/S latch with 3-state

outputs with a common output enable input (EO). Each

latch has an active HIGH set input (S0 to S3), an active

HIGH reset input (R0to R3) and an active HIGH 3-state

output (O0to O3).

When EO is HIGH, the state of the latch output (On) can be

determined from the function table below. When EO is

LOW, the latch outputs are in the high impedance

OFF-state. EO does not affect the state of the latch.

The high impedance off-state feature allows common

busing of the outputs.

Fig.1 Functional diagram.

PINNING

FUNCTION TABLE

Notes

1. H = HIGH state (the more positive voltage)

L = LOW state (the less positive voltage)

X = state immaterial

Z = high impedance state

FAMILY DATA, IDDLIMITS category MSI

See Family Specifications

HEF4043BP(N): 16-lead DIL; plastic (SOT38-1)

HEF4043BD(F): 16-lead DIL; ceramic (cerdip) (SOT74)

HEF4043BT(D): 16-lead SO; plastic (SOT109-1)

( ): Package Designator North America

EO common output enable input

S

0

to S

3

set inputs (active HIGH)

R

0

to R

3

reset inputs (active HIGH)

O

0

to O

3

3-state buffered latch outputs

INPUTS OUTPUT

O

n

EO S

n

R

n

LX X Z

HL H L

HH X H

H L L latched

Fig.2 Pinning diagram.

Page 3

January 1995 3

Philips Semiconductors Product specification

Quadruple R/S latch with 3-state outputs

HEF4043B

MSI

Fig.3 Logic diagram.

Fig.4 Logic diagram (one latch).

Page 4

January 1995 4

Philips Semiconductors Product specification

Quadruple R/S latch with 3-state outputs

HEF4043B

MSI

AC CHARACTERISTICS

V

SS

= 0 V; T

amb

=25°C; CL= 50 pF; input transition times ≤ 20 ns

V

DD

V

SYMBOL MIN. TYP. MAX.

TYPICAL EXTRAPOLATION

FORMULA

Propagation delays

Rn→ O

n

5 90 180 ns 63 ns + (0,55 ns/pF) C

L

HIGH to LOW 10 t

PHL

35 70 ns 24 ns + (0,23 ns/pF) C

L

15 25 50 ns 17 ns + (0,16 ns/pF) C

L

Sn→ O

n

5 65 135 ns 38 ns + (0,55 ns/pF) C

L

LOW to HIGH 10 t

PLH

25 50 ns 14 ns + (0,23 ns/pF) C

L

15 15 35 ns 7 ns + (0,16 ns/pF) C

L

Output transition 5 60 120 ns 10 ns + (1,0 ns/pF) C

L

times 10 t

THL

30 60 ns 9 ns + (0,42 ns/pF) C

L

HIGH to LOW 15 20 40 ns 6 ns + (0,28 ns/pF) C

L

5 60 120 ns 10 ns + (1,0 ns/pF) C

L

LOW to HIGH 10 t

TLH

30 60 ns 9 ns + (0,42 ns/pF) C

L

15 20 40 ns 6 ns + (0,28 ns/pF) C

L

3-state propagation delays

Output disable times

EO → O

n

54590ns

HIGH 10 t

PHZ

20 35 ns

15 10 25 ns

5 50 100 ns

LOW 10 t

PLZ

20 40 ns

15 10 25 ns

Output enable times

EO → O

n

52550ns

HIGH 10 t

PZH

15 30 ns

15 10 25 ns

54080ns

LOW 10 t

PZL

20 45 ns

15 15 35 ns

Minimum S

n

53015 ns

see also waveforms

Fig.5

pulse width; HIGH 10 t

WSH

20 10 ns

15 16 8 ns

Minimum R

n

53015 ns

pulse width; HIGH 10 t

WRH

20 10 ns

15 16 8 ns

Page 5

January 1995 5

Philips Semiconductors Product specification

Quadruple R/S latch with 3-state outputs

HEF4043B

MSI

APPLICATION INFORMATION

An example of application for the HEF4043B is:

• Four-bit storage with output enable

V

DD

V

TYPICAL FORMULA FOR P (µW)

Dynamic power 5 1100 f

i

+∑(foCL) × V

DD

2

where

dissipation per 10 4400 f

i

+ ∑(foCL) × V

DD

2

fi= input freq. (MHz)

package (P) 15 11 400 f

i

+∑(foCL) × V

DD

2

fo= output freq. (MHz)

C

L

= load capacitance (pF)

∑(f

oCL

) = sum of outputs

V

DD

= supply voltage (V)

Fig.5 Waveforms showing minimum Snand Rnpulse widths.

Loading...

Loading...