Page 1

DATA SH EET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF4040B

MSI

12-stage binary counter

For a complete data sheet, please also download:

•The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

•The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

Page 2

January 1995 2

Philips Semiconductors Product specification

12-stage binary counter

HEF4040B

MSI

DESCRIPTION

The HEF4040B is a 12-stage binary ripple counter with a

clock input (CP), an overriding asynchronous master reset

input (MR) and twelve fully buffered outputs (O0to O11).

The counter advances on the HIGH to LOW transition of

CP. A HIGH on MR clears all counter stages and forces all

outputs LOW, independent of CP. Each counter stage is a

static toggle flip-flop. Schmitt-trigger action in the clock

input makes the circuit highly tolerant to slower clock rise

and fall times.

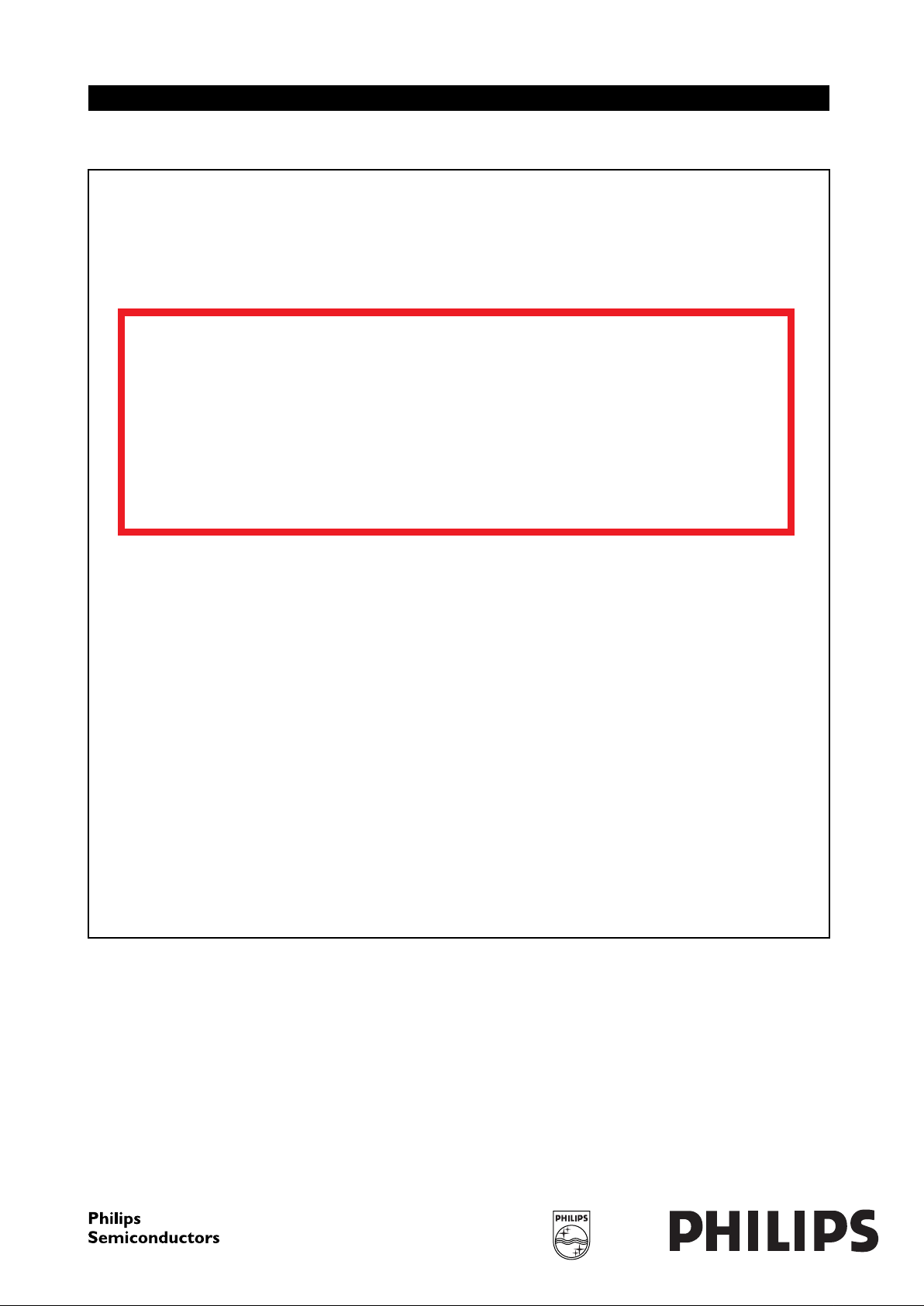

Fig.1 Functional diagram.

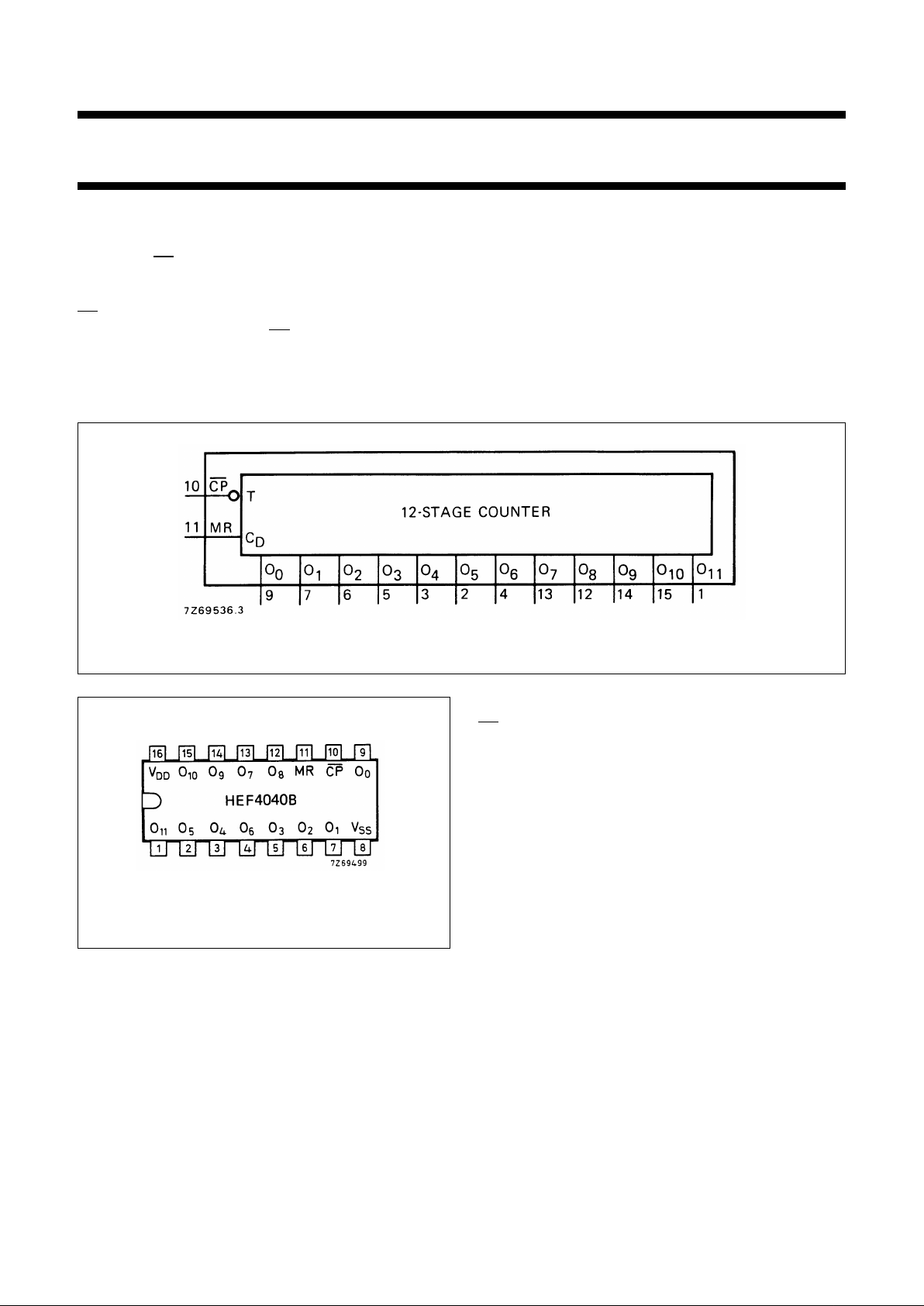

HEF4040BP(N): 16-lead DIL; plastic

(SOT38-1)

HEF4040BD(F): 16-lead DIL; ceramic (cerdip)

(SOT74)

HEF4040BT(D): 16-lead SO; plastic

(SOT109-1)

( ): Package Designator North America

Fig.2 Pinning diagram.

PINNING

APPLICATION INFORMATION

Some examples of applications for the HEF4040B are:

• Frequency dividing circuits

• Time delay circuits

• Control counters

FAMILY DATA, I

DD

LIMITS category MSI

See Family Specifications

CP clock input (HIGH to LOW edge-triggered)

MR master reset input (active HIGH)

O

0

to O

11

parallel outputs

Page 3

January 1995 3

Philips Semiconductors Product specification

12-stage binary counter

HEF4040B

MSI

AC CHARACTERISTICS

V

SS

= 0 V; T

amb

=25°C; CL= 50 pF; input transition times ≤ 20 ns

V

DD

V

SYMBOL MIN. TYP. MAX.

TYPICAL EXTRAPOLATION

FORMULA

Propagation delays

CP → O

0

5 105 210 ns 78 ns + (0,55 ns/pF) C

L

HIGH to LOW 10 t

PHL

45 90 ns 34 ns + (0,23 ns/pF) C

L

15 35 70 ns 27 ns + (0,16 ns/pF) C

L

5 85 170 ns 58 ns + (0,55 ns/pF) C

L

LOW to HIGH 10 t

PLH

40 80 ns 29 ns + (0,23 ns/pF) C

L

15 30 60 ns 22 ns + (0,16 ns/pF) C

L

On→ O

n +1

5 35 70 ns note 1 (0,55 ns/pF) C

L

HIGH to LOW 10 t

PHL

15 30 ns note 1 (0,23 ns/pF) C

L

15 10 20 ns note 1 (0,16 ns/pF) C

L

5 35 70 ns note 1 (0,55 ns/pF) C

L

LOW to HIGH 10 t

PLH

15 30 ns note 1 (0,23 ns/pF) C

L

15 10 20 ns note 1 (0,16 ns/pF) C

L

MR → O

n

5 90 180 ns 63 ns + (0,55 ns/pF) C

L

HIGH to LOW 10 t

PHL

40 80 ns 29 ns + (0,23 ns/pF) C

L

15 30 60 ns 22 ns + (0,16 ns/pF) C

L

Output transition times 5 60 120 ns 10 ns + (1,0 ns/pF) C

L

HIGH to LOW 10 t

THL

30 60 ns 9 ns + (0,42 ns/pF) C

L

15 20 40 ns 6 ns + (0,28 ns/pF) C

L

5 60 120 ns 10 ns + (1,0 ns/pF) C

L

LOW to HIGH 10 t

TLH

30 60 ns 9 ns + (0,42 ns/pF) C

L

15 20 40 ns 6 ns + (0,28 ns/pF) C

L

Fig.3 Logic diagram.

Page 4

January 1995 4

Philips Semiconductors Product specification

12-stage binary counter

HEF4040B

MSI

Note

1. For other loads than 50 pF at the nthoutput, use the slope given.

Minimum clock 5 50 25 ns

see also waveforms

Fig.4

pulse width; HIGH 10 t

WCPH

30 15 ns

15 20 10 ns

Minimum MR 5 40 20 ns

pulse width; HIGH 10 t

WMRH

30 15 ns

15 20 10 ns

Recovery time 5 40 20 ns

for MR 10 t

RMR

30 15 ns

15 20 10 ns

Maximum clock 5 10 20 MHz

pulse frequency 10 f

max

15 30 MHz

15 25 50 MHz

V

DD

V

TYPICAL FORMULA FOR P (µW)

Dynamic power 5 400 f

i

+∑(foCL) × V

DD

2

where

dissipation per 10 2 000 f

i

+∑(foCL) × V

DD

2

fi= input freq. (MHz)

package (P) 15 5 200 f

i

+∑(foCL) × V

DD

2

fo= output freq. (MHz)

C

L

= load cap. (pF)

∑ (f

oCL

) = sum of outputs

V

DD

= supply voltage (V)

V

DD

V

SYMBOL MIN. TYP. MAX.

TYPICAL EXTRAPOLATION

FORMULA

Page 5

January 1995 5

Philips Semiconductors Product specification

12-stage binary counter

HEF4040B

MSI

Fig.4 Waveforms showing propagation delays for MR to Onand CP to O0, minimum MR and CP pulse widths.

Loading...

Loading...