Page 1

DATA SH EET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF4027B

flip-flops

Dual JK flip-flop

For a complete data sheet, please also download:

•The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

•The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

Page 2

January 1995 2

Philips Semiconductors Product specification

Dual JK flip-flop

HEF4027B

flip-flops

DESCRIPTION

The HEF4027B is a dual JK flip-flop which is

edge-triggered and features independent set direct

(SD), clear direct (CD), clock (CP) inputs and outputs

(O,O). Data is accepted when CP is LOW, and transferred

to the output on the positive-going edge of the clock. The

active HIGH asynchronous clear-direct (CD) and set-direct

(SD) are independent and override the J, K, and CP inputs.

The outputs are buffered for best system performance.

Schmitt-trigger action in the clock input makes the circuit

highly tolerant to slower clock rise and fall times.

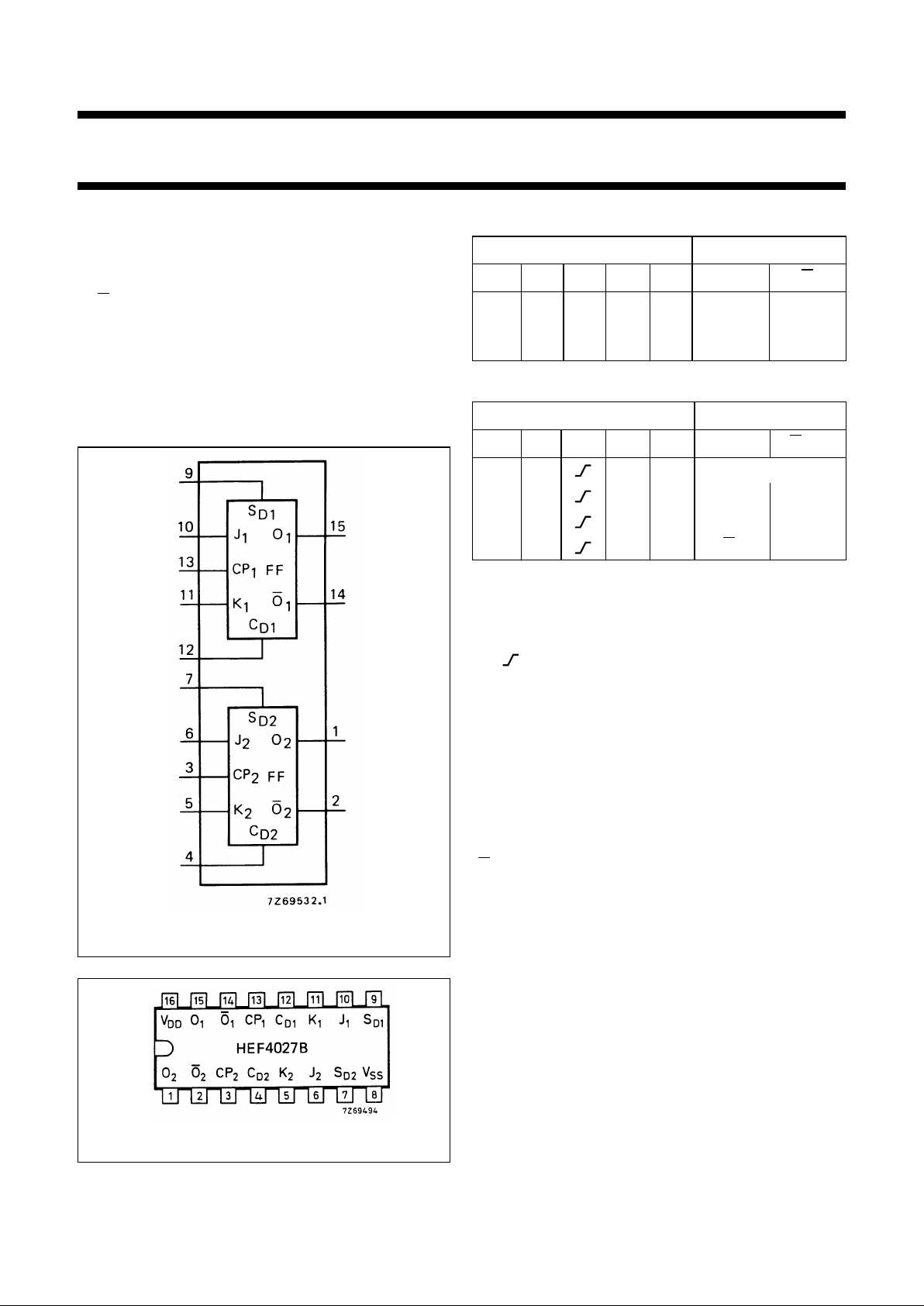

Fig.1 Functional diagram.

Fig.2 Pinning diagram.

FUNCTION TABLES

Notes

1. H = HIGH state (the more positive voltage)

L = LOW state (the less positive voltage)

X = state is immaterial

= positive-going transition

O

n + 1

= state after clock positive transition

PINNING

FAMILY DATA, I

DD

LIMITS category FLIP-FLOPS

See Family Specifications

INPUTS OUTPUTS

S

D

CDCP J K O O

HLXXX H L

LHXXX L H

HHXXX H H

INPUTS OUTPUTS

S

D

CDCP J K O

n + 1

O

n + 1

L L L L no change

LL HL H L

LL LH L H

LL HH

O

n

O

n

J,K synchronous inputs

CP clock input (L to H edge-triggered)

S

D

asynchronous set-direct input (active HIGH)

C

D

asynchronous clear-direct input (active HIGH)

O true output

O complement output

HEF4027BP(N): 16-lead DIL; plastic (SOT38-1)

HEF4027BD(F): 16-lead DIL; ceramic (cerdip) (SOT74)

HEF4027BT(D): 16-lead SO; plastic (SOT109-1)

( ): Package Designator North America

Page 3

January 1995 3

Philips Semiconductors Product specification

Dual JK flip-flop

HEF4027B

flip-flops

AC CHARACTERISTICS

V

SS

= 0 V; T

amb

=25°C; CL= 50 pF; input transition times ≤ 20 ns

V

DD

V

SYMBOL MIN. TYP. MAX.

TYPICAL EXTRAPOLATION

FORMULA

Propagation delays

CP → O, O 5 105 210 ns 78 ns + (0,55 ns/pF) C

L

HIGH to LOW 10 t

PHL

40 80 ns 29 ns + (0,23 ns/pF) C

L

15 30 60 ns 22 ns + (0,16 ns/pF) C

L

5 85 170 ns 58 ns + (0,55 ns/pF) C

L

LOW to HIGH 10 t

PLH

35 70 ns 27 ns + (0,23 ns/pF) C

L

15 30 60 ns 22 ns + (0,16 ns/pF) C

L

SD→ O 5 70 140 ns 43 ns + (0,55 ns/pF) C

L

LOW to HIGH 10 t

PLH

30 60 ns 19 ns + (0,23 ns/pF) C

L

15 25 50 ns 17 ns + (0,16 ns/pF) C

L

CD→ O 5 120 240 ns 93 ns + (0,55 ns/pF) C

L

HIGH to LOW 10 t

PHL

45 90 ns 33 ns + (0,23 ns/pF) C

L

15 35 70 ns 27 ns + (0,16 ns/pF) C

L

SD→ O 5 140 280 ns 113 ns + (0,55 ns/pF) C

L

HIGH to LOW 10 t

PHL

55 110 ns 44 ns + (0,23 ns/pF) C

L

15 40 80 ns 32 ns + (0,16 ns/pF) C

L

Fig.3 Logic diagram (one flip-flop).

Page 4

January 1995 4

Philips Semiconductors Product specification

Dual JK flip-flop

HEF4027B

flip-flops

CD→ O 5 75 150 ns 48 ns + (0,55 ns/pF) C

L

LOW to HIGH 10 t

PLH

35 70 ns 24 ns + (0,23 ns/pF) C

L

15 25 50 ns 17 ns + (0,16 ns/pF) C

L

Output transition times 5 60 120 ns 10 ns + (1,0 ns/pF) C

L

HIGH to LOW 10 t

THL

30 60 ns 9 ns + (0,42 ns/pF) C

L

15 20 40 ns 6 ns + (0,28 ns/pF) C

L

5 60 120 ns 10 ns + (1,0 ns/pF) C

L

LOW to HIGH 10 t

TLH

30 60 ns 9 ns + (0,42 ns/pF) C

L

15 20 40 ns 6 ns + (0,28 ns/pF) C

L

Set-up time 5 50 25 ns

see also waveforms

Figs 4 and 5

J,K → CP 10 t

su

30 10 ns

15 20 5 ns

Hold time 5 25 0 ns

J,K → CP 10 t

hold

20 0 ns

15 15 5 ns

Minimum clock 5 80 40 ns

pulse width; LOW 10 t

WCPL

30 15 ns

15 24 12 ns

Minimum SD,C

D

5

t

WSDH,

t

WCDH

90 45 ns

pulse width; HIGH 10 40 20 ns

15 30 15 ns

Recovery time 5

t

RSD,

t

RCD

20 −15 ns

for S

D,CD

10 15 −10 ns

15 10 −5ns

Maximum clock 5 4 8 MHz

see also waveforms

Fig.4

pulse frequency 10 f

max

12 25 MHz

J = K = HIGH 15 15 30 MHz

V

DD

V

TYPICAL FORMULA FOR P (µW)

Dynamic power 5 900 f

i

+∑(foCL) × V

DD

2

where

dissipation per 10 4 500 f

i

+∑(foCL) × V

DD

2

fi= input freq. (MHz)

package (P) 15 13 200 f

i

+∑(foCL) × V

DD

2

fo= output freq. (MHz)

C

L

= load capacitance (pF)

∑ (f

oCL

) = sum of outputs

V

DD

= supply voltage (V)

V

DD

V

SYMBOL MIN. TYP. MAX.

TYPICAL EXTRAPOLATION

FORMULA

Page 5

January 1995 5

Philips Semiconductors Product specification

Dual JK flip-flop

HEF4027B

flip-flops

APPLICATION INFORMATION

Some examples of applications for the HEF4027B are:

• Registers

• Counters

• Control circuits

Fig.4 Waveforms showing set-up times, hold times and minimum clock pulse width. Set-up and hold times are

shown as positive values but may be specified as negative values.

Fig.5 Waveforms showing recovery times for SDand CD; minimum SDand CDpulse widths.

Loading...

Loading...