HD-15530

March 1997

Features

• Support of MlL-STD-1553

• Data Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . .1.25 MBit/s

• Sync Identification and Lock-In

• Clock Recovery

• Manchester II Encode, Decode

• Separate Encode and Decode

• Low Operating Power . . . . . . . . . . . . . . . . .50mW at 5V

Ordering Information

PACKAGE TEMP. RANGE 1.25 MEGABIT/s PKG. NO.

CERDIP -40oC to +85oC HD1-15530-9 F24.6

-55oC to +125oC HD1-15530-8

SMD# 7802901JA

CLCC -40oC to +85oC HD4-15530-9 J28.A

-55oC to +125oC HD4-15530-8

SMD# 78029013A

PDIP -40oC to +85oC HD3-15530-9 E24.6

CMOS Manchester Encoder-Decoder

Description

The Intersil HD-15530 is a high performance CMOS device

intended to service the requirements of MlL-STD-1553 and

similar Manchester II encoded, time division multiplexed

serial data protocols. This LSI chip is divided into two

sections, an Encoder and a Decoder. These sections

operate completely independent of each other, e xcept f or the

Master Reset functions.

This circuit meets many of the requirements of MIL-STD-

1553. The Encoder produces the sync pulse and the parity

bit as well as the encoding of the data bits. The Decoder

recognizes the sync pulse and identifies it as well as decoding the data bits and checking parity.

This integrated circuit is fully guaranteed to support the

1MHz data rate of MlL-STD-1553 over both temperature and

voltage. It interfaces with CMOS, TTL or N channel support

circuitry, and uses a standard 5V supply.

The HD-15530 can also be used in many party line digital

data communications applications, such as an environmental control system driven from a single twisted pair cable of

fiber optic cable throughout the building.

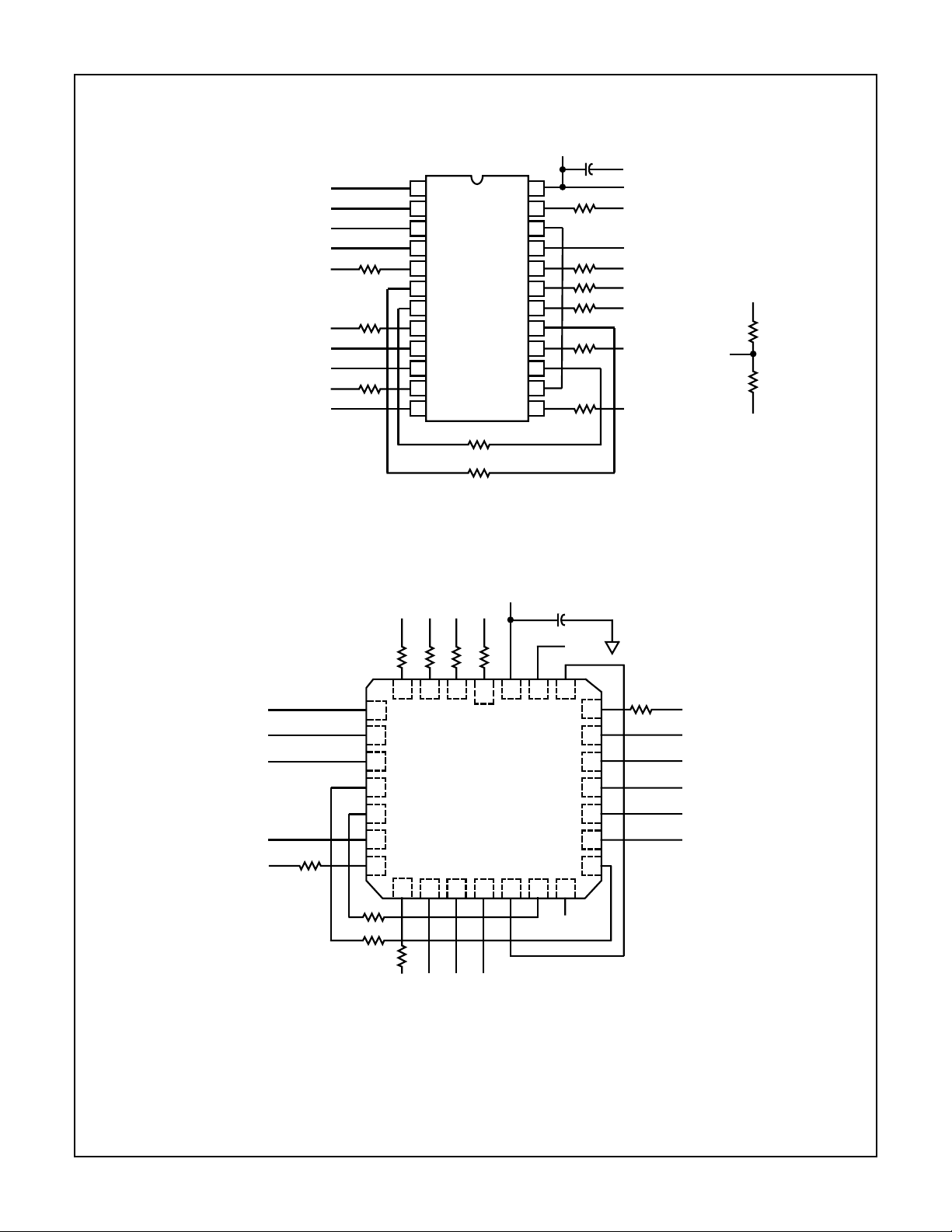

Pinouts

VALID WORD

ENCODER

SHIFT CLK

TAKE DATA

SERIAL DATA OUT

DECODER CLK

BIPOLAR ZERO IN

BIPOLAR ONE IN

UNIPOLAR DATA IN

DECODER SHIFT CLK

COMMAND/

DATA SYNC

DECODER RESET

HD-15530 (CERDIP, PDIP)

TOP VIEW

1

2

3

4

5

6

7

8

9

10

11

GND

12

24

V

CC

23

ENCODER CLK

22

SEND CLK IN

SEND DATA

21

SYNC SELECT

20

ENCODER ENABLE

19

SERIAL DATA IN

18

17

BIPOLAR ONE OUT

16

OUTPUT INHIBIT

BIPOLAR

15

ZERO OUT

14

÷ 6 OUT

MASTER RESET

13

DECODER

CLK

NC

NC

BIPOLAR

ZERO IN

BIPOLAR

ONE IN

UNIPOLAR

DATA IN

DECODER

SHIFT CLK

5

6

7

8

9

10

11

HD-15530 (CLCC)

TOP VIEW

TAKE DATA

DATA OUT

3 2 14

DECODER

DATA SYNC

ENCODER

14 15 16 17 1812 13

RESET

SERIAL

COMMAND/

SHIFT CLK

VALID

WORD

GND

RESET

MASTER

CC

V

ENCODER

CLK

28 27 26

÷ 6 OUT

BIPOLAR

ZERO OUT

SEND

CLK IN

25

24

23

22

21

20

19

INHIBIT

OUTPUT

SEND

DAT A

NC

NC

SYNC

SELECT

ENCODER

ENABLE

SERIAL

DATA IN

BIPOLAR

ONE OUT

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

5-142

File Number 2960.1

HD-15530

Block Diagrams

ENCODER DECODER

GND

12

MASTER RESET

13

SEND CLK IN

22

÷ 6 OUT

14

ENCODER

23

CLK

÷ 6

BIT

COUNTER

÷ 2

21

SEND

DAT A

ENCODER

SHIFT CLK

CHARACTER

FORMER

18 19 20

2

SERIAL

DATA IN

ENCODER

ENABLE

SYNC

SELECT

17

15

OUTPUT

INHIBIT

V

CC

BIPOLAR

ONE OUT

BIPOLAR

ZERO OUT

24

16

UNIPOLAR

DATA IN

BIPOLAR

ONE IN

BIPOLAR

ZERO IN

DECODER

CLK

MASTER

RESET

8

7

TRANSITION

FINDER

6

5

SYNCHRONIZER

13

DECODER

RESET

11

CHARACTER

IDENTIFIER

BIT

PARITY

RATE

CHECK

CLK

BIT

COUNTER

10

4

Pin Description

PIN

NUMBER TYPE NAME SECTION DESCRIPTION

1 O VALID WORD Decoder Output high indicates receipt of a valid word, (valid parity and no Manches-

ter errors).

2 O ENCODER SHIFT

CLOCK

3 O TAKE DATA Decoder Output is high during receipt of data after identification of a sync pulse and

4 O SERIAL DATA OUT Decoder Delivers received data in correct NRZ format.

5 I DECODER CLOCK Decoder Input drives the transition finder, and the synchronizer which in turn

6 I BIPOLAR ZERO IN Decoder A high input should be applied when the bus is in its negative state. This pin

7 I BIPOLAR ONE IN Decoder A high input should be applied when the bus is in its positive state. This pin

8 I UNLPOLAR DATA IN Decoder With pin 6 high and pin 7 low, this pin enters unipolar data into the tr ansition

9 O DECODER SHIFT

CLOCK

10 O COMMAND SYNC Decoder Output of a high from this pin occurs dur ing output of decoded data which

11 I DECODER RESET Decoder A high input to this pin during a rising edge of DECODER SHIFT CLOCK

12 I GROUND Both Ground Supply pin.

13 I MASTER RESET Both A high on this pin clears 2:1 counters in both Encoder and Decoder, and

14 O ÷ 6 OUT Encoder Output from 6:1 divider which is driven by the ENCODER CLOCK.

15 O BIPOLAR ZERO OUT Encoder An active low output designed to drive the zero or negative sense of a

16 I OUTPUT INHIBIT Encoder A low on this pin forces pin 15 and 17 high, the inactive states.

17 O BIPOLAR ONE OUT Encoder An active lo w output designed to drive the one or positiv e sense of a bipolar

Encoder Output for shifting data into the Encoder. The Encoder samples SDI on the

low-to-high transition of Encoder Shift Clock.

two valid Manchester data bits.

supplies the clock to the balance of the decoder, input a frequency equal to

12X the data rate.

must be held high when the Unipolar input is used.

must be held low when the Unipolar input is used.

finder circuit. If not used this input must be held low.

Decoder Output which delivers a frequency (DECODER CLOCK ÷ 12), synchro-

nized by the recovered serial data stream.

was preceded by a Command (or Status) synchronizing character. A low

output indicates a Data synchronizing character.

resets the decoder bit counting logic to a condition ready for a new word.

resets the ÷ 6 circuit.

bipolar line driver.

line driver.

3

TAKE

DAT A

COMMAND/

DATA SYNC

SERIAL

DATA OUT

VALID

WORD

91DECODER

SHIFT

CLK

5-143

HD-15530

Pin Description

PIN

NUMBER TYPE NAME SECTION DESCRIPTION

18 I SERIAL DATA IN Encoder Accepts a serial data stream at a data rate equal to ENCODER SHIFT

19 I ENCODER ENABLE Encoder A high on this pin initiates the encode cycle. (Subject to the preceeding

20 I SYNC SELECT Encoder Actuates a Command sync for an input high and Data sync for an input low.

21 O SEND DATA Encoder An active high output which enables the external source of serial data.

22 I SEND CLOCK IN Encoder Clock input at a frequency equal to the data rate X2, usually driven by ÷ 6

23 I ENCODER CLOCK Encoder Input to the 6:1 divider, a frequency equal to the data rate X12 is usually

24 I V

I = Input O = Output

(Continued)

CC

CLOCK.

cycle being complete.)

output.

input here.

Both VCC is the +5V power supply pin. A 0.1µF decoupling capacitor from V

(pin 24) to GROUND (pin 12) is recommended.

Encoder Operation

The Encoder requires a single clock with a frequency of

twice the desired data rate applied at the SEND CLOCK

input. An auxiliary divide by six counter is provided on chip

which can be utilized to produce the SEND CLOCK by dividing the DECODER CLOCK.

The Encoder’s cycle begins when ENCODER ENABLE is

high during a falling edge of ENCODER SHIFT CLOCK .

This cycle lasts for one word length or twenty ENCODER

SHIFT CLOCK periods. At the next low-to-high transition of

the ENCODER SHIFT CLOCK, a high SYNC SELECT input

actuates a command sync or a low will produce a data sync

for the word . When the Encoder is ready to accept data,

2

the SEND DATA output will go high and remain high for sixteen ENCODER SHIFT CLOCK periods . During these

3

sixteen periods the data should be clocked into the SERIAL

DATA input with every high-to-low transition of the

ENCODER SHIFT CLOCK so it can be sampled on the lowto-high transition - . After the sync and Manchester II

coded data are transmitted through the

3 4

BIPOLAR ONE and

BIPOLAR ZERO outputs, the Encoder adds on an additional

bit which is the parity for that word . If ENCODER

5

ENABLE is held high continuously, consecutive words will be

encoded without an interframe gap. ENCODER ENABLE

1

must go low by time as shown to prevent a consecutive

5

word from being encoded. At any time a low on

INHIBIT input will force both bipolar outputs to a high state

but will not affect the Encoder in any other way.

To abort the Encoder transmission a positive pulse must be

applied at MASTER RESET. Anytime after or during this

pulse, a low-to-high transition on SEND CLOCK clears the

internal counters and initializes the Encoder for a new word.

CC

OUTPUT

SEND CLK

ENCODER

SHIFT CLK

ENCODER

ENABLE

SYNC SELECT

SEND DATA

SERIAL

DATA IN

BIPOLAR

ONE OUT

BIPOLAR

ZERO OUT

3210TIMING

DON’T CARE

VALID DON’T CARE

1112131415 10

2ND HALF1ST HALF

SYNCSYNC

1 2 3 4 5

FIGURE 1.

1112131415

1112131415

0123

5-144

1915 16 17 187654

P0123

P0123

Decoder Operation

HD-15530

The Decoder requires a single clock with a frequency of 12

times the desired data rate applied at the DECODER

CLOCK input. The Manchester II coded data can be

presented to the Decoder in one of two ways. The BIPOLAR

ONE and BIPOLAR ZERO inputs will accept data from a

comparator sensed transformer coupled bus as specified in

Military Spec 1553. The UNIPOLAR DATA input can only

accept non-inverted Manchester II coded data. (e.g. from

BIPOLAR ONE OUT of an Encoder through an inverter to

Unipolar Data Input).

The Decoder is free running and continuously monitors its

data input lines for a valid sync character and two valid

Manchester data bits to start an output cycle. When a valid

sync is recognized , the type of sync is indicated on

COMMAND/

DATA SYNC output. If the sync character was a

command sync, this output will go high and remain high

for sixteen DECODER SHIFT CLOCK periods , otherwise

1

2

3

it will remain low. The TAKE DATA output will go high and

remain high - while the Decoder is transmitting the

2 3

decoded data through SERIAL DATA OUT. The decoded

3210TIMING

DECODER

SHIFT CLK

BIPOLAR

ONE IN

BIPOLAR

ZERO IN

TAKE DATA

2ND HALF1ST HALF

SYNCSYNC

data available at SERIAL DATA OUT is in NRZ format. The

DECODER SHIFT CLOCK is provided so that the decoded

bits can be shifted into an external register on every low-tohigh transition of this clock - . Note that DECODER

2 3

SHIFT CLOCK may adjust its phase up until the time that

TAKE DATA goes high.

After all sixteen decoded bits have been transmitted the

3

data is checked for odd parity. A high on VALID WORD

output indicates a successful reception of a word without

4

any Manchester or parity errors. At this time the Decoder is

looking for a new sync character to start another output

sequence. VALID WORD will go low approximately 20

DECODER SHIFT CLOCK periods after it goes high if not

reset low sooner by a valid sync and two valid Manchester

bits as shown .

1

At any time in the above sequence a high input on

DECODER RESET during a low-to-high transition of

DECODER SHIFT CLOCK will abort transmission and initialize the Decoder to start looking for a new sync character.

8

1112131415

10

1112131415

10

16 17 18 197654

P012

P012

COMMAND/

DATA SYNC

SERIAL

DATA OUT

UNDEFINED

(FROM PREVIOUS RECEPTION)VALID WORD

1

2

FIGURE 2.

12131415

12340

3 4

5-145

HD-15530

How to Make Our MTU Look Like a Manchester Encoded UART

VALID WORD

DECODER

ENCODER CLK

BIPOLAR

ZERO IN

BIPOLAR

ONE IN

UNIPOLAR

DATA IN

COMMAND

SYNC

DECODER

RESET

A B CK H

74LS164

PARALLEL OUT

AB CK

74LS164

1

2

3

4

5

6

7

8

9

10

11

12

FIGURE 3.

V

CC

SYNC

24

23

22

21

20

19

18

17

16

15

14

13

OHSH/LD CK SI

74165

PARALLEL IN

H

74165

CK

SH/LDO

SELECT

ENCODER

ENABLE

BIPOLAR

ONE OUT

INHIBIT

OUTPUT

BIPOLAR

ZERO OUT

MASTER

RESET

Typical Timing Diagrams for a Manchester Encoded UART

VALID

ENCODER ENABLE

SYNC SELECT

PARALLEL IN

BIPOLAR ONE OUT

BIPOLAR ZERO OUT

BIPOLAR ONE IN

BIPOLAR ZERO IN

COMMAND SYNC

PARALLEL OUT

SYNC MSB LSB PARITY

FIGURE 4. ENCODER TIMING

SYNC MSB LSB PARITY

VALID

P

P

P

P

VALID

VALID

VALID WORD

FROM

PREVIOUS

RECEPTION

FIGURE 5. DECODER TIMING

5-146

HD-15530

MIL-STD-1553

The 1553 standard defines a time division multiplexed data

bus for application within aircraft. The bus is defined to be

bipolar, and encoded in a Manchester II format, so no DC

component appears on the bus. This allows transformer

coupling and excellent isolation among systems and their

environment.

The HD-15530 supports the full bipolar configuration,

assuming a bus driver configuration similar to that in Figure

1. Bipolar inputs from the bus, like Figure 2, are also accommodated.

The signaling format in MlL-STD-1553 is specified on the

assumption that the network of 32 or fewer terminals are

controlled by a central control unit by means of Command

BUS

“1”

“0”

FIGURE 6. SIMPLIFIED MIL-STD-1553 DRIVER FIGURE 7. SIMPLIFIED MIL-STD-1553 RECEIVER

Words. Terminals respond with Status Words. Each word is

preceded by a synchronizing pulse, and followed by parity

bit, occupying a total of 20µs. The word f ormats are shown in

Figure 4. The special abbreviations are as follows:

P Parity, which is defined to be odd, taken across all 17

bits.

R/T Receive on logical zero, transmit on ONE.

ME Message Error if logical 1.

TF Terminal Flat, if set, calls for controller to request

self-test data.

The paragraphs above are intended only to suggest the

content of MlL-STD-1553, and do not completely describe its

bus requirements, timing or protocols.

BUS

+

“1” REF

“0” REF

-

+

“1”

“0”

COMMAND

SYNC

COMMAND WORD (FROM CONTROLLER TO TERMINAL)

DAT A

SYNC

BIT

PERIOD

LOGICAL ONE DATA

LOGICAL ZERO DATA

BIT

PERIOD

BIT

PERIOD

5551

SYNC

DATA WORD (SENT EITHER DIRECTION)

SYNC

STATUS WORD (FROM TERMINAL TO CONTROLLER)

SYNC

TERMINAL

ADDRESS

591

TERMINAL

ADDRESS

1

SUB ADDRESS

/MODE

R/T

16 1

CONTROL WORD

1

ME

FIGURE 8. MIL-STD-1553 CHARACTER FORMATS FIGURE 9. MIL-STD-1553 WORD FORMATS

NOTE: This page is a summary of MIL-STD-1553 and is not intended to describe the operation of the HD-15530.

DATA WORD

COUNT

TF

191817161514131211109876543210

P

P

1

PCODE FOR FAILURE MODES

5-147

HD-15530

Absolute Maximum Ratings Thermal Information

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+7.0V

Input, Output or I/O Voltage . . . . . . . . . . . . GND-0.3V to VCC+0.3V

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Class 1

Operating Conditions

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +4.5V to +5.5V

Temperature Range (TA)

HD-15530-9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-40oC to +85oC

HD-15530-8 . . . . . . . . . . . . . . . . . . . . . . . . . . . .-55oC to +125oC

Encoder/Decoder Clock Rise Time . . . . . . . . . . . . . . . . . . .8ns Max

Encoder/Decoder Clock Fall Time . . . . . . . . . . . . . . . . . . . .8ns Max

Sync Transition Span (TD2) . . . . . . . . . . . . . . . 18 TDC Typ (Note 1)

Short Data Transition Span (TD4) . . . . . . . . . . . 6 TDC Typ (Note 1)

Long Data Transition Span (TD5). . . . . . . . . . . 12 TDC Typ (Note 1)

CAUTION: Stresses above those listed in “Absolute Maxim um Ratings” ma y cause permanent damage to the device . This is a stress only rating and oper ation of

the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Thermal Resistance (Typical) θJA (oC/W) θJC (oC/W)

CERDIP Package . . . . . . . . . . . . . . . . 55 12

CLCC Package . . . . . . . . . . . . . . . . . . 65 14

Plastic DIP Package . . . . . . . . . . . . . . 60 N/A

Maximum Junction Temperature

Ceramic Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +175oC

Plastic Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150oC

Maximum Storage Temperature Range . . . . . . . . .-65oC to +150oC

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . .+300oC

Die Characteristics

Gate Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .456 Gates

DC Electrical Specifications V

= 5V ±10%, TA = -40oC to +85oC (HD-15530-9)

CC

TA = -55oC to +125oC (HD-15530-8)

LIMITS

PARAMETER SYMBOL

Input LOW Voltage V

Input HIGH Voltage V

Input LOW Clock Voltage V

Input HIGH Clock Voltage V

Output LOW Voltage V

Output HIGH Voltage V

Input Leakage Current I

Standby Supply Current I

Operating Power Supply Current I

CCSB

CCOP

Function Test F

IL

lH

ILC

IHC

OL

OH

I

T

- 0.2 V

0.7 V

CC

CCVCC

-VCC = 4.5V and 5.5V V

= 4.5V and 5.5V V

- GND +0.5 VCC = 4.5V and 5.5V V

VCC -0.5 - VCC = 4.5V and 5.5V V

- 0.4 IOL = 1.8mA (Note 2), VCC = 4.5V V

2.4 - IOH = -3mA (Note 2), VCC = 4.5V V

-1.0 +1.0 VI = GND or VCC, VCC = 5.5V µA

-2V

-10V

= VCC = 5.5V Output Open mA

IN

= 5.5V, VIN = VCC, f =15MHz, Outputs Open mA

CC

- - (Note 3) -

TEST CONDITIONS UNITSMIN MAX

NOTES:

1. TDC = Decoder clock period = 1/FDC

2. Interchanging of force and sense conditions is permitted.

3. Tested as follows: = f = 15MHz, VIH = 70% VCC, VIL = 20% VCC, CL = 50pF, VOH≥ 1.5V and VOL≤ 1.5V.

Capacitance T

= +25oC; Frequency = 1MHz

A

SYMBOL PARAMETER TYPICAL UNITS CONDITIONS

C

IN

C

O

Input Capacitance 15 pF All measurements are referenced to device GND

Output Capacitance 15 pF

5-148

HD-15530

AC Electrical Specifications V

PARAMETER SYMBOL

ENCODER TIMING

Encoder Clock Frequency FEC VCC = 4.5V and 5.5V, CL = 50pF - 15 MHz

Send Clock Frequency FESC VCC = 4.5V and 5.5V, CL = 50pF - 2.5 MHz

Encoder Data Rate FED VCC = 4.5V and 5.5V, CL = 50pF - 1.25 MHz

Master Reset Pulse Width TMR VCC = 4.5V and 5.5V, CL = 50pF 150 - ns

Shift Clock Delay TE1 VCC = 4.5V and 5.5V, CL = 50pF - 125 ns

Serial Data Setup TE2 VCC = 4.5V and 5.5V, CL = 50pF 75 - ns

Serial Data Hold TE3 VCC = 4.5V and 5.5V, CL = 50pF 75 - ns

Enable Setup TE4 VCC = 4.5V and 5.5V, CL = 50pF 90 - ns

Enable Pulse Width TE5 VCC = 4.5V and 5.5V, CL = 50pF 100 - ns

Sync Setup TE6 VCC = 4.5V and 5.5V, CL = 50pF 55 - ns

Sync Pulse Width TE7 VCC = 4.5V and 5.5V, CL = 50pF 150 - ns

Send Data Delay TE8 VCC = 4.5V and 5.5V, CL = 50pF 0 50 ns

Bipolar Output Delay TE9 VCC = 4.5V and 5.5V, CL = 50pF - 130 ns

Enable Hold TE10 VCC = 4.5V and 5.5V, CL = 50pF 10 - ns

Sync Hold TE11 VCC = 4.5V and 5.5V, CL = 50pF 95 - ns

DECODER TIMING

Decoder Clock Frequency FDC VCC = 4.5V and 5.5V, CL = 50pF - 15 MHz

Decoder Data Rate FDD VCC = 4.5V and 5.5V, CL = 50pF - 1.25 MHz

Decoder Reset Pulse Width TDR VCC = 4.5V and 5.5V, CL = 50pF 150 - ns

Decoder Reset Setup Time TDRS VCC = 4.5V and 5.5V, CL = 50pF 75 - ns

Decoder Reset Hold Time TDRH VCC = 4.5V and 5.5V, CL = 50pF 10 - ns

Master Reset Pulse TMR VCC = 4.5V and 5.5V, CL = 50pF 150 - ns

Bipolar Data Pulse Width TD1 VCC = 4.5V and 5.5V, CL = 50pF TDC + 10

One Zero Overlap TD3 VCC = 4.5V and 5.5V, CL = 50pF - TDC - 10

Sync Delay (ON) TD6 VCC = 4.5V and 5.5V, CL = 50pF -20 110 ns

Take Data Delay (ON) TD7 VCC = 4.5V and 5.5V, CL = 50pF 0 110 ns

Serial Data Out Delay TD8 VCC = 4.5V and 5.5V, CL = 50pF - 80 ns

Sync Delay (OFF) TD9 VCC = 4.5V and 5.5V, CL = 50pF 0 110 ns

Take Data Delay (OFF) TD10 VCC = 4.5V and 5.5V, CL = 50pF 0 110 ns

Valid Word Delay TD11 VCC = 4.5V and 5.5V, CL = 50pF 0 110 ns

NOTES:

1. TDC = Decoder clock period = 1/FDC

2. AC Testing as follows: Input levels: VIH = 70% VCC, VIL = 20% VCC; Input rise/fall times driven at 1ns/V; Timing Reference levels: 1.5V;

Output load: CL = 50pF.

= 5V ±10%, TA = -40oC to +85oC (HD-15530-9)

CC

TA = -55oC to +125oC (HD-15530-8)

(NOTE 2)

TEST CONDITIONS

LIMITS

UNITSMIN MAX

-ns

(Note 1)

ns

(Note 1)

5-149

Timing Waveforms

SEND CLOCK

ENCODER SHIFT CLOCK

SERIAL DATA IN

SEND CLOCK

ENCODER SHIFT CLOCK

ENCODER ENABLE

SYNC SELECT

HD-15530

T

E1

T

E2

T

E3

VALIDVALID

T

E1

T

E4

T

E5

T

E6

VALID

T

E7

ENCODER SHIFT CLOCK

SEND DATA

SEND CLOCK

BIPOLAR ONE OUT OR

BIPOLAR ZERO OUT

DECODER SHIFT CLOCK

COMMAND/DATA SYNC

TAKE DATA

DECODER SHIFT CLOCK

SERIAL DATA OUT

DECODER SHIFT CLOCK

COMMAND/

DATA SYNC

TAKE DATA

T

E8

T

E9

FIGURE 10. ENCODER TIMING

T

D6

T

D7

T

D8

DATA BIT

T

D9

T

D10

VALID WORD

DECODER SHIFT CLOCK

DECODER RESET

T

D11

T

DRS

T

DR

T

DRH

FIGURE 11. DECODER TIMING

5-150

HD-15530

Timing Waveforms

BIPOLAR ONE IN

BIPOLAR ZERO IN

BIPOLAR ONE IN

BIPOLAR ZERO IN

BIPOLAR ONE IN

BIPOLAR ZERO IN

UNIPOLAR IN

UNIPOLAR IN

UNIPOLAR IN

(Continued)

NOTE: UNIPOLAR IN = 0, FOR NEXT DIAGRAMS.

T

T

D1

T

D1

T

D1

T

D3

T

D4

COMMAND SYNC

T

D2

T

D2

DATA SYNC

T

D3

T

D1

T

D5

ONE ZERO ONE

NOTE: BIPOLAR ONE IN = 0; BIPOLAR ZERO IN = 1, FOR NEXT DIAGRAMS.

T

D2

COMMAND SYNC

T

D2

DATA SYNC

T

T

D4

D5

ONE ZERO ONE

D3

T

D1

T

D1

T

D3

T

D1

T

D3

T

D2

T

D2

T

D5

T

D2

T

D2

T

D5

BIT PERIODBIT PERIODBIT PERIOD

T

D3

T

D3

T

D3

T

D1

T

D4

T

D4

T

D3

T

D4

ONE

FIGURE 12. DECODER TIMING

Test Load Circuit AC Testing Input, Output Waveform

INPUT

DUT

CL9

(NOTE)

NOTE: Includes stray and jig capacitance.

V

IH

50% 50%

V

IL

AC Testing: All input signals must switch between VIL and VIH. Input

rise and fall times are driven at 1ns per volt.

OUTPUT

V

OH

V

OL

5-151

Burn-In Circuits

GND

GND

GND

F0

HD-15530

HD1-15530 CERDIP

V

CC

C1

GND

A

A

A

A

R1

R1

A

A

R1

1

2

3

4

5

6

7

8

9

10

11

12

R1

R1

24

23

22

21

20

19

18

17

16

15

14

13

R1

R1

R1

R1

R1

R1

V

CC

F0

A

GND

V

CC

GND

V

CC

GND

V

CC

R1

A

R1

GND

NOTES:

1. VCC = 5.5V ± 0.5V

2. VIH = 4.5V ± 10%

3. VIL = -0.2V +0.4V

4. R1 = 47KΩ± 5%

5. R2 = 1.8KΩ± 5%

6. F0 = 100KHz ± 10%

7. C1 = 0.01µF Min.

NC

NC

GND

GND

F0

R2

GND GND

R2

5

6

7

8

9

10

11

R2

R2

R2

HD4-15530 CLCC

R2

GND

R2

R2

14 15 16 17 1812 13

GND

GNDGNDGND

GND

3 2 14

V

CC

28 27 26

C1

V

CC

F0

25

R2

24

23

22

21

20

19

GND

NC

NC

GND

V

CC

GND

5-152

Die Characteristics

HD-15530

DIE DIMENSIONS:

155 x 195 x 19mils

METALLIZATION:

Type: Si-Al

Thickness: 11k

Å ±2kÅ

Metallization Mask Layout

TAKE DATA

SERIAL DATA OUT

HD-15530

ENCODER VALID

WORDSHIFT CLK

GLASSIVATION:

Type: SiO

2

Thickness: 8kA ±1kÅ

WORST CASE CURRENT DENSITY:

1.8 x 10

V

CC

5

A/cm

2

ENCODER CLK

SEND CLK IN

SEND DATA

DECODER CLK

SYNC SELECT

BIPOLAR ZERO IN

BIPOLAR ONE IN

UNIPOLAR DATA IN

DECODER SHIFT CLK

COMMAND/DATA SYNC

DECODER

RESET

RESET

÷ 6 OUTMASTERGND

ENCODER ENABLE

SERIAL DATA IN

BIPOLAR ONE OUT

OUTPUT INHIBIT

BIPOLAR ZERO OUT

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate

and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which

may result from its use. No license is granted by implication or otherwise under an y patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

5-153

Loading...

Loading...