Page 1

G S I T E C H N O L O G Y

GS820V32Q/T

GS820V32Q/T

4/5/6, 2.5V I/O, 2.0mA

64K x 32 Burst

Features

• Single 3.3V +5%/-5% power supply

• Separate VDDQ to allow 2.375V to 3.465V output supply level

• High frequency operation: 117MHz

• Fast access time: 4.5ns Clock to Q

• Low power: 0.5mA ISB and IDD static

• FT mode pin for either flow-thru or pipeline operation

• LBO mode pin for linear or interleave (Pentium

burst mode

TM

and X86)

• Byte write (BWE) and global write (GW) operation

• 3 chip enable signals for easy depth expansion

• 2 cycles enable (pipeline mode) and 1 cycle disable to allow multiple

bank without data buss contention

• Compatible to both 3.3V and 2.5V interface level

• Standard Industrial Temperature Option: -40 to +85C

• JEDEC standard 100 lead package:

Q: QFP

T: TQFP

Pentium is a trademark of Intel Corp.

Functional Description

The GS820V32 is a 64Kx32 high performance synchronous SRAM

with 2 bit burst counter. It is designed to provide L2 Cache for PentiumTM and other high performance CPU. Addresses (A0-15), data

IOs (DQ1-32), chip enables (CE1, CE2, CE3), address control inputs

(ADSP, ADSC, ADV) and write control inputs (BW1, BW2, BW3,

BW4, BWE, GW) are synchronous and are controlled by a positive

edge triggered clock (CLK).

80-133MHz (P/L)

66MHz Flow-Thru

Output enable (OE) and power down control (ZZ) are asynchronous. 2 mode control pins (LBO & FT) define 4 operation modes

of linear/interleave burst order and output flow-thru/pipeline.

Burst can be initiated with either ADSP or ADSC inputs. Subsequent burst address are generated internally and are controlled by

ADV. The burst sequence is either interleave order (Pentium

and X86) or linear order and is defined by LBO.

Output registers are provided and are controlled by FT mode pin.

With FT mode pin, Output registers can be programmed in either

pipeline mode for very high frequency operation (117MHz) or

flow-thru mode for reduced latency.

Byte write operation can be obtained through byte write enable

(BWE) input combined with 4 individual byte write signals

BW1-4. In addition, global write (GW) signal is also available to

write all bytes at once.

Low power state (standby mode) can be obtained either through

the assertion of ZZ signal or simply stop the clock (CLK). In

standby mode, memory data are still retained. Low power design

of 0.5mA standby are provided on L version.

The GS820V32 operates from a 3.3V power supply and all

inputs and outputs are LVTTL compatible. Separate output

power (VDDQ) and ground (VSSQ) pins are employed to decouple output noise from internal circuit and VDDQ allow user

the flexibility to employ lower output supply level like 2.5V.

GS820V32’s interface level is also compatble to 2.5V supply

level.

The GS820V32 is implemented with GSI’s high performance

CMOS technology and is available in JEDEC standard 100 lead

QFP ( Q version ) and TQFP ( T version) package.

TM

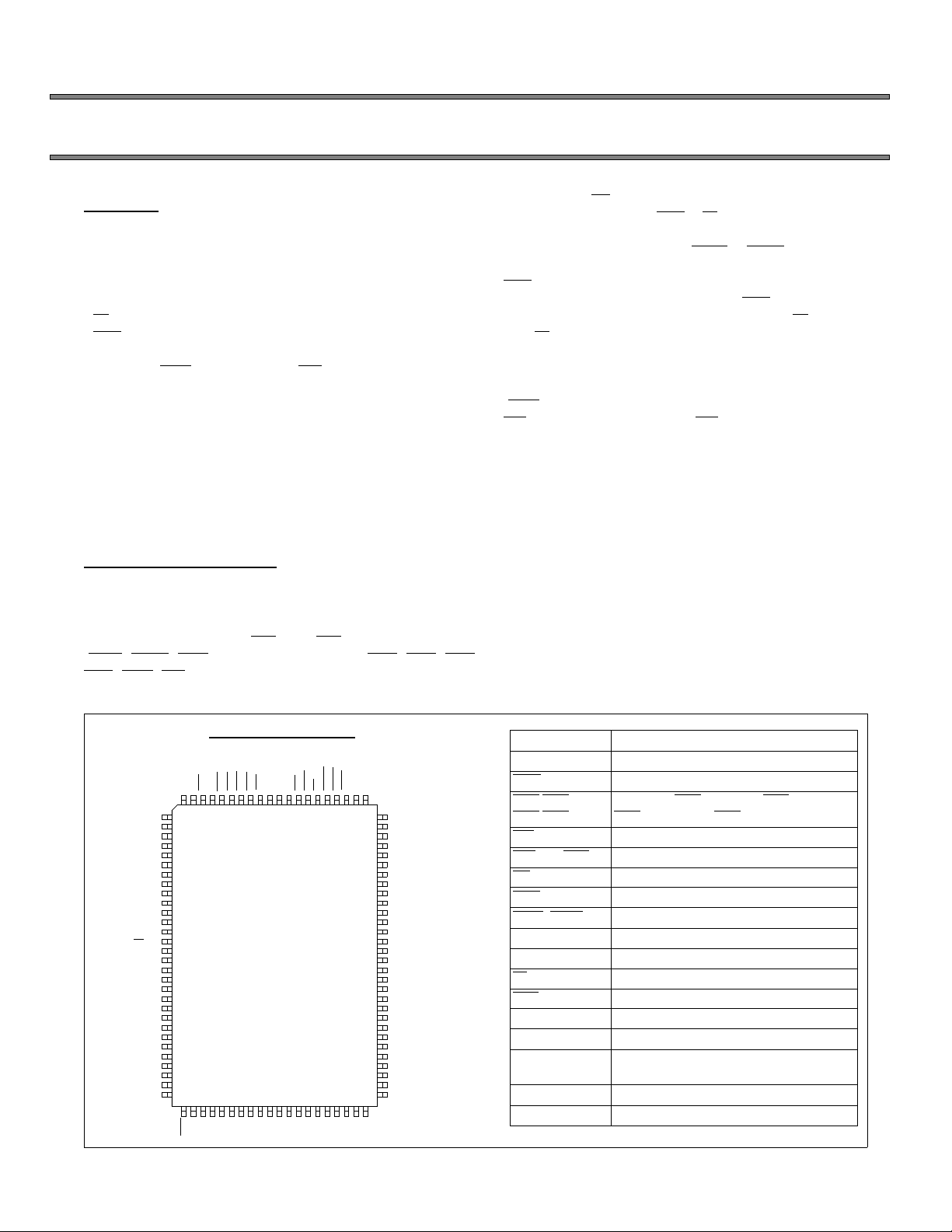

Pin configuration

Top view

A6

A7

CE1

CE2

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81

NC

1

DQ17

2

DQ18

3

VDDQ

4

VSSQ

5

DQ19

6

DQ20

7

DQ21

8

DQ22

9

VSSQ

10

11

VDDQ

12

DQ23

13

DQ24

14

FT

15

VDD

NC

16

VSS

17

DQ25

18

DQ26

19

VDDQ

20

VSSQ

21

22

DQ27

23

DQ28

24

DQ29

25

DQ30

26

VSSQ

27

VDDQ

28

DQ31

29

DQ32

30

NC

31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

LBOA5A4

A3A2A1A0NC

Rev. 9/09/97 1/15

CE3

VDD

BW2

BW1

BW3

BW4

GW

BWE

VSS

OE

CLK

100 pin QFP / TQFP

NC

NC

VSS

NC

A10

A11

VDD

ADVA8A9

ADSP

ADSC

NC

80

DQ16

79

DQ15

78

VDDQ

77

VSSQ

76

DQ14

75

DQ13

74

DQ12

73

DQ11

72

71

VSSQ

70

VDDQ

69

DQ10

68

DQ9

67

VSS

66

NC

65

VDD

64

ZZ

63

DQ8

DQ7

62

61

VDDQ

60

VSSQ

59

DQ6

58

DQ5

57

DQ4

56

DQ3

55

VSSQ

54

VDDQ

53

DQ2

52

DQ1

51

NC

NC

A13

A15

A12

A14

A0-15 Address Inputs

CLK Clock Input

BWE Byte Write Enable

BW1,BW2

BW3,BW4

Byte Write. BW1 for DQ1-8; BW2 for DQ9-16;

BW3 for DQ17-24; BW4 for DQ25-32

GW Global Write Enable

CE1,CE2, CE3 Chip Enable

OE Output Enable

ADV Burst Address advance

ADSP, ADSC Address Status

DQ1-32 Data I/O

ZZ Power down control

FT Flow-Thru mode

LBO Linear Burst mode

VDD 3.3V Power Supply

VSS Ground

VDDQ Output Power Supply, 2.375V to VDD

(3.465Vmax)

VSSQ Output Ground

NC No Connect

Page 2

G S I T E C H N O L O G Y

GS820V32Q/T

GS820V32Q/T

4/5/6, 2.5V I/O, 2.0mA

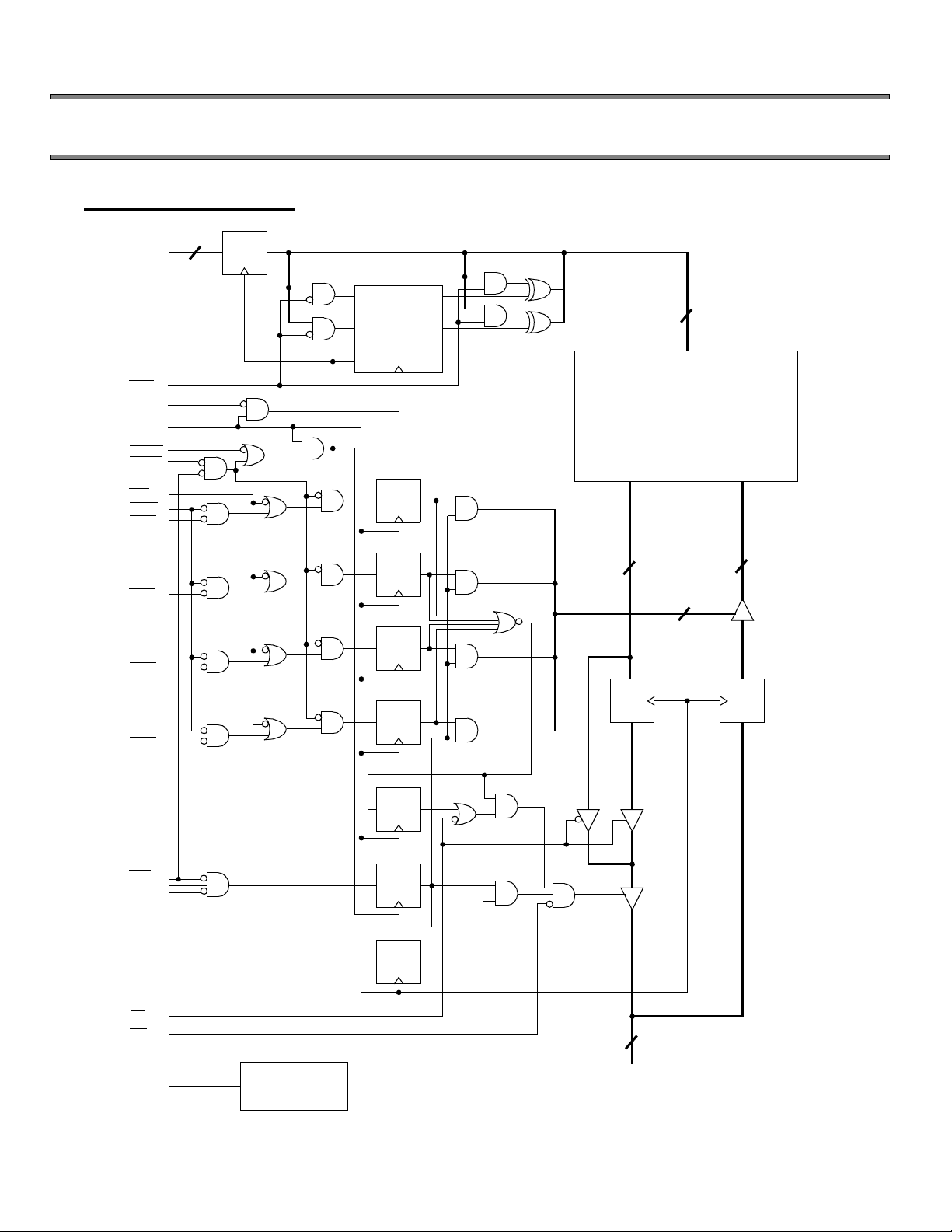

Functional Block Diagram

16

A0-15

LBO

ADV

CLK

ADSC

ADSP

GW

BWE

BW1

BW2

Register

D Q

64K x 32 Burst

Q0

Q1

A0

A1

A0

A1

D0

D1

Load

Binary

Counter

Register

D Q

Register

D Q

16

A

64Kx32

Memory

Array

Q D

32

4

80-133MHz (P/L)

66MHz Flow-Thru

32

BW3

BW4

CE1

CE2

CE3

FT

OE

ZZ

Powerdown

Control

Register

D Q

Register

D Q

Register

D Q

Register

D Q

Register

D Q

DQ

Register

32

DQ1-32

Register

DQ

Rev. 9/09/97 2/15

Page 3

G S I T E C H N O L O G Y

GS820V32Q/T

GS820V32Q/T

4/5/6, 2.5V I/O, 2.0mA

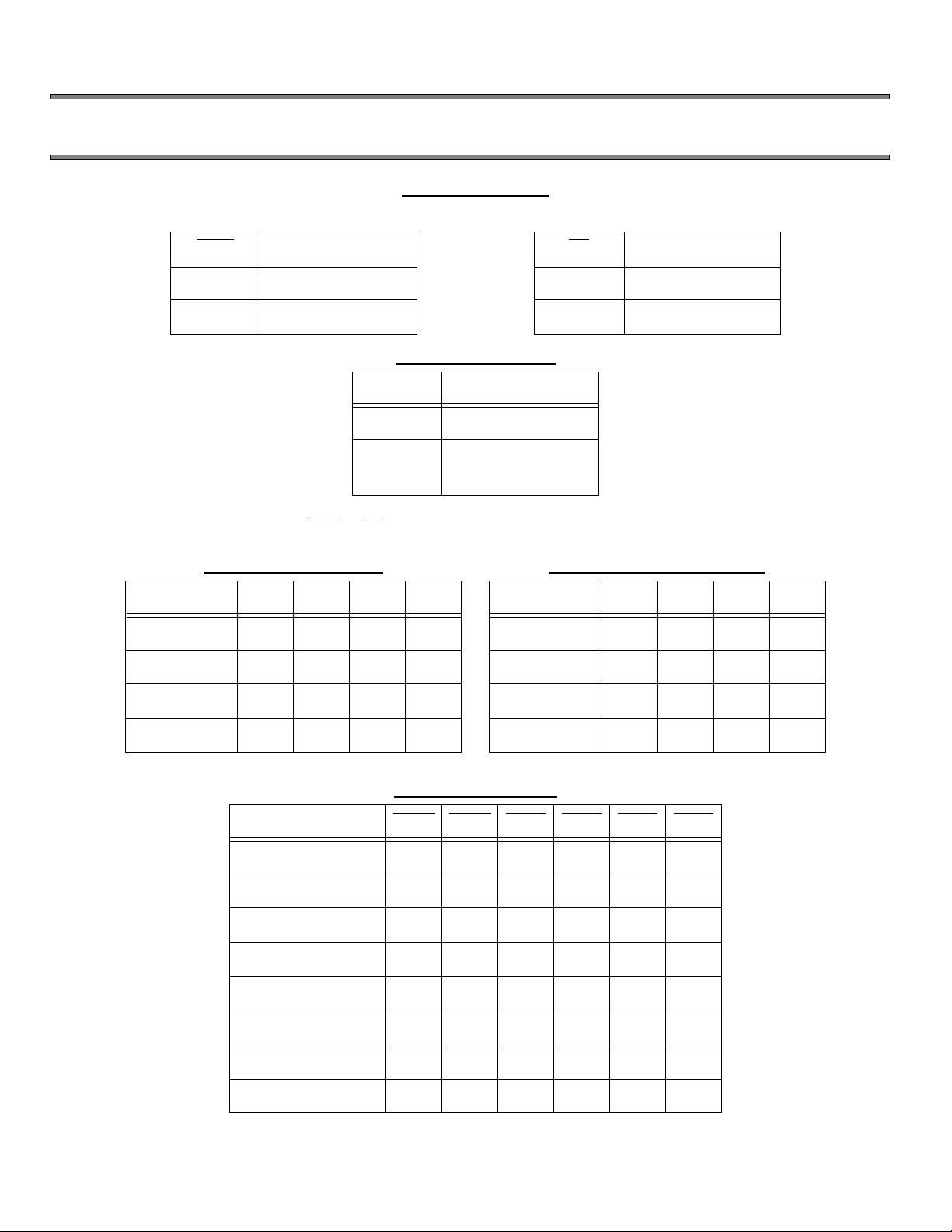

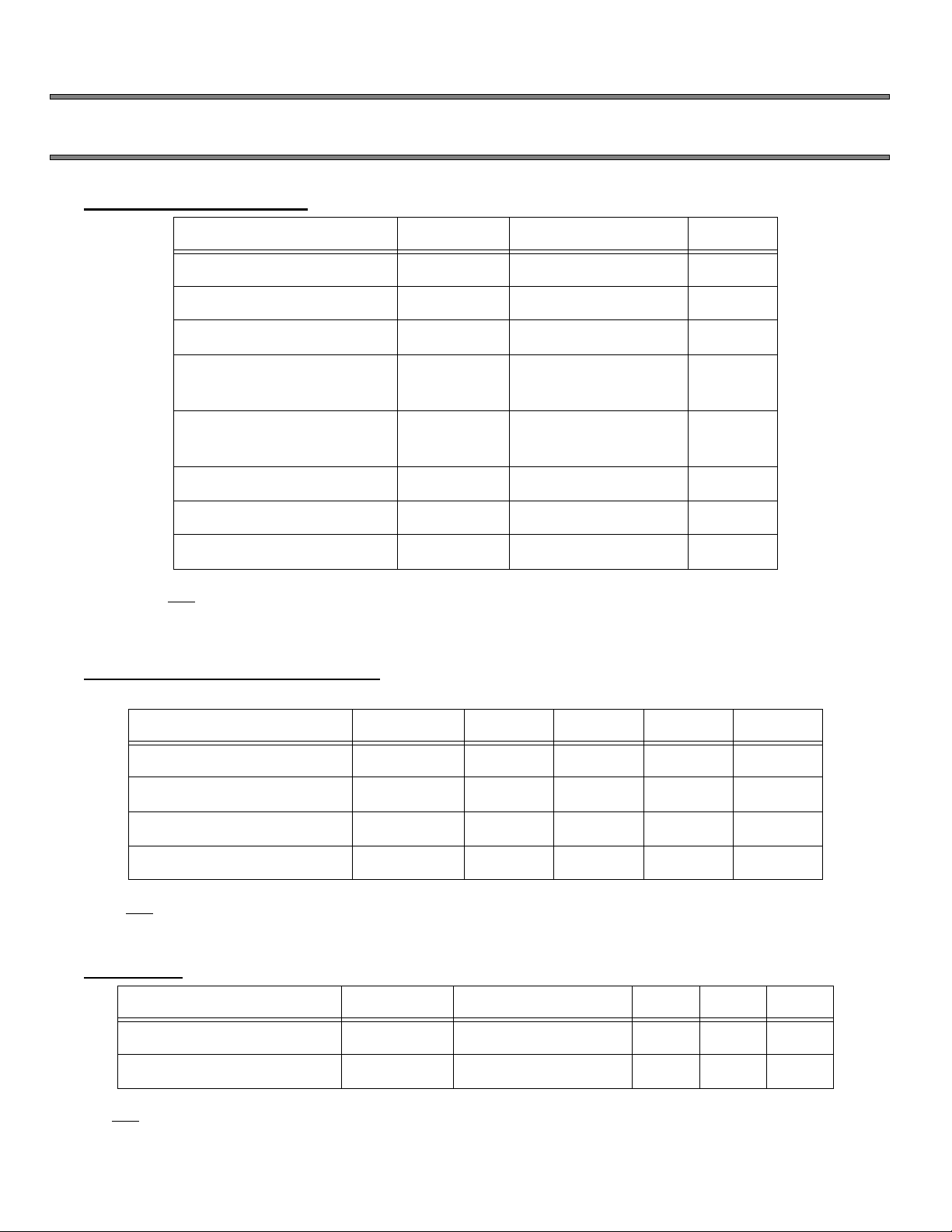

LBO Function

L Linear Burst

H or NC Interleaved Burst

Note: There are pull up devices on LBO and FT pins and pull down device on ZZ pin, so those input pins can be unconnected and

the chip will operate in the default states as specified in the above tables.

Linear Burst sequence

64K x 32 Burst

Mode pin function

FT Function

L Flow-Thru

H or NC Pipeline

Power down control

ZZ Function

L or NC Active

H Standby

IDD=ISB

Interleaved Burst sequence

80-133MHz (P/L)

66MHz Flow-Thru

A[1:0] A[1:0] A[1:0] A[1:0]

1st address 00 01 10 11

2nd address 01 10 11 00

3rd address 10 11 00 01

4th address 11 00 01 10

The burst wrap around to initial state upon completion

Byte Write Function

Function SGW BWE BW1 BW2 BW3 BW4

Read H H X X X X

Read H L H H H H

Write all bytes L X X X X X

Write all bytes H L L L L L

Write byte 1 H L L H H H

Write byte 2 H L H L H H

A[1:0] A[1:0] A[1:0] A[1:0]

1st address 00 01 10 11

2nd address 01 00 11 10

3rd address 10 11 00 01

4th address 11 10 01 00

The burst wrap around to initial state upon completion

Write byte 3 H L H H L H

Write byte 4 H L H H H L

Note: H=logic high, L=logic low, NC= no connect

Rev. 9/09/97 3/15

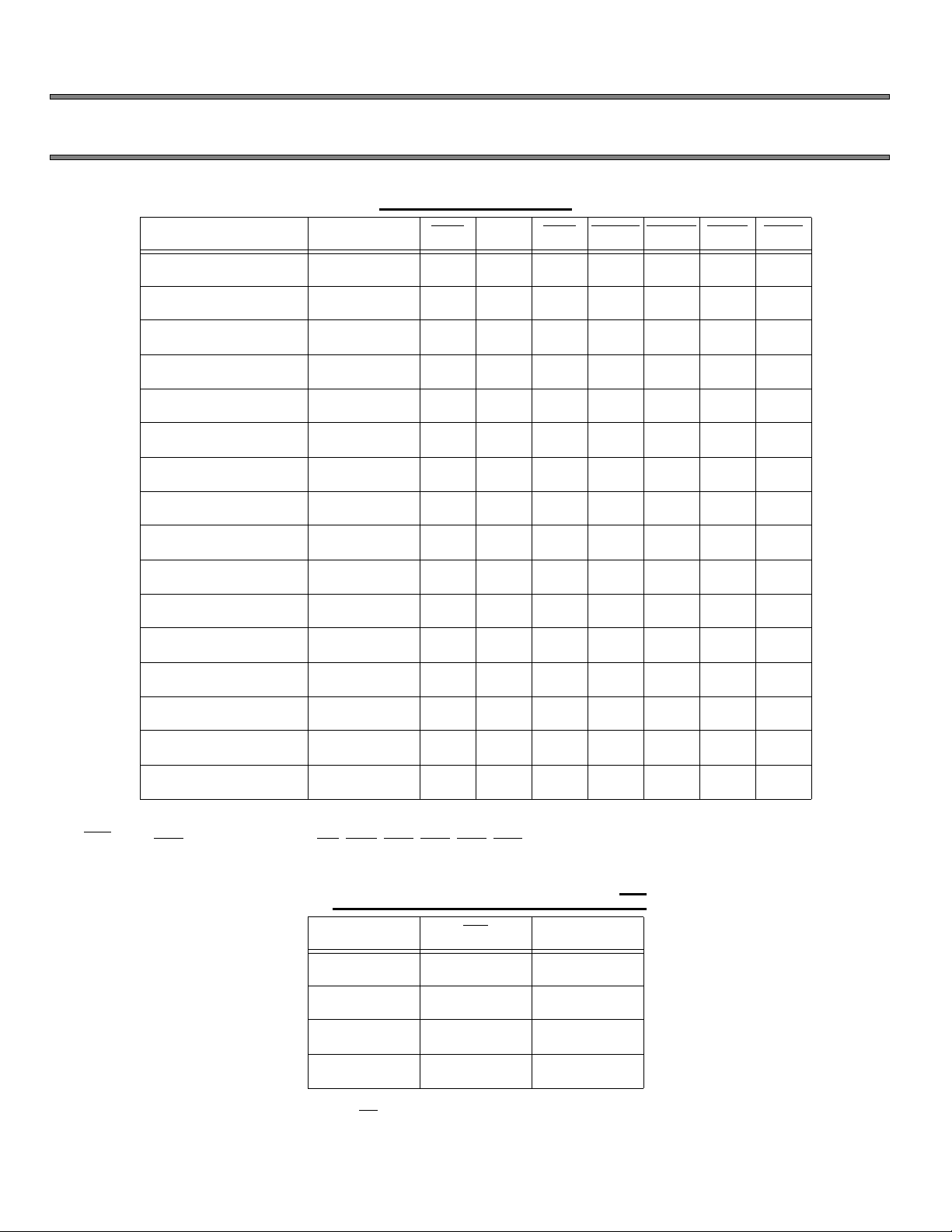

Page 4

G S I T E C H N O L O G Y

GS820V32Q/T

GS820V32Q/T

4/5/6, 2.5V I/O, 2.0mA

Cycle Address used CE1 CE2 CE3 ADSP ADSC ADV BWx

Deselect none H X X X L X X

Deselect none L L X X L X X

Deselect none L X H X L X X

Deselect none L L X L X X X

Deselect none L X H L X X X

Read, begin burst external L H L L X X X

Read, begin burst external L H L H L X H

Read, continue burst next X X X H H L H

Read, continue burst next H X X X H L H

64K x 32 Burst

Synchronous truth table

80-133MHz (P/L)

66MHz Flow-Thru

Read, suspend burst current X X X H H H H

Read, suspend burst current H X X X H H H

Write, begin burst external L H L H L X L

Write, continue burst next X X X H H L L

Write, continue burst next H X X X H L L

Write, suspend burst current X X X H H H L

Write, suspend burst current H X X X H H L

Note: 1. X=don’t care, H=logic high, L=logic low

2. BWx is the logic function of GW, BWE, BW1, BW2, BW3, BW4. See Byte Write Function table for detail.

3. All inputs in the table must meet setup and hold on rising edge of CLK.

DQ Bus Control and Asynchronous OE

Cycle OE DQ

Read L Q

Read H Hi-Z

Write X Hi-Z; D

Deselect X Hi-Z

Note: On the write cycle that follows read cycle, OE need to be held high prior to the start of write cycle to tri-state DQ buss and allow data

input to SRAM.

Rev. 9/09/97 4/15

Page 5

G S I T E C H N O L O G Y

GS820V32Q/T

GS820V32Q/T

4/5/6, 2.5V I/O, 2.0mA

Absolute Maximum Ratings (Voltage reference to VSS=0V)

Parameter Symbol Rating Unit

Supply Voltage VDD -0.5 to 4.6 V

Output Supply Voltage VDDQ -0.5 to VDD V

CLK Input Voltage VCLK -0.5 to 6 V

Input Voltage VIN -0.5 to VDD+0.5

Output Voltage VOUT -0.5 to VDD+0.5

Power Dissipation PD 1.5 W

Operating Temperature Topr 0 to 70

Storage Temperature Tstg -55 to 150

64K x 32 Burst

(≤ 4.6 V max. )

(≤ 4.6 V max. )

80-133MHz (P/L)

66MHz Flow-Thru

V

V

o

C

o

C

Note: Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional operation should be

restricted to Recommended Operating Conditions. Exposure to higher than recommended voltages for extended periods

of time could affect device reliability.

Recommended Operating Conditions (Voltage reference to VSS=0V)

(VDD=3.135V to 3.465V, Ta=0 70C)

Parameter Symbol Min. Typ. Max. Unit

Supply Voltage VDD 3.135 3.3 3.465 V

Output Supply Voltage VDDQ 2.375 3.3 3.465 V

Input High Voltage VIH 1.7 --- VDD+0.3 V

Input Low Voltage VIL -0.3 --- 0.8 V

Note: Input overshoot voltage should be less than VDD+2V and not exceed 5ns.

Input undershoot voltage should be higher than -2V and not exceed 5ns.

Capacitance ( Ta=25C, f=1MHz)

Parameter Symbol Test conditions Typ. Max. Unit

Input Capacitance CIN VIN=0V 4 5 pF

Output Capacitance COUT VOUT=0V 6 7 pF

Note: These parameters are sampled and are not 100% tested.

Rev. 9/09/97 5/15

Page 6

G S I T E C H N O L O G Y

GS820V32Q/T

GS820V32Q/T

4/5/6, 2.5V I/O, 2.0mA

DC Characteristics (Voltage reference to VSS=0V)

(VDD=3.135V to 3.465V, Ta=0 to 70C)

(TA= -40 to +85C for Industrial Temperature Offering)

Parameter Symbol Test Conditions

Input Leakage Current

(except ZZ, FT, LBO pins)

ZZ Input Current IIN

Mode Input Current

(FT & LBO pins)

Output Leakage Current I

Output High Voltage V

Output Low Voltage V

IIN

I

IL

ZZ

M

OL

OH

OL

64K x 32 Burst

V

= 0 to V

IN

V

DD ≥ VIN ≥ VIH

0V ≤ V

V

DD ≥ VIN ≥ VIH

0V ≤ V

Output Disable,

V

OUT

I

OH

I

OL

DD

≤ V

IN

IH

≤ V

IN

IH

= 0 to V

= - 8mA 2.4V 2.4 2.4V 2.4V

= + 8mA 0.4V 0.4V 0.4V 0.4V

DD

80-133MHz (P/L)

66MHz Flow-Thru

133MHz -4 -5 -6

Min Max Min Max Min Max Min Max

-1uA 1uA -1uA 1uA -1uA 1uA -1uA 1uA

-1uA

-1uA

-300uA

-1uA

-1uA 1uA -1uA 1uA -1uA 1uA -1uA 1uA

1uA

300uA

1uA

1uA

-1uA

-1uA

-300uA

-1uA

1uA

300uA

1uA

1uA

-1uA

-1uA

-300uA

-1uA

1uA

300uA

1uA

1uA

-1uA

-1uA

-300uA

-1uA

300uA

1uA

1uA

1uA

Parameter Symbol Test Conditions

Operating Supply Current

(VDD = man, E = VIH)

Standby Current I

Deselect Supply Current I

I

DD

SB

DD

Device Selected;

All other inputs ≥ VIH or ≤ V

Output open

ZZ ≥ V

Device Selected;

All other inputs ≥ VIH or ≤ V

AC Test Conditions

(VDD=3.135V to 3.465V, Ta=0 to 70C)

Parameter Conditions

Input high level VIH=2.4V

Input low level VIL=0.4V

Input rise time tr=1V/ns

Input fall time tf=1V/ns

Input reference level 1.4V

Output reference level 1.4V

Output load Fig. 1& 2

Note: 1. Include scope and jig capacitance.

2. Test conditions as specified with output loading as shown in

Fig. 1 unless otherwise noted

3. Output load 2 for tLZ, tHZ, t

OLZ

133MHz -4 -5 -6

0 to

70C

240mA 245mA 210mA 215mA 180mA 185mA 150mA 155mA

IL

- 0.2V 2mA 7mA 2mA 7mA 2mA 7mA 2mA 7mA

DD

80mA 85mA 70mA 75mA 60mA 65mA 50mA 55mA

IL

-40 to

+85C

0 to

70C

-40 to

+85C

0 to

70C

-40 to

+85C

0 to

70C

Output load 1

DQ

30pF

50Ω

VT=1.4V

Fig. 1

Output load 2

3.3V

295Ω

1

217Ω

and t

OHZ

DQ

5pF

.

Fig. 2

-40 to

+85C

1

Rev. 9/09/97 6/15

Page 7

G S I T E C H N O L O G Y

GS820V32Q/T

GS820V32Q/T

4/5/6, 2.5V I/O, 2.0mA

64K x 32 Burst

80-133MHz (P/L)

66MHz Flow-Thru

Rev. 9/09/97 7/15

Page 8

G S I T E C H N O L O G Y

GS820V32Q/T

GS820V32Q/T

4/5/6, 2.5V I/O, 2.0mA

AC Electrical Characteristics

(VDD=3.135V to 3.465V, Ta=0 to 70oC)

Parameter Symbol

Clock to output valid t

Pipeline

Flow-Thru

Clock to output invalid t

Clock to output in Low-Z t

Clock cycle time t

Clock to output valid t

Clock to output invalid t

Clock to output in Low-Z t

64K x 32 Burst

-4 -5 -6

Min Max Min Max Min Max

KQ

KQX

LZ

KC

KQ

KQX

LZ

--- 4.5 --- 5 --- 6 ns

2 --- 2 --- 2 --- ns

2

2 --- 2 --- 2 --- ns

8.5 --- 10 --- 12.5 --- ns

--- 12

3 --- ns

2

3 --- ns

NA

80-133MHz (P/L)

66MHz Flow-Thru

Unit

ns

1

Clock cycle time t

Clock high time t

Clock low time t

Clock to output in Hi-Z t

OE to output valid t

OE to output in Low-Z t

OE to output in Hi-Z t

Setup time t

Hold time t

ZZ setup time t

ZZ hold time t

ZZ recovery t

Note: 1. Flow-Thru mode is available in -4 bin only

2. These parameters are sampled and are not 100% tested

3. ZZ is a asynchronous signal. However, in order to be recognized on any given clock cycle, the signal must meet specified setup

and hold time.

KC

KH

KL

HZ

OE

OLZ

OHZ

S

H

ZZS

ZZH

ZZR

15 --- ns

2 --- 3 --- 4 --- ns

2 --- 3 --- 4 --- ns

2

--- 4 --- 5 --- 6 ns

--- 4 --- 5 --- 6 ns

2

0 --- 0 --- 0 --- ns

2

--- 4 --- 5 --- 6 ns

2.0 --- 2.5 --- 2.5 --- ns

0.5 --- 0.5 --- 0.5 --- ns

3

5 --- 5 --- 5 --- ns

3

1 --- 1 --- 1 --- ns

20 --- 20 --- 20 --- ns

Rev. 9/09/97 8/15

Page 9

G S I T E C H N O L O G Y

GS820V32Q/T

GS820V32Q/T

4/5/6, 2.5V I/O, 2.0mA

CLK

ADSP

ADSC

ADV

A0-A15

GW

BWE

Single Read

t

t

H

S

t

t

S

H

RD1

64K x 32 Burst

Read Cycle Timing (Pipeline)

Burst Read

t

KH

t

t

S

H

t

t

S

H

RD2

t

S

t

S

t

KC

KL

t

ADSP is blocked by CE1 inactive

Suspend Burst

ADSC initiated read

RD3

t

H

t

H

80-133MHz (P/L)

66MHz Flow-Thru

BW1 -

BW4

CE1

CE2

CE3

OE

DQ1DQ32

Hi-Z

t

t

H

S

t

t

H

S

t

t

S

H

t

OLZ

t

LZ

CE2 and CE3 only sampled with ADSP or ADSC

t

OE

t

OHZ

Q1a

t

KQ

CE1 masks ADSP

t

KQX

Q2a

Q2b

Q2c

Deselected with CE2

t

KQX

Q2d

Q3a

t

HZ

Rev. 9/09/97 9/15

Page 10

G S I T E C H N O L O G Y

GS820V32Q/T

GS820V32Q/T

4/5/6, 2.5V I/O, 2.0mA

CLK

ADSP

ADSC

ADV

64K x 32 Burst

Write Cycle Timing

(This waveform can apply to both Pipeline and Flow-Thru modes)

Single Write

t

StH

t

t

S

H

t

KH

t

t

H

S

t

t

S

H

ADV must be inactive for ADSP Write

Burst Write

t

KL

ADSP is blocked by CE1 inactive

t

KC

Write

ADSC initiated write

80-133MHz (P/L)

66MHz Flow-Thru

Deselected

A0-A15

GW

BWE

BW1 BW4

CE1

CE2

CE3

OE

DQ1DQ32

Hi-Z

WR1

t

S

tSt

t

S

WR2 WR3

tSt

H

t

t

H

S

t

t

S

H

WR1 WR2 WR3

WR1

t

H

H

t

H

CE2 and CE3 only sampled with ADSP or ADSC

t

t

S

H

D1a

WR2 WR3

CE1 masks ADSP

Write specified byte for 2a and all bytes for 2b, 2c& 2d

D2a D2b

D2c D2d D3a

Deselected with CE2

Rev. 9/09/97 10/15

Page 11

G S I T E C H N O L O G Y

GS820V32Q/T

GS820V32Q/T

4/5/6, 2.5V I/O, 2.0mA

CLK

ADSP

ADSC

ADV

64K x 32 Burst

Read/Write Cycle Timing (Pipeline)

KL

tSt

Single Write

t

KC

ADSC initiated read

H

ADSP is blocked by CE1 inactive

Single Read Burst Read

t

t

H

S

t

t

S

H

t

t

S

H

t

t

KH

80-133MHz (P/L)

66MHz Flow-Thru

A0-A15

GW

BWE

BW1 BW4

CE1

CE2

CE3

OE

DQ1DQ32

Hi-Z

t

t

t

RD1

S

S

S

WR1

t

t

S

H

t

S

t

H

t

H

t

H

CE2 and CE3 only sampled with ADSP and ADSC

OE

t

Q1a

t

t

KQ

OHZ

t

H

t

StH

WR1

t

S

D1a

RD2

CE1 masks ADSP

Deselected with CE3

t

H

Q2a

Q2b Q2c

Q2d

Rev. 9/09/97 11/15

Page 12

G S I T E C H N O L O G Y

GS820V32Q/T

GS820V32Q/T

4/5/6, 2.5V I/O, 2.0mA

CLK

ADSP

ADSC

ADV

A0-A15

GW

BWE

Single Read

t

t

H

S

t

t

S

H

RD1

64K x 32 Burst

Read Cycle Timing (Flow-Thru)

Burst Read

t

KH

t

t

S

H

t

t

S

H

RD2 RD3

t

S

t

S

t

KC

KL

t

ADSP is blocked by CE1 inactive

Suspend Burst

ADSC initiated read

Suspend Burst

t

H

t

H

80-133MHz (P/L)

66MHz Flow-Thru

BW1 -

BW4

CE1

CE2

CE3

OE

DQ1DQ32

Hi-Z

t

t

H

S

t

t

H

S

t

t

S

H

t

OE

t

OLZ

t

LZ

t

KQ

CE2 and CE3 only sampled with ADSP or ADSC

Q1a

t

OHZ

Q2a

t

KQX

CE1 masks ADSP

Q2cQ2b

Q2d

Deselected with CE2

t

KQX

Q3a

t

HZ

Rev. 9/09/97 12/15

Page 13

G S I T E C H N O L O G Y

GS820V32Q/T

GS820V32Q/T

4/5/6, 2.5V I/O, 2.0mA

CLK

ADSP

ADSC

ADV

64K x 32 Burst

Read/Write Cycle Timing (Flow-Thru)

KL

tSt

Single Write

t

KC

ADSC initiated read

H

ADSP is blocked by CE1 inactive

Single Read Burst Read

t

t

H

S

t

t

S

H

t

t

S

H

t

t

KH

80-133MHz (P/L)

66MHz Flow-Thru

A0-A15

GW

BWE

BW1 BW4

CE1

CE2

CE3

OE

DQ1DQ32

Hi-Z

t

t

t

RD1

S

S

S

WR1

t

t

S

H

t

S

t

H

t

H

t

H

t

OE

t

KQ

Q1a D1a

CE2 and CE3 only sampled with ADSP and ADSC

t

OHZ

t

H

t

StH

WR1

t

S

RD2

CE1 masks ADSP

Deselected with CE3

t

H

Q2a

Q2b Q2c

Q2d

Q2a

Rev. 9/09/97 13/15

Burst wrap around to it’s initial state

Page 14

G S I T E C H N O L O G Y

GS820V32Q/T

GS820V32Q/T

4/5/6, 2.5V I/O, 2.0mA

CLK

ADSP

ADSC

ZZ

80-133MHz (P/L)

64K x 32 Burst

ZZ Timing

~

~

~

~

~

~

~

Snooze

~

~

~

~

~

~

~

t

ZZH

t

ZZR

t

t

t

H

S

KC

t

t

KH

KL

t

ZZS

66MHz Flow-Thru

Rev. 9/09/97 14/15

Page 15

G S I T E C H N O L O G Y

GS820V32Q/T

GS820V32Q/T

4/5/6, 2.5V I/O, 2.0mA

Package Dimension

L1

80-133MHz (P/L)

64K x 32 Burst

θ

L

e

b

c

Pin 1

66MHz Flow-Thru

D1

D

A1

A2

E1

Y

E

QFP (Q) TQFP (T)

Symbol Description Min. Nom. Max Min. Nom. Max

A1 Stand Off 0.25 0.35 0.45 0.05 0.10 0.15

A2 Body Thickness 2.55 2.72 2.90 1.35 1.40 1.45

b Lead Width 0.20 0.30 0.40 0.20 0.30 0.40

c Lead Thickness 0.10 0.15 0.20 0.09 0.20

D Terminal Dimension 22.95 23.2 23.45 21.9 22.0 22.1

D1 Package Body 19.9 20.0 20.1 19.9 20.0 20.1

E Terminal Dimension 17.0 17.2 17.4 15.9 16.0 16.1

E1 Package Body 13.9 14.0 14.1 13.9 14.0 14.1

e Lead Pitch 0.65 0.65

L Foot Length 0.60 0.80 1.00 0.45 0.60 0.75

L1 Lead Length 1.60 1.00

Y Coplanarity 0.10 0.10

θ Lead Angle 0

Note:

1. All dimensions are in millimeters (mm).

2. Package width and length do not include mold protrusion.

o

o

7

o

0

o

7

Rev. 9/09/97 15/15

Loading...

Loading...