Datasheet GM71VS17403CT-7, GM71VS17403CT-6, GM71VS17403CT-5, GM71VS17403CLT-7, GM71VS17403CLT-6 Datasheet (HYNIX)

...Page 1

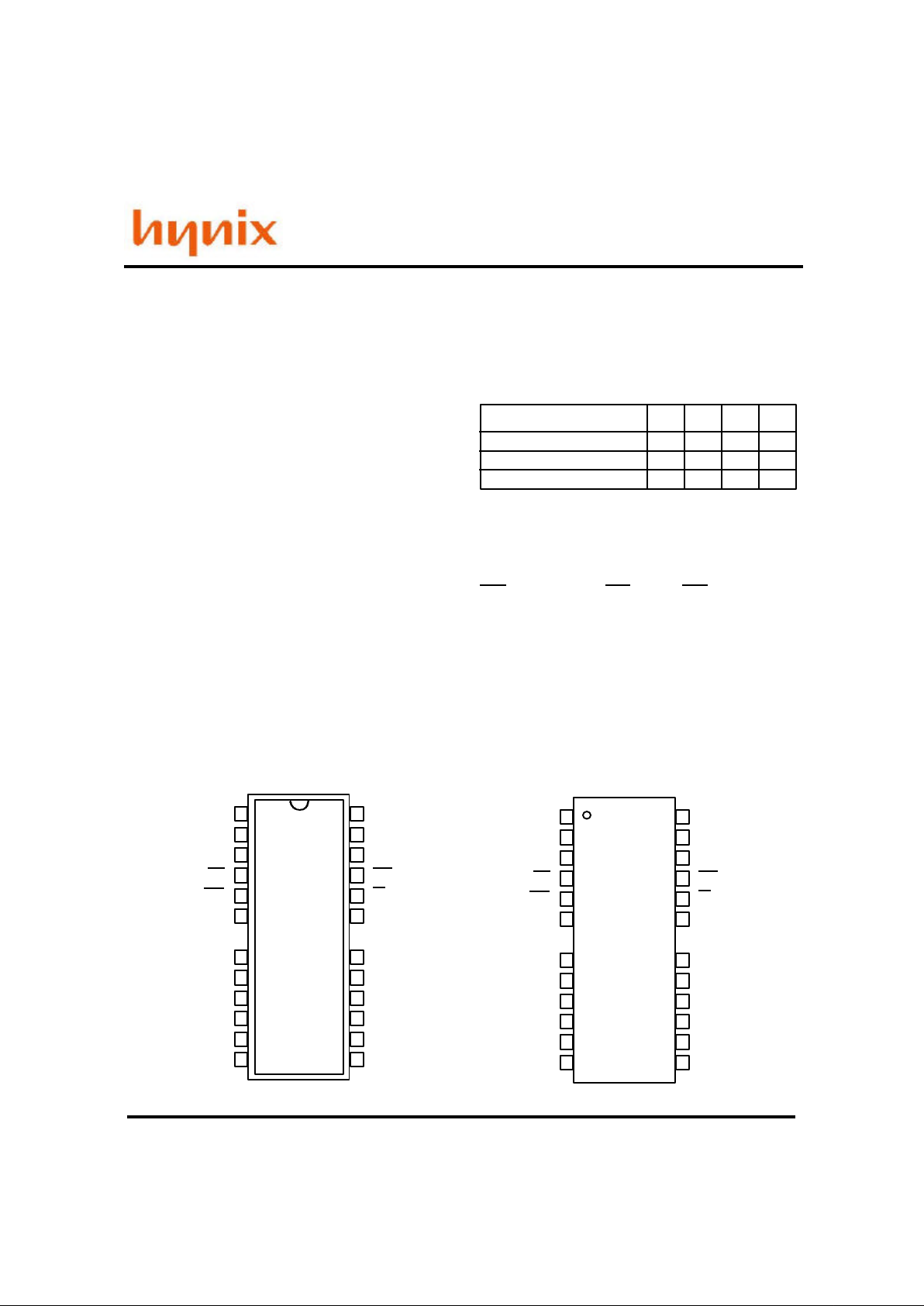

4,194,304 WORDS x 4 BIT

CMOS DYNAMIC RAM

Description

The GM71V(S)17403C/CL is the new

generation dynamic RAM organized 4,194,304

words x 4 bit. GM71V(S)17403C/CL has

realized higher density, higher performance and

various functions by utilizing advanced CMOS

process technology. The GM71V(S)17403C/CL

offers Extended Data Out (EDO) Page Mode as

a high speed access mode. Multiplexed address

inputs permit the GM71V(S)17403C/CL to be

packaged in a standard 300 mil 24(26) pin SOJ,

and a standard 300 mil 24(26) pin plastic TSOP

II. The package size provides high system bit

densities and is compatible with widely

available automated testing and insertion

equipment. System oriented features include

single power supply 3.3V +/- 0.3V tolerance,

direct interfacing capability with high

performance logic families such as Schottky

TTL.

Features

* 4,194,304 Words x 4 Bit Organization

* Extended Data Out Mode Capability

* Single Power Supply (3.3V +/- 0.3V)

* Fast Access Time & Cycle Time

* Low Power

Active : 432/369/360mW (MAX)

Standby : 7.2mW (CMOS level : MAX)

: 0.36mW (L-version : MAX)

* RAS Only Refresh, CAS before RAS Refresh,

Hidden Refresh Capability

*All inputs and outputs TTL Compatible

* 2048 Refresh Cycles/32ms

* 2048 Refresh Cycles/128ms (L-version)

* Self Refresh Operation (L-version)

* Battery Backup Operation (L-version)

* Test Function : 16bit parallel test mode

GM71V(S)17403C/CL-5

GM71V(S)17403C/CL-6

GM71V(S)17403C/CL-7

tRAC tCAC tRC tHPC

50601315 84

1042025

70 18 124 30

(Top View)

Pin Configuration

24(26) SOJ

VCC

I/O1

I/O2

WE

RAS

NC

A10

A0

A1

A2

A3

VCC

VSS

I/O4

I/O3

CAS

OE

A9

A8

A7

A6

A5

A4

VSS

1

2

3

4

5

6

8

9

10

11

12

13 14

15

16

17

18

19

21

22

23

24

25

26

24(26) TSOP II

VCC

I/O1

I/O2

WE

RAS

A11

A10

A0

A1

A2

A3

VCC

VSS

I/O4

I/O3

CAS

OE

A9

A8

A7

A6

A5

A4

VSS

1

2

3

4

5

6

8

9

10

11

12

13 14

15

16

17

18

19

21

22

23

24

25

26

(Unit: ns)

GM71V17403C

GM71VS17403CL

Rev 0.1 / Apr’ 01

Page 2

GM71V17403C

GM71VS17403CL

Rev 0.1 / Apr’ 01

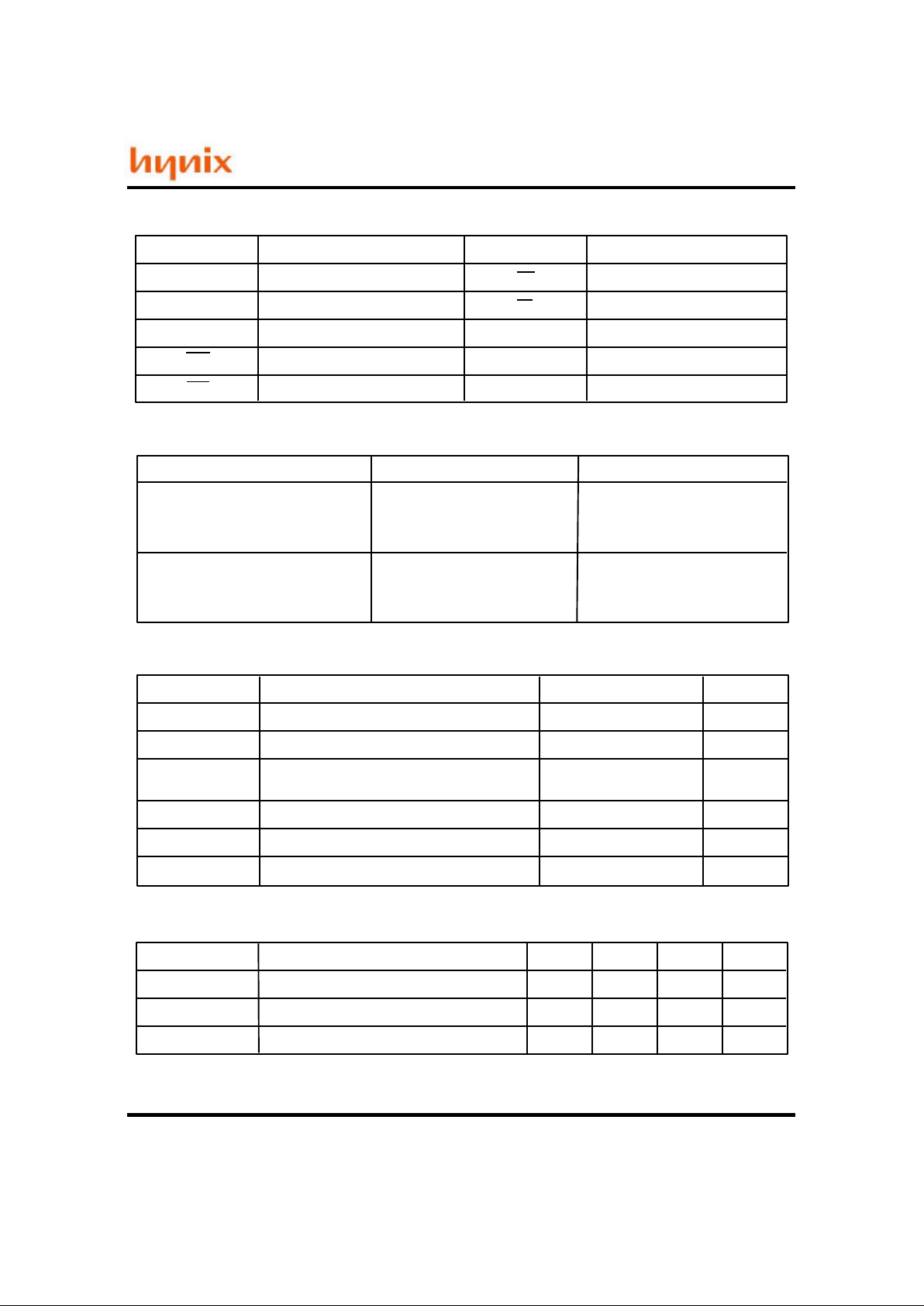

Pin Description

Pin Function Pin Function

A0-A10

A0-A10

I/O1-I/O4

VCC

VSS

Address Inputs

Refresh Address Inputs

Data Input/Data Output

Row Address Strobe

Column Address Strobe

Read/Write Enable

Output Enable

Power (+3.3V)

Ground

Ordering Information

Type No. Access Time Package

GM71V(S)17403CJ/CLJ-5

GM71V(S)17403CJ/CLJ-6

GM71V(S)17403CJ/CLJ-7

50ns

60ns

70ns

300 Mil

24(26) Pin

Plastic SOJ

GM71V(S)17403CT/CLT-5

GM71V(S)17403CT/CLT-6

GM71V(S)17403CT/CLT-7

300 Mil

24(26) Pin

Plastic TSOP II

Absolute Maximum Ratings

Symbol Parameter Rating Unit

TA

TSTG

VIN/OUT

VCC

IOUT

0 ~ 70

-55 ~ 125

-0.5 ~ Vcc+0.5

(<=4.6V(MAX))

-0.5 ~ 4.6

50

Ambient Temperature under Bias

Storage Temperature

Voltage on any Pin Relative to VSS

Supply Voltage Relative to VSS

Short Circuit Output Current

V

V

mA

PD 1.0Power Dissipation W

Note: All voltage referred to Vss.

RAS

CAS

Recommended DC Operating Conditions (TA = 0 ~ 70C)

Symbol Parameter Unit

VCC

VIH

VIL

Supply Voltage

Input High Voltage

Input Low Voltage

V

V

V

Max

3.6

VCC + 0.3

0.8

Typ

3.3

-

-

Min

3.0

2.0

-0.3

C

C

NC No Connection

OE

WE

50ns

60ns

70ns

Page 3

GM71V17403C

GM71VS17403CL

Rev 0.1 / Apr’ 01

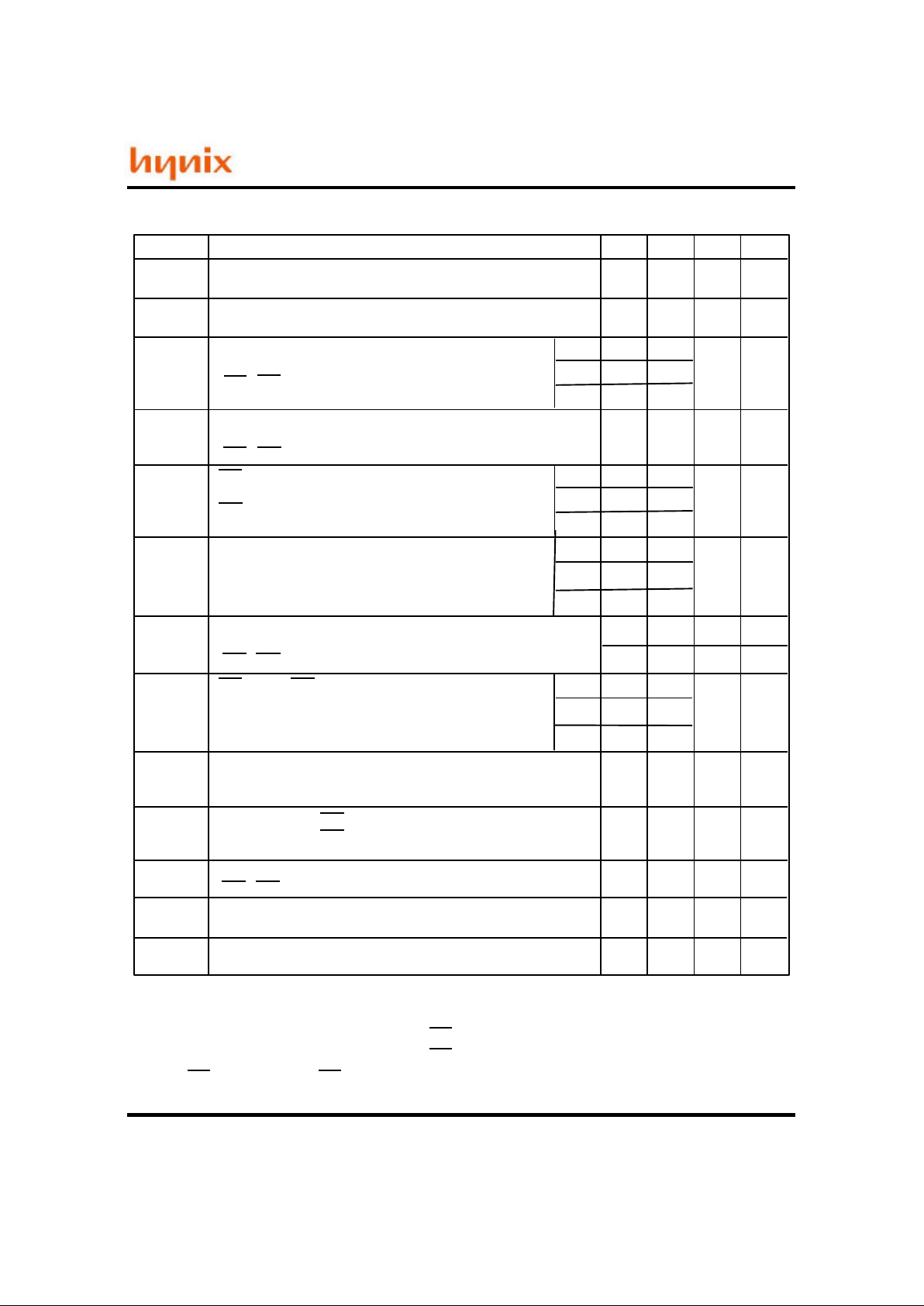

DC Electrical Characteristics (VCC = 3.3V+/-0.3V, VSS = 0V, TA = 0 ~ 70C)

Symbol Parameter Note

VOH

VOL

Output Level

Output "H" Level Voltage (IOUT = -2mA)

UnitMax

VCC

0.4

Min

2.4

0

Output Level

Output "L" Level Voltage (IOUT = 2mA)

ICC1

Operating Current

Average Power Supply Operating Current

(RAS, CAS Cycling : tRC = tRC min)

ICC2

Standby Current (TTL)

Power Supply Standby Current

(RAS, CAS = VIH, DOUT = High-Z)

ICC3

RAS Only Refresh Current

Average Power Supply Current

RAS Only Refresh Mode

(tRC = tRC min)

ICC4

ICC5

Standby Current (CMOS)

Power Supply Standby Current

(RAS, CAS >= VCC - 0.2V, DOUT = High-Z)

1

-

ICC6

CAS-before-RAS Refresh Current

(tRC = tRC min)

ICC7

100

-

ICC8

IL(I)

10-10

IL(O)

10-10

Input Leakage Current

Any Input (0V<=VIN<= 4.6V)

Output Leakage Current

(DOUT is Disabled, 0V<=VOUT<= 4.6V)

ICC9

Self-Refresh Mode Current

(RAS, CAS<=0.2V, DOUT=High-Z, CMOS interface)

200-

EDO Page Mode Current

Average Power Supply Current

EDO Page Mode

(tHPC = tHPC min)

Note: 1. ICC depends on output load condition when the device is selected.

ICC(max) is specified at the output open condition.

2. Address can be changed once or less while RAS = VIL.

3. Address can be changed once or less while CAS = VIH.

4. CAS = L (<=0.2) while RAS = L (<=0.2).

5. L - Version.

100-50ns

60ns

70ns

90

80

-

2-

-

100-50ns

60ns

70ns

90

80

-

-

-

90-50ns

60ns

70ns

80

75

-

V

V

mA

uA

uA

uA

-

Standby Current RAS = VIH

CAS = VIL

DOUT = Enable

5 1mA

Battery Backup Operating Current(Standby with CBR Refresh)

(CBR refresh, tRC = 31.3us, tRAS <= 0.3us,

DOUT = High-Z, CMOS interface)

300- uA

4,5

uA

5

5

mA 1, 2

mA

mA 2

mA 1, 3

mA

100-50ns

60ns

70ns

-

-

90

80

Page 4

GM71V17403C

GM71VS17403CL

Rev 0.1 / Apr’ 01

Capacitance (VCC = 3.3V +/- 0.3V, TA = 25C)

AC Characteristics (VCC = 3.3V +/- 0.3V, VSS = 0V, TA = 0 ~ 70C, Notes 1, 2, 18)

Read, Write, Read-Modify-Write and Refresh Cycles (Common Parameters)

Symbol Parameter Note

CI1

CI2

CI/O

Input Capacitance (Address)

Input Capacitance (Clocks)

Output Capacitance (Data-In/Out)

1

1

1, 2

Unit

pF

pF

pF

Max

5

7

7

Min

-

-

-

Test Conditions

Input rise and fall times : 2ns

Input levels : VIL = 0V, VIH = 3V

Input timing reference levels : 0.8V, 2.0V

Output timing reference levels : 0.8V, 2.0V

Output load : 1 TTL gate + CL (100pF)

(Including scope and jig)

Note: 1. Capacitance measured with Boonton Meter or effective capacitance measuring method.

2. CAS = VIH to disable DOUT.

Symbol Parameter

Note

Max

Unit

Min MaxMin MaxMin

tRC Random Read or Write Cycle Time 84 - 104 - 124 -

tRP RAS Precharge Time 30 - 40 - 50 -

tRAS RAS Pulse Width 50 10,000

60

10,000

70

10,000

tCAS CAS Pulse Width 8 10,000 10,000 10,00010 13

tASR Row Address Set up Time 0 - - -0 0

tRAH Row Address Hold Time 8 - - -10 10

tASC

Column Address Set-up Time 0 - - -0 0

tCAH

Column Address Hold Time 8 - - -10 13

tRCD

RAS to CAS Delay Time 12 37 45 5214 14 3

tRAD RAS to Column Address Delay Time 10 25 30 3512 12 4

tRSH

RAS Hold Time 10 - - -13 13

tCSH

CAS Hold Time 35 - - -40 45

tCRP CAS to RAS Precharge Time 5 - - -5 5

tT Transition Time (Rise and Fall) 2 50 50 502 2 7

tDZO

OE Delay Time from DIN 0 - - -0 0

tDZC

CAS Delay Time from DIN 0 - - -0 0

GM71V(S)17403

C/CL-5

OE to DIN Delay Time 13 - - -15 18 5

6

6

tCP

CAS Precharge Time 8 - 10 - 13 -

tODD

GM71V(S)17403

C/CL-6

GM71V(S)17403

C/CL-7

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Page 5

GM71V17403C

GM71VS17403CL

Rev 0.1 / Apr’ 01

Read Cycle

Symbol Parameter

Unit

Max

Note

Min MaxMin

tRAC

Access Time from RAS - 60 - 70 ns

tCAC Access Time from CAS - 15 - 18 ns

tAA

Access Time from Address - 30 - 35 ns

tRCS

Read Command Setup Time 0 - 0 - ns

tRCH

Read Command Hold Time to CAS 0 - - ns0

tRRH

Read Command Hold Time to RAS 5 - - ns5

tRAL

Column Address to RAS Lead Time 30 - - ns35

12

12

tCLZ

CAS to Output in low-Z 0 - - ns0

8.9.19

9,10,

17,19

9,11,

17,19

tCAL

Column Address to CAS Lead Time 18 - - ns23

tOFF

Output Buffer Turn-off Time - 15 15 ns- 13

tOAC

Access Time from OE - 15 - 18 ns 9

tOH

Output Data Hold Time 3 - - ns3

tOHO

Output Data Hold Time from OE 3 - - ns3

tOEZ

Output Buffer Turn-off Time to OE - 15 15 ns- 13

tCDD

CAS to DIN Delay Time 15 - - ns18 5

tWDD

WE to DIN Delay Time 15 - - ns18

tOHR

Output Data Hold Time from RAS 3 - - ns3

tOFR

Output Buffer Turn-off Time to RAS - 15 15 ns-

tWEZ

Output Buffer Turn-off to WE - 15 15 ns-

tRDD

RAS to DIN Delay Time 15 - - ns18

tRCHR

Read Command Hold Time from RAS 60 - - ns70

GM71V(S)17403

C/CL-6

GM71V(S)17403

C/CL-7

MaxMin

- 50

- 13

- 25

0 0 -

5 -

25 -

0 -

15 -

- 13

- 13

3 3 -

- 13

13 -

13 -

3 -

- 13

- 13

13 -

50 -

GM71V(S)17403

C/CL-5

Page 6

GM71V17403C

GM71VS17403CL

Rev 0.1 / Apr’ 01

Read- Modify-Write Cycle

Refresh Cycle

Write Cycle

Symbol Parameter

Max

Unit

Min MaxMin

0 - 0 -

10

-

13

-

10

-

10

-

10

-

13

-

10

- -

13

0 - -0

10

- -

13

Write Command Setup Time

Write Command Hold Time

Write Command Pulse Width

Write Command to RAS Lead Time

Write Command to CAS Lead Time

Data-in Setup Time

Data-in Hold Time

GM71V(S)17403

C/CL-6

GM71V(S)17403

C/CL-7

ns

Min

0 -

8

-

8

-

-

-

0 -

-

Max

GM71V(S)17403

C/CL-5

8

8

8

ns

ns

ns

ns

ns

ns

Symbol Parameter

Max

Unit

Min MaxMin

136 - 161 -

79 - 92 34 - 40 49 - 57 15 - 18 -

Read-Modify-Write Cycle Time

RAS to WE Delay Time

CAS to WE Delay Time

Column Address to WE Delay Time

OE Hold Time from WE

GM71V(S)17403

C/CL-6

GM71V(S)17403

C/CL-7

ns

ns

ns

ns

ns

Min

111 -

67 30 42 13 -

Max

GM71V(S)17403

C/CL-5

Symbol Parameter

Note

15

15

14

Note

14

14

14

Note

Max

Unit

Min MaxMin

5 - 5 - ns

10 - 10 - ns

5 - 5 - ns

GM71V(S)17403

C/CL-6

GM71V(S)17403

C/CL-7

0 - 0 - ns

tWCS

tWCH

tWP

tRWL

tCWL

tDS

tDH

tRWC

tRWD

tCWD

tAWD

tOEH

tCSR

tCHR

tRPC

tWRP

tWRH

10 - 10 - ns

CAS Setup Time

(CAS-before-RAS Refresh Cycle)

CAS Hold Time

(CAS-before-RAS Refresh Cycle)

RAS Precharge to CAS Hold Time

WE Setup Time

(CAS-before-RAS Refresh Cycle)

WE Hold Time

(CAS-before-RAS Refresh Cycle)

Min

5 -

8 -

5 -

GM71V(S)17403

C/CL-5

0 -

10 -

Max

Page 7

GM71V17403C

GM71VS17403CL

Rev 0.1 / Apr’ 01

Refresh

Symbol Parameter

Unit

Max

Note

Min MaxMin

- 32 -

Test Mode Cycle

Symbol Parameter

Unit

Max

Note

Min MaxMin

0 - 0 - ns

10 - 10 - ns

Test Mode WE Setup Time

Test Mode WE Hold Time

EDO Page Mode Read-Modify-Write Cycle

EDO Page Mode Cycle

Refresh Period

Refresh Period (L - version)

- 128 -

GM71V(S)17403

C/CL-6

GM71V(S)17403

C/CL-7

GM71V(S)17403

C/CL-6

GM71V(S)17403

C/CL-7

ms

ms

32

128

2048

cycles

2048

cycles

Symbol Parameter

Note

Max

Unit

Min MaxMin

25 - 30 -

35 - 40 -

9,17,19

- -

16

100,000 100,000

- 35 40

GM71V(S)17403

C/CL-6

GM71V(S)17403

C/CL-7

20

3 3-

-

-

-

9

10 13

5 5

35

40

ns

ns

ns

ns

ns

ns

ns

ns

Min

20 -

30 -

-

-

GM71V(S)17403

C/CL-5

3 -

-

-

-

5

30

Max

100,000

8

Access Time from CAS Precharge

RAS Hold Time from CAS Precharge

EDO Page Mode RAS Pulse Width

EDO Page Mode Cycle Time

Output data Hold Time from CAS low

CAS Hold Time referred OE

CAS to OE Setup Time

Read command Hold Time

from CAS Precharge

Symbol Parameter

Note

Max

Unit

Min MaxMin

68 - 79 - ns

tREF

tWTS

tWTH

tREF

tHPC

tRASP

tACP

tRHCP

tDOH

tCOL

tCOP

tRCHP

tHPRWC

tCPW

54 - 62 -

ns

14

EDO Page Mode Read-Modify-Write

Cycle Time

WE Delay Time from CAS Precharge

GM71V(S)17403

C/CL-6

GM71V(S)17403

C/CL-7

MaxMin

57 -

45 -

GM71V(S)17403

C/CL-5

MaxMin

0 -

10 -

GM71V(S)17403

C/CL-5

MaxMin

- 32

- 128

GM71V(S)17403

C/CL-5

30

∗18

Page 8

GM71V17403C

GM71VS17403CL

Rev 0.1 / Apr’ 01

AC Measurements assume tT = 2ns.

An initial pause of 200us is required after power up followed by a minimum of eight

initialization cycles (any combination of cycles containing RAS-only refresh or CAS-beforeRAS refresh). If the internal refresh counter is used, a minimum of eight CAS-before-RAS

refresh cycles are required.

Operation with the tRCD(max) limit insures that tRAC(max) can be met, tRCD(max) is specified as a

reference point only; if tRCD is greater than the specified tRCD(max) limit, then access time is

controlled exclusively by tCAC.

Operation with the tRAD(max) limit insures that tRAC(max) can be met, tRAD(max) is specified as a

reference point only; if tRAD is greater than the specified tRAD(max) limit, then access time is

controlled exclusively by tAA.

Either tODD or tCDD must be satisfied.

Either tDZO or tDZC must be satisfied.

VIH(min) and VIL(max) are reference levels for measuring timing of input signals. Also,

transition times are measured between VIH(min) and VIL(max).

Assume that tRCD<=tRCD(max) and tRAD<=tRAD(max). If tRCD or tRAD is greater than the maximum

recommended value shown in this table, tRAC exceeds the value shown.

Measured with a load circuit equivalent to 1 TTL loads and 100pF.

Assume that tRCD >=tRCD(max) and tRCD + tCAC(max) >= tRAD + tAA(max).

Assume that tRAD >=tRAD(max) and tRCD + tCAC(max) <= tRAD + tAA(max).

Either tRCH or tRRH must be satisfied for a read cycles.

tOFF(max) and tOEZ(max) define the time at which the outputs achieve the open circuit condition

and are not referenced to output voltage levels.

Notes:

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

Self Refresh Mode ( L-version )

Symbol Parameter

Note

Max

Unit

Min MaxMin

GM71VS17403

CL-6

GM71VS17403

CL-7

tRASS

RAS Pulse Width ( Self-refresh ) 100 - 100 - µs

tRPS

RAS Precharge Time ( Self-refresh ) 110 - 130 - ns

tCHS

CAS Hold Time ( Self-refresh ) -50 - -50 - ns

Min

100 -

90 -

-50 -

Max

GM71VS17403

CL-5

Page 9

GM71V17403C

GM71VS17403CL

Rev 0.1 / Apr’ 01

tWCS, tRWD, tCWD, tAWD and tCPW are not restrictive operating parameters. They are included in the

data sheet as electrical characteristics only; if tWCS>=tWCS(min), the cycles is an early write cycle

and the data out pin will remain open circuit (high impedance) throughout the entire cycle; if

tRWD>=tRWD(min), the tCWD>=tCWD(min), and tAWD>=tAWD(min), or tCWD>=tCWD(min), tAWD>=

tAWD(min) and tCPW>=tCPW(min), the cycle is a read-modify-write and the data output will contain

data read from the selected cell; if neither of the above sets of conditions is satisfied, the

condition of the data out (at access time) is indeterminate.

These parameters are referenced to CAS leading edge in early write cycles and to WE leading

edge in delayed write or read-modify-write cycles.

tRASP defines RAS pulse width in EDO page mode cycles.

Access time is determined by the longest among tAA or tCAC or tACP.

The 16M DRAM offers a 16-bit time saving parallel test mode. Address CA0 and CA1 for the

4M x 4 are don't care during test mode. Test mode is set by performing a WE-and-CAS-beforeRAS (WCBR) cycle. In 16-bit parallel test mode, data is written into 4 bits in parallel at each I/O

(I/O1 to I/O4) and read out from each I/O. If 4 bits of each I/O are equal (all 1s or 0s), data

output pin is a high state during test mode read cycle, then the device has passed. If they are not

equal, data output pin is a low state, then the device has failed. Refresh during test mode

operation can be performed by normal read cycles or by WCBR refresh cycles. To get out of test

mode and enter a normal operation mode, perform either a regular CAS-before-RAS refresh

cycle or RAS-only refresh cycle.

In a test mode read cycle, the value of tRAC, tAA, tCAC and tACP is delayed by 2ns to 5ns for the

specified value. These parameters should be specified in test mode cycles by adding the above

value to the specified value in this data sheet.

tHPC(min) can be achieved during a series of EDO page mode write cycles or EDO page mode

read cycles. If both write and read operation are mixed in a EDO page mode RAS cycle(EDO

page mode mix cycle (1),(2)), minimum value of CAS cycle (tCAS + tCP + 2tT) becomes greater

than the specified tHPC(min) value. The value of CAS cycle time of mixed EDO page mode is

shown in EDO page mode mix cycle (1) and (2).

18.

19.

20.

14.

15.

16.

17.

Page 10

GM71V17403C

GM71VS17403CL

Rev 0.1 / Apr’ 01

Package Dimension

Unit: Inches (mm)

24(26) TSOP (TYPE II)

24(26) SOJ

0.669(17.00) MAX

0.661(16.80) MIN

0.295(7.49) MIN

0.329(8.38) MIN

0.340(8.64) MAX

0.147(3.75) MAX

0.128(3.25) MIN

0.020(0.50) MAX

0.015(0.38) MIN

TYP

0.050(1.27)

0.305(7.75) MAX

0.260(6.60) MIN

0.275(6.99) MAX

0.025(0.64)

MIN

0.032(0.81) MAX

0.026(0.66) MIN

0.085(2.16)

MIN

0.020(0.50) MAX

0.012(0.30) MIN

TYP

0.050(1.27)

0.007(0.18) MAX

0.003(0.08) MIN

0.047(1.20)

MAX

0.041(1.05) MAX

0.037(0.95) MIN

0.296(7.52) MIN

0.303(7.72) MAX

0.678(17.24) MAX

0.670(17.04) MIN

0.355(9.02) MIN

0.371(9.42) MAX

0.024(0.60) MAX

0.016(0.40) MIN

0.008(0.21) MAX

0.004(0.12) MIN

0 ~ 5

o

Loading...

Loading...