Datasheet GLT4160L04SE-70TC, GLT4160L04SE-70J3, GLT4160L04SE-60TC, GLT4160L04SE-60J3, GLT4160L04SE-50TC Datasheet (G-LINK)

...Page 1

G-LINK

RAS

CAS

RAS

RAS

CAS

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Features : Description :

GLT4160L04

May 2001 (Rev.3.1)

∗ 4,194,304 words by 4 bits organization.

∗ Fast access time and cycle time

∗ Low power dissipation.

∗ Read-Modify-Write,

-Before-

Refresh, Hidden Refresh.

-Only Refresh,

∗ 2,048 refresh cycles per 32ms.

∗ Available in 300 mil 26(24) SOJ and TSOPII.

∗ 3.3V±0.3V Vcc Power Supply voltage.

∗ All inputs and Outputs are LVTTL compatible.

∗ Extended Data-Out (EDO) Page access

cycle.

∗ Self-refresh Capability. (S-Version).

The GLT4160L04 is a high-performance

CMOS dynamic random access memory

containing 16,777,216 bits organized in a x4

configuration. The GLT4160L04 offers page

cycle access with Extended Data Output.

The GLT4160L04 has 11 row- and 11

column-addresses, and accepts 2048-cycle

refresh in 32 ms.

The GLT4160L04 provides EDO PAGE

MODE operation which allows for fast data

access within a row-address defined

boundary, up to 2048 x 4 bits with cycle

times as short as 18ns.

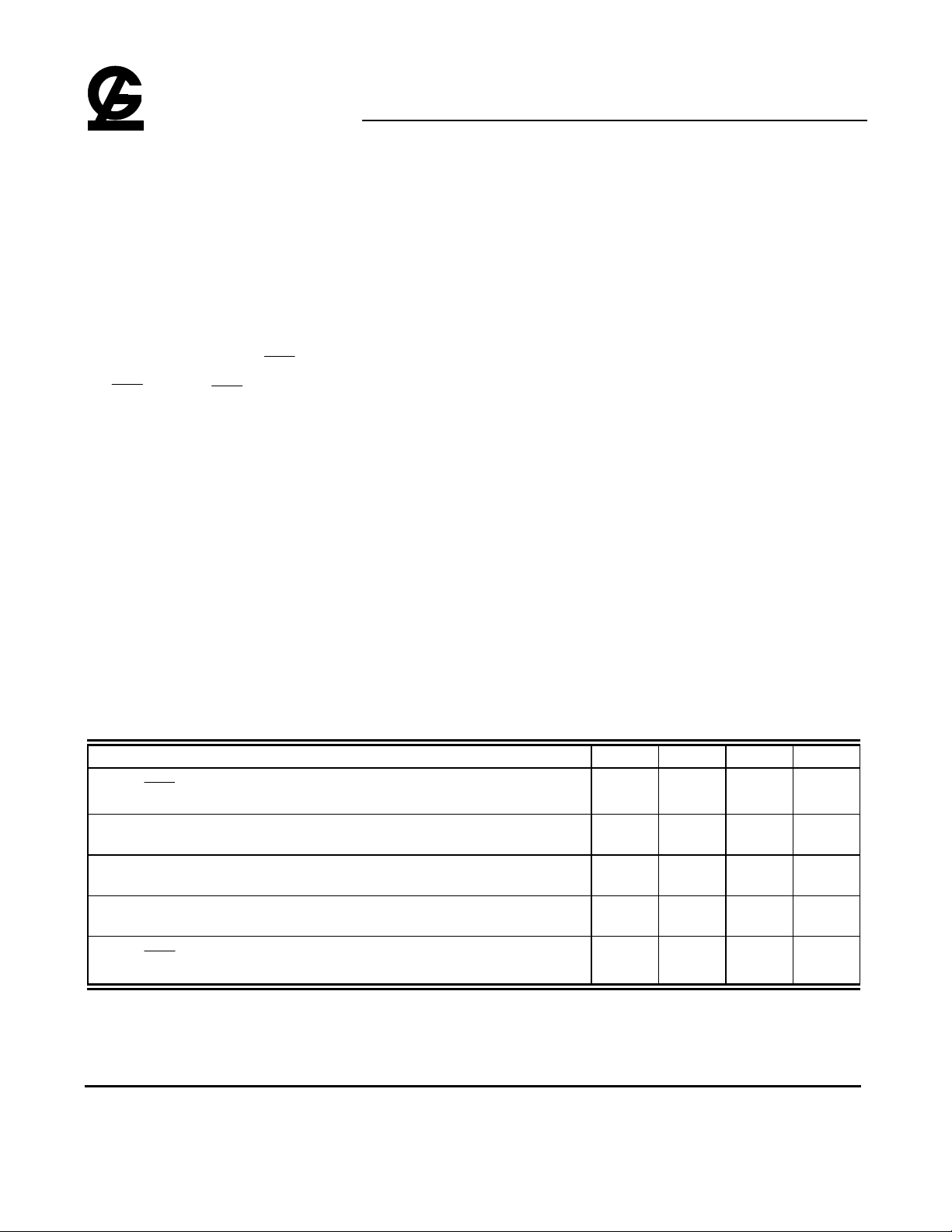

HIGH PERFORMANCE 40 50 60 70

Max.

Access Time, (t

RAC

)

40 ns 50 ns 60 ns 70 ns

Max. Column Address Access Time, (tAA) 20 ns 25 ns 30 ns 35 ns

Min. Extended Data Out Page Mode Cycle Time, (tPC) 18 ns 20 ns 25 ns 30 ns

Min. Read/Write Cycle Time, (tRC) 70 ns 84 ns 104 ns 124 ns

Max.

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

Access Time (t

CAC

)

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

12 ns 13 ns 15 ns 20 ns

- 1 -

Page 2

G-LINK

RAS

CAS

WE

OE

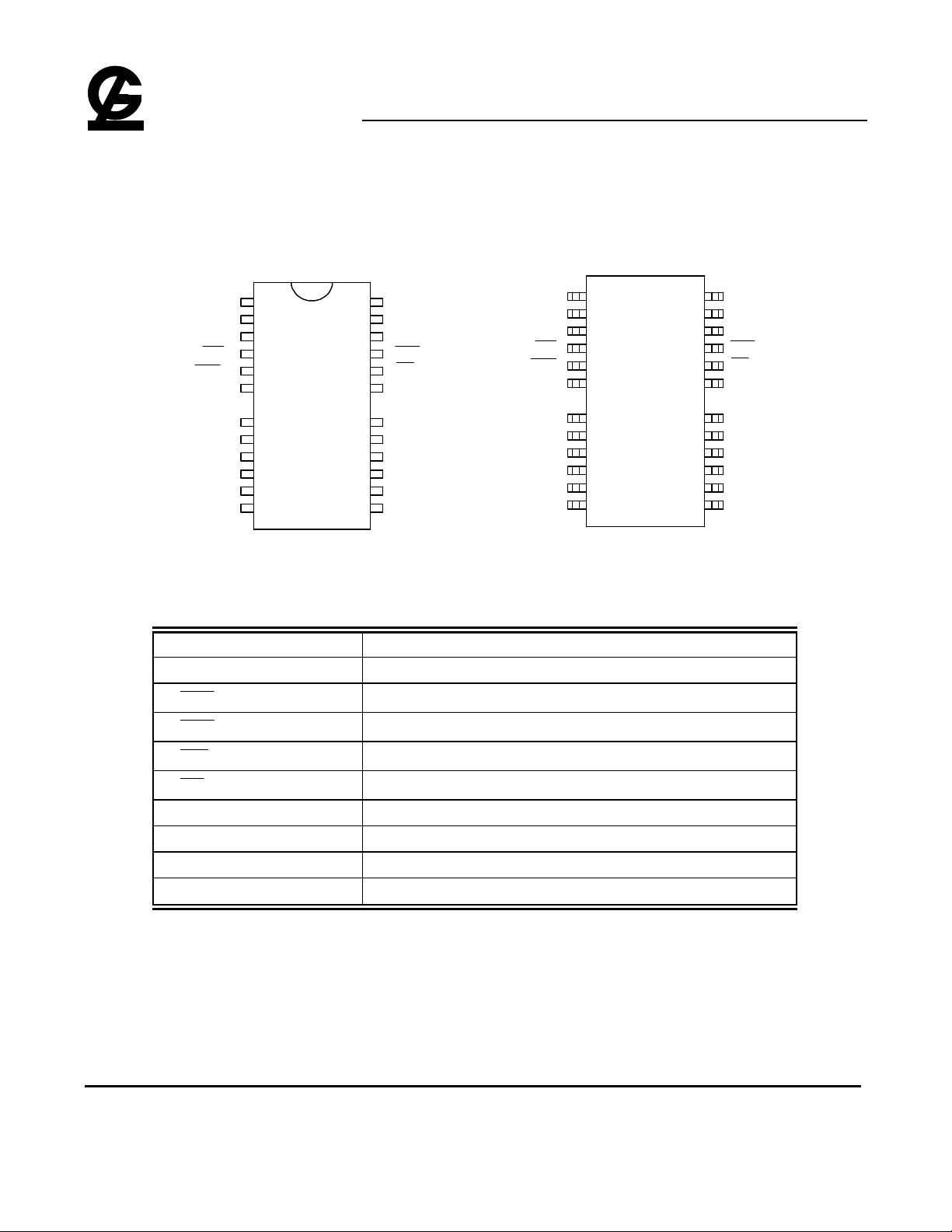

Pin Configuration :

GLT4160L04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

May 2001 (Rev.3.1)

Vcc

DQ0

DQ1

WE

RAS

NC

10

A

0

A

A1

A2

3

A

VCC

Pin Descriptions:

A0 - A

10

GLT4160L04

300mil 26(24) SOJ

1

2

3

4

5

6

8

9

10

11

12

13

26

25

24

23

22

21

19

18

17

16

15

14

VSS

DQ3

DQ2

CAS

OE

A9

8

A

A7

A6

A5

4

A

VSS

Vcc

DQ0

DQ1

WE

RAS

NC

A10

A0

A1

A2

A3

VCC

GLT4160L04

300mil 26(24) TSOPII

1

2

3

4

5

6

8

9

10

11

12

13

Name Function

Address Inputs

Row Address Strobe

26

25

24

23

22

21

19

18

17

16

15

14

VSS

DQ3

DQ2

CAS

OE

A9

A8

A7

A6

A5

A4

VSS

DQ0 - DQ

V

CC

V

SS

NC No Connection

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

Column Address Strobe

Write Enable

Output Enable

3

Data Inputs / Outputs

+3.3V Power Supply

Ground

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 2 -

Page 3

G-LINK

CAS

RAS

RAS

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Absolute Maximum Ratings* Capacitance*

TA=25°C, VCC=3.3V±0.3V, VSS=0V

Operating Temperature, TA (ambient)

.............................................….0°C to

+70°C

For Extended Temperature……………..-20°C to 85°C

Storage Temperature(plastic)............-55°C to +150°C

Voltage Relative to VSS........................-0.5V to + 4.6V

Short Circuit Output Current...............................20mA

Power Dissipation...............................................1.0W

*Note: Operation above Absolute Maximum Ratings can

aversely affect device reliability.

Electrical Specifications

l All voltages are referenced to GND.

l After power up, wait more than 200µs and then, execute eight

refresh cycles as dummy cycles to initialize internal circuit.

Symbol

C

C

C

*Note: Capacitance is sampled and not 100% tested

Address Input

IN1

RAS, CAS, WE, OE

IN2

Data Input/Output

OUT

Parameter

-before-

GLT4160L04

May 2001 (Rev.3.1)

Max.

or

Unit

5

7

7

pF

pF

pF

-only

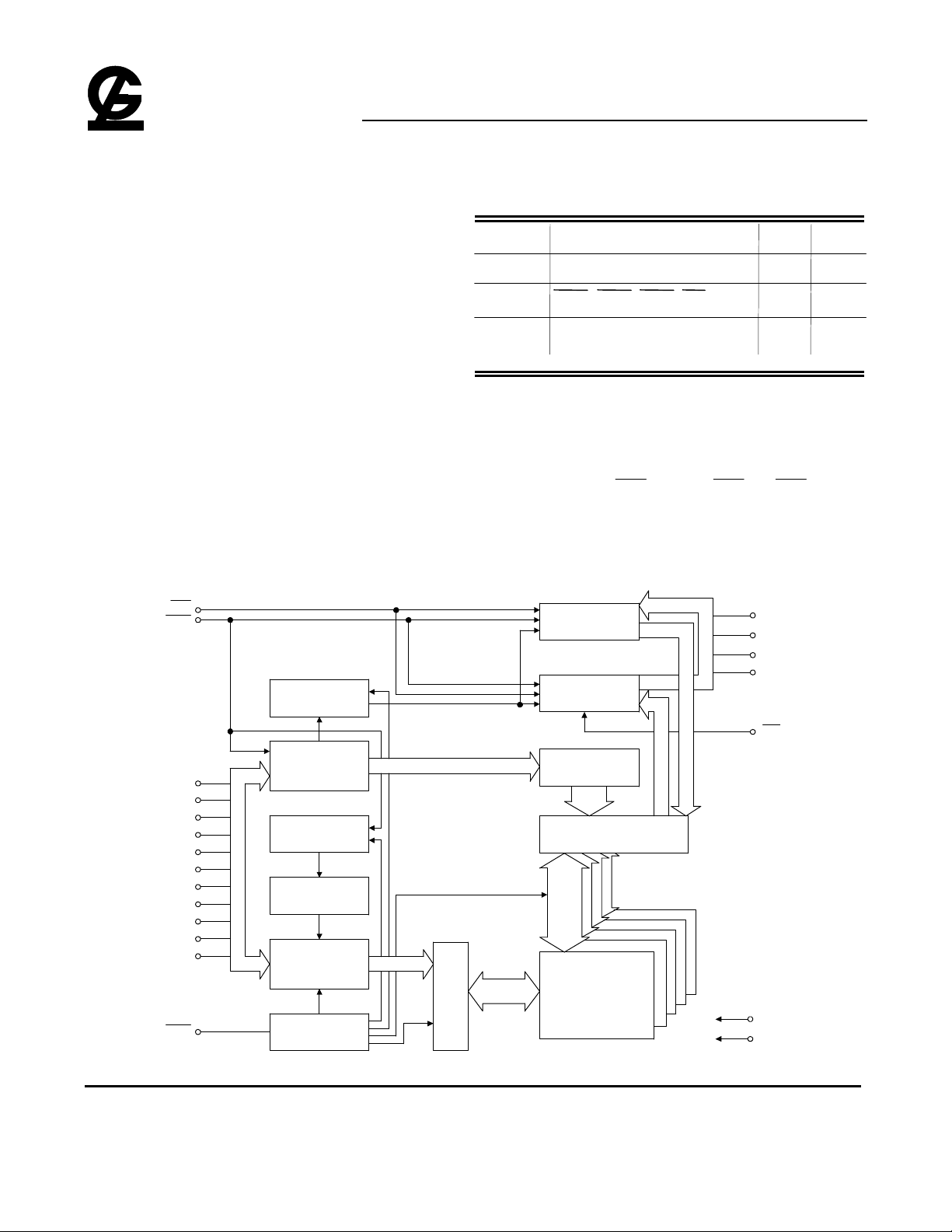

Block Diagram :

WE

CAS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

RAS

11

11

NO.2 CLOCK

GENERATOR

COLUMN-

ADDRESS

BUFFER(11)

REFRESH

CONTROLLER

REFRESH

COUNTER

ROW

ADDRESS

BUFFERS(11)

NO.1 CLOCK

GENERATOR

11

11

ROW DECODER

2048

DATA-IN

BUFFER

DATA-OUT

BUFFER

COLUMN

DECODER

2048

SENSE AMPLIFIERS

I/O GATING

2048

2048 x 1024 x 4

MEMORY

ARRAY

4

4

4

4

DQ0

DQ1

DQ2

DQ3

OE

VDD

VSS

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 3 -

Page 4

G-LINK

RAS

CAS

WE

OE

RAS

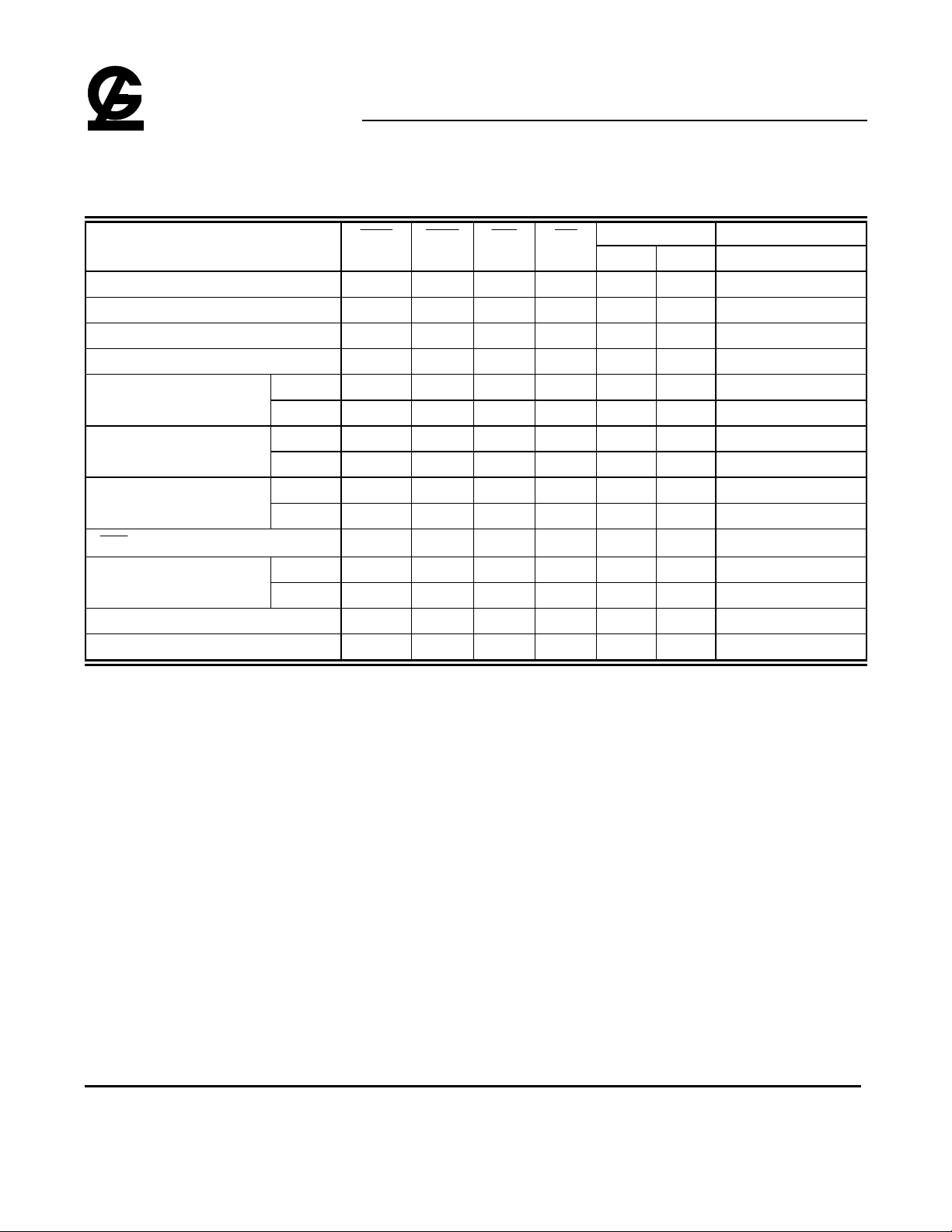

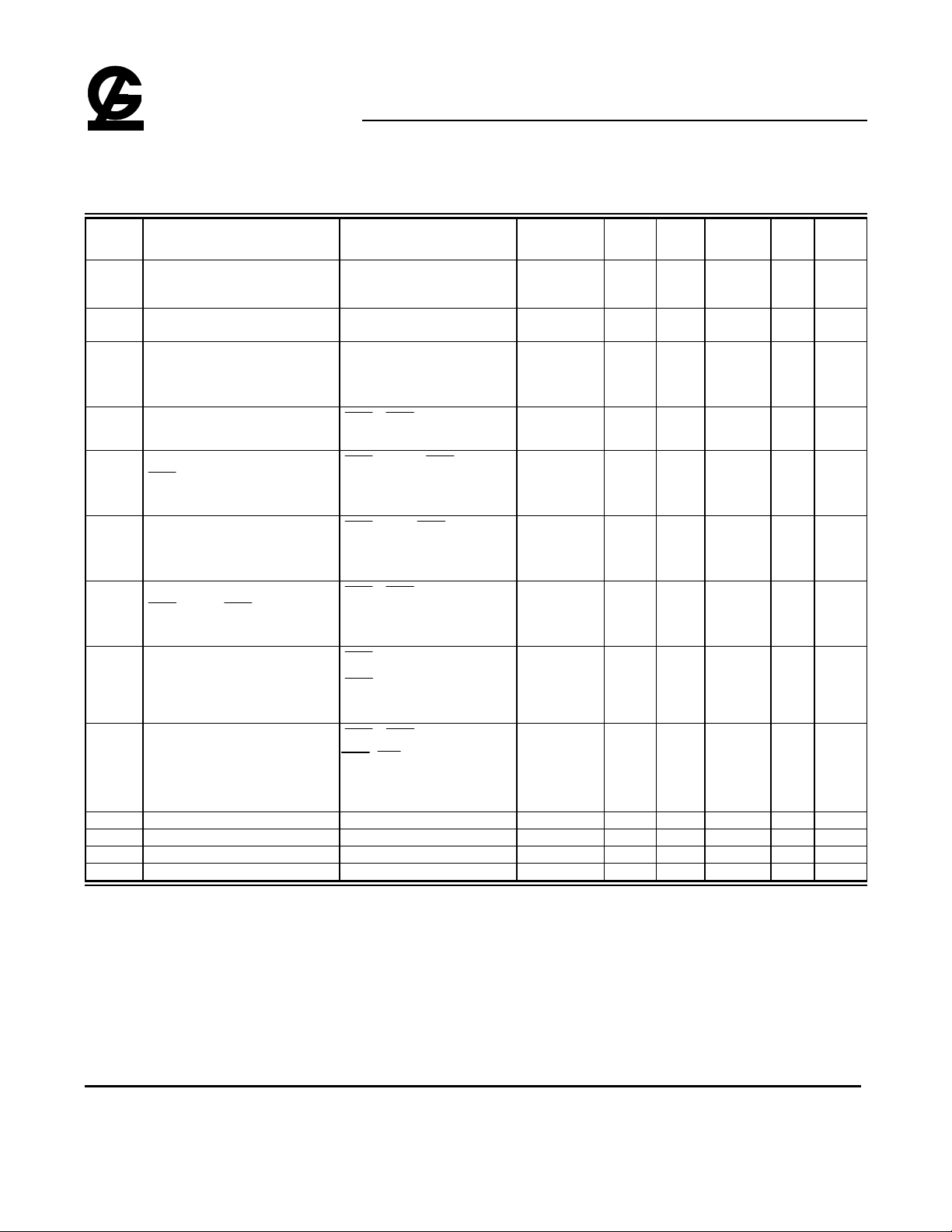

Truth Table:

GLT4160L04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

May 2001 (Rev.3.1)

Function

Standby H

H→X

X X X X High-Z

ADDRESS DATA-IN/OUT

t

R

t

C

DQ1-DQ4

READ L L H L ROW COL Data-Out

EARLY WRITE L L L X ROW COL Data-In

READ WRITE L L

EDO-PAGE-MODE 1st Cycle L

READ 2nd cycle L

EDO-PAGE-MODE 1st Cycle L

EARLY-WRITE 2nd cycle L

EDO-PAGE-MODE 1st Cycle L

READ-WRITE 2nd cycle L

-ONLY REFRESH

HIDDEN REFRESH READ

WRITE

CBR REFRESH

SELF REFRESH

L→H→L

L→H→L

H→L

H→L

L H X X ROW n/a High-Z

H→L

H→L

H→L

H→L

H→L H→L L→H

H→L H→L L→H

H→L L→H

H L ROW COL Data-Out

H L n/a COL Data-Out

L X ROW COL Data-In

L X n/a COL Data-In

L H L ROW COL Data-Out

L L X ROW COL Data-In

L H X X X High-Z

L H X X X High-Z

ROW COL Data-Out,Data-In

ROW COL Data-Out,Data-In

n/a COL Data-Out,Data-In

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 4 -

Page 5

G-LINK

Time

RAS, CAS

RAS

RAS

CAS

RAS

CAS

CAS

RAS

RAS, CAS

RAS

CAS

RAS=CAS

WE = OE = A~A=V

-0.2V or

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

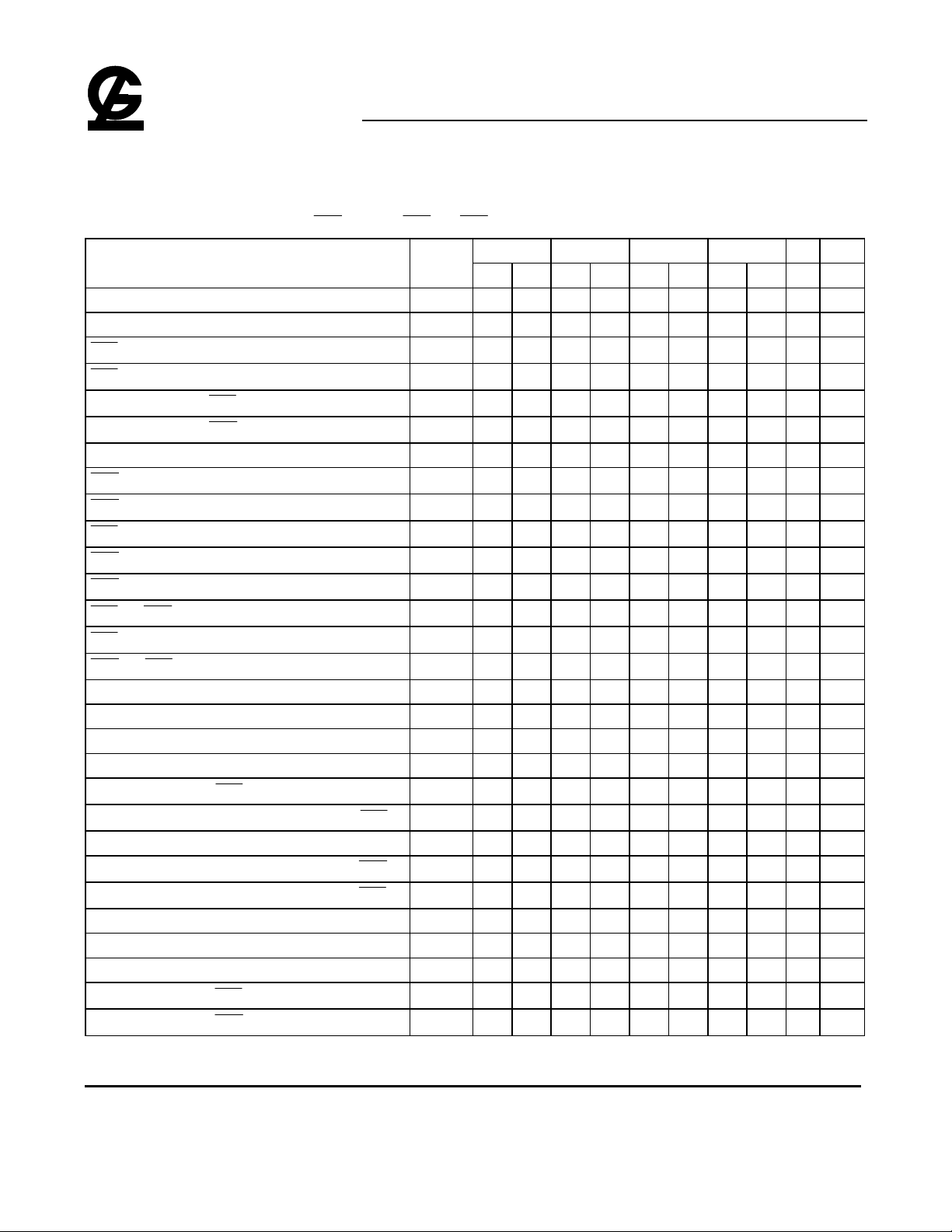

DC and Operating Characteristics (1-2)

TA = 0°C to 70°C, -20°C to 85°C VCC=3.3V±0.3V, VSS=0V, unless otherwise specified.

GLT4160L04

May 2001 (Rev.3.1)

Sym. Parameter Test Conditions Access

I

Input Leakage Current

LI

(any input pin)

0V ≤ V

≤ VCC+0.3V

IN

(All other pins not under

Min. Typ Max. Unit Notes

-5 +5

µA

test=0V)

I

I

I

I

I

I

I

I

Output Leakage Current

LO

(for High-Z State)

Operating Current,

CC1

Random READ/WRITE

Standby Current (TTL)

CC2

Refresh Current,

CC3

-Only

Operating Current,

CC4

EDO Page Mode

Refresh Current,

CC5

Before

Standby Current, (CMOS)

CC6

Self refresh Current

CC7

0V ≤ V

out

≤ V

CC

Output is disabled (Hiz)

tRC = tRC (min.) t

at V

other inputs ≥V

cycling,

IH

SS

at V

IH

tRC = tRC (min.)

at VIL,

address

cycling:tPC=tPC(min.)

address cycling:

tRC=tRC (min.)

≥VCC-0.2V,

≥VCC-0.2V,

All other inputs V

SS

=0.2V,

0.2V

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

RAC

RAC

RAC

RAC

RAC

RAC

RAC

RAC

RAC

RAC

RAC

RAC

RAC

RAC

RAC

RAC

= 40ns

= 50ns

= 60ns

= 70ns

= 40ns

= 50ns

= 60ns

= 70ns

= 40ns

= 50ns

= 60ns

= 70ns

= 40ns

= 50ns

= 60ns

= 70ns

-5 +5

130

120

80

70

130

120

80

70

130

120

80

70

130

120

80

70

300

300

µA

mA

1 mA

mA

mA

mA 1

µA

µA

1,2

2

1,2

1,5

DQ0~DQ3=VCC-0.2V,0.2V or

Open

V

V

V

V

Input Low Voltage -0.3 +0.8 V 3

IL

Input High Voltage 2.0 VCC+0.3 V 4

IH

Output Low Voltage IOL = 2mA 0.4 V

OL

Output High Voltage IOH = -2mA 2.4 V

OH

Notes:

1. ICC is dependent on output loading when the device output is selected. Specified ICC(max.) is measured with the output open.

2. ICC is dependent upon the number of address transitions specified ICC(max.) is measured with a maximum of one transition per address cycle

in random Read/Write and EDO Fast Page Mode.

3. Specified VIL(min.) is steady state operation. During transitions VIL(min.) may undershoot to –1V for a period not to exceed 15ns. All AC

parameters are measured with VIL(min.)≥VSS and VIH(max.)≤VCC.

4. Specified VIH(max.) is steady state operation . During transitions VIH(max.) may overshoot to VCC+1V for a period not to exceed 15ns. All AC

parameters are measured with VIL(min.) ≥ VSS and VIH(max.) ≤ VCC .

5. S-Version.

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 5 -

Page 6

G-LINK

CAS

RAS

RAS

RAS

RAS

RAS

CAS

CAS

CAS

RAS

CAS

CAS

RAS

CAS

RAS

CAS

RAS

RAS

RAS

CAS

RAS

RAS

CAS

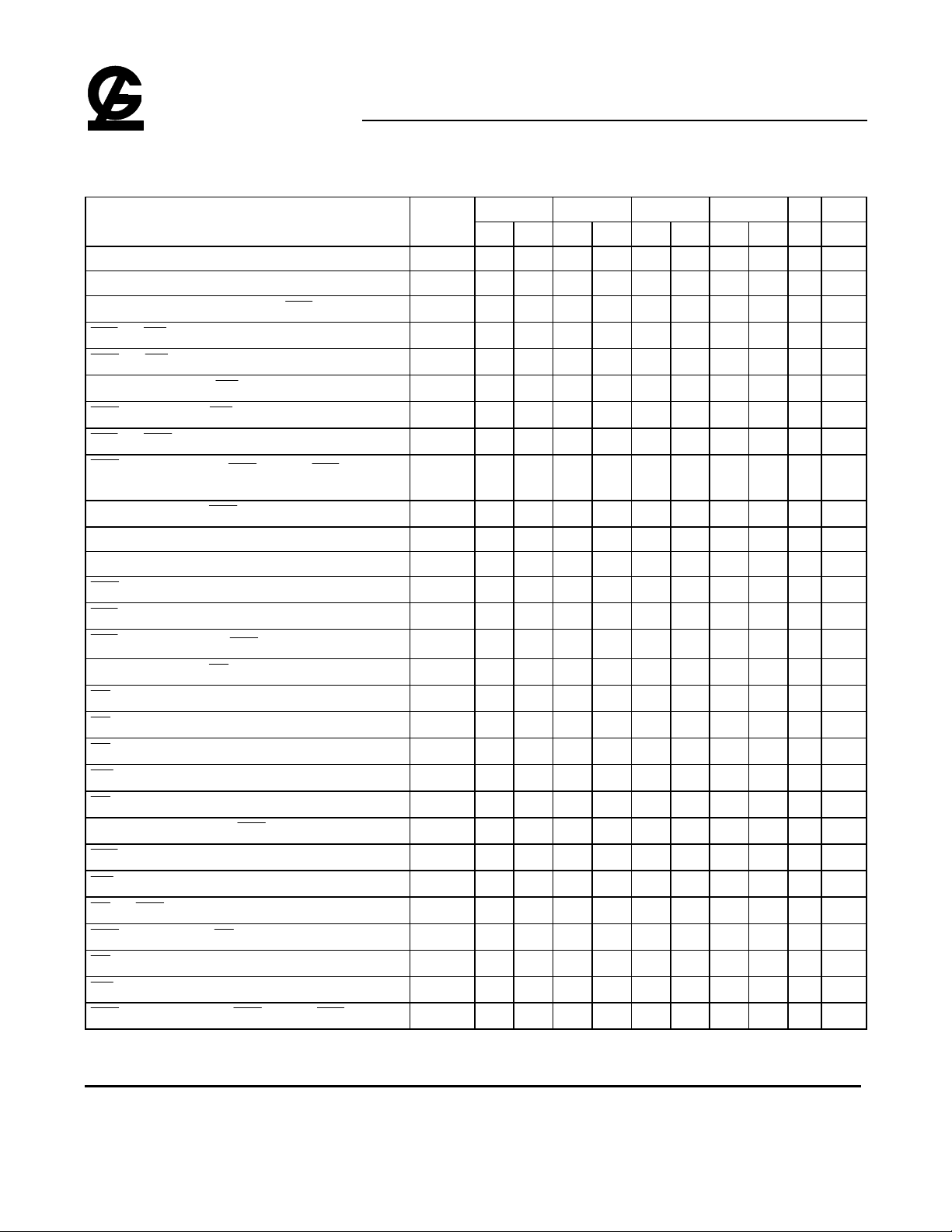

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

AC Characteristics

TA =0°C to 70°C , -20°C to 85°C VCC = 3.3 V ± 0.3V, VIH/VIL = 3/0 V, VOH/VOL = 2/0.8V

An initial pause of 200 µs and 8

Parameter

Read or Write Cycle Time

Read Modify Write Cycle Time

Precharge Time

Pulse Width

Access Time from

Access Time from

Access Time from Column Address

to Output Low-Z

to Output High-Z

Hold Time

Hold Time

Pulse Width

to

to Column Address Delay Time

to

Row Address Set-Up Time

Row Address Hold Time

Column Address Set-Up Time

Column Address Hold Time

Column Address to

Column Address Hold Time Referenced to

Read Command Set-Up Time

Read Command Hold Time Referenced to

Read Command Hold Time Referenced to

Write Command Set-Up Time

Write Command Hold Time

Write Command Pulse Width

Write Command to

Write Command to

Delay Time

Precharge Time

Lead Time

Lead Time

Lead Time

-before-

or

-only refresh cycles are required after power-up.

40 50 60 70

Symbol Min. Max. Min. Max. Min. Max. Min. Max. Unit Notes

t

t

RWC

t

t

RAS

t

RAC

t

CAC

t

t

t

CEZ

t

RSH

t

CSH

t

CAS

t

RCD

t

RAD

t

CRP

t

ASR

t

RAH

t

ASC

t

CAH

t

RAL

t

t

RCS

t

RCH

t

RRH

t

WCS

t

WCH

t

t

RWL

t

CWL

RC

RP

AA

CLZ

AR

WP

70 84 104 124 ns

91 116 140 170 ns

25 30 40 50 ns

40 10K 50 10k 60 10k 70 10k ns

40 50 60 70 ns 1,2,3

12 13 15 20 ns 1,5,10

20 25 30 35 ns 1,5,6

0 3 3 3 ns

3 8 3 13 3 15 3 20 ns

12 13 15 20 ns

34 38 45 50 ns

7 10k 8 10k 10 10k 15 10k ns

18 28 20 37 20 45 20 50 ns

13 20 15 25 15 30 15 35 ns 7

5 5 5 5 ns

0 0 0 0 ns

8 10 10 10 ns

0 0 0 0 ns

6 8 10 15 ns

20 25 30 35 ns

34 40 45 50 ns

0 0 0 0 ns

0 0 0 0 ns 4

0 0 0 0 ns 4

0 0 0 0 ns 8,9

6 10 10 15 ns

6 10 10 15 ns

12 13 15 30 ns

8 8 10 15 ns

GLT4160L04

May 2001 (Rev.3.1)

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 6 -

Page 7

G-LINK

RAS

RAS

CAS

CAS

WE

RAS

CAS

CAS

CAS

RAS

CAS

CAS

RAS

RAS

CAS

OE

OE

OE

OE

WE

OE

CAS

RAS

WE

OE

CAS

CAS

OE

OE

WE

CAS

CAS

RAS

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

AC Characteristics

Parameter

Data Set-Up Time

Data Hold Time

Data Hold Time Referenced to

to WE Delay Time

to WE Delay Time

Column Address to WE Delay Time

Precharge to

to

Precharge Time

precharge time

test cycle)

Access Time from

EDO Page Mode Cycle Time

EDO Page Mode Read-Modify-Write Cycle Time

Precharge Time (EDO Page Mode)

Pulse Width (EDO Page Mode Only)

Hold Time from

Access Time from

to Data Delay Time

to Output Low-Z

to Output High-Z

to Data Delay

Command Hold Time

Data Output Hold after

to Output High-Z

to Output High-Z

to

Hold Time

Hold Time to

Precharge Time

Puts width (EDO mixed read write cycle)

Set-Up Time for

(

Delay

Before

Precharge

precharge

low

-before-

counter

Cycle

GLT4160L04

May 2001 (Rev.3.1)

40 50 60 70

Symbol Min. Max. Min. Max. Min. Max. Min. Max. Unit Notes

t

DS

t

DH

t

DHR

t

RWD

t

CWD

t

AWD

t

CPWD

t

RPC

t

CPT

t

CPA

t

PC

t

PRWC

t

CP

t

RASP

t

RHCP

t

OEA

t

OED

t

OLZ

t

OEZ

t

WED

t

OEH

t

DOH

t

REZ

t

WEZ

t

OCH

t

CHO

t

OEP

t

WPE

t

CSR

0 0 0 0 ns

7 8 10 15 ns

36 40 45 50 ns

54 67 79 94 ns

24 30 34 44 ns

32 42 49 59 ns

47 47 54 64 ns

0 5 5 5 ns

20 20 20 25 ns

22 28 35 40 ns

18 20 25 30 ns

50 47 56 71 ns

6 8 10 10 ns

40 100k 50 100k 60 100k 70 100k ns

30 30 35 40 ns

12 13 15 0 20 ns 8

8 13 15 20 ns

3 3 0 0 ns

3 8 3 13 3 15 3 20 ns

15 15 15 20 ns

7 13 15 20 ns

3 5 5 5 ns

3 8 3 13 3 15 3 20 ns

3 10 3 13 3 15 3 20 ns

5 5 5 5 ns

5 5 5 5 ns

5 5 5 5 ns

5 5 5 5 ns

5 5 5 5 ns

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 7 -

Page 8

G-LINK

CAS

CAS

RAS

WE

RAS

CAS

RAS

WE

RAS

CAS

RAS

RAS

CAS

RAS

RAS

CAS

RAS

CAS

CAS

RAS

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Parameter Symbol

t

Hold Time for

to

precharge time (

-before-

refresh )

refresh

to

hold time (

)

Transition Time

Refresh Period (2,048 cycles)

Refresh Period (S-Version)

Pulse Width (

Before

)

precharge Time (

refresh

)

Hold Time (

Before

Before

Before

Cycle

Before

Self

Self

refresh

Self

refresh

CHR

t

WRP

t

WRH

t

T

t

REF

t

REF

t

RASS

t

RPS

t

CHS

)

GLT4160L04

May 2001 (Rev.3.1)

40 50 60 70

Min. Max. Min. Max. Min. Max. Min. Max. Unit Notes

8 10 10 15 ns

10 10 10 10 ns

10 10 10 10 ns

2 50 2 50 2 50 2 50 ns

32 32 32 32 ms

128 128 128 128 ms

100 100 100 100

70 90 110 130 ns

-50 -50 -50 -50 ns

µs

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 8 -

Page 9

G-LINK

RAS

CAS

RAS

CAS

RAS

CAS

RAS

CAS

RAS

CAS

RAS

CAS

OE

OE

OE

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

TEST MODE CYCLE

Parameter

Random read or write cycle time

Read-modify-write cycle time

Access time from

Access time from

Access time from column address

pulse width

pulse width

hold time

hold time

Column address to

to WE delay time

to WE delay time

Column address to WE delay time t

Precharge to WE delay time

EDO Page Mode cycle time

EDO page mode read-modify-write cycle time

Pulse width (EDO page cycle)

Access time form

access time

to data delay

command hold time

Write command set-up time (Test mode in)

Write command hold time (Test mode in)

lead time

precharge

Symbol Min. Max. Min. Max. Min. Max. Min. Max. Unit Notes

t

RC

t

RWC

t

RAC

t

CAC

t

t

RAS

t

CAS

t

RSH

t

CSH

t

RAL

t

CWD

t

RWD

AWD

t

CPWD

t

t

PRWC

t

RASP

t

CPA

t

OEA

t

OED

t

OEH

t

WTS

t

WTH

GLT4160L04

40 50 60 70

89 89 109 129 ns

121 121 145 175 ns

55 55 65 75 ns 1,2,3,7

18 18 20 25 ns 1,3,7

AA

PC

30 30 35 40 ns 1,2,7

55 10k 55 10k 65 10k 75 10k ns

13 10k 13 10k 15 10k 20 10k ns

18 18 20 25 ns

43 43 50 55 ns

30 30 35 40 ns

35 35 39 49 ns 8

72 72 84 99 ns 8

47 47 54 64 ns 8

52 52 59 69 ns 8

25 25 30 35 ns

53 53 61 76 ns

55 100k 55 100k 65 100k 75 100k ns

33 33 40 45 ns 1

18 18 20 25 ns

18 18 20 25 ns

18 18 20 25 ns

10 10 10 10 ns

10 10 10 10 ns

May 2001 (Rev.3.1)

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 9 -

Page 10

G-LINK

CAS

WE

GLT4160L04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

May 2001 (Rev.3.1)

Notes:

1. Measure with a load equivalent to one TTL input and 100 pF.

2. Assumes that t

dominant.

3. Assumes that t

controlled by t

4. Either t

RRH

or t

5. Access time is determined by the longest of tAA, t

6. Assumes that t

7. Operation within the t

is specified as a reference point only. If t

limit, the access time is controlled by t

8. t

9. t

, t

WCS

WCS

, t

RWD

AWD

(min.) must be satisfied in an Early Write Cycle.

10. tDS and tDH are referenced to the latter occurrence of

11. tT is measured between VIH (min.) and VIL (max.). AC-measurements assume tT = 2 ns.

≤ t

RCD

≤ t

RAD

.

CAC

must be satisfied for a Read Cycle.

RCH

≥ t

RAD

and t

(max.). If t

RCD

(max.). If t

RAD

(max.).

RAD

(max.) limit ensures that t

RAD

are not restrictive operating parameters.

CWD

is greater than t

RCD

is greater than t

RAD

is greater than the specified t

RAD

and t

CAA

CAC

(max.), access time will be t

RCD

(max.), access time will be

RCD

and t

CAC

(max.) can be met. t

RAC

CPA

.

.

or

(max.)

RAD

(max.)

RAD

.

AA

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 10 -

Page 11

G-LINK

Read CYCLE

RAS

CAS

Address

WE

OE

DQ

GLT4160L04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

t

RC

t

RAS

V

IH-

V

IL-

t

CRP

V

IH-

V

IL-

t

V

IH-

V

IL-

V

IH-

V

IL-

V

IH-

V

IL-

V

OH-

V

OL-

ASR

ROW

ADDRESS

t

RAH

t

RAD

t

RCS

t

RCD

t

t

ASC

t

RAC

AR

t

CSH

COLUMN

ADDRESS

t

t

t

CAH

AA

CLZ

t

CAC

t

t

t

RAL

OEA

t

CAS

RSH

DATA-OUT

t

OEZ

t

RP

t

t

RRH

CRP

t

RCH

t

CEZ

May 2001 (Rev.3.1)

Early Write Cycle NOTE : D

VIH-

RAS

VIL-

VIH-

CAS

VIL-

DQ

WE

OE

VIH-

VIL-

VIH-

VIL-

VIH-

VIL-

V

V

IH-

IL-

Address

= OPEN

OUT

tCRP

tASR

tRAH

ROW

ADDRESS

tRCD

tRAD

tASC

tWCS

tDHR

tDS tDH

tCSH

COLUMN

ADDRESS

tAR

DATA - IN

tRAS

tCAH

tCWL

tRWL

tWCR

tWCH

tWP

tRC

tCAS

tRAL

t

RSH

Don't Care

tRP

tCRP

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

Don't Care

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 11 -

Page 12

G-LINK

GLT4160L04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

May 2001 (Rev.3.1)

OE Controlled Write Cycle NOTE : D

V

IH-

RAS

V

IL-

V

IH-

CAS

V

IL-

t

t

ADDRESS

Address

WE

DQ

OE

V

IH-

V

IL-

V

IH-

V

IL-

V

IH-

V

IL-

V

IH-

V

IL-

t

CRP

ASR

RAH

OUT

ROW

= OPEN

t

RAD

t

t

ASC

RCS

t

RCD

t

OED

t

COLUMN

ADDRESS

t

DS

DATA - IN

CSH

t

RAS

t

CAH

t

t

DH

t

WP

OEH

t

t

t

RC

CAS

RAL

t

CWL

t

t

RSH

RWL

t

RP

t

CRP

Don't Care

Read - Modify - Write Cycle

V

IH-

RAS

V

IL-

V

IH-

CAS

V

IL-

V

DQ

WE

OE

IH-

V

IL-

IH-

V

V

IL-

V

IH-

V

IL-

V

I/OH-

V

I/OL-

Address

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

t

CRPtRCD

t

RAD

t

ASR

t

ASC

t

RAH

ROW

ADDR.

COLUMN

ADDRESS

t

AA

t

RAC

RC

t

t

RAS

t

RSH

t

CAS

t

CSH

t

CAH

t

AWD

t

CWD

t

OEA

CLZ

t

CAC

t

VALID

DATA-OUT

t

OEZ

t

OED

DS

t

t

t

DH

VALID

DATA-IN

t

WP

t

RWL

CWL

t

RP

CRP

t

Don't Care

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 12 -

Page 13

G-LINK

GLT4160L04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

May 2001 (Rev.3.1)

EDO Page Mode Read Cycle NOTE : D

VIH-

RAS

VIL-

= OPEN

OUT

tCSH

CAS

Address

tCRP

VIH-

VIL-

tCSR

VIH-

VIL-

ROW

ADDR.

tRCD tCAS

tRAD

tRAH

tASC

COLUMN

ADDRESS

tRCS

VIH-

WE

VIL-

VIH-

OE

VIL-

VOH-

DQ

VOL-

EDO Page Mode Early Write Cycle NOTE : D

VIH-

RAS

VIL-

CAS

Address

WE

tCRP

VIH-

VIL-

tASR

VIH-

VIL-

VIH-

VIL-

ROW

ADDR.

tRCD tCAS

tRAD

tRAH

tASC

COLUMN

ADDRESS

tWCS

tCAH

tWCH tWCS tWCStWCH

tCAH

tCAC

tCLZ

tCSH

tWP

tOEA

tRAC

tOLZ

OUT

tPC tPC tPC

tCP

tCAS

tASC

tCAH

COLUMN

ADDRESS

tAA

tCPA

tCAC

tDOH

VALID

DATA-OUT

= OPEN

tPC tPC

tCP tCP

tASC tASC

COLUMN

ADDRESS

tWP tWP

tRASP tRP

tRHCP

tCP tCP

tCAS tCAS

tASC

tOEZ

VALID

DATA-OUT

tOCH

tOEA

tOEP

COL.

ADDR.

tCAH

tASC

tCAC

tAA

tCPA

VALID

DATA-OUT

tCAH

COL.

ADDR.

tRRH

tRCH

tCPA

tCAC

tAA

tCHO

tOEP

tOEZ tOEZ

VALID

DATA-OUT

Don't Care

tRASP tRP

tRHCP

tCAS

tRSH

tCAS

tCAH tCAH

COLUMN

ADDRESS

tWCH

VALID

DATA-OUT

VIH-

OE

VIL-

VIH-

DQ

VIL-

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

tDS tDS tDStDH

VALID

DATA-IN

VALID

DATA-IN

- 13 -

VALID

DATA-IN

tDS

Don't Care

tDS

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

Page 14

G-LINK

GLT4160L04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

May 2001 (Rev.3.1)

EDO Page Mode Read - Modify - Write Cycle NOTE : D

V

RAS

CAS

Address

WE

OE

DQ

IH-

V

IL-

t

ASR

ROW

ADDR.

RCD

t

RAD

t

RAH

t

ASC

t

RCS

t

V

IH-

V

IL-

t

V

IH-

V

IL-

V

IH-

V

IL-

V

IH-

IL-

V

V

I/OH-

V

I/OL-

COL.

ADDR.

CLZ

t

CAH

t

RAC

t

t

CAC

t

AA

t

OEA

t

t

RWD

CSH

t

CWD

AWD

t

CAS

t

OED

t

OEZ

VALID

DATA-OUT

t

CWL

t

WP

t

DH

t

DS

VALID

DATA-IN

EDO PAGE READ AND WRITE MIXED CYCLE

V

IH-

RAS

V

CAS

ADDRESS

WE

OE

DQ

0

~DQ

IL-

t

RAH

t

ROW

COL.

ADDR

t

AA

t

RAC

ASC

t

CAH

t

CAS

t

RCH

t

OEA

t

CAC

DATA-OUT

V

IH-

V

IL-

t

ASR

V

IH-

ADDR

V

IL-

t

RCS

V

IH-

V

IL-

V

IH-

V

IL-

V

I/OH-

3

V

I/OL-

t

CP

t

ASC

COLUMN

ADDRESS

t

t

t

VALID

RCS

WPE

t

CPA

WEZ

t

HPC

t

CAH

OUT

t

RCH

t

t

CLZ

t

WEZ

VALID

DATA-OUT

= OPEN

t

RASP

t

CP

ASC

COL.

ADDR.

t

CLZ

t

RASP

t

CP

t

t

WCStWCH

t

WED

t

ASC

COLUMN

ADDRESS

t

CAH

t

CPWD

t

OEA

t

CAC

t

AA

HPC

t

CAS

t

CAH

t

DH

t

DS

VALID

DATA-IN

t

CAS

t

PRWC

t

RAL

t

CWD

t

AWD

VALID

DATA-OUT

t

RSH

t

OEZ

t

OED

t

CP

t

ASC

COLUMN

ADDRESS

VALID

DATA-IN

t

HPC

t

CAH

t

AA

t

t

t

t

CAS

WP

OEH

DH

t

t

DS

t

CWL

RCH

t

RP

t

CRP

t

RWL

Don't Care

t

VALID

DATA-OUT

t

RP

REZ

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

Don't Care

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 14 -

Page 15

G-LINK

CAS

RAS

RAS

t

t

GLT4160L04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

May 2001 (Rev.3.1)

- Before -

RAS

CAS

WE

Refresh Cycle

V

IH-

V

IL-

V

IH-

V

IL-

V

IH-

V

IL-

Remark Address, OE : Don’t care DQ : Hi - Z

-Only Refresh Cycle

V

IH-

RAS

V

IL-

V

IH-

CAS

V

IL-

V

Address

IH-

V

IL-

Remark WE, OE : Don’t care DQ : Hi - Z

t

t

CSR

WRP

t

t

CRP

ASR

t

CHR

t

WRH

ROW

ADDRESS

t

RAS

t

RAH

t

RAS

t

t

RAS

RC

RC

t

t

RP

t

RPCtCRP

t

RP

RPC

t

t

CRP

t

RC

t

RP

t

t

RPC

RC

t

CSR

t

WRPtWRH

t

RP

t

ASR

t

CHR

t

RAH

ROW

ADDRESS

t

RAS

Hidden Refresh Cycle ( Read )

VIH-

RAS

VIL-

Address

WE

OE

DQ

VIH-

VIL-

VIH-

VIL-

VIH-

VIL-

VIH-

VIL-

V

VIL-

IH-

UCAS,LCAS

t

CRP

ROW

ADDRESS

RC

tRAS tRAS

tRCD

tRAD tRAL

tASC tCAHtASR tCAH

COLUMN

ADDRESS

tRCS

tAA

tRAC

tCLZ

OPEN

tRSH

tCAC

tOEA

tRP

RC

tRP

tCHR

tWRH

tWRPtRRH

tWEZ

tOEZ

DATA-OUT

tCEZ

tREZ

Don't Care

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 15 -

Page 16

G-LINK

GLT4160L04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

May 2001 (Rev.3.1)

Hidden Refresh Cycle ( Write ) NOTE : D

V

IH-

RAS

V

IL-

tCRP

V

IH-

CAS

V

IL-

tCAH

V

Address

WE

OE

DQ

IH-

V

IL-

V

IH-

V

IL-

V

IH-

V

IL-

V

IH-

IL-

V

ROW

ADDRESS

= OPEN

OUT

tRAS tRAS

tRCD

tRSH

tRAD tRSH

COLUMN

ADDRESS

tCAHtASC

tWCH

tASC

tWCS

tWP

tDS

tDH

DATA-IN

t

RC

tRP

tWRP tWRH

tRP

tCHR

Don't Care

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 16 -

Page 17

G-LINK

t

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

CAS-Before RAS Refresh Counter Test Cycle

VIH-

RAS

VIL-

VIH-

CAS

VIL-

VIH-

Address

VIL-

Read Cycle

VIH-

WE

VIL-

VIH-

OE

VIL-

VOH-

DQ

VOL-

Write Cycle

VIH-

WE

VIL-

VIH-

OE

VIL-

VIH-

DQ

VIL-

Read-Modify-Write

VIH-

WE

VIL-

VIH-

OE

VIL-

VI/OH-

DQ

VI/OL-

tCSR

tWRP tWRH

tWRP tWRH

tCHR

tWRHtWRP

OPEN

tRCS

tWCS

tRAS

tCPT

tASC

ADDRESS

tRCS

COLUMN

tCLZ

tDS

VALID DATA-IN

tRSH

tCAS

tRAL

tCAH

tAA

tCAC

tOEA

tRWL

tCWL

tWCH

tWP

tDH

tAWD

tCWD tRWL

tCAC

tAA

tOEA

tOED

tCLZ

tOEZ

VALID

DATA-OUT

tOEZ

VALID DATA-OUT

tCWL

tWP

tDH

tDS

VALID

DATA-IN

GLT4160L04

May 2001 (Rev.3.1)

RP

tRRH

tRCH

tCEZ

Don't Care

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 17 -

Page 18

G-LINK

t

GLT4160L04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

May 2001 (Rev.3.1)

TEST MODE IN CYCLE

RC

tRP

tRAS

tRPC

OPEN

Don't Care

RAS

CAS

WE

DQ

VIH-

VIL-

VIH-

VIL-

VIH-

VIL-

VI/OH-

VI/OL-

tRP

t

RPC

tCP tCSR

tWTS

tCEZ

tCHR

tWTH

Test Mode

By using the test mode, the test time can be reduced. The reason for this is that, the memory emulates the x

16-bit organization during test mode. Don’t care about the input levels of the CAS input A0, A1 .

(1) Setting the mode

Executing the test mode cycle (WE , CAS before RAS refresh cycle ) sets the test mode.

(2) Write / read operation

When either a “0” or a “1” is written to the input pin in test mode, this data is written to 16 bits of memory

cell.

Next, when the data is read from the output pin at the same address, the cell be checked.

Output = “1” Normal write (all memory cells)

Output = “0” Abnormal write

(3) Refresh

Refresh in the test mode must be performed with the RAS / CAS cycle or with the WE, CAS before RAS

refresh cycle. The WE, CAS before RAS refresh cycle use the same counter as the CAS before RAS

refresh’s internal counter.

(4) Mode Cancellation

The test mode is cancelled by executing one cycle of RAS only refresh cycle or CAS before RAS refresh

cycle.

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 18 -

Page 19

G-LINK

t

t

t

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

CAS-BEFORE-RAS SELF REFRESH CYCLE

VIH-

RAS

VIL-

V

CAS

DQ

WE

IH-

VIL-

V

I/OH-

VI/OL-

V

VIL-

IH-

NOTE : OE , Address = Don’t Care

RP

tRPC

tCP

tCEZ

tWRP tWRH

tCSR

RASS

GLT4160L04

May 2001 (Rev.3.1)

RPS

tRPC

tCHS

OPEN

Don't Care

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 19 -

Page 20

G-LINK

Part Number

SPEED

POWER

FEATURE

TEMPERATURE

PACKAGE

GLT4160L04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

May 2001 (Rev.3.1)

Ordering Information

GLT4160L04-40J3 40ns Normal EDO Commercial SOJ 300mil 26(24)L

GLT4160L04-50J3 50ns Normal EDO Commercial SOJ 300mil 26(24)L

GLT4160L04-60J3 60ns Normal EDO Commercial SOJ 300mil 26(24)L

GLT4160L04-70J3 70ns Normal EDO Commercial SOJ 300mil 26(24)L

GLT4160L04E-40J3 40ns Normal EDO Extended SOJ 300mil 26(24)L

GLT4160L04E-50J3 50ns Normal EDO Extended SOJ 300mil 26(24)L

GLT4160L04E-60J3 60ns Normal EDO Extended SOJ 300mil 26(24)L

GLT4160L04E-70J3 70ns Normal EDO Extended SOJ 300mil 26(24)L

GLT4160L04S-40J3 40ns Self Refresh EDO Commercial SOJ 300mil 26(24)L

GLT4160L04S-50J3 50ns Self Refresh EDO Commercial SOJ 300mil 26(24)L

GLT4160L04S-60J3 60ns Self Refresh EDO Commercial SOJ 300mil 26(24)L

GLT4160L04S-70J3 70ns Self Refresh EDO Commercial SOJ 300mil 26(24)L

GLT4160L04SE-40J3 40ns Self Refresh EDO Extended SOJ 300mil 26(24)L

GLT4160L04SE-50J3 50ns Self Refresh EDO Extended SOJ 300mil 26(24)L

GLT4160L04SE-60J3 60ns Self Refresh EDO Extended SOJ 300mil 26(24)L

GLT4160L04SE-70J3 70ns Self Refresh EDO Extended SOJ 300mil 26(24)L

GLT4160L04-40TC 40ns Normal EDO Commercial TSOPII 300mil 26(24)L

GLT4160L04-50TC 50ns Normal EDO Commercial TSOPII 300mil 26(24)L

GLT4160L04-60TC 60ns Normal EDO Commercial TSOPII 300mil 26(24)L

GLT4160L04-70TC 70ns Normal EDO Commercial TSOPII 300mil 26(24)L

GLT4160L04E-40TC 40ns Normal EDO Extended TSOPII 300mil 26(24)L

GLT4160L04E-50TC 50ns Normal EDO Extended TSOPII 300mil 26(24)L

GLT4160L04E-60TC 60ns Normal EDO Extended TSOPII 300mil 26(24)L

GLT4160L04E-70TC 70ns Normal EDO Extended TSOPII 300mil 26(24)L

GLT4160L04S-40TC 40ns Self Refresh EDO Commercial TSOPII 300mil 26(24)L

GLT4160L04S-50TC 50ns Self Refresh EDO Commercial TSOPII 300mil 26(24)L

GLT4160L04S-60TC 60ns Self Refresh EDO Commercial TSOPII 300mil 26(24)L

GLT4160L04S-70TC 70ns Self Refresh EDO Commercial TSOPII 300mil 26(24)L

GLT4160L04SE-40TC 40ns Self Refresh EDO Extended TSOPII 300mil 26(24)L

GLT4160L04SE-50TC 50ns Self Refresh EDO Extended TSOPII 300mil 26(24)L

GLT4160L04SE-60TC 60ns Self Refresh EDO Extended TSOPII 300mil 26(24)L

GLT4160L04SE-70TC 70ns Self Refresh EDO Extended TSOPII 300mil 26(24)L

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 20 -

Page 21

G-LINK

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Parts Numbers (Top Mark) Definition :

GLT4160L04

May 2001 (Rev.3.1)

4 : DRAM

5 : Synchronous

DRAM

6 : Standard

SRAM

7 : Cache SRAM

8 : Synchronous

Burst SRAM

9 : SGRAM

GLT 4 160 L 04 S E - 40 J3

-SRAM

064 : 8K

256 : 256K

512 : 512K

100 : 1M

-DRAM

10 : 1M(C/EDO)

11 : 1M(C/FPM)

12 : 1M(H/EDO)

13 : 1M(H/FPM)

20 : 2M(EDO)

21 : 2M(FPM)

40 : 4M(EDO)

41 : 4M(FPM)

80 : 8M(EDO)

81 : 8M(FPM)

160 : 16M(EDO)

161 : 16M(FPM)

640 : 64M(EDO)

641 : 64M(FPM)

-SDRAM

40 : 4M

160 : 16M

320 : 32M,4Bank

321 : 32M,2Bank

640 : 64M

CONFIG.

04 : x04

08 : x08

16 : x16

32 : x32

VOLTAGE

Blank : 5V

L : 3.3V

M : 2.5V

N : 2.1V

POWER

Blank : Standard

S : Self Refresh Low Power

L : Low Power

LL : Low Low Power

SL : Super Low Power

SPEED

-SRAM

12 : 12ns

15 : 15ns

20 : 20ns

70 : 70ns

-DRAM

25 : 25ns

28 : 28ns

30 : 30ns

35 : 35ns

40 : 40ns

45 : 45ns

50 : 50ns

60 : 60ns

70 : 70ns

80 : 80ns

100 : 100ns

SDRAM :

5 : 5ns/200 MHZ

5.5 : 5.5ns/182 MHZ

6 : 7ns/166 MHZ

7 : 8ns/125 MHZ

10 : 10ns/100 MHZ

PACKAGE

T : PDIP(300mil)

TS : TSOP(Type I)

ST : sTSOP(Type I)

TC : TSOPll (40/44)

TD : TSOPII (44/50)

PL : PLCC

FA : 300mil SOP

FB : 330mil SOP

FC : 445mil SOP

J3 : 300mil SOJ

J4 : 400mil SOJ

P : PDIP(600mil)

Q : PQFP

TQ : TQFP

FG : 48Pin BGA 9x12

FH : 48Pin BGA 8x10

FI : 48Pin BGA 6x8

Temperature Range

E : Extended Temperature

I : Industrial Temperature

Blank : Commercial Temperature

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 21 -

Page 22

G-LINK

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Package Information

300mil 24/26 Lead Thin Small Outline Package SOJ

GLT4160L04

May 2001 (Rev.3.1)

300mil 24/26 Lead Thin Small Outline Package (TSOP) TYPE II

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD, IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 22 -

Loading...

Loading...