Page 1

www.fairchildsemi.com

FMS3110/3115

Triple Video D/A Converters

3 x 10 bit, 150 Ms/s

Features

• 10-bit resolution

• 150 megapixels per second

• ± 0.1% linearity error

• Sync and blank controls

• 1.0V p-p video into 37.5 Ω or 75 Ω load

• Internal bandgap voltage reference

• Double-buffered data for low distortion

• TTL-compatible inputs

• Low glitch energy

• Single +5 Volt power supply

Applications

• Video signal conversion

– RGB

– YC

C

B

R

– Composite, Y, C

• Multimedia systems

• Image processing

• True-color graphics systems (1 billion colors)

• Broadcast television equipment

• High-Definition Television (HDTV) equipment

• Direct digital synthesis

Description

FMS3110/3115 products are low-cost triple D/A converters

that are tailored to fit graphics and video applications where

speed is critical. Two speed grades are available:

FMS3110 100 Ms/s

FMS3115 150 Ms/s

TTL-level inputs are converted to analog current outputs that

can drive 25–37.5 Ω loads corresponding to doubly-terminated

50–75 Ω loads. A sync current following SYNC

is added to the I

inputs, setting I

output. BLANK

OG

, I

OB

and I

OG

will override RGB

currents to zero when

OR

BLANK = L. Although appropriate for many applications

the internal 1.235V reference voltage can be overridden by

the V

REF

input.

Few external components are required, just the current

reference resistor, current output load resistors, and

decoupling capacitors.

Package is a 48-lead LQFP. Fabrication technology is

CMOS. Performance is guaranteed from 0 to 70°C.

input timing

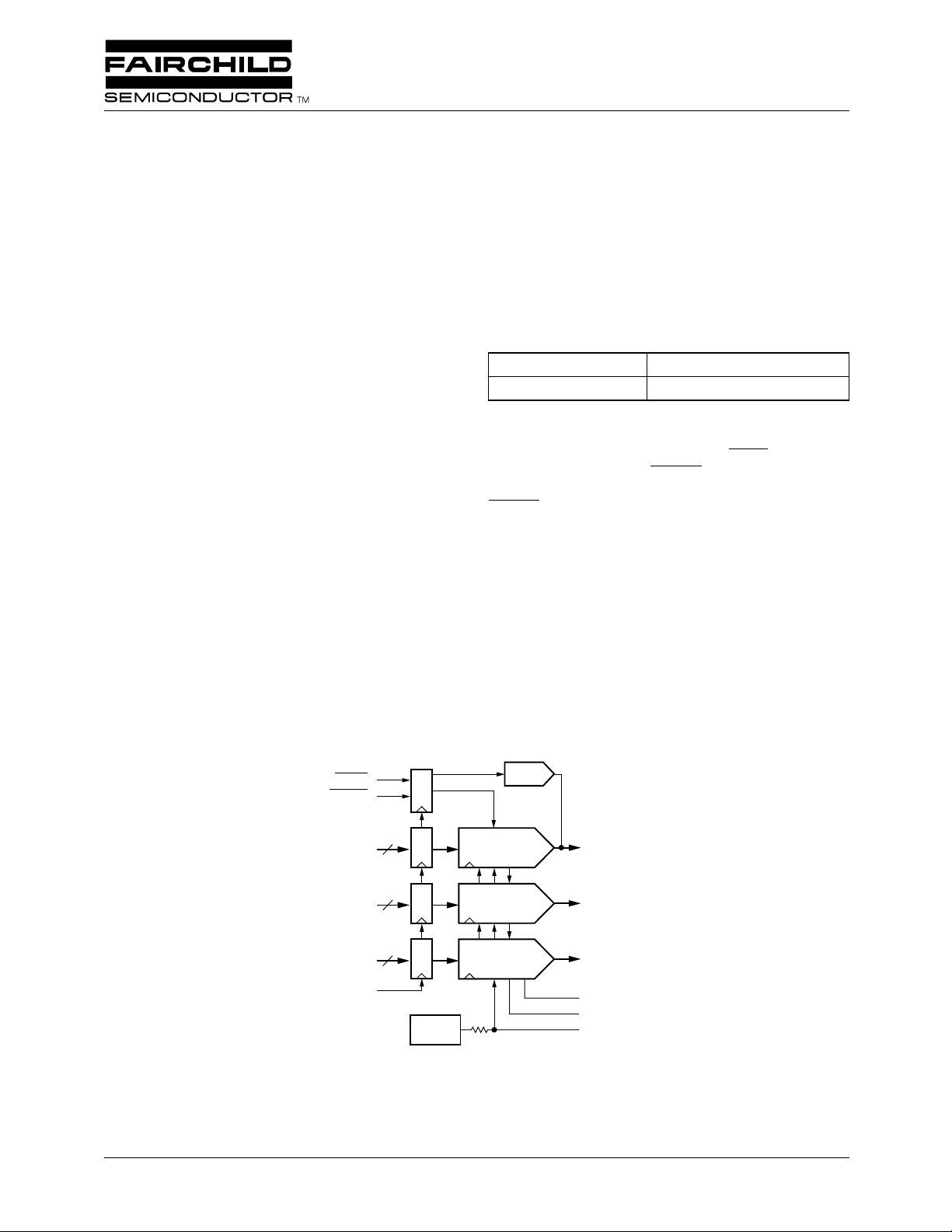

Block Diagram

SYNC

BLANK

G

9-0

B

9-0

R

9-0

CLOCK

10

10

10

+1.235V

Ref

SYNC

10 bit D/A

Converter

10 bit D/A

Converter

10 bit D/A

Converter

IO

G

IO

B

IO

R

COMP

R

REF

V

REF

Rev. 1.05 12/21/00

Page 2

FMS3110/3115 PRODUCT SPECIFICATION

Functional Description

Within the FMS3110/3115 are three identical 10-bit D/A

converters, each with a current source output. External loads

are required to convert the current to voltage outputs. Data

inputs RGB

= H activates, sync current from I

are overridden by the BLANK

7-0

for sync-on-green video

OS

signals.

Digital Inputs

All digital inputs are TTL-compatible. Data is registered on

the rising edge of the CLK signal. Following one stage of

pipeline delay, the analog output changes t

edge of CLK.

and BLANK

SYNC

SYNC and BLANK inputs control the output level (Figure 1

and Table 1) of the D/A converters during CRT retrace

intervals. BLANK forces the D/A outputs to the blanking

level while SYNC = L turns off a current source that is

connected to the green D/A converter. SYNC = H adds a 40

IRE sync pulse to the green output, SYNC = L sets the green

output to 0.0 Volts during the sync tip. SYNC and BLANK

are registered on the rising edge of CLK.

BLANK gates the D/A inputs and sets the pedestal voltage.

If BLANK = HIGH, the D/A inputs are added to a pedestal

which offsets the current output. If BLANK = Low, data

inputs and the pedestal are disabled.

input. SYNC

after the rising

DO

D/A Outputs

Each D/A output is a current source. To obtain a voltage

output, a resistor must be connected to ground. Output

voltage depends upon this external resistor, the reference

voltage, and the value of the gain-setting resistor connected

between R

and GND.

REF

Normally, a source termination resistor of 75 Ohms is

connected between the D/A current output pin and GND

near the D/A converter. A 75 Ohm line may then be

connected with another 75 Ohm termination resistor at the

far end of the cable. This “double termination” presents the

D/A converter with a net resistive load of 37.5 Ohms.

The FMS3110/3115 may also be operated with a single 75

Ohm terminating resistor. To lower the output voltage swing

to the desired range, the nominal value of the resistor on

R

should be doubled.

REF

Voltage Reference

All three D/A converters are supplied with a common

voltage reference. Internal bandgap voltage reference voltage

is +1.235 Volts with a 3K Ω source resistance. An external

voltage reference may be connected to the V

overriding the internal voltage reference.

A 0.1µF capacitor must be connected between the COMP

pin and V

to stabilize internal bias circuitry and ensure

DD

low-noise operation.

REF

pin,

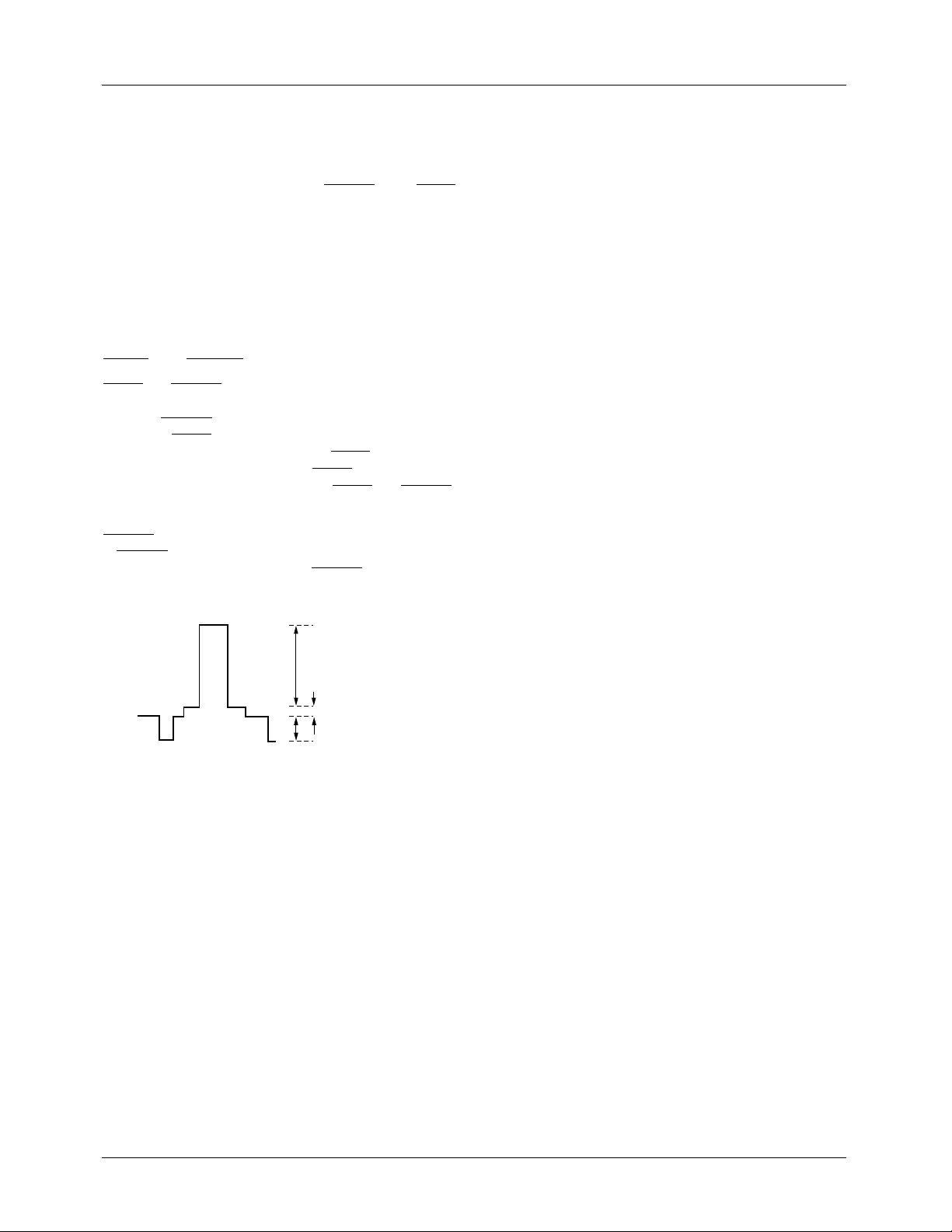

data: 660 mV max.

pedestal: 54 mV

sync: 286 mV

Figure 1. Nominal Output Levels

Power and Ground

Required power is a single +5.0 Volt supply. To minimize

power supply induced noise, analog +5V should be connected

to V

pins with 0.1 and 0.01 µF decoupling capacitors

DD

placed adjacent to each V

The high slew-rate of digital data makes capacitive coupling

to the outputs of any D/A converter a potential problem.

Since the digital signals contain high-frequency components

of the CLK signal, as well as the video output signal, the

resulting data feedthrough often looks like harmonic

distortion or reduced signal-to-noise performance. All

ground pins should be connected to a common solid ground

plane for best performance.

pin or pin pair.

DD

2

REV. 1.05 12/21/00

Page 3

PRODUCT SPECIFICATION FMS3110/3115

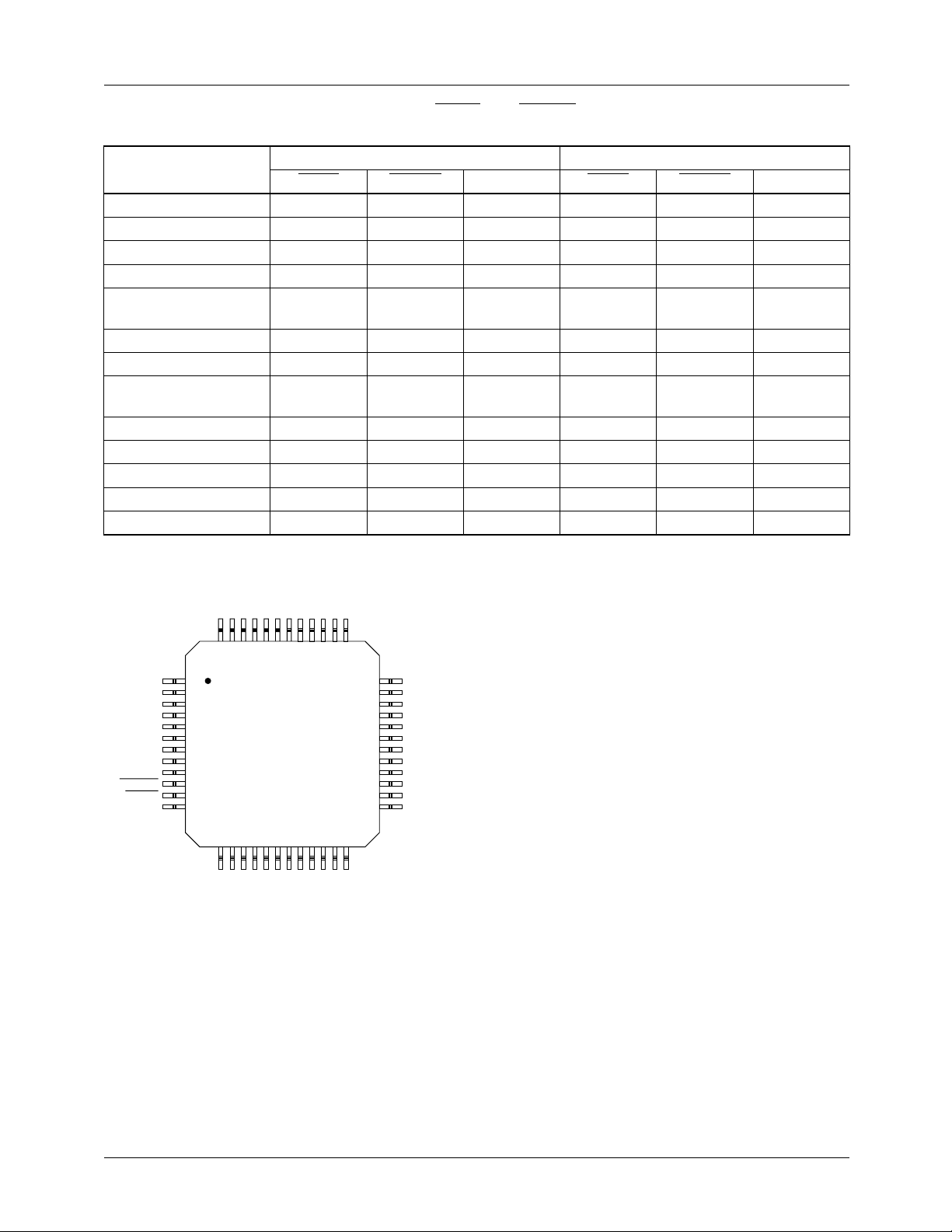

Table 1. Output Voltage Versus Input Code, SYNC

V

= 1.235 V, R

REF

= 590 Ω , R

REF

= 37.5 Ω

L

and BLANK

Blue and Red D/As Green D/A

RGB

(MSB…LSB)

9-0

SYNC BLANK V

OUT

SYNC BLANK V

11 1111 1111 X 1 0.7140 1 1 1.0000

11 1111 1111 X 1 0.7140 0 1 0.7140

11 1111 1110 X 1 0.7134 1 1 0.9994

11 1111 1101 X 1 0.7127 1 1 0.9987

•

•

•

•

•

•

•

•

•

•

•

•

10 0000 0000 X 1 0.3843 1 1 0.6703

01 1111 1111 X 1 0.3837 1 1 0.6697

•

•

•

•

•

•

•

•

•

•

•

•

00 0000 0010 X 1 0.0553 1 1 0.3413

00 0000 0001 X 1 0.0546 1 1 0.3406

00 0000 0000 X 1 0.0540 1 1 0.3400

XX XXXX XXXX X 0 0.0000 1 0 0.2860

XX XXXX XXXX X 0 0.0000 0 0 0.0000

OUT

•

•

•

•

Pin Assignments

G0R9R8R7R6R5R4R

484746454443424140

G

G

G

G

G

G

G

G

G

BLANK

SYNC

V

DD

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

11

12

FMS3110/3115

131415161718192021

B0B1B2B3B4B6B

NC

LQFP

3

5

0

R2R1NC

R

39

38

37

22

23

24

9

B7B8B

NC

36

35

34

33

32

31

30

29

28

27

26

25

R

REF

V

REF

COMP

IO

R

IO

G

OV

DD

V

DD

IO

B

GND

GND

CLOCK

NC

REV. 1.05 12/21/00

3

Page 4

FMS3110/3115 PRODUCT SPECIFICATION

Pin Descriptions

Pin Name Pin Number Value Description

Clock and Pixel I/O

CLK 26 TTL

R

9-0

G

9-0

B

9-0

47-37 TTL

48, 9–1 TTL

23–14 TTL

Controls

SYNC 11 TTL

Clock Input. The clock input is TTL-compatible and all pixel data is

registered on the rising edge of CLK. It is recommended that CLK be

driven by a dedicated TTL buffer to avoid reflection induced jitter,

overshoot, and undershoot.

Red Pixel Data Inputs. TTL-compatible Red Data Inputs are

registered on the rising edge of CLK.

Green Pixel Data Inputs. TTL-compatible Green Data Inputs are

registered on the rising edge of CLK.

Blue Pixel Data Inputs. TTL-compatible Blue Data Inputs are

registered on the rising edge of CLK.

Sync Pulse Input. Bringing SYNC LOW, turns off a 40 IRE (7.62 mA)

current source which forms a sync pulse on the Green D/A converter

output. SYNC is registered on the rising edge of CLK with the same

pipeline latency as BLANK and pixel data. SYNC does not override

any other data and should be used only during the blanking interval.

BLANK 10 TTL

Video Outputs

IO

IO

IO

R

G

B

33 0.714 V

32 1 V

p-p

29 0.714 V

Since this is a single-supply D/A and all signals are positive-going,

sync is added to the bottom of the Green D/A range. So turning SYNC

OFF means turning the current source ON. When a sync pulse is

desired, the current source is turned OFF. If the system does not

require sync pulses from the Green D/A converter, SYNC should be

connected to GND.

Blanking Input. When BLANK is LOW, pixel inputs are ignored and

the D/A converter outputs fall to the blanking level. BLANK is

registered on the rising edge of CLK and has the same pipeline

latency as SYNC

Red Current Output. The current source outputs of the D/A

p-p

.

converters are capable of driving RS-343A/SMPTE-170M compatible

levels into doubly-terminated 75 Ohm lines.

Green Current Output. The current source outputs of the D/A

converters are capable of driving RS-343A/SMPTE-170M compatible

levels into doubly-terminated 75 Ohm lines. Sync pulses may be

added to the Green D/A output.

Blue Current Output. The current source outputs of the D/A

p-p

converters are capable of driving RS-343A/SMPTE-170M compatible

levels into doubly-terminated 75 Ohm lines.

4

REV. 1.05 12/21/00

Page 5

PRODUCT SPECIFICATION FMS3110/3115

Pin Descriptions

(continued)

Pin Name Pin Number Value Description

Voltage Reference

V

REF

35 +1.235 V Voltage Reference Output/Input. An internal voltage source of

+1.235 Volts is output on this pin. An external +1.235 Volt reference

may be applied here which overrides the internal reference.

R

REF

Decoupling V

36 560 Ω Current-Setting Resistor. Full-scale output current of each D/A

to GND with a 0.1µF ceramic capacitor is required.

REF

converter is determined by the value of the resistor connected

between R

R

= 9.1 (V

REF

where I

FS

D/A converter (without sync). Sync is 0.4 * I

and GND. Nominal value of R

REF

/I

FS

)

REF

is found from:

REF

is the full-scale (white) output current (in amps) from the

.

FS

D/A full-scale (white) current may also be calculated from:

I

= V

FS

Where V

(in ohms) on each D/A converter. V

/R

FS

L

is the white voltage level and R

FS

is the total resistive load

L

is the blank to full-scale

FS

voltage.

COMP 34 0.1 µF Compensation Capacitor. A 0.1 µF ceramic capacitor must be

connected between COMP and V

to stabilize internal bias circuitry.

DD

Power and Ground

V

DD

GND 27, 28 0.0V

12, 30, 31 +5 V

Power Supply.

Ground.

Equivalent Circuits

Digital

Input

GND

Figure 2. Equivalent Digital Input Circuit

V

DD

p

np

n

Figure 3. Equivalent Analog Output Circuit

V

GND

V

DD

DD

OUT

REV. 1.05 12/21/00

5

Page 6

FMS3110/3115 PRODUCT SPECIFICATION

Equivalent Circuits

Absolute Maximum Ratings

(continued)

R

REF

V

REF

Figure 4. Equivalent Analog Input Circuit

V

DD

p

GND

p

27012B

(beyond which the device may be damaged)

1

Parameter Min Typ Max Unit

Power Supply Voltage

V

(Measured to GND) -0.5 7.0 V

DD

Inputs

Applied Voltage (measured to GND)

Forced Current

3,4

2

-0.5 V

+ 0.5 V

DD

-10.0 10.0 mA

Outputs

Applied Voltage (measured to GND)

Forced Current

3,4

2

-0.5 VDD + 0.5 V

-60.0 60.0 mA

Short Circuit Duration (single output in HIGH state to ground) Infinite second

Temperature

Operating, Ambient -20 110 °C

Junction 150 °C

Lead Soldering (10 seconds) 300 °C

Vapor Phase Soldering (1 minute) 220 °C

Storage -65 150 °C

Notes:

1. Functional operation under any of these conditions is NOT implied. Performance and reliability are guaranteed only if

Operating Conditions are not exceeded.

2. Applied voltage must be current limited to specified range.

3. Forcing voltage must be limited to specified range.

4. Current is specified as conventional current flowing into the device.

6

REV. 1.05 12/21/00

Page 7

PRODUCT SPECIFICATION FMS3110/3115

Operating Conditions

Parameter Min Nom Max Units

V

DD

f

S

t

PWH

t

PWL

t

W

t

S

t

h

t

PWH

t

PWL

V

REF

C

C

R

L

V

IH

V

IL

T

A

Power Supply Voltage 4.75 5.0 5.25 V

Conversion Rate FMS3110 100 Msps

FMS3115 150 Msps

CLK Pulsewidth, HIGH FMS3110 3.1 ns

FMS3115 2.5 ns

CLK Pulsewidth, LOW FMS3110 3.1 ns

FMS3115 2.5 ns

CLK Pulsewidth FMS3110 10 ns

FMS3115 6.6 ns

Input Data Setup Time 1.7 ns

Input Date Hold Time 0 ns

CLK Pulsewidth, HIGH 2 ns

CLK Pulsewidth, LOW 2 ns

Reference Voltage, External 1.0 1.235 1.5 V

Compensation Capacitor 0.1 µF

Output Load 37.5 Ω

Input Voltage, Logic HIGH 2.0 V

DD

V

Input Voltage, Logic LOW GND 0.8 V

Ambient Temperature, Still Air 0 70 °C

Electrical Characteristics

Parameter Conditions

I

DD

PD

R

O

C

O

I

IH

I

IL

I

REF

V

REF

V

OC

C

DI

Notes:

1. Values shown in Typ column are typical for V

2. Minimum/Maximum values with V

3. V

Power Supply Current

Total Power Dissipation

Output Resistance 100 kΩ

Output Capacitance I

Input Current, HIGH VDD = Max, VIN = 2.4V -5 µA

Input Current, LOW VDD = Max, VIN = 0.4V 5 µA

V

Input Bias Current 0 ±100 µA

REF

Reference Voltage Output 1.235 V

Output Compliance Referred to V

Digital Input Capacitance 4 10 pF

= 1.235V, R

REF

LOAD

= 37.5Ω, R

2

DD

VDD = Max 125 mA

2

V

= Max 655 mW

DD

= 0mA 30 pF

OUT

= +5V and TA = 25°C.

DD

= Max and TA = Min.

= 540Ω

REF

3

DD

Min Typ

-0.4 0 +1.5 V

1

Max Units

REV. 1.05 12/21/00 7

Page 8

FMS3110/3115 PRODUCT SPECIFICATION

Switching Characteristics

Parameter Conditions

t

D

t

SKEW

t

R

t

F

Notes:

1. Values shown in Typ column are typical for V

2. V

Clock to Output Delay VDD = Min 10 15 ns

Output Skew 1 2 ns

Output Risetime 10% to 90% of Full Scale 3 ns

Output Falltime 90% to 10% of Full Scale 3 ns

= +5V and TA = 25°C.

DD

= 1.235V, R

REF

LOAD

= 37.5Ω, R

REF

= 590Ω.

2

Min Typ

1

Max Units

System Performance Characteristics

Parameter Conditions

E

LI

E

LD

E

DM

Integral Linearity Error VDD, V

Differential Linearity Error VDD, V

DAC to DAC Matching VDD, V

2

= Nom ±0.1 ±0.25 %/FS

REF

= Nom ±0.1 ±0.25 %/FS

REF

= Nom 3 10 %

REF

Min Typ

PSR Power Supply Rejection Ratio 0.05 %/%

Notes:

1. Values shown in Typ column are typical for V

2. V

= 1.235V, R

REF

LOAD

= 37.5Ω, R

REF

= 590Ω.

= +5V and TA = 25°C.

DD

1

Max Units

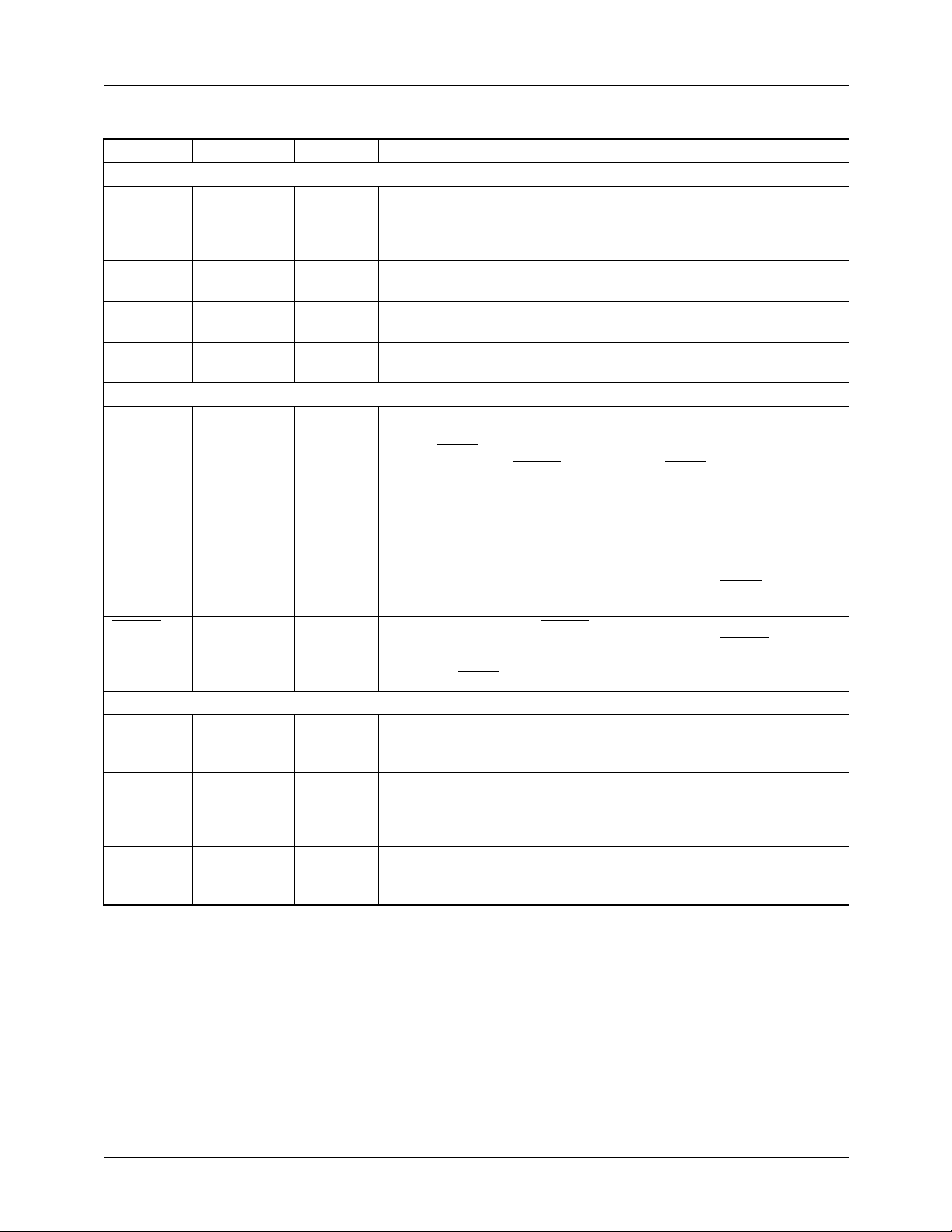

Timing Diagram

CLK

PIXEL DATA

& CONTROLS

OUTPUT

1/f

t

PWL

t

S

DataN DataN+1 DataN+2

50%

t

PWH

t

H

3%/FS

t

D

t

SET

S

90%

t

F

10%

t

R

8 REV. 1.05 12/21/00

Page 9

PRODUCT SPECIFICATION FMS3110/3115

Applications Discussion

Figure 5 illustrates a typical FMS3110/3115 interface circuit. In this example, an optional 1.2 Volt bandgap reference

is

connected to the V

age reference source.

Grounding

It is important that the FMS3110/3115 power supply is wellregulated and free of high-frequency noise. Careful power

supply decoupling will ensure the highest quality video signals at the output of the circuit. The FMS3110/3115 has separate analog and digital circuits. To keep digital system noise

from the D/A converter, it is recommended that power supply

voltages (VDD) come from the system analog power source

and all ground connections (GND) be made to the analog

ground plane. Power supply pins should be individually

decoupled at the pin.

Printed Circuit Board Layout

Designing with high-performance mixed-signal circuits

demands printed circuits with ground planes. Overall system

performance is strongly influenced by the board layout.

Capacitive coupling from digital to analog circuits may

result in poor D/A conversion. Consider the following suggestions when doing the layout:

output, overriding the internal volt-

REF

2. Power plane for the FMS3110/3115 should be separate

from that which supplies the digital circuitry. A single

power plane should be used for all of the VDD pins. If

the power supply for the FMS3110/3115 is the same as

that of the system's

digital circuitry, power to the FMS3110/3115 should be

decoupled with 0.1µF and 0.01µF capacitors and isolated with a ferrite bead.

3. The ground plane should be solid, not cross-hatched.

Connections to the ground plane should have very short

leads.

4. If the digital power supply has a dedicated power plane

layer, it should not be placed under the FMS3110/3115,

the voltage reference, or the analog outputs. Capacitive

coupling of digital power supply noise from this layer to

the FMS3110/3115 and its related analog circuitry can

have an adverse effect on performance.

5. CLK should be handled carefully. Jitter and noise on

this clock will degrade performance. Terminate the

clock line carefully to eliminate overshoot and ringing.

Related Products

• FMS38XX Triple 8-bit 150 Msps D/A Converters

• FMS9884A 3 x 8-bit 140 Ms/s A/D Converter

1. Keep the critical analog traces (V

REF

, I

REF

, COMP,

IOS, IOR, IOG) as short as possible and as far as possible from all digital signals. The FMS3110/3115 should

be located near the board edge, close to the analog output connectors.

+5V

10µF

0.1µF

VDD

RED PIXEL

INPUT

GREEN PIXEL

INPUT

BLUE PIXEL

INPUT

CLOCK

SYNC

BLANK

R

9-0

G

9-0

B

9-0

CLK

SYNC

BLANK

FMS31XX

Triple 10-bit

D/A Converter

GND

IO

IO

IO

COMP

V

REF

R

REF

Red

R

75Ω

G

75Ω

B

75Ω

0.1µF

560Ω

ZO=75Ω

Green w/Sync

ZO=75Ω

Blue

=75Ω

Z

O

+5V

3.3kΩ (not required without

LM185-1.2

(Optional)

75Ω

75Ω

75Ω

external reference)

0.1µF

Figure 5. Typical Interface Circuit

REV. 1.05 12/21/00 9

Page 10

FMS3110/3115 PRODUCT SPECIFICATION

Mechanical Dimensions

48-Lead LQFP Package

Symbol

A .055 .063 1.40 1.60

A1 .001 .005 .05 .15

A2 .053 1.35

B .006 .010 .17 .27

D/E

D1/E1

e

L .017 .029 .45 .75 6

N48 48

ND

α 0° 7° 0° 7°

ccc .004 0.08

Inches

Min. Max. Min. Max.

.057 1.45

.346 .362 8.8 9.2

.268 .284 6.8 7.2

.019 BSC

12 12

Millimeters

.50 BSC

D

D1

Notes

Notes:

All dimensions and tolerances conform to ANSI Y14.5M-1982.

1.

Dimensions "D1" and "E1" do not include mold protrusion.

2.

Allowable protrusion is 0.25mm per side. D1 and E1 are maximum

plastic body size dimensions including mold mismatch.

Pin 1 identifier is optional.

3.

7

8

2

4

5

Dimension ND: Number of terminals.

4.

Dimension ND: Number of terminals per package edge.

5.

"L" is the length of terminal for soldering to a substrate.

6.

Dimension "B" does not include dambar protrusion. Allowable

7.

dambar protrusion shall not cause the lead width to exceed the

maximum B dimension by more than 0.08mm. Dambar can not be

located on the lower radius or the foot. Minimum space between

protrusion and an adjacent lead is 0.07mm for 0.4mm and 0.5mm

pitch packages.

8.

To be determined at seating place —C—

e

B

PIN 1

IDENTIFIER

Seating Plane

See Lead Detail

Base Plane

-C-

LEAD COPLANARITY

ccc

0.063" Ref (1.60mm)

C

C

L

α

E1

E

A2

A

A1

10 REV. 1.05 12/21/00

Page 11

FMS3110/3115 PRODUCT SPECIFICATION

Ordering Information

Conversion

Product Number

Rate Temperature Range Screening Package

FMS3110KRC 100 Ms/s T

FMS3115KRC 150 Ms/s T

Package

Marking

= 0°C to 70°C Commercial 48-Lead LQFP 3110KRC

A

= 0°C to 70°C Commercial 48-Lead LQFP 3115KRC

A

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES

OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR

CORPORATION. As used herein:

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the body,

or (b) support or sustain life, and (c) whose failure to

perform when properly used in accordance with

instructions for use provided in the labeling, can be

reasonably expected to result in a significant injury of the

user.

www.fairchildsemi.com

2. A critical component in any component of a life support

device or system whose failure to perform can be

reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

12/21/00 0.0m 003

2000 Fairchild Semiconductor Corporation

Stock#DS30003110

Loading...

Loading...