Page 1

FDH15N50 / FDP15N50 / FDB15N50

15A, 500V, 0.38 Ohm, N-Channel SMPS Power MOSFET

FDH15N50 / FDP15N50 / FDB15N50

August 2003

Applications

Switch Mode Power Supplies(SMPS), such as

• PFC Boost

• Two-Switch Forward Converter

• Single Switch Forward Converter

• Flyback Converter

• Buck Converter

• High Speed Switching

Features

• Low Gate Charge Qg results in Simple Drive

Requirement

• Improved Gate, Avalanche and High Reapplied dv/dt

Ruggedness

• Reduced r

• Reduced Miller Capacitance and Low Input Capacitance

• Improved Switching Speed with Low EMI

DS(ON)

• 175°C Rated Junction Temperature

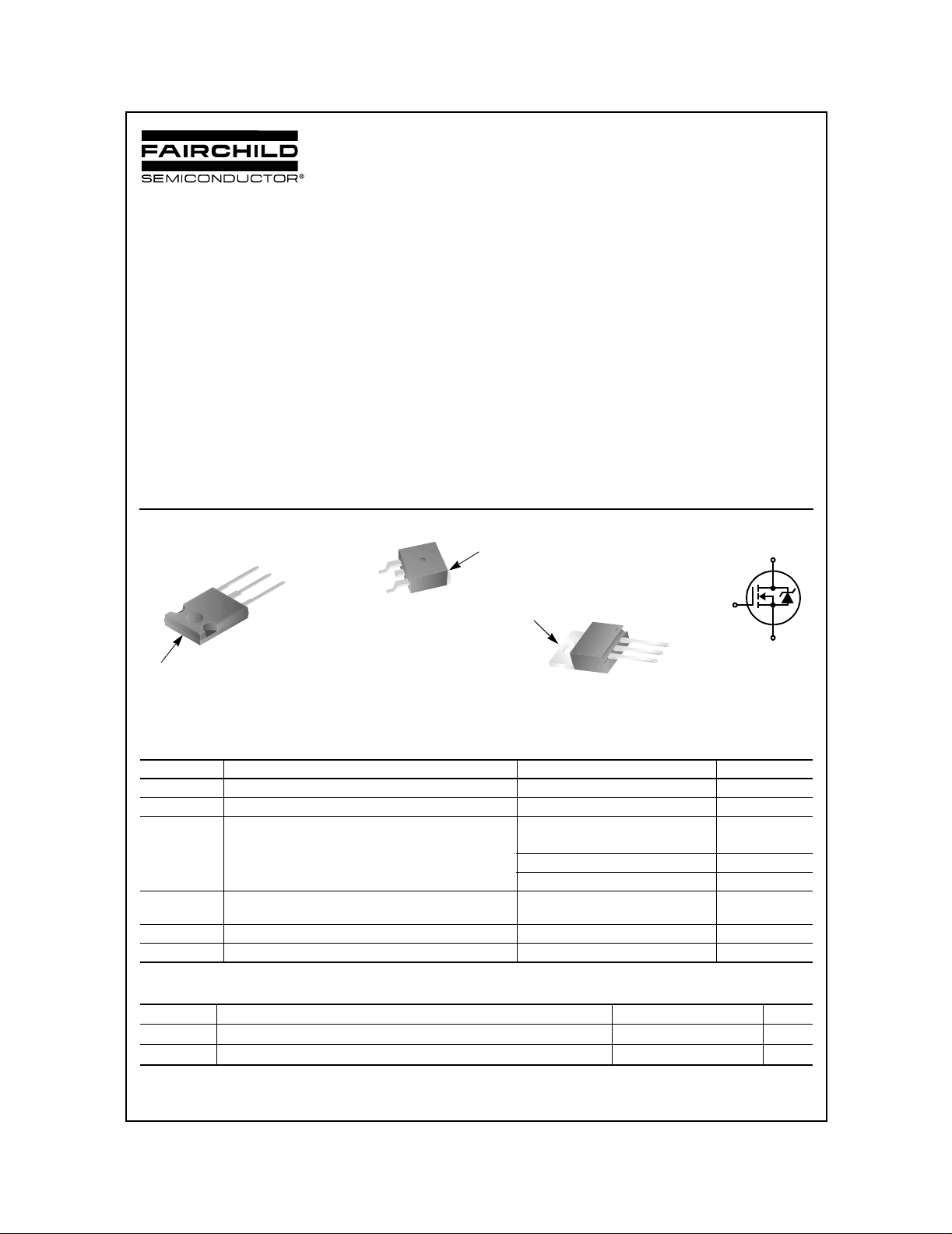

Package

DRAIN

(BOTTOM)

SOURCE

DRAIN

GATE

TO-247

FDH SERIES

GATE

SOURCE

TO-263AB

FDB SERIES

Absolute Maximum Ratings T

DRAIN

(FLANGE)

o

= 25

C unless otherwise noted

C

DRAIN

(FLANGE)

TO-220AB

FDP SERIES

SOURCE

DRAIN

GATE

Symbol

G

Symbol Parameter Ratings Units

V

DSS

V

GS

Drain to Source Voltage 500 V

Gate to Source Voltage ±30 V

Drain Current

I

D

P

, T

T

J

Continuous (T

Continuous (T

1

Pulsed

Power dissipation

D

Derate above 25

Operating and Storage Temperature -55 to 175

STG

= 25oC, VGS = 10V)

C

= 100oC, VGS = 10V) 11 A

C

o

C

15 A

60 A

300

2

Soldering Temperature for 10 seconds 300 (1.6mm from case)

D

S

W

W/oC

o

C

o

C

Thermal Characteristics

R

R

R

©2003 Fairchild Semiconductor Corporation

Thermal Resistance Junction to Case 0.50

θJC

Thermal Resistance Junction to Ambient (TO-247) 40

θJA

Thermal Resistance Junction to Ambient (TO-220, TO-263) 62

θJA

o

C/W

o

C/W

o

C/W

FDH15N50 / FDP15N50 / FDB15N50 RevD2

Page 2

Package Marking and Ordering Information

Device Marking Device Package Reel Size Tape Width Quantity

FDH15N50 FDH15N50 TO-247 Tube - 30

FDP15N50 FDP15N50 TO-220 Tube - 50

FDB15N50 FDB15N50 TO-263 330mm 24mm 800

FDH15N50 / FDP15N50 / FDB15N50

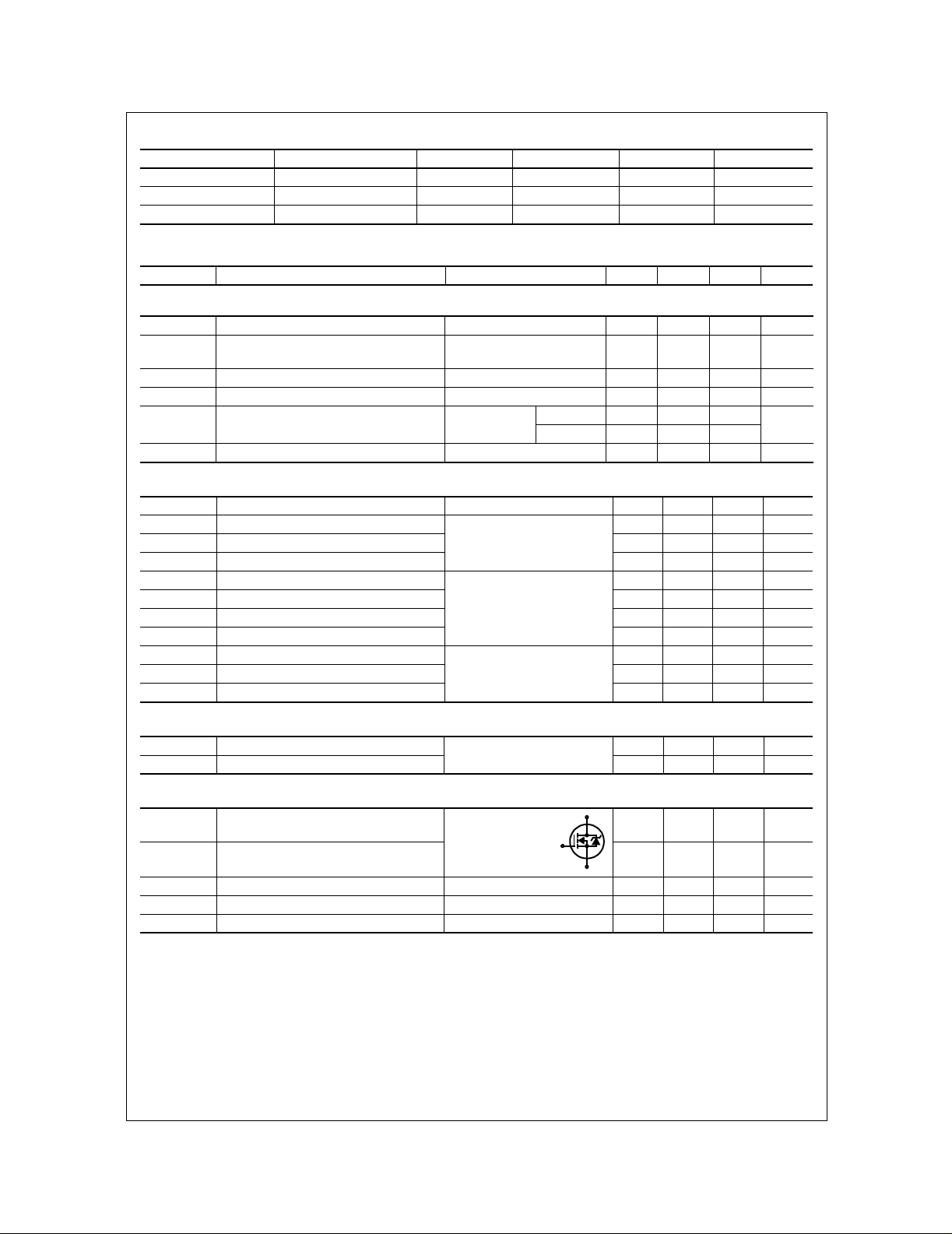

Electrical Characteristics

TJ = 25°C (unless otherwise noted)

Symbol Parameter Test Conditions Min Typ Max Units

Statics

Drain to Source Breakdown Voltage ID = 250µA, VGS = 0V 500 - - V

/∆TJBreakdown Voltage Temp. Coefficient

Reference to 25

ID = 1mA

o

C,

-0.58-V/°C

Drain to Source On-Resistance VGS = 10V, ID = 7.5A - 0.33 0.38 Ω

Gate Threshold Voltage VDS = VGS, ID = 250µA 2.0 3.4 4.0 V

V

= 500V TC = 25oC- - 25

Zero Gate Voltage Drain Current

DS

= 0V TC = 150oC- - 250

V

GS

Gate to Source Leakage Current VGS = ±30V - - ±100 nA

∆B

B

VDSS

VDSS

r

DS(ON)

V

GS(th)

I

DSS

I

GSS

Dynamics

g

Q

g(TOT)

Q

Q

t

d(ON)

t

d(OFF)

C

C

OSS

C

RSS

Forward Transconductance VDD = 10V, ID = 7.5A 10 - - S

fs

Total Gate Charge at 10V

Gate to Source Gate Charge - 7.2 10 nC

gs

Gate to Drain “Miller” Charge - 12 16 nC

gd

Tur n-On Delay Time

t

Rise Time - 5.4 - ns

r

Turn-Off Delay Time - 26 - ns

t

Fall Time - 5 - ns

f

Input Capacitance

ISS

Output Capacitance - 230 - pF

Reverse Transfer Capacitance - 16 - pF

V

= 10V,

GS

V

= 400V,

DS

= 15A

I

D

= 250V,

V

DD

= 15A,

I

D

= 6.2Ω,

R

G

R

= 17Ω

D

= 25V, VGS = 0V,

V

DS

f = 1MHz

-3341nC

-9-ns

-1850- pF

µA

Avalanche Characteristics

E

I

AR

Single Pulse Avalanche Energy

AS

Avalanche Current - - 15 A

2

760 - - mJ

Drain-Source Diode Characteristics

I

I

SM

V

t

Q

Notes:

1: Repetitive rating; pulse width limited by maximum junction temperature

2: Starting T

©2003 Fairchild Semiconductor Corporation FDH15N50 / FDP15N50 / FDB15N50 RevD2

Continuous Source Current

S

(Body Diode)

Pulsed Source Current

1

(Body Diode)

Source to Drain Diode Voltage I

SD

Reverse Recovery Time ISD = 15A, diSD/dt = 100A/µs - 470 730 ns

rr

Reverse Recovered Charge ISD = 15A, diSD/dt = 100A/µs - 5 6.6 µC

RR

= 25°C, L = 7.0mH, IAS = 15A

J

MOSFET symbol

showing the

integral reverse

p-n junction diode.

= 15A - 0.86 1.2 V

SD

D

G

S

--15A

--60A

Page 3

Typical Characteristics

FDH15N50 / FDP15N50 / FDB15N50

100

TJ = 25oC

VGS DESCENDING

10V

6.5V

6V

5.5V

5V

4.5V

10

PULSE DURATION = 80µs

DUTY CYCLE = 0.5% MAX

, DRAIN TO SOURCE CURRENT (A)

D

I

1

110100

VDS, DRAIN TO SOURCE VOLTAGE (V)

100

TJ = 175oC

VGS DESCENDING

10V

6V

5.5V

5V

4.5V

4V

10

, DRAIN TO SOURCE CURRENT (A)

D

I

1

110100

PULSE DURATION = 80µs

DUTY CYCLE = 0.5% M AX

VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 1. Output Characteristics Figure 2. Output Characteristics

60

PULSE DURATION = 80µs

DUTY CYCLE = 0.5% MAX

50

VDD = 100V

40

30

20

, DRAIN CURRENT (A)

D

I

10

0

3.0 3.5 4.0 4.5 5.0 5.5 6.0 6.5

TJ = 175oC

TJ = 25oC

VGS, GATE TO SOURCE VOLTAGE (V)

3.5

PULSE DURATION = 80µs

3.0

DUTY CYCLE = 0.5% MAX

2.5

2.0

1.5

1.0

0.5

NORMALIZED ON RESISTANCE

0

-50 -25 0 25 50 75 100 150 175

VGS = 10V, ID = 7.5A

TJ, JUNCTION TEMPERATURE (oC)

Figure 3. Transfer Characteristics Figure 4. Normalized Drain To Source On

Resistance vs Junction Temperature

125

4000

1000

100

C, CAPACITANCE (pF)

V

= 0V, f = 1MHz

GS

10

1 10 100

C

ISS

C

OSS

C

RSS

VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 5. Capacitance vs Drain To Source

Voltage

©2003 Fairchild Semiconductor Corporation FDH15N50 / FDP15N50 / FDB15N50 RevD2

15

ID = 15A

12

9

6

3

100V

250V

400V

, GATE TO SOURCE VOLTAGE (V)

GS

V

0

0 10203040

50

Qg, GATE CHARGE (nC)

Figure 6. Gate Charge Waveforms For Constant

Gate Current

Page 4

Typical Characteristics

FDH15N50 / FDP15N50 / FDB15N50

30

25

20

15

10

5

TJ = 175oC

TJ = 25oC

, SOURCE TO DRAIN CURRENT (A)

SD

I

0

0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0

VSD, SOURCE TO DRAIN VOLTAGE (V)

Figure 7. Body Diode Forward Voltage vs Body

Diode Current

16

12

8

100

10

1.0

, DRAIN CURRENT (A)

D

I

OPERATION IN THIS AREA

LIMITED BY R

0.1

1 10 100 1000

DS(ON)

VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 8. Maximum Safe Operating Area

50

If R = 0

tAV = (L)(IAS)/(1.3*RATED BV

If R ≠ 0

t

= (L/R)ln[(IAS*R)/(1.3*RATED BV

AV

10

- VDD)

DSS

DSS

STARTING TJ = 25oC

- VDD) +1]

TC = 25oC

100µs

1ms

10ms

DC

4

, DRAIN CURRENT (A)

D

I

0

25 50 75 100 125 175

150

TC, CASE TEMPERATURE (oC)

Figure 9. Maximum Drain Current vs Case

Temperature

0

10

0.50

0.20

-1

10

0.10

0.05

0.02

, NORMALIZED THERMAL RESPONSE

0.01

JC

θ

-2

Z

10

10

-5

SINGLE PULSE

10

-4

-3

10

t1, RECTANGULAR PULSE DU R ATION (s)

Figure 11. Normalized Transient Thermal Impedance, Junction to Case

, AVALANCHE CURRENT (A)

AS

I

1

0.01 0.1 1 5010

STARTING TJ = 150oC

tAV, TIME IN AVALANCHE (ms)

Figure 10. Unclamped Inductive Switching

Capability

t

1

P

D

t

2

DUTY FACTOR, D = t1 / t

PEAK TJ = (PD X Z

-2

10

-1

10

10

X R

θ

JC

0

2

θJC

) + T

C

1

10

©2003 Fairchild Semiconductor Corporation FDH15N50 / FDP15N50 / FDB15N50 RevD2

Page 5

Test Circuits and Waveforms

FDH15N50 / FDP15N50 / FDB15N50

VARY t

TO OBTAIN

P

REQUIRED PEAK I

V

GS

V

DS

L

I

AS

R

AS

G

+

V

DD

-

BV

DSS

t

P

V

DS

DUT

t

0V

P

I

AS

0.01Ω

0

t

AV

Figure 12. Unclamped Energy Test Circuit Figure 13. Unclamped Energy Waveforms

V

I

g(REF)

DS

R

L

V

GS

+

V

DD

-

DUT

V

DD

V

0

I

g(REF)

0

GS

V

GS

= 1V

Q

g(TOT)

V

DS

Q

g(TH)

Q

gs

Q

gd

V

DD

V

= 10V

GS

Figure 14. Gate Charge Test Circuit Figure 15. Gate Charge Waveforms

V

DS

R

L

V

GS

R

GS

V

GS

DUT

+

V

DD

-

V

DS

0

V

GS

10%

0

t

d(ON)

90%

t

ON

50%

10%

t

r

PULSE WIDTH

t

d(OFF)

90%

t

OFF

50%

t

f

90%

10%

Figure 16. Switching Time Test Circuit Figure 17. Switching Time Waveform

©2003 Fairchild Semiconductor Corporation FDH15N50 / FDP15N50 / FDB15N50 RevD2

Page 6

TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not

intended to be an exhaustive list of all such trademarks.

ACEx™

ActiveArray™

Bottomless™

CoolFET™

CROSSVOLT™

DOME™

EcoSPARK™

2

CMOS™

E

EnSigna™

FACT™

FACT Quiet Series™

®

FAST

FASTr™

FRFET™

GlobalOptoisolator™

GTO™

HiSeC™

2

C™

I

Across the board. Around the world.™

The Power Franchise™

Programmable Active Droop™

ImpliedDisconnect™

ISOPLANAR™

LittleFET™

MicroFET™

MicroPak™

MICROWIRE™

MSX™

MSXPro™

OCX™

OCXPro™

OPTOLOGIC

®

OPTOPLANAR™

PACMAN™

POP™

Power247™

PowerTrench

QFET

®

®

QS™

QT Optoelectronics™

Quiet Series™

RapidConfigure™

RapidConnect™

SILENT SWITCHER

SMART START™

SPM™

Stealth™

SuperSOT™-3

SuperSOT™-6

SuperSOT™-8

SyncFET™

TinyLogic

TruTranslation™

UHC™

UltraFET

®

VCX™

®

®

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY

PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY

LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;

NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR

CORPORATION.

As used herein:

1. Life support devices or systems are devices or syst em s

which, (a) are intended for surgical implant into the body,

or (b) support or sustain life, or (c) whose failure to perform

when properly used in accordance with instructions for use

provided in the labeling, can be reasonably expected to

result in significant injury to the user.

2. A critical component is any component of a life support

device or system whose failure to perform can be

reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or In

Design

Preliminary First Production This datasheet contains preliminary data, and

No Identification Needed Full Production This datasheet contains final specifications. Fairchild

Obsolete Not In Production This datasheet contains specifications on a product

This datasheet contains the design specifications for

product development. Specifications may change in

any manner without notice.

supplementary data will be published at a later date.

Fairchild Semiconductor reserves the right to make

changes at any time without notice in order to improve

design.

Semiconductor reserves the right to make changes at

any time without notice in order to improve design.

that has been discontinued by Fairchild semiconductor.

The datasheet is printed for reference information only.

Rev. I3

Loading...

Loading...