Page 1

FDC37N972

ADVANCE INFORMATION

Ad vanced Notebook I/O Controller with Enhanced

Keyboard Control and System Management

FEATURES

!" 3.3V Operation With 5V Tolerant Buffers

!" ACPI 1.0 and PC99 Compliant

!" Three Power Planes

!" ACPI Embedded Controller Interface

!" Low Standby Current in Sleep Mode

!" Configuration Register Set Compatible With

ISA Plug-and-Play Standard (Version 1.0a)

!" Serial IRQ Interface Compatible With

Serialized IRQ Support for PCI Systems

!" Floppy Disk Interface on Parallel Port

!" 8051 Controller uses Parallel Port to

Reprogram the Flash ROM

!" Advanced Infrared Communications

Controller (IrCC 2.0)

- IrDA V1.1 (4Mbps), HPSIR, ASKIR,

Consumer IR Support

- Two IR Ports

- Relocatable Base I/O Address

!" 512k Byte Flash ROM Interface

- 8051/Host CPU Multiplexed Interface

- Sixteen 32K Pages - 8051 Keyboard

BIOS

- Eight 64K Pages - Host System BIOS

- Embedded Controller uses Parallel Port

to Reprogram Flash ROM

!" ISA Host Interface With Clock Run Support

and ACPI SCI Interface

- 16 Bit Address Qualification

- 8 Bit Data Bus

- Zero Wait-State I/O Register Access

- Shadowed Write Only registers

- IOCHRDY for ECP, IRCC 2.0 and Flash

Cycles

- 15 Direct IRQs Including nSMI

- Four 8 Bit DMA Channels

- XNOR Test Chain

!"High-Performance Embedded 8051

Keyboard and System Controller

- Provides System Power Management

- System Watch Dog Timer (WDT)

- 8042 Style Host Interface

- Asynchronous Access to Two Data

Registers and One Status Register

- Supports Interrupt and Polling Access

- 2K Internal ROM, nEA Pin Select

- 32K Bank Switchable External Flash

ROM Interface

- 256 Bytes Data RAM

- On-Chip Control Registers Available via

MOVX External Data Access Commands

- Access to RTC and CMOS Registers

- Up to 16x8 Keyboard Scan Matrix

- Three 16 Bit Timer/Counters

- Integrated TX/RX Serial Interface

- Eleven 8051 Interrupt Sources

- Thirty-Two 8 Bit, Host/8051 Mailbox

Registers

- Thirty Maskable Hardware Wake-Up

Events Supported

- Fast GATEA20

- Fast CPU_RESET

- Multiple Clock Sources and Frequencies

- IDLE and SLEEP Modes

- Fail-Safe Ring Oscillator

!"Real Time Clock

- MC146818 and DS1287 Compatible

- 256 Bytes of Battery Backed CMOS in

Two 128-Byte Banks

- 128 Bytes of CMOS RAM Lockable in

4x32 Byte Blocks

- 12 and 24 Hour Time Format

- Binary and BCD Format

Page 2

- <2!A Standby Current (typ)

!"

Two 8584-Style ACCESS.bus Controllers

!"

Four independent Hardware Driven PS/2

Ports

!"

General Purpose I/O

- 22 I/O Pins

- 12 Out Pins

- Eight In Pins

!"

Two Programmable Pulse-Width Modulator

Outputs

- Independent Clock Rates

- 6 Bit Duty Cycle Granularity

- VCC1 and VCC2 operation mode

!"

Intelligent Auto Power Management

!"

2.88MB Super I/O Floppy Disk Controller

- Relocatable to 480 Different Base I/O

Addresses

- 15 IRQ Options

- Four DMA Options

- Open-Drain/Push-Pull Configurable

Output Drivers

- Licensed CMOS 765B Floppy Disk

Controller

- Advanced Digital Data Separator

- Software and Register Compatible With

SMSC's Proprietary 82077AA Compatible

Core

- Low Power CMOS Design with

Sophisticated Power Control Circuitry

(PCC) Including Multiple Powerdown

Modes for Reduced Power Consumption

- Supports Two Floppy Drives on the FDD

Interface and Two Floppy Drives on the

Parallel Port Interface

- 12 mA FDD Interface Cable Drivers With

Schmitt Trigger Inputs

!"

Licensed CMOS 765B Floppy Disk Controller

Core

- Supports Vertical Recording Format

- 16-Byte Data FIFO

- 100% IBM Compatibility

- Detects All Overrun and Underrun

Conditions

- 12 mA Drivers and Schmitt Trigger Inputs

- DMA Enable Logic

- Data Rate and Drive Control Registers

!"

Enhanced Digital Data Separator

- Low Cost Implementation

- No Filter Components Required

- 2 Mbps, 1 Mbps, 500 Kbps, 300 Kbps,

250 Kbps Data Rates

- Programmable Precompensation Modes

!"

Multi-Mode Parallel Port with ChiProtect

- Standard Mode IBM PC/XT, PC/AT, and

PS/2 Compatible Bi-directional Parallel

Port

- Enhanced Parallel Port EPP 1.7 and EPP

1.9 Compatible (IEEE 1284 Compliant)

IEEE 1284 Compliant Enhanced

Capabilities Port (ECP)

- ChiProtect Circuitry to Prevent Printer

Power-On Damage

- Relocatable to 480 Different Base I/O

Addresses

- 15 IRQ Options

- 4 DMA Options

- Microsoft and HP compatible High Speed

Mode

- 12 mA Output Drivers

!"

Serial Port

- High-Speed NS16550A-Compatible

UART with 16-Byte Send/Receive FIFOs

- Programmable Baud Rate Generator

Modem Control Circuitry Including 230k

and 460k Baud

- Relocatable to 480 Different Base I/O

Addresses

- 15 IRQ Options

!"

208 Pin TQFP Package Options

!"

208 Pin FBGA Package Options

2

Page 3

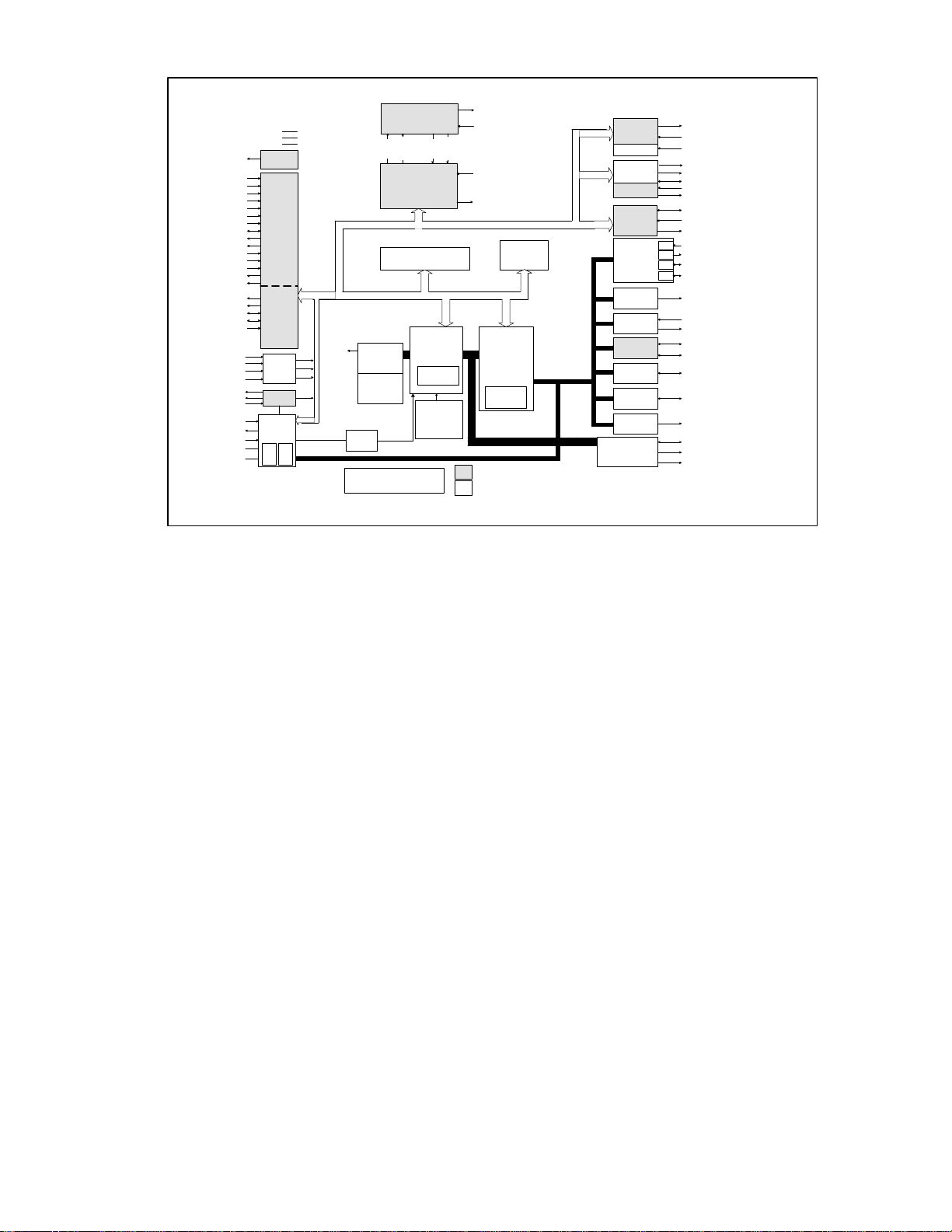

GENERAL DESCRIPTION

The FDC37N972 is a 208-pin 3.3V ISA Host

ACPI 1.0 and PC98 (/PC99)-compliant Ultra I/O

Controller with Fast Infrared for mobile

applications.

The FDC37N972 incorporates a highperformance 8051-based keyboard controller; a

512k byte Flash ROM interface; four PS/2 ports;

a real-time clock; SMSC's true CMOS 765B

floppy disk controller with advanced digital data

separator and 16-byte data FIFO; an

NS16C550A-compatible UART, SMSC’s

advanced Infrared Communications Controller

(IrCC 2.0) with a UART and a Synchronous

Communications Engine to provide IrDA v1.1

(Fast IR) capabilities; one Multi-Mode parallel

port with ChiProtect circuitry plus EPP and ECP

support; two 8584-style Access Bus controllers;

a Serial IRQ peripheral agent interface; an ACPI

Embedded Controller Interface; General

Purpose I/O pins; two independently

programmable pulse width modulators; twofloppy direct drive support; and maskable

hardware wake-up events.

The true CMOS 765B core provides 100%

compatibility with IBM PC/XT and PC/AT

architectures in addition to providing data

overflow and underflow protection. The SMSC

advanced digital data separator incorporates

SMSC's patented data separator technology,

allowing for ease of testing and use.

The parallel port is compatible with IBM PC/AT

architecture, as well as EPP and ECP. The

8051 controller can also take control of the

parallel port interface to provide remote

diagnostics or “Flashing” of the Flash memory.

The FDC37N972 has three separate power

planes to provide “instant on” and system power

management functions. Additionally, the

FDC37N972 incorporates sophisticated power

control circuitry (PCC). The PCC supports

multiple low power down modes. Wake-up

events and ACPI-related functions are supported

through the SCI Interface.

The FDC37N972’s configuration register set is

compatible with the ISA Plug-and-Play Standard

(Version 1.0a) and provides the functionality to

support Windows '95. Through internal

configuration registers, each of the

FDC37N972's logical device's I/O address, DMA

channel and IRQ channel may be programmed.

There are 480 I/O address location options, 15

IRQ options, and four DMA channel options for

each logical device.

The FDC37N972 does not require any external

filter components and is, therefore, easy to use

and offers lower system cost and reduced board

area. The FDC37N972 is software and register

compatible with SMSC's proprietary 82077AA

core.

3

Page 4

TABLE OF CONTENTS

FEATURES.......................................................................................................................................1

GENERAL DESCRIPTION................................................................................................................3

PIN CONFIGURATION......................................................................................................................9

DESCRIPTION OF PIN FUNCTIONS..............................................................................................11

FUNCTIONAL DESCRIPTION.........................................................................................................28

FLOPPY DISK CONTROLLER........................................................................................................30

FDC INTERNAL REGISTERS......................................................................................................30

STATUS REGISTER ENCODING................................................................................................44

FDC RESET.................................................................................................................................46

FDC MODES OF OPERATION....................................................................................................47

DMA TRANSFERS.......................................................................................................................47

CONTROLLER PHASES.................................................................................................................47

FDC INSTRUCTION SET.............................................................................................................53

FDC DATA TRANSFER COMMANDS..........................................................................................64

ACPI EMBEDDED CONTROLLER..................................................................................................82

ECI CONFIGURATION REGISTERS............................................................................................83

SERIAL PORT (UART)....................................................................................................................86

FIFO INTERRUPT MODE OPERATION.......................................................................................97

FIFO POLLED MODE OPERATION.............................................................................................97

INFRARED COMMUNICATIONS CONTROLLER (IRCC 2.0).........................................................102

OVERVIEW................................................................................................................................103

IRRX/IRTX PIN ENABLE.............................................................................................................104

IR REGISTERS - LOGICAL DEVICE 5........................................................................................104

IR DMA CHANNELS...................................................................................................................105

S.......................................................................................................................................105

IR IRQ

IR HALF DUPLEX TIMEOUT.......................................................................................................106

IRTX OUTPUT PINS DEFAULT...................................................................................................106

PARALLEL PORT.......................................................................................................................106

THE PARALLEL PORT PHYSICAL INTERFACE (PPPI)..............................................................128

PARALLEL PORT FDC INTERFACE...........................................................................................129

AUTO POWER MANAGEMENT.....................................................................................................131

SYSTEM POWER MANAGEMENT.............................................................................................131

DSR FROM POWERDOWN.......................................................................................................132

WAKE UP FROM AUTO POWERDOWN....................................................................................132

REGISTER BEHAVIOR...............................................................................................................132

PIN BEHAVIOR...........................................................................................................................132

SYSTEM INTERFACE PINS........................................................................................................133

4

Page 5

FDD INTERFACE PINS...............................................................................................................134

UART POWER MANAGEMENT..................................................................................................135

PARALLEL PORT POWER MANAGEMENT................................................................................135

8051 EMBEDDED CONTROLLER .................................................................................................136

8051 FUNCTIONAL OVERVIEW.................................................................................................136

POWERING UP OR RESETTING THE 8051...............................................................................137

CPU RESET SEQUENCE...........................................................................................................140

8051 CLOCK CONTROLS ..........................................................................................................142

8051 RING OSCILLATOR FAIL-SAFE CONTROLS ....................................................................144

8051 MEMORY MAP...................................................................................................................145

FLASH ROM INTERFACE...........................................................................................................152

8051 CONTROL REGISTERS.....................................................................................................153

8051 CONFIGURATION/CONTROL MEMORY MAPPED REGISTERS .........................................162

8051 INTERRUPTS.....................................................................................................................165

WATCH DOG TIMER.....................................................................................................................183

WDT OPERATION......................................................................................................................183

WDT ACTION.............................................................................................................................183

WDT ACTIVATION .....................................................................................................................183

WDT RESET MECHANISM .........................................................................................................183

WDT MEMORY MAPPED REGISTERS ......................................................................................184

SHARED FLASH INTERFACE.......................................................................................................185

FLASH INTERFACE DIAGRAM...................................................................................................185

SYSTEM MEMORY MAP............................................................................................................186

KEYBOARD BIOS (KMEM).........................................................................................................187

SYSTEM BIOS (HMEM)..............................................................................................................189

HOST FLASH ACCESS ..............................................................................................................189

IDLE MODE................................................................................................................................195

SLEEP MODE.............................................................................................................................197

WAKE-UP EVENTS....................................................................................................................201

8042 STYLE HOST INTERFACE.................................................................................................204

KEYBOARD DATA WRITE..........................................................................................................204

8051- TO- HOST KEYBOARD COMMUNICATION......................................................................205

HOST-TO 8051 KEYBOARD COMMUNICATION........................................................................206

GATEA20 HARDWARE SPEED-UP............................................................................................208

SMSC PS/2 LOGIC OVERVIEW.................................................................................................217

SMSC PS/2 MEMORY MAPPED CONTROL REGISTERS ..........................................................218

DEVIL LOGIC OVERVIEW..........................................................................................................225

THE DEVIL PS/2 LOGIC COMMANDS........................................................................................225

DEVIL PS/2 MEMORY MAPPED CONTROL REGISTERS..........................................................227

5

Page 6

ACCESS.BUS................................................................................................................................233

BACKGROUND ..........................................................................................................................233

REGISTER DESCRIPTION.........................................................................................................234

ACCESS.BUS INTERFACE DESCRIPTION................................................................................238

MEMORY MAPPED CONTROL REGISTERS..............................................................................239

SECOND I2C BUS INTERFACE .....................................................................................................241

MEMORY MAPPED CONTROL REGISTERS..............................................................................241

I2C CLOCK DIVIDER BIT............................................................................................................243

OVERVIEW................................................................................................................................244

MAILBOX REGISTERS INTERFACE BASE ADDRESS...............................................................246

MAILBOX REGISTERS...............................................................................................................247

THE SYSTEM/8051 INTERFACE REGISTERS`..........................................................................247

LED CONTROLS........................................................................................................................249

PULSE WIDTH MODULATORS..................................................................................................250

OPERATION REGISTERS..........................................................................................................257

GENERAL PURPOSE I/O (GPIO)..................................................................................................260

OVERVIEW................................................................................................................................266

MULTIPLEXING_1 REGISTER ...................................................................................................266

MULTIPLEXING_2 REGISTER ...................................................................................................270

MULTIPLEXING_3 REGISTER ...................................................................................................272

ACPI PM1 BLOCK.........................................................................................................................276

ACPI PM1 BLOCK OVERVIEW...................................................................................................276

ACPI PM1 BLOCK SCI EVENT-GENERATING FUNCTIONS ......................................................276

ACPI PM1 BLOCK BASE ADDRESS ...........................................................................................277

ACPI PM1 BLOCK ......................................................................................................................278

REGISTERS...............................................................................................................................278

REAL TIME CLOCK.......................................................................................................................283

GENERAL DESCRIPTION..........................................................................................................283

CONFIGURATION REGISTERS.................................................................................................283

ISA HOST I/O INTERFACE .........................................................................................................284

INTERNAL REGISTERS.............................................................................................................285

TIME CALENDAR AND ALARM ..................................................................................................286

UPDATE CYCLE .........................................................................................................................287

CONTROL AND STATUS REGISTERS.......................................................................................288

INTERRUPTS.............................................................................................................................292

FREQUENCY DIVIDER...............................................................................................................292

32KHZ CLOCK INPUT.................................................................................................................295

POWER MANAGEMENT ............................................................................................................295

6

Page 7

PCI CLOCK RUN SUPPORT..........................................................................................................295

OVERVIEW................................................................................................................................295

SERIAL INTERRUPTS...................................................................................................................298

SERIRQ MODE BIT FUNCTION .................................................................................................299

FDC37N972 CONFIGURATION ....................................................................................................303

OVERVIEW................................................................................................................................303

CONFIGURATION REGISTER ACCESS.....................................................................................303

CHIP LEVEL (GLOBAL) CONTROL/CONFIGURATION REGISTERS [0X00-0X2F].....................308

LOGICAL DEVICE CONFIGURATION/CONTROL REGISTERS [0X30-0XFF].............................311

I/O BASE ADDRESS CONFIGURATION REGISTER DESCRIPTION ..........................................313

INTERRUPT SELECT CONFIGURATION REGISTER DESCRIPTION........................................315

DMA CHANNEL SELECT CONFIGURATION REGISTER DESCRIPTION...................................316

IRQ AND DMA ENABLE AND DISABLE......................................................................................317

SMSC DEFINED LOGICAL DEVICE CONFIGURATION REGISTERS.........................................318

ELECTRICAL SPECIFICATIONS...................................................................................................327

MAXIMUM GUARANTEED RATINGS*........................................................................................327

DC SPECIFICATIONS ................................................................................................................328

AC SPECIFICATIONS.................................................................................................................332

TIMING DIAGRAMS ......................................................................................................................333

LOAD CAPACITANCE ................................................................................................................333

FAST GATEA20 IOW TIMING.....................................................................................................334

ISA IO WRITE ............................................................................................................................335

ISA IO READ CYCLE..................................................................................................................336

DMA TIMING (BURST TRANSFER MODE) .................................................................................340

FLOPPY DISK DRIVE TIMING (AT MODE).................................................................................341

SERIAL PORT TIMING...............................................................................................................342

PARALLEL PORT TIMING..........................................................................................................343

EPP 1.9 DATA OR ADDRESS WRITE CYCLE............................................................................344

EPP 1.9 DATA OR ADDRESS READ CYCLE ..............................................................................346

EPP 1.7 DATA OR ADDRESS WRITE CYCLE............................................................................348

EPP 1.7 DATA OR ADDRESS READ CYCLE ..............................................................................350

ECP PARALLEL PORT TIMING..................................................................................................351

ACCESS.BUS TIMING................................................................................................................355

HOST FLASH READ TIMING......................................................................................................356

HOST FLASH READ/WRITE.......................................................................................................358

ZERO WAIT STATE (NOWS) TIMING........................................................................................360

FLASH PROGRAM FETCH TIMING ............................................................................................361

8051 FLASH READ TIMING ........................................................................................................362

8051 FLASH WRITE TIMING......................................................................................................363

7

Page 8

EPP 1.7 DATA OR ADDRESS READ CYCLE.............................................................................353

ECP PARALLEL PORT TIMING..................................................................................................354

ACCESS.BUS TIMING..................................................................................................................358

HOST FLASH READ TIMING......................................................................................................359

HOST FLASH READ/WRITE.......................................................................................................361

ZERO WAIT STATE (NOWS) TIMING.......................................................................................363

FLASH PROGRAM FETCH TIMING...........................................................................................364

8051 FLASH READ TIMING........................................................................................................365

8051 FLASH WRITE TIMING......................................................................................................366

PS/2 CHANNEL RECEIVE TIMING DIAGRAM ........................................................................367

PS/2 CHANNEL TRANSMIT TIMING DIAGRAM.....................................................................369

PS/2 CHANNEL “BIT-BANG” TIMING......................................................................................371

IN CIRCUIT TEST (ICT)................................................................................................................373

APPENDIX A...................................................................................................................................377

HIGH-PERFORMANCE 8051 CYCLE TIMING AND INSTRUCTION SET.............................377

APPENDIX B...................................................................................................................................382

HIGH PERFORMANCE 8051 EXTENDED INTERRUPT UNIT................................................382

8

Page 9

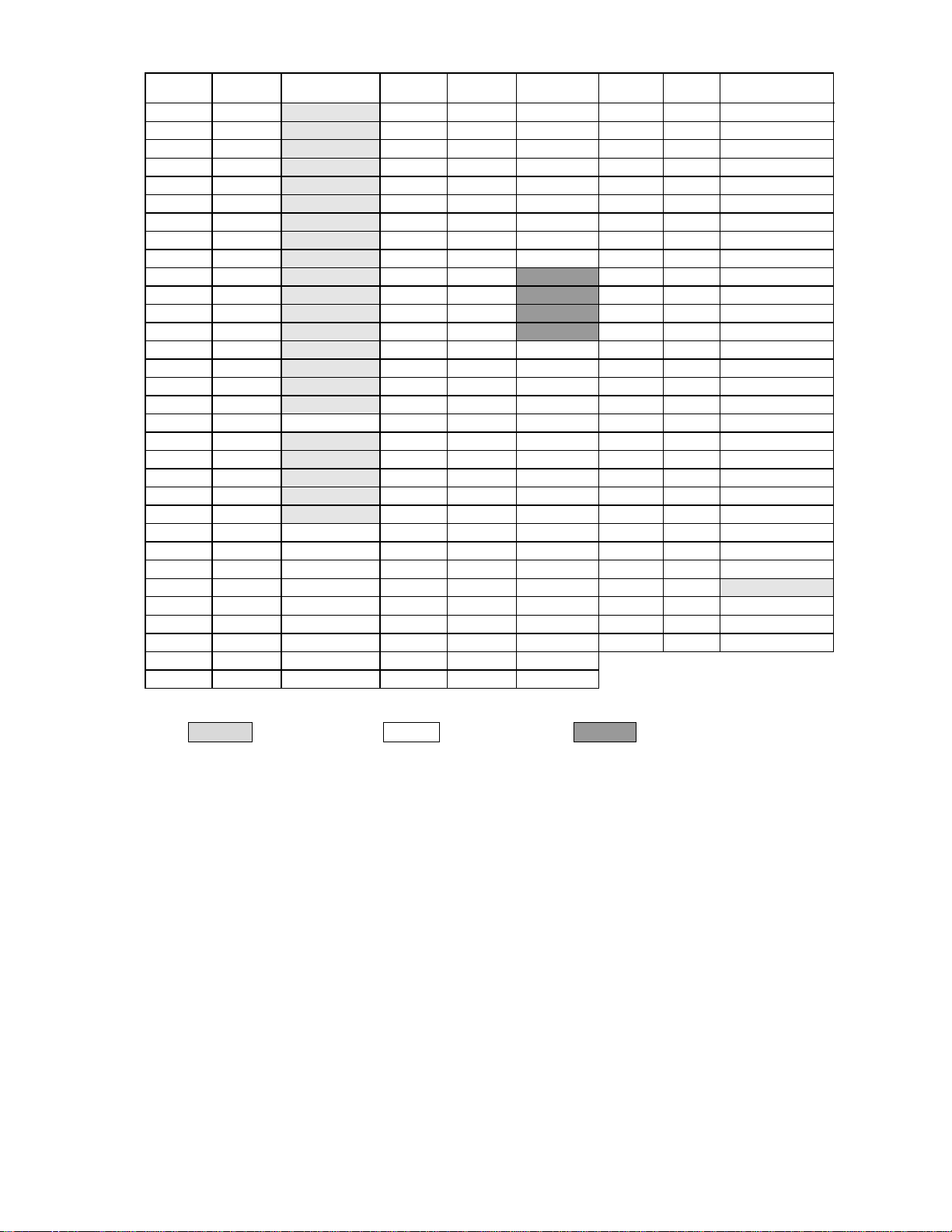

IN5

OUT5

OUT6

DRVDEN0

DRVDEN1

nMTR0

nDS0

nDIR

nSTEP

nWDATA

nWGATE

nHDSEL

nINDEX

nTRK0

nRDATA

nDSKCHG

KSO13

KSO12

KSO11

KSO10

KSO9

KSO8

KSO7

VCC1

KSO6

KSO5

KSO4

KSO3

KSO2

KSO1

KSO0

IN6

IN7

VCC0

IN1

IN2

IN3

IN4

GPIO10

GPIO11

GPIO12

IN0

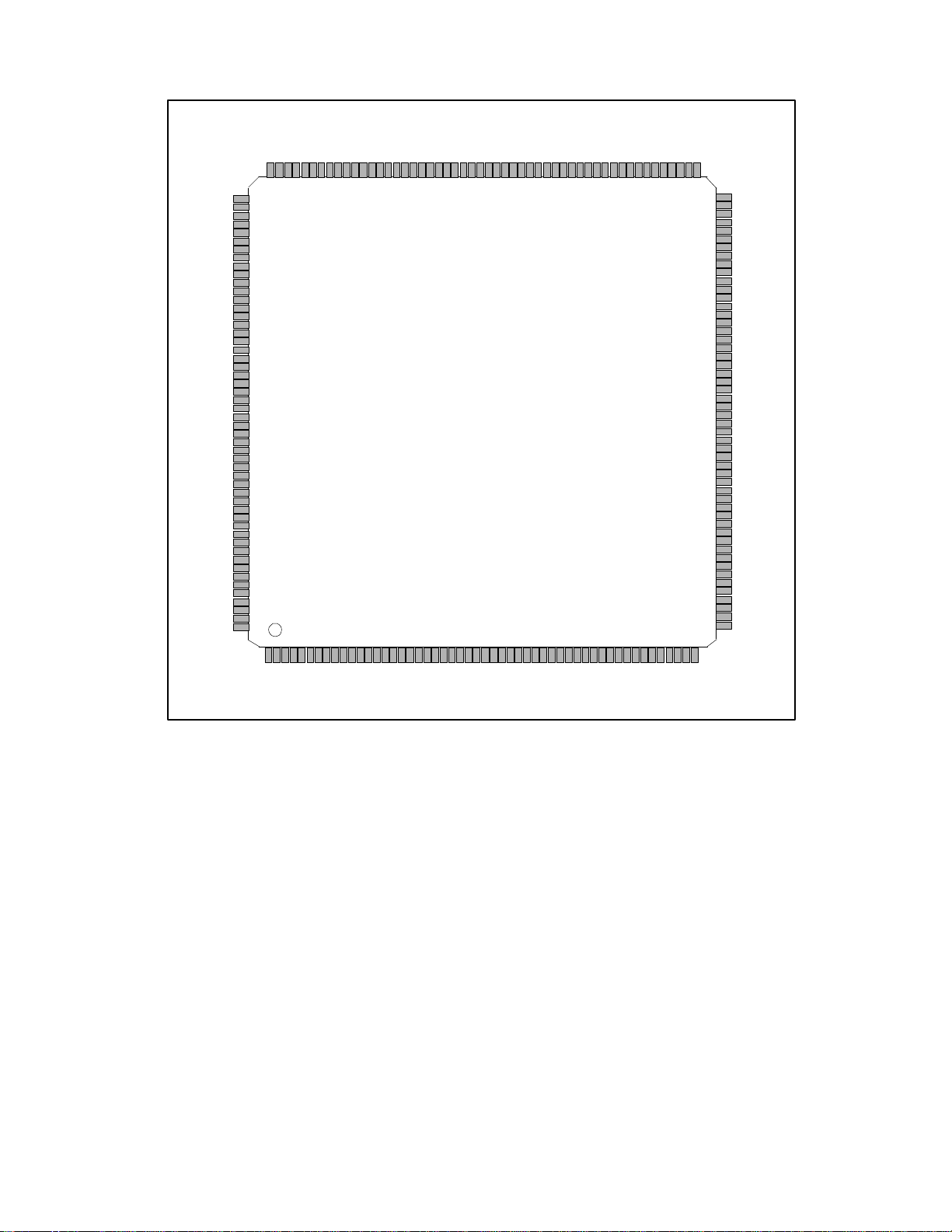

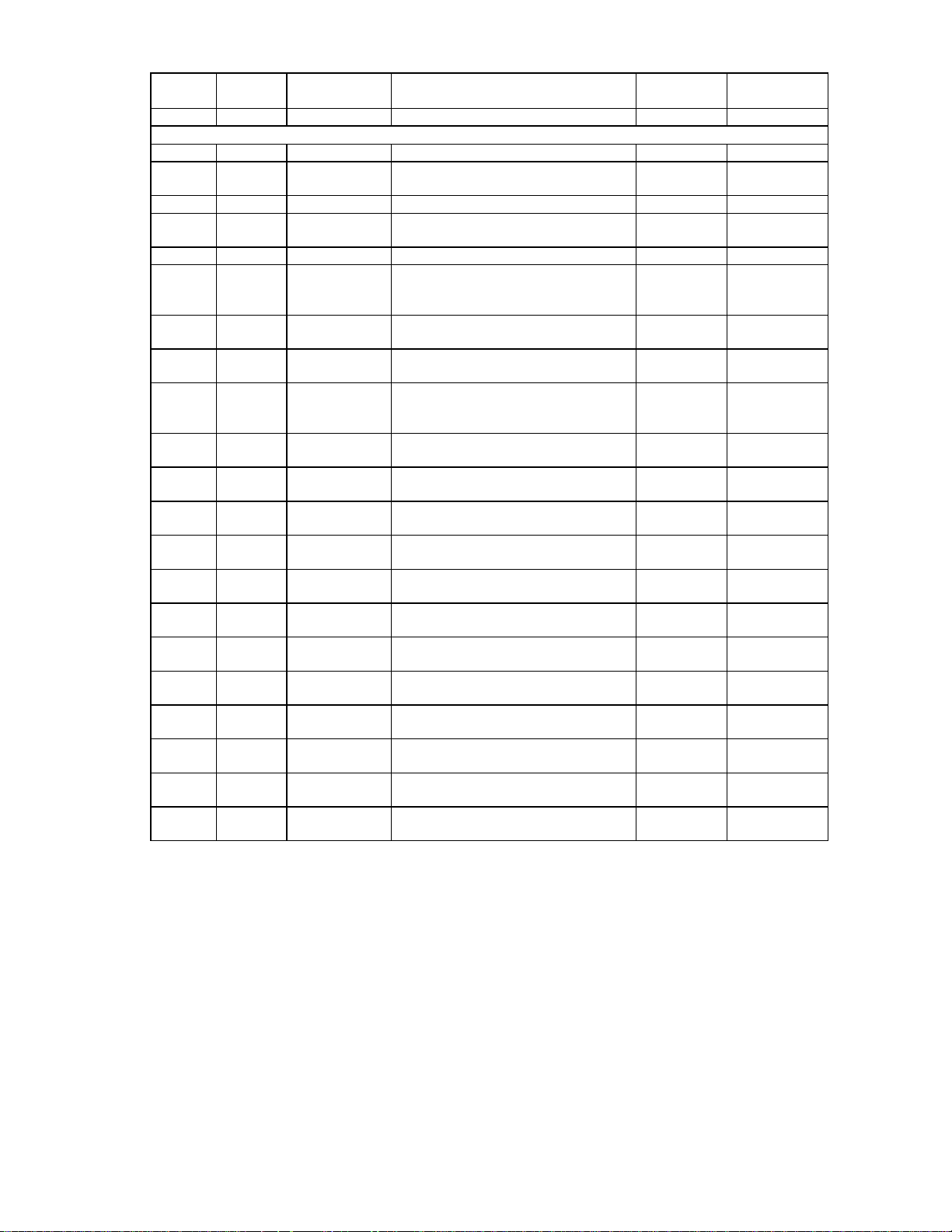

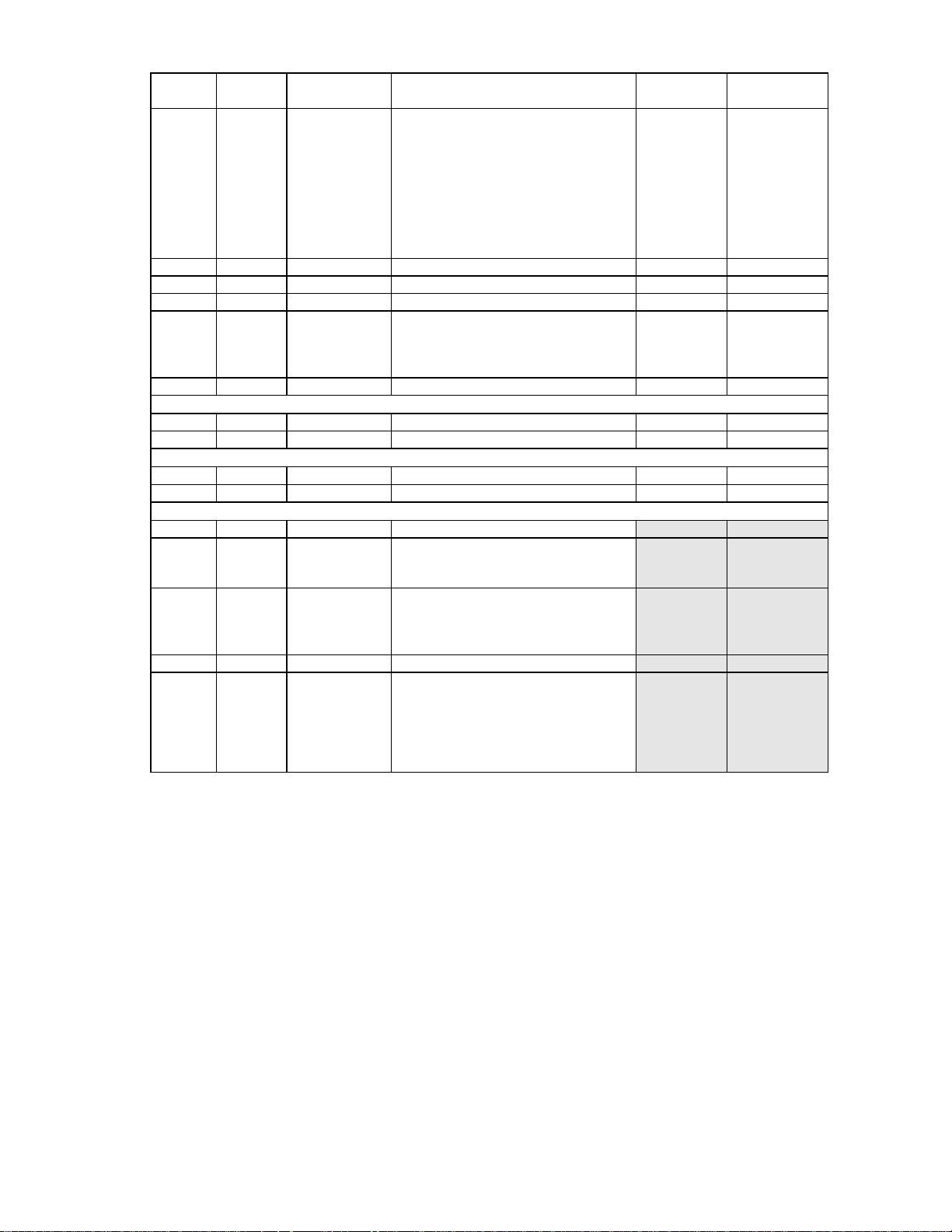

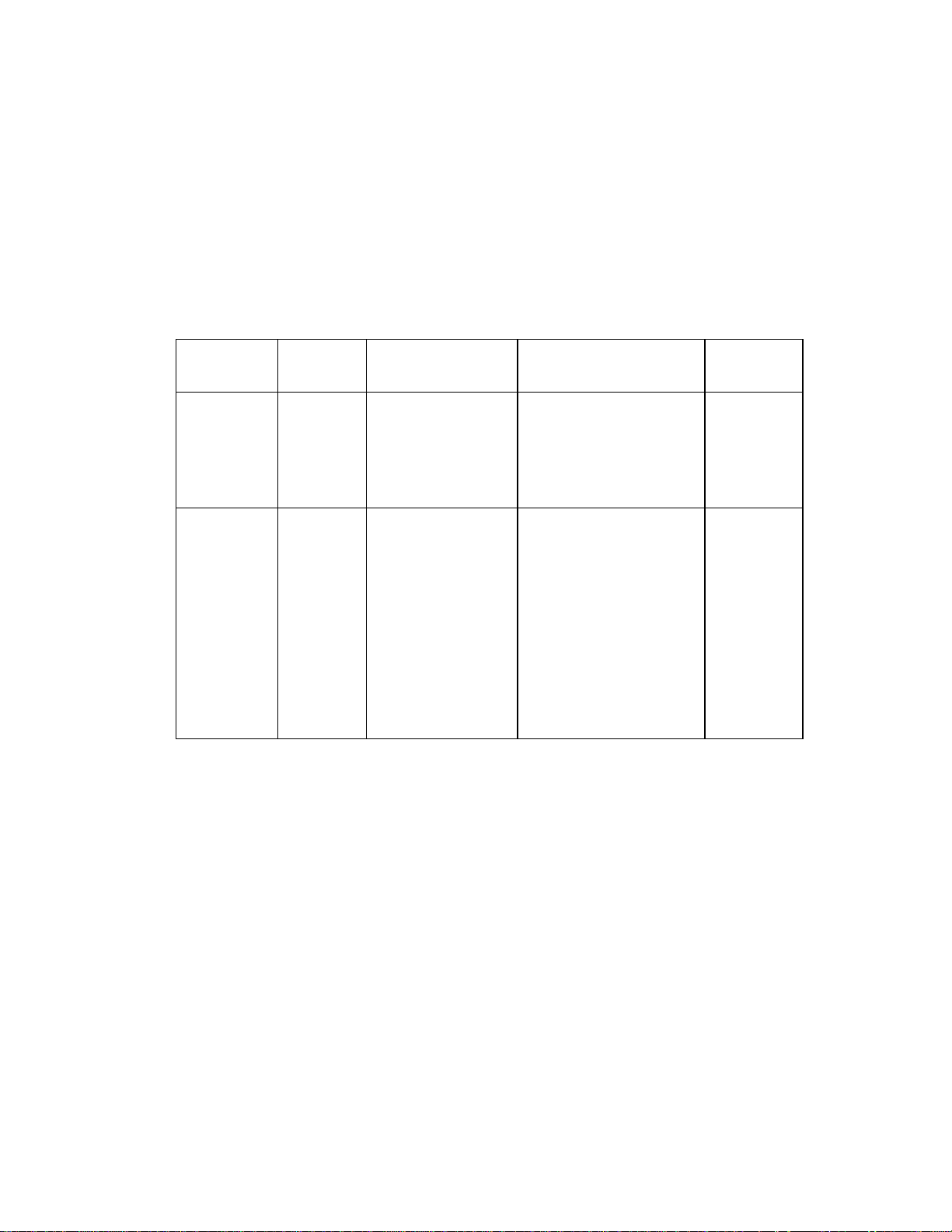

PIN CONFIGURATION

GPIO15

GPIO14

GPIO8

GPIO9

VCC1

FA18

nDCD

nRI

nDTR

nCTS

nDSR

TXD

nRTS

VSS

nERROR

nALF

RXD

nSTROBE

PD1

PD0

nSLCTIN

nINIT

PD5

PD4

PD3

PD2

VCC2

PD7

PD6

BUSY

nACK

VCC1_PWRGD

PWRGD

PE

nPWR_LED

SLCT

32kHz_OUT

24MHz_OUT

nEC_SCI

VSS

XOSEL

XTAL1

XTAL2

AGND

FAD0

FAD1

FAD2

FAD3

FAD4

FAD5

VSS

FAD6

FAD7

FA8

FA9

FA10

FA11

FA12

FA13

VCC1

FA14

FA15

FA16

FA17

FALE

nFRD

nFWR

nFCS

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

VSS

nEA

MODE

AB1_DATA

AB1_CLK

nBAT_LED

nFDD_LED

OUT11

OUT10

OUT9

OUT8

OUT7

GPIO16

VCC2

GPIO17

GPIO18

GPIO19

155

153

154

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

123467891011121314151617181920222324252627282930313233343536373839404142434445464748495051

147

148

149

150

151

152

5

141

142

143

144

145

146

FDC37N972

208 PIN TQFP

135

136

137

138

139

140

21

129

130

131

132

133

134

123

124

125

126

127

128

117

118

119

120

121

122

111

112

113

114

115

116

105

106

107

108

109

110

VCC2

104

CLOCKI

103

nRESET_OUT

102

SER_IRQ

101

nCLKRUN

100

PCI_CLK

99

nMEMWR

98

nMEMRD

97

nROMCS

96

IOCHRDY

95

TC

94

DRQ1

93

nDACK1

92

DRQ0

91

nDACK0

90

VSS

89

SD7

88

SD6

87

SD5

86

SD4

85

SD3

84

VCC2

83

SD2

82

SD1

81

SD0

80

AEN

79

nIOW

78

nIOR

77

nNOWS

76

OUT4

75

OUT3

74

VSS

73

OUT2

72

nIRQ8

71

OUT0

70

SA15

69

SA14

68

SA13

67

SA12

66

SA11

65

SA10

64

SA9

63

SA8

62

SA7

61

SA6

60

SA5

59

SA4

58

SA3

57

SA2

56

SA1

55

SA0

54

EMDAT

53

52

VSS

VSS

nWRTPRT

FPD

IRTX

IRRX

KSI7

KSI6

KSI5

KSI4

KSI3

KSI2

KSI1

GPIO20

GPIO21

KSI0

VSS

IMCLK

IMDAT

EMCLK

KCLK

KDAT

FIGURE 1 - FDC37N972 PIN CONFIGURATION

For FBGA BALL PAD Configuration refer to FIGURE 81 on Page 372.

9

Page 10

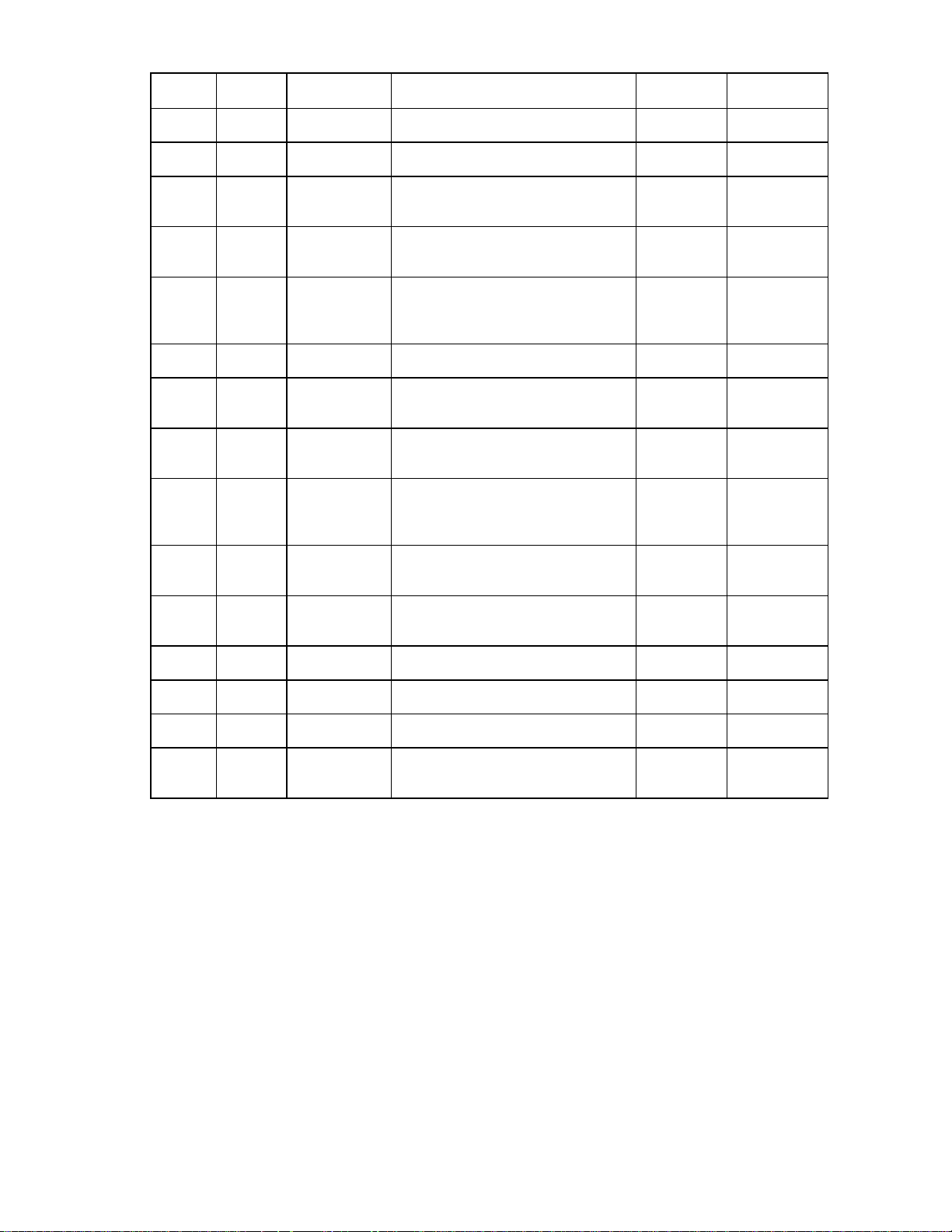

nRESET_OUT

nIOR

nIOW

nMEMRD

nMEMWR

nROMCS

SA[0:15]

SD[0:7]

DRQ[0:1]

DRQ[2:3]*

nDACK[0:1]

nDACK[2:3]*

nNOWS

IOCHRDY

nIRQ8*

nSMI*

SER_IRQ

nCLKRUN

PCI_CLK

MODE

VCC1_PWRGD

PWRGD

32KHz_OUT

24MHz_OUT

CLOCKI

(14.318 MHz)

XOSEL

XTAL2

XTAL1

VCC0

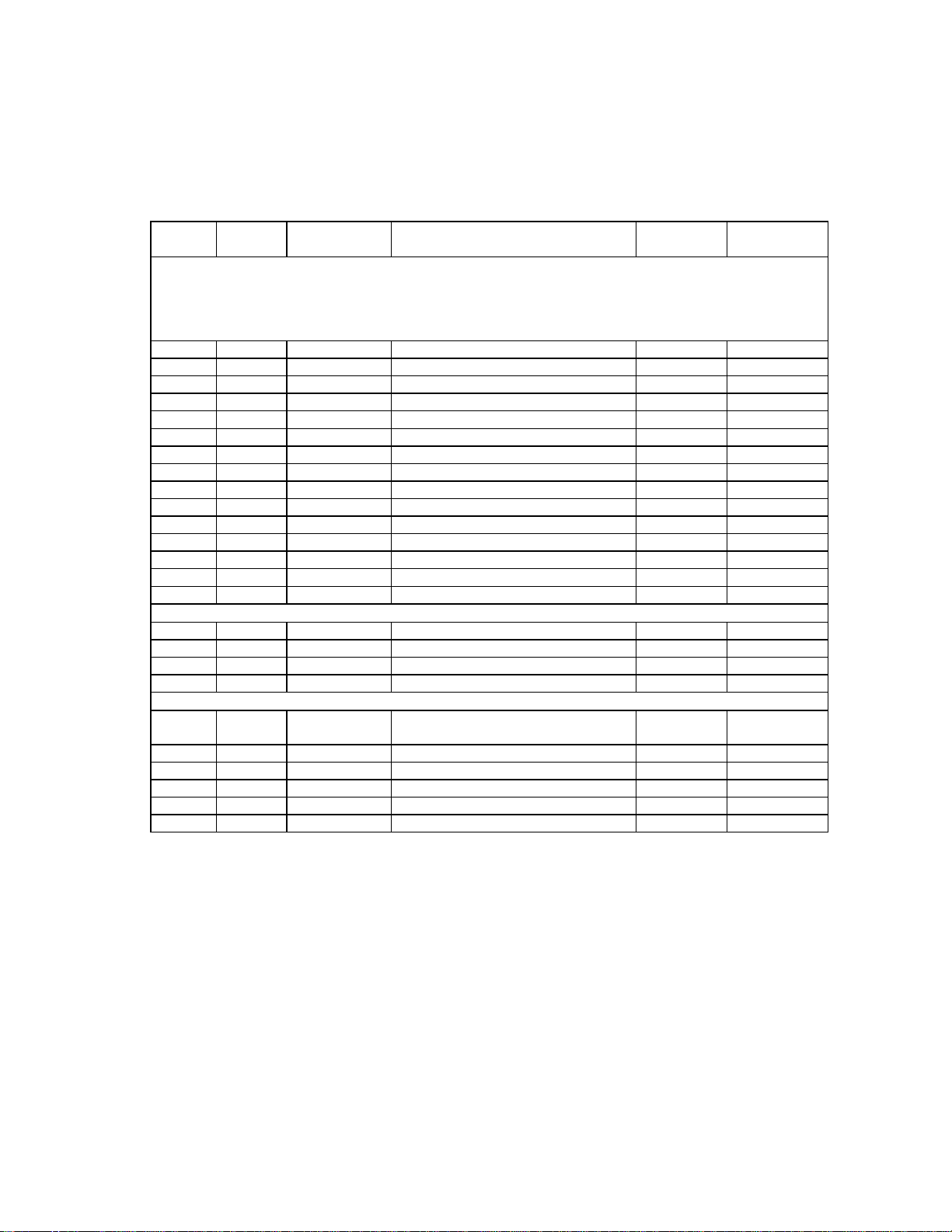

AGND

DIGITAL DATA

SEPARATOR

WITH WRITE

VCC1(3)

VCC2(4)

VSS(9)

SYSTEM

RESET

AEN

HOST

CPU

TC

INTERFACE

INTERRUPTS

nEA

CONTROL

INPUTS

PLL CLOCK

GENERATOR

RTC

2 x 128 BYTE

BANKS OF

CMOS RAM

BANK

1

nEC_SCI

BANK

2

PRECOMPENSATION

MDATA

MCLOCK

SMSC

PROPRIETARY

82077 COMPATIBLE

VERTICAL FLOPPY DISK

CONTROLLER CORE

CONFIGURATION REGISTERS

CONTROL, ADDRESS, DATA

ACPI

EMBEDDED

CONTROLLER

PM1

BLOCK

256B Direct

w/ FAIL SAFE

WDT

* -- ALTERNATE FUNCITON

RDATA

8051

Oscillator

nWDATA

nRDATA

RCLOCK

nDSKCHG, nWRTPRT,

nTRK0, nINDEX, FPD, nTRK0

nWGATE, nHDSEL, nDIR,

nSTEP, nDS0, nDS1*, nMTR0,

nMTR1*, DRVDEN0, DRVDEN1*,

FPD

POWER

MANAGEMENT

MAILBOX

REGISTERS

8051

SUB-BLOCK

EXTERNAL

RAM

Ring

CONTROL

REGISTERS

256B

EXTERNAL

8051 RAM

16C550

COMPATIBLE

SERIAL PORT 1

INFRARED

MULTI-MODE

PARALLEL

PORT / FDC

MUX

GENERAL

PURPOSE I/O

INTERFACE

LED

DRIVER

16 x 8

KEYBOARD

INTERFACE

PS/2

PORTS

ACCESS

BUS

ACCESS

BUS2

PWM

FLASH

VCC2 POWERED

VCC1 POWERED

INTERFACE

TXD, nRTS, nDTR

RXD, nCTS, nDSR, nDCD

nRI

IRRX*

IRRX2

IRMODE / IRRX3A, IRMODE / IRRX3B

IRTX*

IRTX2

PD[0:7]

BUSY, SLCT, PE, nERROR, nACK

nSLCTIN, nINIT, nALF, nSTROBE

IN0-7

IN

OUT0-11

OUT

GPIO 16-21

I/O

GPIO 0-15

I/O

nBAT_LED, nPWR_LED, nFDD_LED

KSI[0:7]

KS0[0:13], KS0[14:15]*

KCLK, EMCLK, IMCLK, PS2CLK

KDAT, EMDAT, IMDAT, PS2DAT

AB_DATA, AB_CLK

AB2_DATA *, AB2_CLK *

PWM0*, PWM1*

FAD[0:7]

FA[8:18], nFRD, nFWR, FALE

nFCS

FDC37N97x

(TIKKI)

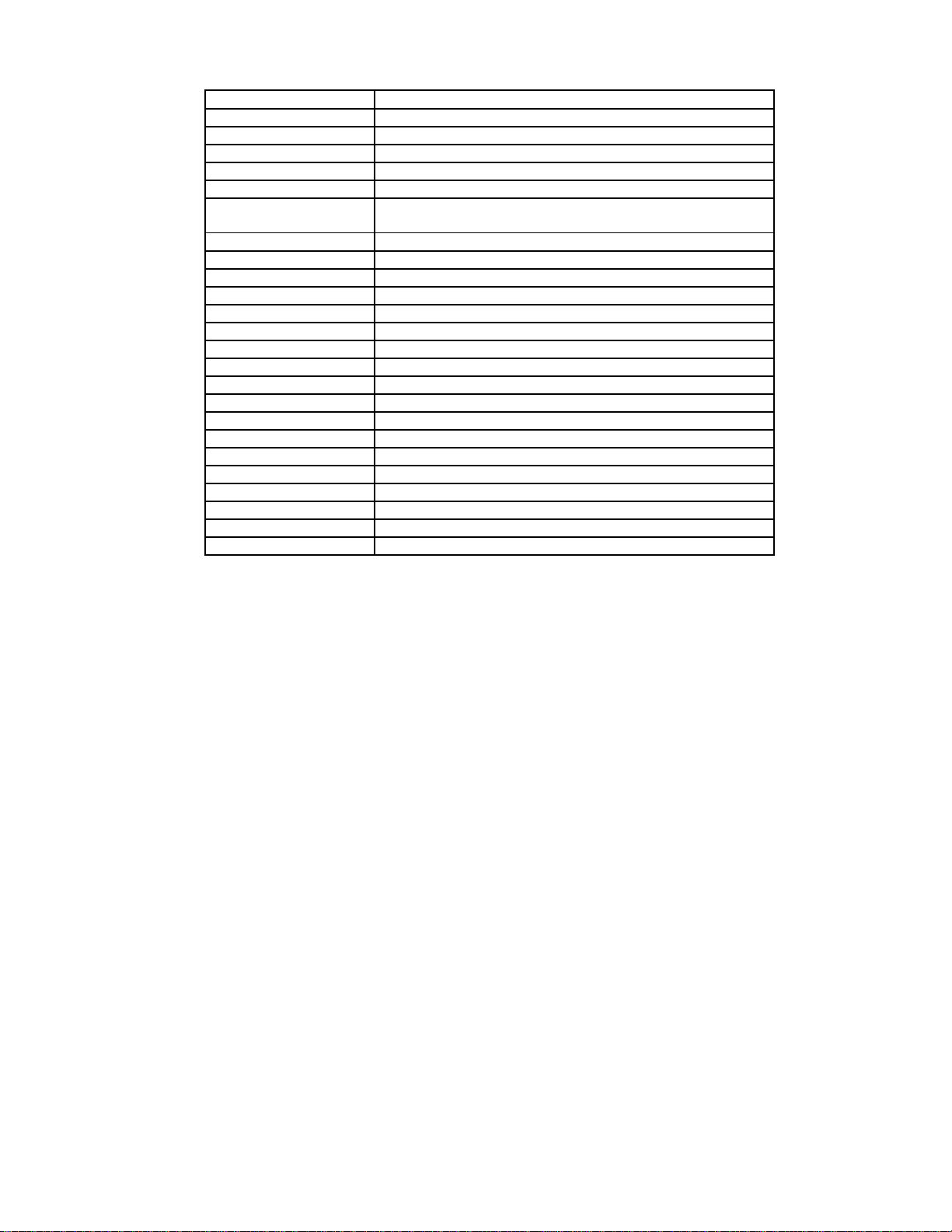

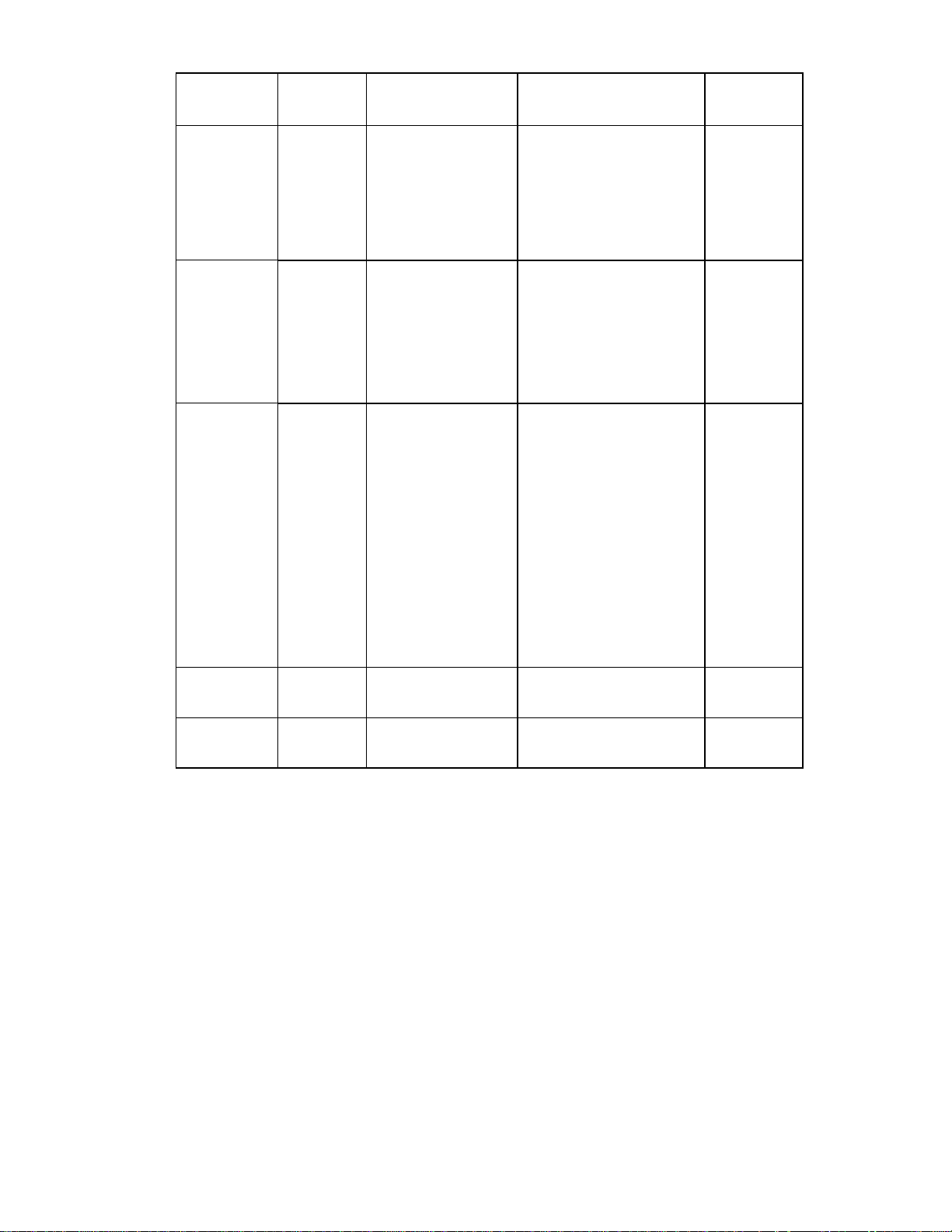

FIGURE 2 - FDC37N972 BLOCK DIAGRAM

10

Page 11

DESCRIPTION OF PIN FUNCTIONS

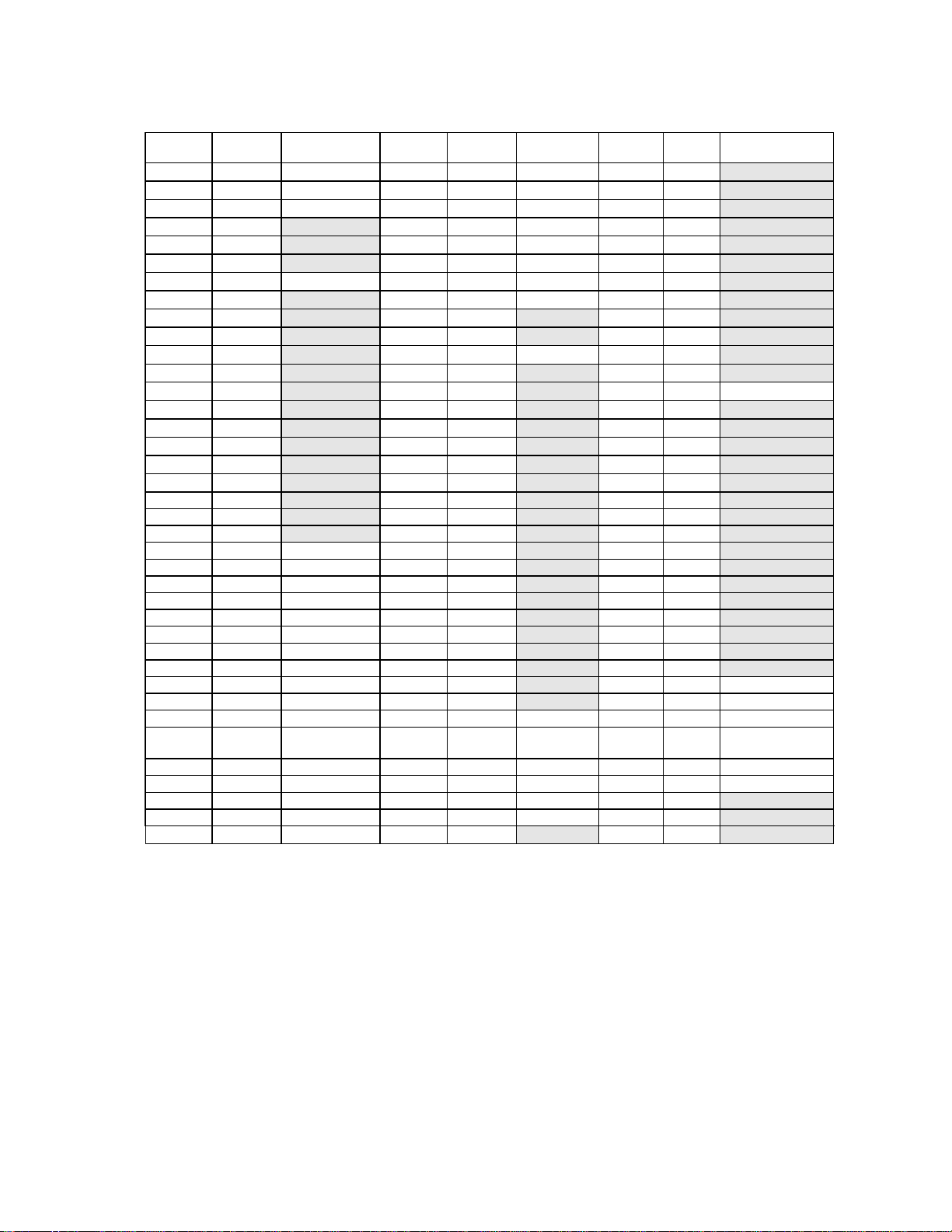

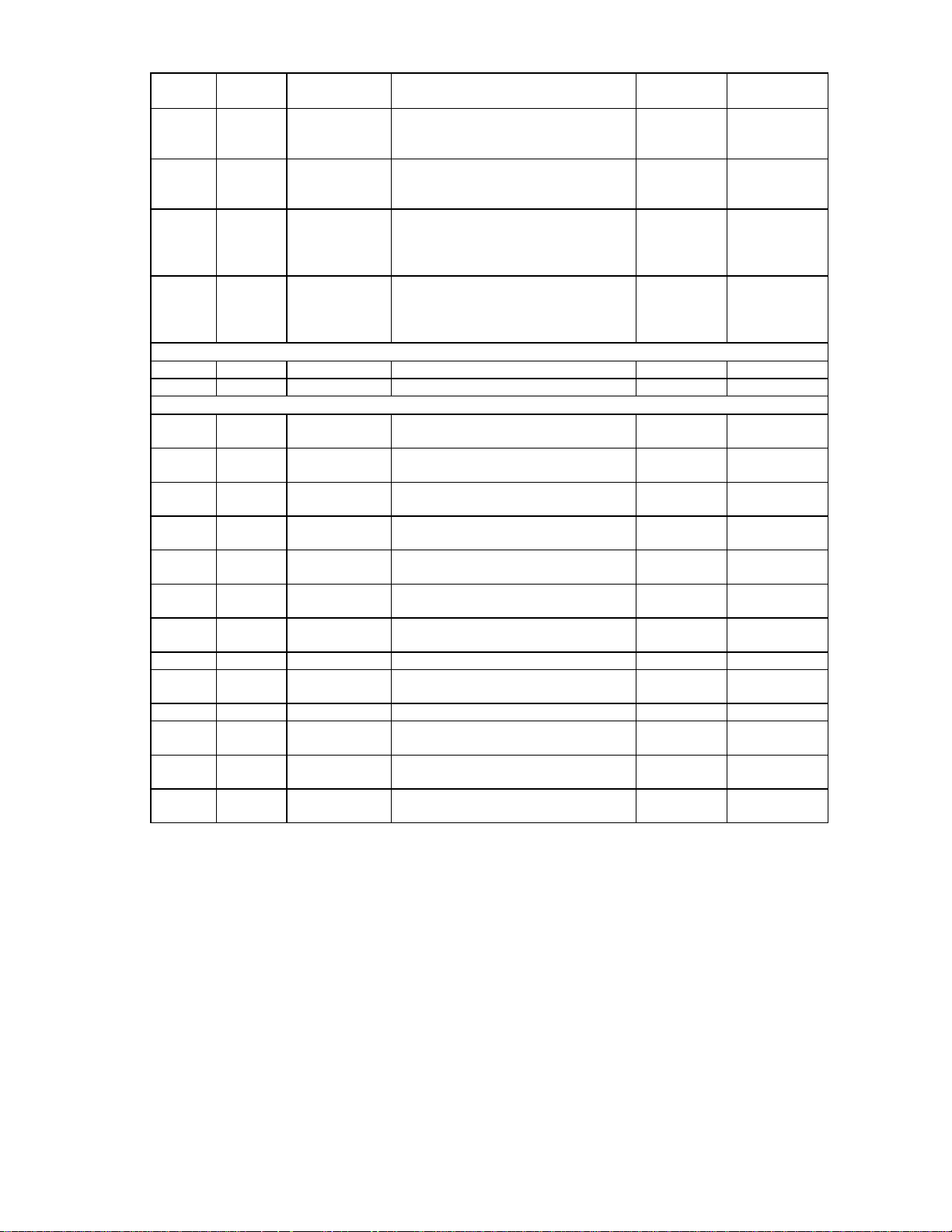

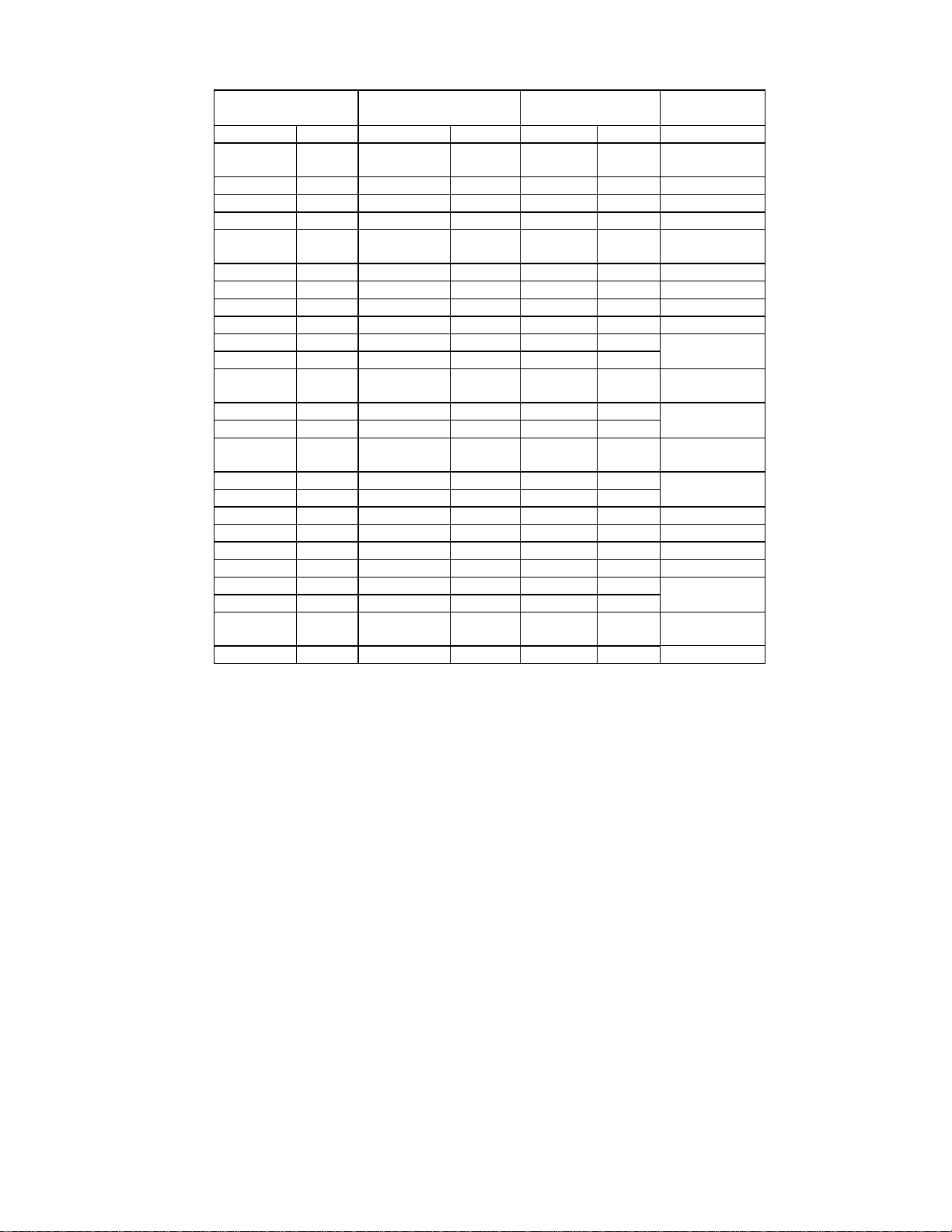

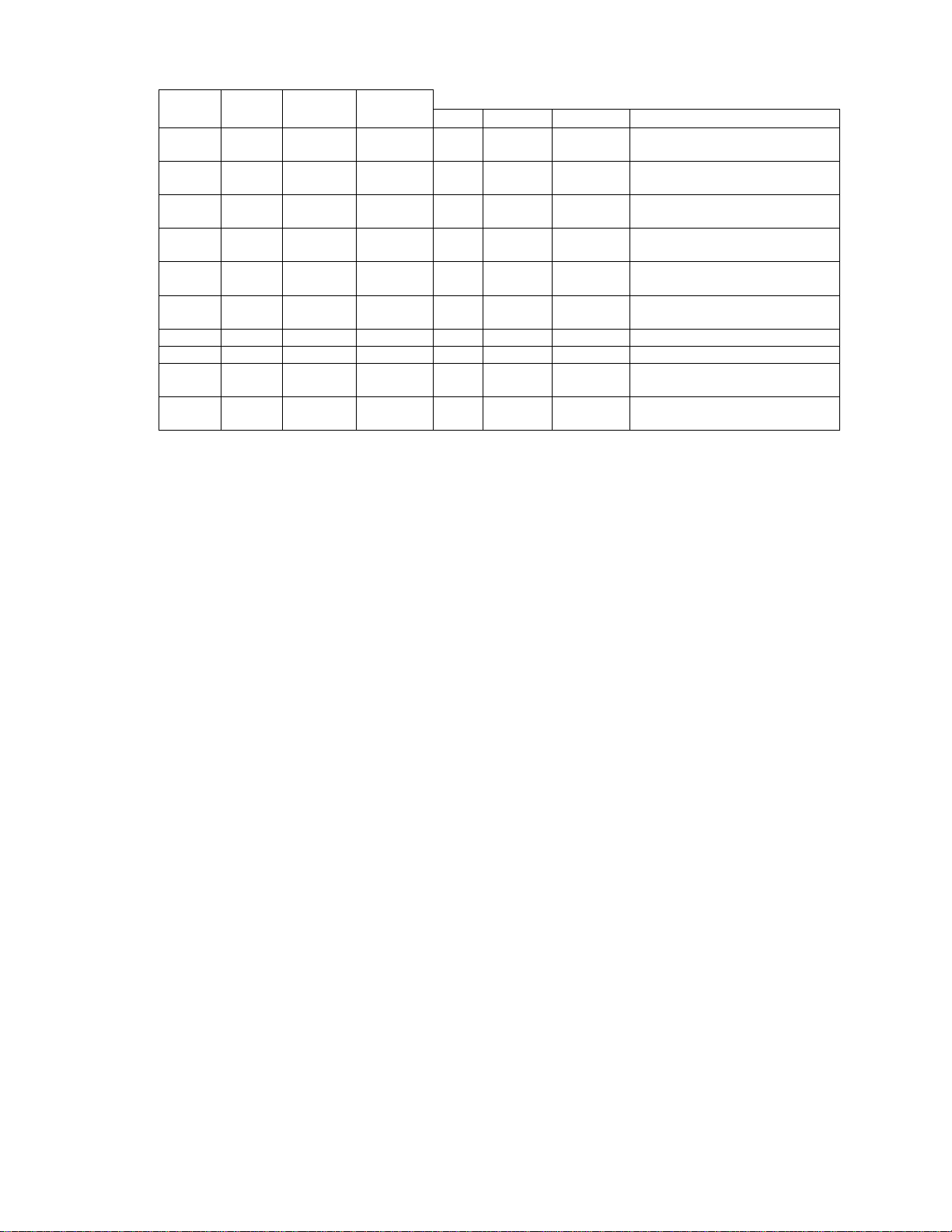

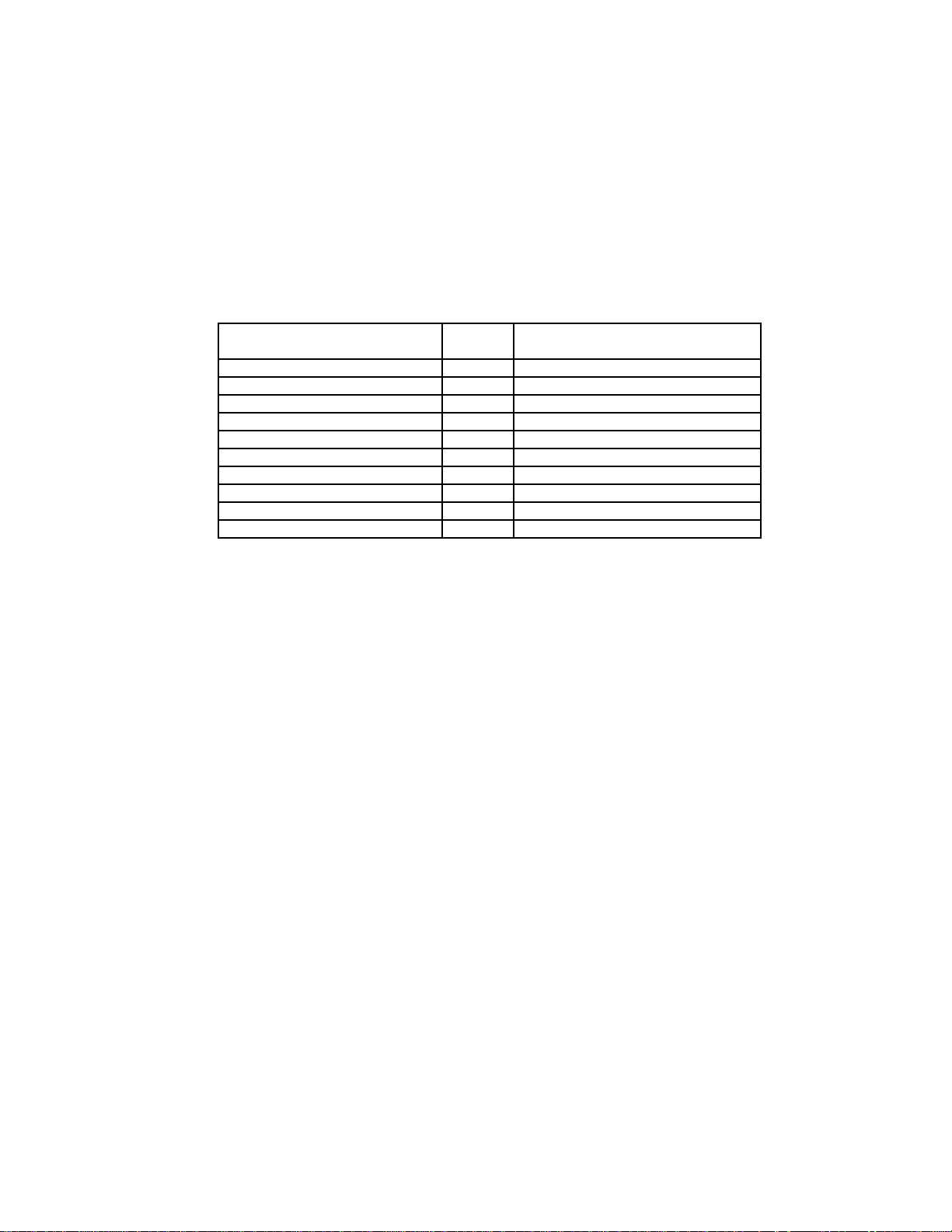

TABLE 1 - FDC37N972 PIN CONFIGURATION

TQFP

PIN#

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19 G3 FPD 57 U3 SA3 95 R13 IOCHRDY

20 H4 IRTX 58 T4 SA4 96 U13 nROMCS

21 G1 IRRX 59 R4 SA5 97 U14 nMEMRD

22 H2 KSO13 60 P5 SA6 98 T14 nMEMWR

23 H3 KSO12 61 U4 SA7 99 R14 PCI_CLK

24 J4 KSO11 62 T5 SA8 100 U15 nCLKRUN

25 H1 KSO10 63 R5 SA9 101 U16 SER_IRQ

26 J2 KSO9 64 P6 SA10 102 T15 nRESET_OUT

27 J3 KSO8 65 U5 SA11 103 R15 CLOCKI

28 K4 KSO7 66 T6 SA12 104 T16 VCC2

29 J1 VCC1 67 R6 SA13 105 U17 24MHz_OUT

30 K2 KSO6 68 P7 SA14 106 R16 nEC_SCI

31 K3 KSO5 69 U6 SA15 107 P14 VSS

32 L4 KSO4 70 T7 OUT0 108 T17 32kHz_OUT

33 K1 KSO3 71 R7 OUT1 109 R17 VCC1_

34 L2 KSO2 72 P8 OUT2 110 P16 nPWR_LED

35 L3 KSO1 73 U7 VSS 111 P15 PWRGD

36 M4 KSO0 74 T8 OUT3 112 N14 SLCT

37 L1 KSI7 75 R8 OUT4 113 P17 PE

38

FGBA

PIN# NAME

A1

VSS 39

C2 OUT5

D4 OUT6

B1 DRVDEN0

C1 DRVDEN1

D2 nMTR0

D3

VSS 45

E4 nDS0

D1 nDIR

E2 nSTEP

E3 nWDATA

F4 nWGATE

E1 nHDSEL

F2 nINDEX

F3 nTRK0

G4 nWRTPRT

F1 nRDATA

G2 nDSKCHG

M2 KSI6

TQFP

PIN#

40

41

42

43

44

46

47

48

49

50

51

52

53

54

55

56

76

FGBA

PIN# NAME

M3 KSI5

N4 KSI4

M1 KSI3

N2 KSI2

N3 KSI1

N1 KSI0

P1 GPIO20

P2 GPIO21

P3 IMCLK

R1 IMDAT

T1

VSS 87

R2 KCLK

R3 KDAT

T2 EMCLK

U1 EMDAT

T3 SA0

P4 SA1

U2 SA2

P9 nNOWS

11

TQFP

PIN#

77

78

79

80

81

82

83

84

85

86

88

89

90

91

92

93

94

114

FGBA

PIN# NAME

U8 nIOR

T9 nIOW

R9 AEN

P10 SD0

U9 SD1

T10 SD2

R10

VCC2

P11 SD3

U10 SD4

T11 SD5

R11 SD6

P12 SD7

U11

VSS

T12 nDACK0

R12 DRQ0

P13 nDACK1

U12 DRQ1

T13 TC

PWRGD

N16 BUSY

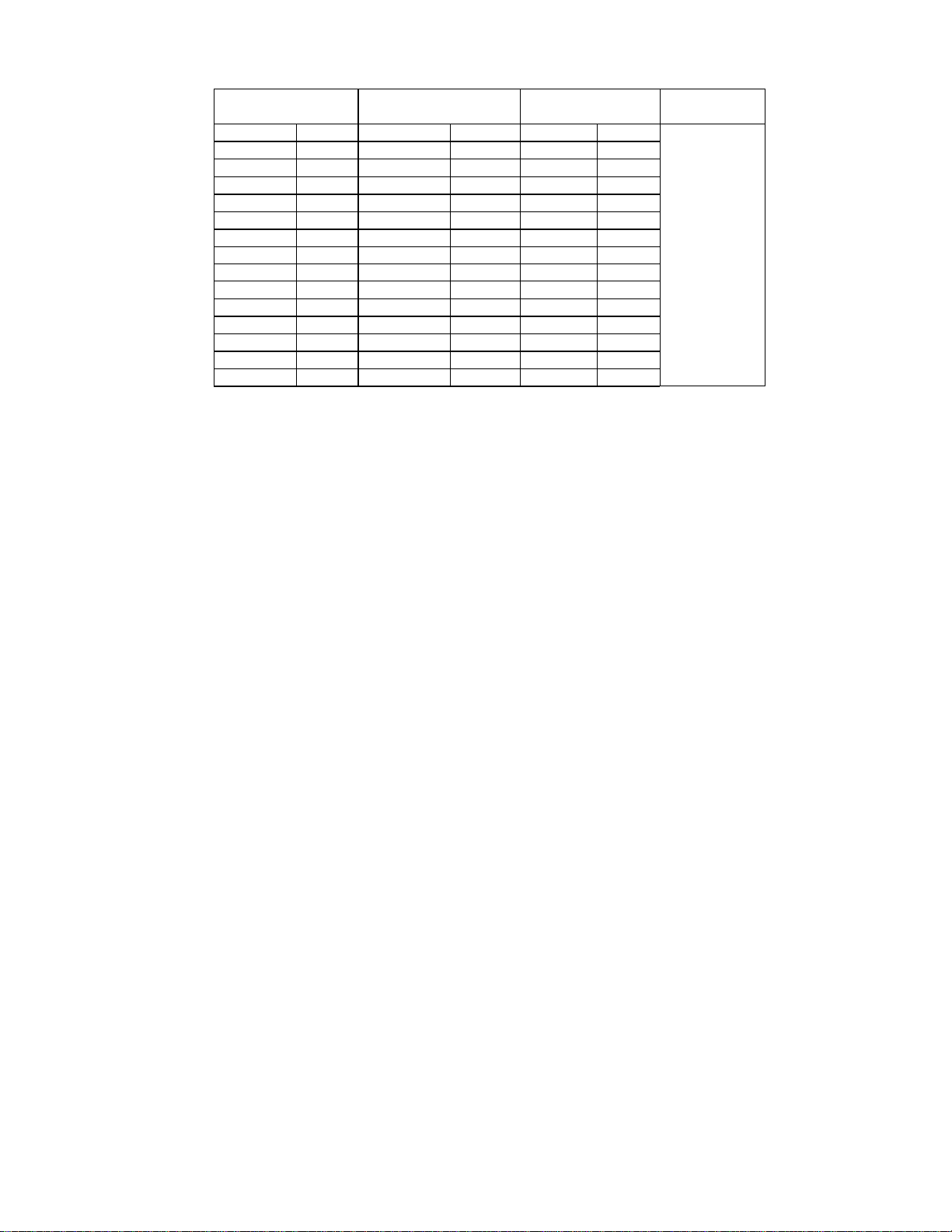

Page 12

TQFP

PIN#

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

FGBA

PIN# NAME

N15 nACK

M14 PD7

N17 PD6

M16 PD5

M15 PD4

L14

VCC2 152

M17 PD3

L16 PD2

L15 PD1

K14 PD0

L17 NSLCTIN

K16 nINIT

K15 nERROR

J14 nALF

K17 nSTROBE

J16 RXD

J15 TXD

H14

VSS 164

J17 nDSR

H16 nRTS

H15 nCTS

G14 nDTR

H17 nDCD

G16 nRI

G15 GPIO15

F14 GPIO14

G17 GPIO8

F16 GPIO9

F15

VCC1 175

E14 FA18

F17 GPIO10

E16 GPIO11

TQFP

PIN#

147

148

149

150

151

153

154

155

156

157

158

159

160

161

162

163

165

166

167

168

169

170

171

172

173

174

176

177

178

FGBA

PIN# NAME

E15 GPIO12

E17 IN0

D17 IN1

D16 IN2

D15 IN3

C17 IN4

B17 IN5

C16 IN6

C15 IN7

B16

VCC0 188

A17 XOSEL

B15 XTAL1

D14 XTAL2

A16

AGND 192

A15 FAD0

B14 FAD1

C14 FAD2

D13 FAD3

A14 FAD4

B13 FAD5

C13

VSS 199

D12 FAD6

A13 FAD7

B12 FA8

C12 FA9

D11 FA10

A12 FA11

B11 FA12

C11 FA13

D10

VCC1 208

A11 FA14

B10 FA15

TQFP

PIN#

179

180

181

182

183

184

185

186

187

189

190

191

193

194

195

196

197

198

200

201

202

203

204

205

206

207

FGBA

PIN# NAME

C10 FA16

D9 FA17

A10 FALE

B9 nFRD

C9 nFWR

D8 nFCS

A9 GPIO1

B8 GPIO2

C8 GPIO3

D7 GPIO4

A8 GPIO5

B7 GPIO6

C7 GPIO7

D6

VSS

A7 nEA

B6 MODE

C6 AB1_DATA

D5 AB1_CLK

A6 nBAT_LED

B5 nFDD_LED

C5 OUT11

A5 OUT10

A4 OUT9

B4 OUT8

C4 OUT7

A3 GPIO16

A2

VCC2

B3 GPIO17

C3 GPIO18

B2 GPIO19

VCC2 VCC1 VCC0

12

Page 13

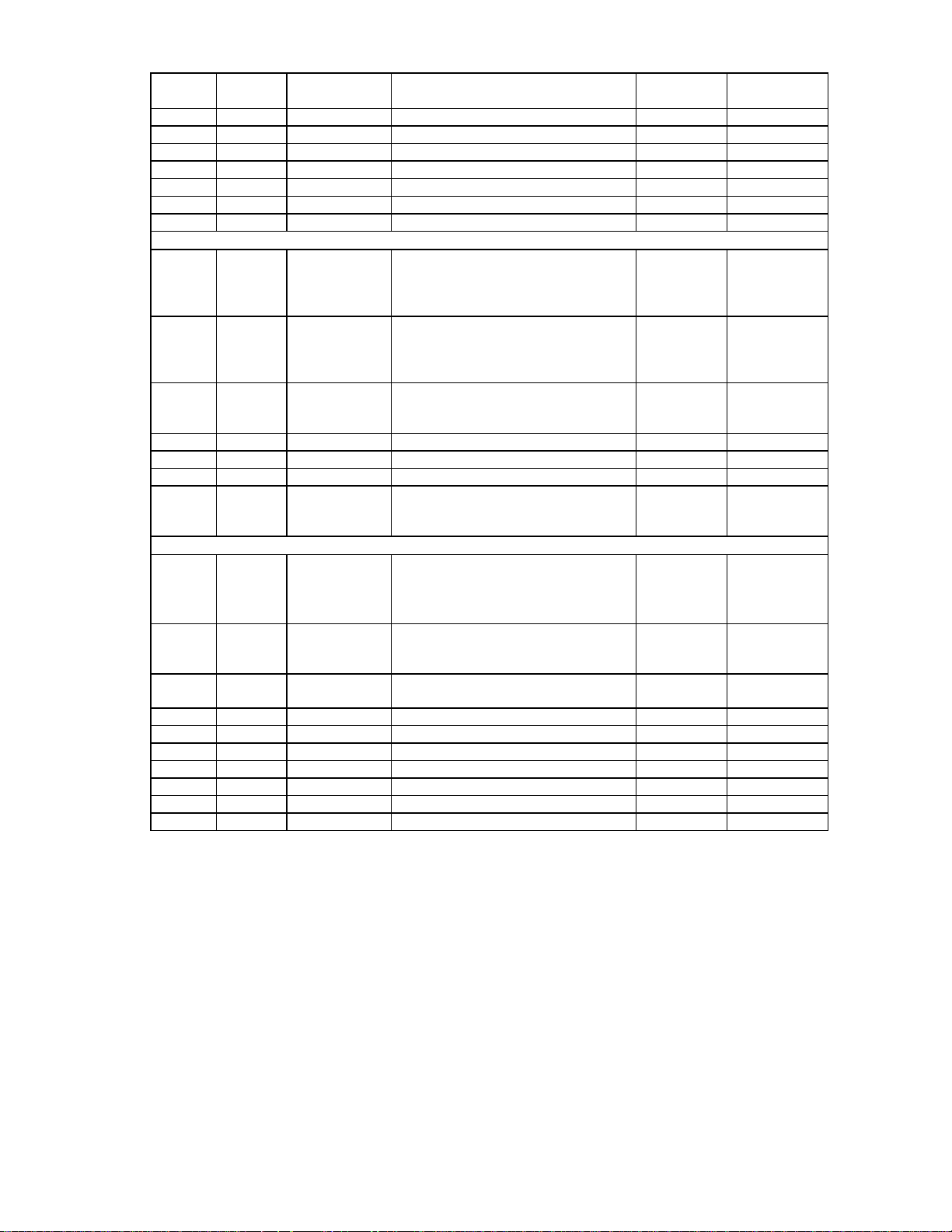

Device functions per pin are shown in TABLE 2.

Buffer Modes symbols in TABLE 2 are described

in Table 3. Multifunction pins are summarized

in Table 4, including a multiplex controls

reference.

The pins and descriptions in Table 2 are

organized by primary pin function. For example,

the PS2 Serial Clock and PS2 Serial Data pins

are technically part of the KEYBOARD AND

MOUSE INTERFACE but are listed in the

GENERAL PURPOSE I/O INTERFACE because

the GPIO function of these pins is the default.

TABLE 2 - PIN FUNCTION DESCRIPTION

TQFP

PIN# NOTES NAME DESCRIPTION

POWER

PLANE

BUFFER

MODES

FDD INTERFACE (15)

The following FDC output pins can be configured as either Open Drain outputs capable of sinking 12mA

(OD12) or as push-pull outputs capable of driving 6mA and sinking 12mA (O12). The FDC output pins

must tristate when the FDC is in powerdown mode (The board designer must provide external pull-up

resistors on these output pins).

4 DRVDEN0 Drive Density Select 0 VCC2 (O12/OD12)

5 DRVDEN1 Drive Density Select 1 VCC2 (O12/OD12)

6 nMTR0 Motor On 0 VCC2 (O12/OD12)

8 nDS0 Drive Select 0 VCC2 (O12/OD12)

9 nDIR Step Direction VCC2 (O12/OD12)

10 nSTEP Step Pulse VCC2 (O12/OD12)

11 nWDATA Write Disk Data VCC2 (O12/OD12)

12 nWGATE Write Gate VCC2 (O12/OD12)

13 nHDSEL Head Select VCC2 (O12/OD12)

14 nINDEX Index Pulse Input VCC2 IS

15 nTRK0 Track 0 VCC2 IS

16 nWRTPRT Write Protected VCC2 IS

17 nRDATA Read Disk Data VCC2 IS

18 nDSKCHG Disk Change VCC2 IS

19 FPD Floppy Power Down Output Control VCC2 O8

PCI POWER MANAGEMENT AND SIRQ INTERFACE (4)

106 7 nEC_SCI Power Management Event VCC1 PCI_OD

99 PCI_CLK PCI Clock VCC2 PCI_ICLK

101 SER_IRQ Serial IRQ VCC2 PCI_IO

100 nCLKRUN PCI Clock Control VCC2 PCI_OD

ISA HOST INTERFACE (37)

80: 82,

SD[7:0] System Data Bus VCC2 IO12

84: 88

54: 69 SA[15:0] System Address Bus VCC2 I

96 nROMCS ROM Chip Select VCC2 I

79 AEN Address Enable VCC2 I

95 IOCHRDY I/O Channel Ready VCC2 OD12

91, 93 DRQ[1:0] DMA Requests VCC2 O12

2

13

Page 14

TQFP

PIN# NOTES NAME DESCRIPTION

POWER

PLANE

90, 92 NDACK[1:0] DMA Acknowledge VCC2 I

94 TC Terminal Count VCC2 I

77 nIOR I/O Read VCC2 I

78 nIOW I/O Write VCC2 I

97 nMEMRD Memory Read VCC2 I

98 nMEMWR Memory Write VCC2 I

76 nNOWS No Wait State VCC2 OD12

FLASH ROM INTERFACE (23)

161:

FAD[7:0] Flash Address/Data[7:0] Bus VCC1 IO8

166,

168,

169

170:

175,

177:

FA[8:17] Flash Address[17:8]

NOTE: Upper Address bit FA18 is

multiplexed on GPIO13

VCC1 O8

180

144 5 FA18/

GPIO13

Flash Address 18

General Purpose I/O

VCC1 O8/IO8

(WK_SE17)

182 nFRD Flash Memory Read VCC1 O8

183 nFWR Flash Memory Write VCC1 O8

181 FALE Flash Address Latch Enable VCC1 O8

184 5 nFCS/

GPIO0

Flash ROM Chip Select

General Purpose I/O

VCC1 O8/IO8

(WK_SE02)

KEYBOARD AND MOUSE INTERFACE (29)

30: 36,

24:

28

KSO[0:11]

Keyboard Scan Outputs (14 × 8).

NOTE: GPIO4 and GPIO5 can be

configured as KSO14 and KSO15

VCC1 OD4

(16 × 8).

23 3 KSO12/

OUT8/

KBRST

22 11 KSO13/

GPIO18

Keyboard Scan Output

General Purpose Output

CPU_RESET

Keyboard Scan Output

General Purpose I/O

VCC1 OD4/OD4/

VCC1 OD4/IOD4

37:44 KSI[0:7] Keyboard Scan Inputs VCC1 ISP

193 nEA External Access for 2k ROM VCC1 I

52 EMCLK EM Serial Clock VCC2 IOD16

53 EMDAT EM Serial Data VCC2 IOD16

47 IMCLK IM Serial Clock VCC2 IOD16

48 IMDAT IM Serial Data VCC2 IOD16

51 KDAT Keyboard Data VCC2 IOD16

BUFFER

MODES

OD4

2

14

Page 15

TQFP

PIN# NOTES NAME DESCRIPTION

POWER

PLANE

BUFFER

MODES

50 KCLK Keyboard Clock VCC2 IOD16

GENERAL PURPOSE I/O INTERFACE (40)

70 7,8 OUT0 (SCI) General Purpose Output (SCI) VCC1 (O12/OD12)

71 3 OUT1/

nIRQ8

General Purpose Output/

Active Low RTC IRQ

VCC1 O12/O12

72 OUT2 General Purpose Output VCC1 O12

74 OUT3/

FRW

General Purpose Output

Inverted Flash ROM Memory Write

VCC1 O12/O12

75 OUT4 General Purpose Output VCC1 O12

2 3 OUT5/

nDS1/

KBRST

3 3 OUT6/

nMTR1

203 3 OUT7/

nSMI

202 3 OUT8/

DRQ2/

KBRST

201 3 OUT9/

DRQ3

200 OUT10/

PWM0

199 OUT11/

PWM1

148 4 IN0

General Purpose Output

FDD Drive Select 1

CPU_RESET

3

3

General Purpose Output

VCC1 O12/(O12/

VCC1 O12/(O12/

FDD Motor On 1

General Purpose Output

VCC1 O12/OD12

SMI Output

General Purpose Output

VCC1 O12/O12/

DMA Request

CPU_RESET

General Purpose Output

VCC1 O12/O12

DMA Request

General Purpose Output

VCC1 O12/O12

Pulse Width Modulator Output

General Purpose Output

VCC1 O12/O12

Pulse Width Modulator Output

General Purpose Input VCC1 I

OD12)/O12

OD12)

O12

(WK_EE4)

149 4 IN1

General Purpose Input VCC1 I

(WK_EE2)

150 4 IN2

General Purpose Input VCC1 I

(WK_EE3)

151 IN3

(nGPWKUP)

152 5 IN4

General Purpose Input (General

VCC1 I

Purpose Wake Up)

General Purpose Input VCC1 I

(WK_SE00)

153 5 IN5

General Purpose Input VCC1 I

(WK_SE01)

154 5 IN6

General Purpose Input VCC1 I

(WK_SE05)

155 4 IN7

General Purpose Input VCC1 I

(WK_EE1)

185 5 GPIO1

General Purpose I/O VCC1 IO8

(WK_SE03)

15

2

Page 16

TQFP

PIN# NOTES NAME DESCRIPTION

186 5 GPIO2

General Purpose I/O VCC1 IO8

(WK_SE04)

187 6 GPIO3

(TRIGGER)

188 5 GPIO4

(WK_SE07)/

General Purpose I/O (Interrupt 1

Event)

General Purpose I/O

Keyboard Scan Output

KSO14

189 5 GPIO5

(WK_SE10)/

General Purpose I/O

Keyboard Scan Output

KSO15

190 5 GPIO6

(WK_SE11)/

IRMODE/IRR

General Purpose I/O

FIR Mode Output or 2nd Receive

Input

X3A

191 5, 8 GPIO7

(WK_SE06)

141 5 GPIO8

(WK_SE12)/

General Purpose I/O VCC1 (IO8/IOD8)

5

General Purpose I/O

IR Receive Input

IRRX2

142 1,

5

GPIO9

(WK_SE13)/

General Purpose I/O

IR Transmit Output

IRTX2

145 5 GPIO10

(WK_SE14)/

IRMODE/IRR

General Purpose I/O

FIR Mode Output or 2nd Receive

Input

X3B

146 5 GPIO11

(WK_SE15)/

General Purpose I/O

ACCESS.bus 2 Serial Data

AB2_DATA

147 5 GPIO12

(WK_SE16)/

General Purpose I/O

ACCESS.bus 2 Clock

AB2_CLK

140 5 GPIO14

General Purpose I/O VCC1 IO8

(WK_SE20)

139 5 GPIO15

General Purpose I/O VCC1 IO8

(WK_SE21)

204 5 GPIO16

(WK_SE22)

206 3,

5

GPIO17

(WK_SE23)/

General Purpose I/O VCC1 IO8

5

General Purpose I/O

KBD GATEA20 Output

GATEA20

POWER

PLANE

BUFFER

MODES

VCC1 IO8

VCC1 IO8/OD8

VCC1 IO8/OD8

VCC1 IO8/(O8/I)

VCC1 IO8/I

VCC1 IO12/O12

VCC1 IO8/O8/

(O8/I)

VCC1 IO12/IOD12

VCC1 IO12/IOD12

VCC1 IO8/O8

2

8

16

Page 17

TQFP

PIN# NOTES NAME DESCRIPTION

207 5 GPIO18

(WK_SE27)/

General Purpose I/O/

DMA Acknowledge

POWER

PLANE

VCC1 IO8/I

nDACK2

208 5 GPIO19

(WK_SE24)/

General Purpose I/O/

DMA Acknowledge

VCC1 IO8/I

nDACK3

45 3,

5

GPIO20

(WK_SE25)/

PS2CLK/

General Purpose I/O

PS2 Serial Clock

8051 RX Input

VCC1 IOD16/

IOD16/I

8051RX/

46 3,5 GPIO21

(WK_SE26)/

PS2DAT/

General Purpose I/O

PS2 Serial Data

8051 TX Input

VCC1 IOD16/

IOD16/

OD16

8051TX

INFRARED INTERFACE (2)

21 IRRX IR Receive Input VCC1 I

20 1 IRTX IR Transmit Output VCC2 O12

PARALLEL PORT INTERFACE (17)

126 nINIT/

nDIR

125 nSLCTIN/

nSTEP

124 PD0/

nINDEX

123 PD1/

nTRK0

122 PD2/

nWRTPRT

121 PD3/

nRDATA

119 PD4/

nDSKCHG

Initiate Output

FDC Direction Control

Printer Select Input

FDC Step Pulse

Port Data 0

FDC Index

Port Data 1

FDC Track 0

Port Data 2

FDC Write Protected

Port Data 3

FDC Read Disk Data

Port Data 4

FDC Disk Change

VCC2 (OD14/

OP14)/OD14

VCC2 (OD14/

OP14)/OD14

VCC2 IOP14/I

VCC2 IOP14/I

VCC2 IOP14/I

VCC2 IOP14/I

VCC2 IOP14/I

118 PD5 Port Data 5 VCC2 IOP14

117 PD6/

nMTR0

Port Data 6

FDC Motor On 0

VCC2 IOP14/OD14

116 PD7 Port Data 7 VCC2 IOP14

112 SLCT/

nWGATE

113 PE/

nWDATA

114 BUSY/

nMTR1

Printer Selected Status

FDC Write Gate

Paper End

FDC Write Data

Busy

FDC Motor On 1

VCC2 I/OD12

VCC2 I/OD12

VCC2 I/OD12

BUFFER

MODES

2

17

Page 18

TQFP

PIN# NOTES NAME DESCRIPTION

115 nACK/

nDS1

127 nERROR/

nHDSEL

128 nALF/

DRVDEN0

129 nSTROBE/

nDS0

Acknowledge

FDC Drive Select 1

Error

FDC Head Select

Autofeed Output

FDC Density Select 0

Strobe Output

FDC Drive Select 0

POWER

PLANE

VCC2 I/OD12

VCC2 I/OD12

VCC2

VCC2

SERIAL PORT INTERFACE (8)

130 RXD Receive Data VCC2 I

131 TXD Transmit Data VCC2 O12

133 nDSR Data Set Ready VCC2 I

134 nRTS Request to Send VCC2 O8

135 nCTS Clear to Send VCC2 I

136 nDTR Data Terminal Ready VCC2 O8

138 nRI Ring Indicator VCC1 I

137 nDCD Data Carrier Detect VCC2 I

MISCELLANEOUS (11)

108 32kHz_OUT 32.768kHz Output Clock --The 32

VCC1 O8

KHz output is enabled / disabled by

setting / clearing bit-0 of the Output

Enable 8051 memory mapped

register. When disabled the 32

KHz_OUT pin is driven low. The 32

KHz_OUT pin defaults to the

disabled state on VCC1 POR.

105 24MHz_OUT 24MHz Clock Output

VCC2 O24

Programmable Clock Output.

1.8432 MHz (default = 24 MHz/13)

14.318 MHz

16 MHz

24 MHz

48 MHz

103 CLOCKI 14.318MHz Clock Input VCC2 ICLK

194 MODE Configuration Ports Base Address

VCC1 I

Select

157 10 XOSEL External 32kHz Clock Enable Input VCC0 I

BUFFER

MODES

(OD14/OP14)/

OD14

(OD14/OP14)/

OD14

2

18

Page 19

TQFP

PIN# NOTES NAME DESCRIPTION

109 9 VCC1_PWRGDVCC1 Power Good Input. The

POWER

PLANE

VCC1 IP

BUFFER

MODES

trailing edge of VCC1 POR is

released 20ms from the assertion of

this pin. If this pin is pulled low

while VCC1 is valid, then VCC1

POR will be asserted and held until

20ms from re-assertion of this pin.

This pin has an internal weak

(90µA) pull-up to VCC1.

102

nRESET_OUT

System Reset VCC2 O8

197 nBAT_LED Battery LED (0 = ON) VCC1 OD12

110 nPWR_LED Power LED (0 = ON) VCC1 OD12

198 nFDD_LED Floppy LED (0 = ON). This pin is

VCC1 OD12

asserted whenever either DRVSEL1

or DRVSEL0 is asserted or

controlled by the 8051.

111 9 PWRGD VCC2 Power Good Input VCC1 I

ACCESS BUS INTERFACE (2)

195 AB1_DATA ACCESS.bus 1 Serial Data VCC1 IOD12

196 AB1_CLK ACCESS.bus 1 Clock VCC1 IOD12

REAL TIME CLOCK INTERFACE (2)

158 XTAL1 32.768kHz Crystal Input VCC0 ICLK2

159 10 XTAL2 32.768kHz Crystal Output VCC0 (OCLK2/I)

POWER PLANES

156 VCC0 RTC (V

29,

VCC1

+3.3V ± 5% Main Battery Supply

) Supply Voltage

BAT

143,

176,

83,

104,

VCC2

+3.3V ± 5% Switched AC/Main

Battery Supply

120,

205

160 AGND Analog Ground

1,7,49,

VSS Digital Ground

73, 89,

107,

132,

167,

192

2

19

Page 20

NOTE 1: These pins default to “output”, “low” to prevent infrared transceiver damage (see

Section IRTX Output Pins DEFAULT).

NOTE 2: Buffer Modes per function on multiplexed pins are separated by a slash “/”; e.g., a

pin with two multiplexed functions where the primary function is an input and the

secondary function is an 8mA bidirectional driver is represented as “I/IO8”. Buffer

Modes in parenthesis represent multiple buffer modes for a single pin function.

NOTE 3: This pin is tristated when PWRGD is inactive and the pin is configured as a VCC2-

powered alternate function.

NOTE 4: These devices can generate wake-up events on either edge of the signal that is

applied when the pin is configured as an input. The interrupts are masked by the

Wake-up Mask Register bits.

NOTE 5: These devices can generate wake-up events on selectable edges of the signal that is

applied when the pin is configured as an input. The interrupts are masked by the

Wake-up Mask Registers and selected edges are programmed via the Edge Select

registers (see section 8051 Internal PARALLEL on page 170).

NOTE 6: This interrupt is masked by INT1 Mask Register bit 3. GPIO3 is the only GPIO pin

which does not generate a wakeup event.

NOTE 7: The nEC_SCI pin can be controlled by hardware and 8051 software. The nEC_SCI

pin can drive either the ACPI Run-time GPE Chipset input or the Wake GPE Chipset

input (FIGURE 7). Depending how the nEC_SCI pin is used, other ACPI-related SCI

functions may be best supplied by FDC37N972 general purpose output OUT0.

NOTE 8: OUT0 and GPIO7 are suitable as an SCI output pin because the buffer type can be

configured as a push-pull or open-drain output (see a description of the MISC21 and

MISC23 bits in Multiplexing_3 Register on page 278).

NOTE 9: Input levels for the PWRGD and VCC1_PWRGD pins are rail-to-rail ±400mV; e.g.,

PWRGD VIL = .4V max, PWRGD VIH = 2.7V min. @ VCC1 min.

NOTE 10: The function of these pins are described in Section 32kHz Clock Input

The FDC37N972 uses the XOSEL pin to select either a 32.768kHz input clock or a

32.768kHz crystal to drive the Real Time Clock Interface (Table 2 - PIN FUNCTION

DESCRIPTION).

When XOSEL = ‘0’, the RTC uses a 32.768kHz crystal connected between the

XTAL1 and XTAL2 pins. When XOSEL = ‘1’, the RTC is driven by a 32.768kHz

single-ended clock source connected to THE XTAL2 PIN.

NOTE: ICC0 ≥≥ 10µA for time-keeping operations under VCC0 using a single-ended

clock source. ICC1 = 30µA under VCC1 using a single-ended clock source.

NOTE 11: The GPIO18 alternate function of the KS013 pin has no wake-up capability (see note

following).

20

Page 21

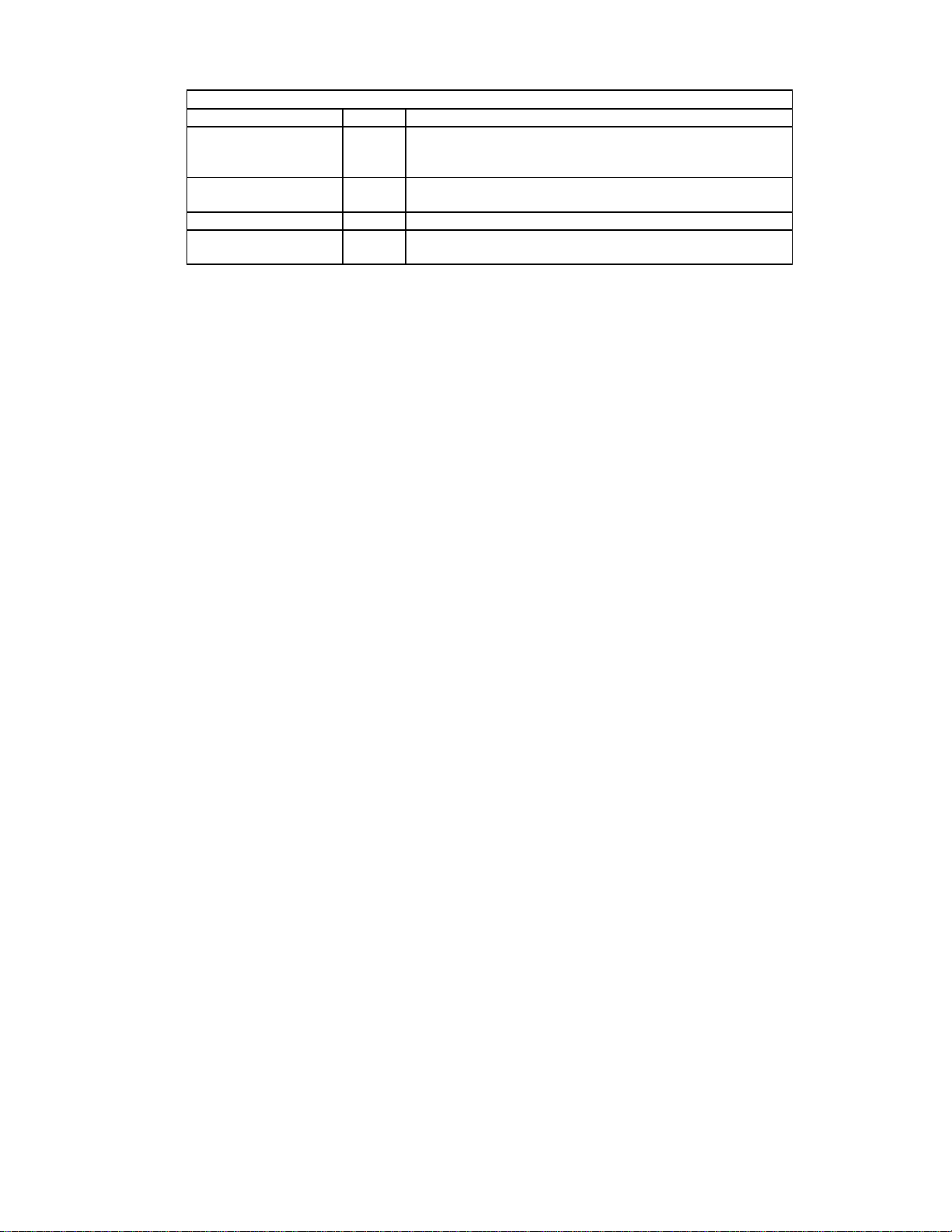

TABLE 3 - BUFFER MODE LEGEND

BUFFER SYMBOL DESCRIPTION

I Input

IO12 Bidirectional – 12mA sink, 6mA source

IO8 Bidirectional – 8mA, 4mA source

IOD16 Input, open drain output – 16mA sink

IOD8 Input, open drain output – 8mA sink

IOP14 Bidirectional – 14mA sink, 14mA source, backdrive

protected

IP Input with pullup

IS Schmitt trigger input

ISP Schmitt trigger input with pullup

O12 Output – 12mA, 6mA source

O8 Output – 8mA, 4mA source

OD12 Open drain – 12mA sink

OD14 Open drain – 14mA sink

OD16 Open drain – 16mA sink

OD4 Open drain – 4mA sink

OD8 Open drain – 8mA sink

OP14 Output – 14mA sink, 14mA source, backdrive protected

PCI_ICLK PCI clock input

PCI_IO PCI bidirectional

PCI_OD PCI open drain

ICLK Clock input

ICLK2 Clock input 2

OCLK2 Clock output 2

O24 Output – 12mA, 6mA source

21

Page 22

TABLE 4 - ALTERNATE FUNCTION PINS

DEFAULT

FUNCTION

2

OUT1 VCC1 nIRQ8

OUT3 VCC1 FWR VCC1 - - ALT WRITE

OUT5 VCC1 nDS1

OUT6 VCC1 nMTR1

OUT7 VCC1 nSMI

OUT8 VCC1 DRQ2

OUT9 VCC1 DRQ3

OUT10 VCC1 PWM0 VCC1 - MISC4

OUT11 VCC1 PWM1 VCC1 - MISC12

nFCS VCC1 GPIO0 VCC1 - MISC19

GPIO4 VCC1 KSO14 VCC1 -

ALTERNATE

FUNCTION #1

3

VCC2 - MISC0

3

3

VCC2 KBRST3VCC2 MISC[5, 22]

3

VCC2 - - MISC5

VCC2 - MISC18

3

VCC2 KBRST3VCC2 MISC[17,10,

3

VCC2 - MISC11

ALTERNATE

FUNCTION #2

MULTIPLEX

CONTROLS

SELECT

6

1

6]

1

1

MISC9

GPIO5 VCC1 KSO15 VCC1 GPIO6 VCC1 IRMODE/IR

GPIO8 VCC1 IRRX VCC1 GPIO9 VCC1 IRTX

GPIO10 VCC1 IRMODE/IR

RX3A

RX3B

3

4

3

GPIO11 VCC1 AB2_DATA VCC1

GPIO12 VCC1 AB2_CLK VCC1

FA18 VCC1 GPIO13 VCC1 - MISC8

GPIO17 VCC1 GATEA20

VCC2 - MISC[14:13]

VCC2 VCC2 - MISC[16:15]

3

VCC1 - MISC6

MISC[2,7]

MISC20

1

GPIO18 VCC1 nDACK2 VCC1 - MISC17

GPIO19 VCC1 nDACK3 VCC1 - MISC11

GPIO20 VCC1 PS2CLK

GPIO21 VCC1 PS2DAT

3

VCC2 8051RX VCC1

3

VCC2 8051TX VCC1

MISC[3, 1]

KSO12 VCC1 OUT8 VCC1 KBRST3VCC2 MISC[17, 10,

6]

KSO13 VCC1 GPIO18 VCC1 - MISC17

5

22

Page 23

DEFAULT

FUNCTION

2

ALTERNATE

FUNCTION #1

ALTERNATE

FUNCTION #2

MULTIPLEX

CONTROLS

nINIT VCC2 nDIR VCC2 -

nSLCTIN VCC2 nSTEP VCC2 -

CR25[4:3]

PD0 VCC2 nINDEX VCC2 PD1 VCC2 nTRK0 VCC2 PD2 VCC2 nWRTPRT VCC2 PD3 VCC2 nRDATA VCC2 PD4 VCC2 nDSKCHG VCC2 PD6 VCC2 nMTR0 VCC2 -

SLCT VCC2 nWGATE VCC2 -

PE VCC2 nWDATA VCC2 -

BUSY VCC2 nMTR1 VCC2 -

nACK VCC2 NDS1 VCC2 -

nERROR VCC2 NHDSEL VCC2 -

nALF VCC2 DRVDEN0 VCC2 -

nSTROBE VCC2 NDS0 VCC2 -

NOTE 1: See a description in Section MULTIFUNCTION PIN on page 271.

NOTE 2: The FDC37N972 pins are identified by primary pin function (see

DESCRIPTION OF PIN FUNCTIONS on page 11). Note that some functions are

available on more than one pin; e.g., OUT8, GPIO18 and KBRST.

NOTE 3: When this pin is configured as an alternate function output and PWRGD is inactive,

i.e. VCC2 is 0v, the pin will tri-state to prevent back-biasing of external circuitry (see

Section General Purpose I/O (GPIO) on page 265).

NOTE 4: This pin defaults to “output”, “low” for both the default (GPIO) function and the

alternate (IRTX) function, regardless of the state of PWRGD (see Section General

Purpose I/O (GPIO) on page 265).

NOTE 5: MISC5 must be inactive for MISC22 to enable KBRST.

NOTE 6: The ALT WRITE SELECT bit is in the Flash Configuration Register (see Section

ALT WRITE SELECT Bit, D3 on page 197).

23

Page 24

There are three power planes in the FDC37N972

V

CC0, VCC1,

and V

with the following power

CC2

sequencing requirement:

1. V

simultaneously with or after V

2. V

simultaneously with or after V

All internal components which utilize V

shall have power applied

CC2

shall have power applied

CC1

CC1

CC0

.

.

CC0

power

plane are switched internally between the VCC1

and VCC0 pins according to VCC1_PWRGD

See Table 5 for power consumption in various

states.

Two FDC37N972 power supply configurations

can be utilized. These power supply

configuration types fundamentally differ upon

the need for a backup battery (V

to V

.

CC0

) connection

BAT

TYPE 1 devices do not require a V

CC0

battery

connection. Power supply requirements for

TYPE 1 devices are as follows: V

VSS, V

supply, and V

is connected to the main battery

CC1

is switched from either the

CC2

is tied to

CC0

main battery or AC power if available. In this

configuration all internal components which

utilize V

power plane are switched internally

CC0

to the VCC1 upon POR according to

VCC1_PWRGD.

TYPE 2 devices require a V

CC0

battery

connection. Power supply requirements for

TYPE 2 devices are as follows: V

connected to a backup battery (V

BAT

connected to the main battery supply, and V

), V

CC0

CC1

is

is

CC2

is switched from either the main battery or AC

power if available. In this configuration all

internal components which utilize V

plane only when V

is absent. Normally (when

CC1

CC0

power

VCC1_PWRGD is asserted) they are switched

internally to the VCC1 power plane.

24

Page 25

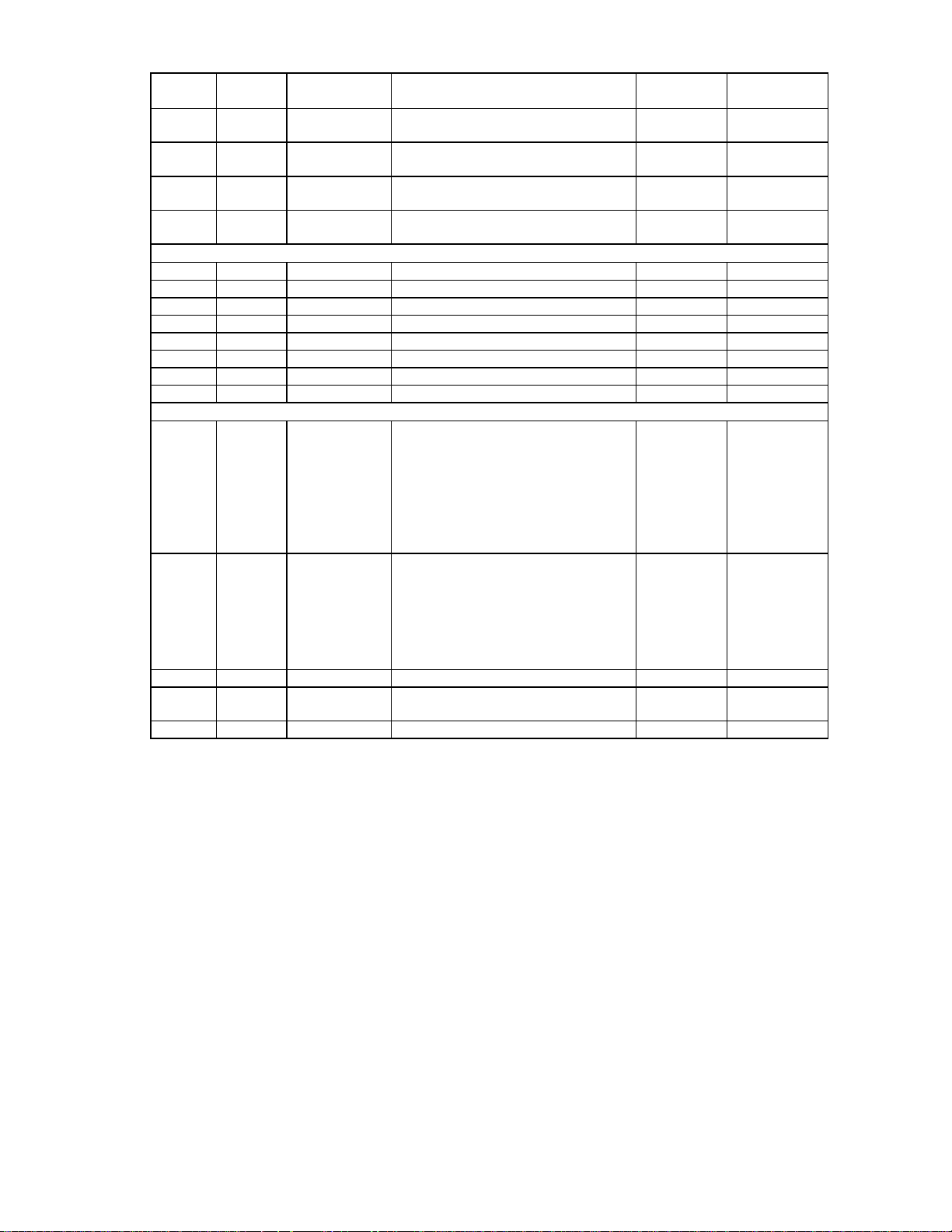

TABLE 5 - POWER COMSUMPTION IN VARIOUS STATES

V

CC2

(VDC)

3.3 3.3 Run 24 MHz I

3.3 3.3 Run 12 MHz I

3.3 3.3 Run Ring

3.3 3.3 Idle Ring

0 3.3 Run Ring

0 3.3 Idle Ring

0 3.3 Sleep Stop I

0 3.3 Sleep Stop I

0 0 I

V

CC1

(VDC)

8051

STATE

CLOCK

STATE

OSC

OSC

OSC

OSC

SYM TYP MAX COMMENTS

I

I

I

I

I

I

I

I

I

I

CC2

CC1

CC2

CC1

CC2

CC1

CC2

CC1

CC2

CC1

CC2

CC1

CC1

CC1

CC0

15 ma

24 ma

13 ma

12 ma

>1ma

8 ma

>1ma

5 ma

8 ma 10 ma

6 ma 8 ma

5 µa 10 µa XOSEL=0

40 µa 60 µa 2.4 < V

20 ma

30 ma

15 ma

18 ma

2 ma

10 ma

2 ma

FLOPPY @ 1 Meg Data Rate

I2C @ 24 MHz

Floppy @ 500K Data Rate

I2C @ 12 MHz

PLL On

I2C Off

PLL Off

7 ma

PLL Off

I2C Off

PLL Off

I2C Off

160 µa XOSEL=1

cc0

< 4 VDC,

XOSEL=1,

0 0 I

CC0

0.4 µa 1.5 µa 2.4 < V

< 4 VDC,

cc0

XOSEL = 0

Note: When a single-ended 32.768kHz clock source is selected (see Section 32kHz Clock Input).

The FDC37N972 uses the XOSEL pin to select either a 32.768kHz input clock or a

32.768kHz crystal to drive the Real Time Clock Interface (Table 2 - PIN FUNCTION

DESCRIPTION). When XOSEL = ‘0’, The RTC uses a 32.768kHz crystal connected between

the XTAL1 and XTAL2 pins. When XOSEL = ‘1’, the RTC is driven by a 32.768kHz singleended clock source connected to the XTAL2 pin.

25

Page 26

TABLE 7 - POWER PIN LIST

BIAS PINS

156 VCC0 RTC (V

)Supply Voltage 2.7-3.3V ibat<2ma

BAT

29, 143, 176 VCC1 8051 + AB + CI + RTC+ ACPI + PM1 + WDT + MR + CR

+ PM + AB2 + FI + PWM + KI + GPIO + LED + IR + 3.3V

+/-5% Supply Voltage (Note)

83, 104, 120, 205 VCC2 SR + PCG + FDC + DDS + UART + PP + PS/2 + Core

+3.3V +/-5%Supply Voltage

160 AGND Analog Ground for VCC0.

1, 7, 49, 73, 89,

VSS Digital Ground

107, 132, 167, 192

Note:

AB = ACCESS.bus

CI = Control Inputs

WDT = Watch Dog Timer

MR = Mailbox Registers

CR = Control Registers

PM = Power Management

AB2 = ACCESS.BUS2

FI = Flash Interface

KI = Keyboard Interface

GPIO = General Purpose I/O Interface

IR = Infrared

SR = System Reset

PCG = PLL Clock Generator

FDC = Floppy Disk Controller

DDS = Digital Data Seperator

PP = Multi-Mode Parallel Port

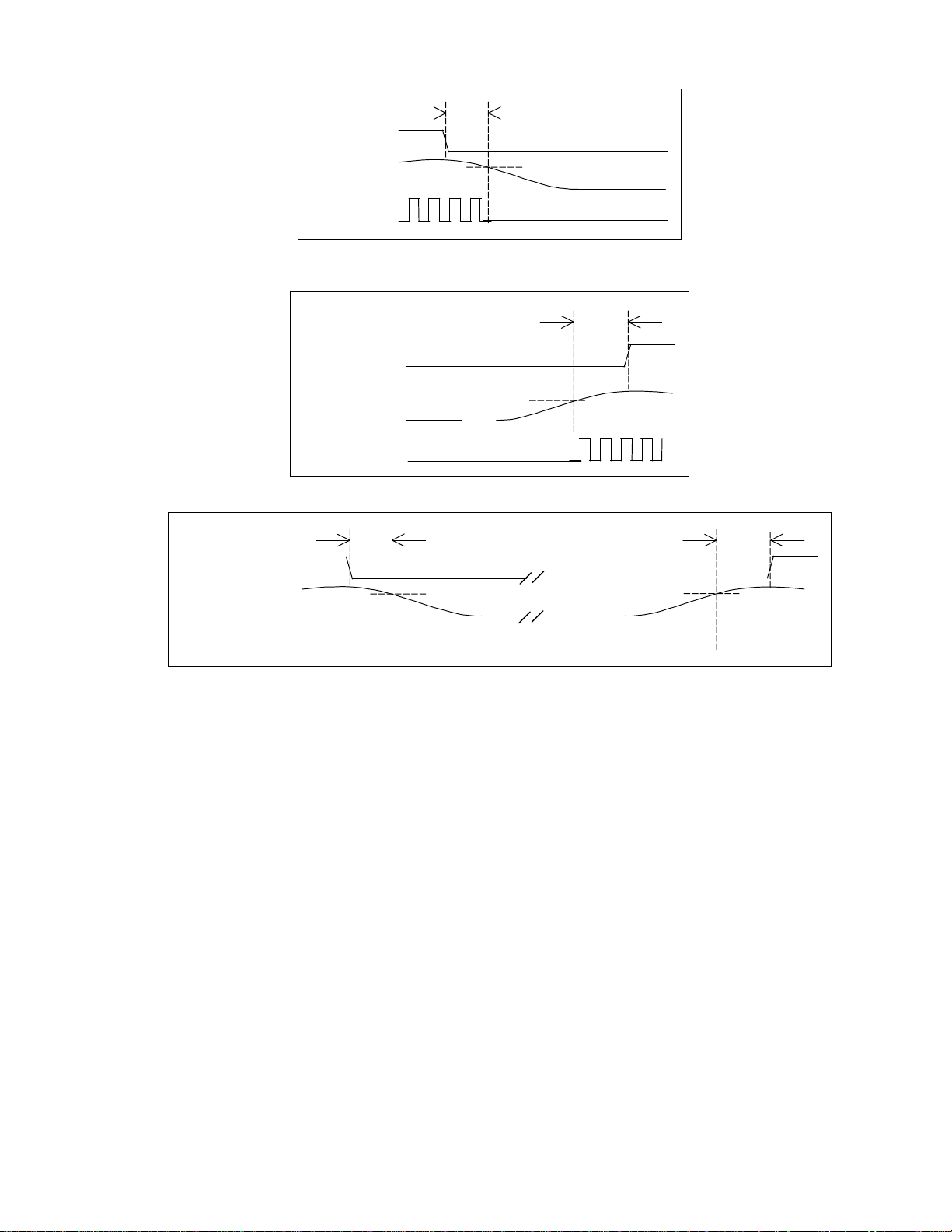

PWRGD and VCC1_PWRGD timing is illustrated in FIGURE 3 through FIGURE 5.

26

Page 27

10µs

PWRGD

VCC2

CLOCKI

min.

3V

FIGURE 3 – POWER-FAIL EVENT

PWRGD

10µs

min.

VCC2

CLOCKI

3V

FIGURE 4 - VCC2 POWER-UP TIMING

1µs

min.

VCC1_PWRGD

VCC1

3V 3V

FIGURE 5 - VCC1_PWRGD TIMING

These figures also appear in the “Timing Diagrams” section of this spec.

1µs

min.

27

Page 28

FUNCTIONAL DESCRIPTION

FDC37N972 OPERATING REGISTERS

The address map, shown below in TABLE 8,

shows the set of operating registers and

addresses for each of the logical blocks of the

FDC37N972 Ultra I/O controller. The base

addresses of the FDC, Parallel, Serial 1 and

Infrared ports can be moved via the

configuration registers.

TABLE 8 - FDC37N972 OPERATING REGISTER ADDRESSES

LOGICAL

DEVICE

NUMBER

0x00 FDC [0x100:0x0FF8]

0x03 Parallel

LOGICAL

DEVICE

Port

BASE I/O

RANGE

(NOTE3)

ON 8 BYTE

BOUNDARIES

[0x100:0x0FFC]

ON 4 BYTE

BOUNDARIES

(EPP Not supported)

or

[0x100:0x0FF8]

ON 8 BYTE

BOUNDARIES

(all modes

supported,

EPP is only available

when the base

address is on an 8byte boundary)

HOST PROCESSOR INTERFACE

The host processor communicates with the

FDC37N972 through a series of read/write

registers. The range of base I/O port addresses

for these registers is shown in TABLE 8.

Register access is accomplished through

programmed I/O or DMA transfers. All registers

are 8 bits. Most of the registers support zero

wait-state access (NOWS). All host interface

output buffers are capable of sinking a minimum

of 6 mA.

ISA

FIXED

BASE OFFSETS

+0 : SRA

+1 : SRB

+2 : DOR

+3 : TSR

+4 : MSR/DSR

+5 : FIFO

+7 : DIR/CCR

+0 : Data / ecpAfifo

+1 : Status

+2 : Control

+400h : cfifo / ecpDfifo

tfifo / cnfgA

+401h : cnfgB

+402h : ecr

CYCLE

TYPE

NOWS

Std. ISA I/O

28

Page 29

LOGICAL

DEVICE

NUMBER

LOGICAL

DEVICE

0x04 Serial

BASE I/O

RANGE

(NOTE3)

[0x100:0x0FF8]

Port 1

ON 8 BYTE

BOUNDARIES

0x05 Infrared

[0x100:0x0FF8]

Port

ON 8 BYTE

BOUNDARIES

0x62,

0x63

[0x100:0x0FF8]

ON 8 BYTE

BOUNDARIES

0x06 RTC Not Relocatable

Fixed Base Address

0x07 KYBD Not Relocatable

Fixed Base

Address

FIXED

BASE OFFSETS

+0 : RB/TB LSB div

+1 : IER MSB div

+2 : IIR/FCR

+3 : LCR

+4 : MCR

+5 : LSR

+6 : MSR

+7 : SCR

+0 : RB/TB LSB div

+1 : IER MSB div

+2 : IIR/FCR

+3 : LCR

+4 : MCR

+5 : LSR

+6 : MSR

+7 : SCR

+0 : Register Block N,

address 0

+1 : Register Block N,

address 1

+2 : Register Block N,

address 2

+3 : Register Block N,

address 3

+4 : Register Block N,

address 4

+5 : Register Block N,

address 5

+6 : Register Block N,

address 6

+7 : SCE Master Control

Reg.

0x70, 0x74 : Address

Register

0x71, 0x76 : Data Register

0x60 : Data Register

0x64 : Command/Status

Reg.

ISA

CYCLE

TYPE

NOWS

NOWS

NOWS

Std. ISA I/O

NOWS

Note 1: Refer to the configuration register descriptions for setting the base address

Note 2: This chip uses all ISA address bits to decode the base address of each of its logical devices.

29

Page 30

FLOPPY DISK CONTROLLER

The Floppy Disk Controller (FDC) provides the

interface between a host microprocessor and

the Floppy Disk Drives (FDD). The FDC

integrates the functions of the

formatter/controller, Digital Data Separator,

Write Precompensation and data rate Selection

logic for an IBM XT/AT compatible FDC. The

true CMOS 765B core guarantees 100% IBM

PC XT/AT compatibility in addition to providing

data overflow and underflow protection.

TABLE 9 - STATUS, DATA AND CONTROL REGISTERS

FDC PRIMARY BASE I/O

ADDRESS OFFSET R/W REGISTER

0 R Status Register A (SRA)

1 R Status Register B (SRB)

2 R/W Digital Output Register (DOR)

3 R/W Tape Drive Register (TDR)

4 R Main Status Register (MSR)

4 W Data Rate Select Register (DSR)

5 R/W Data (FIFO)

6 Reserved

7 R Digital Input Register (DIR)

7 W Configuration Control Register (CCR)

The FDC is compatible to the 82077AA using

SMSC's proprietary FDC core.

FDC INTERNAL REGISTERS

The FDC contains eight internal registers, which

facilitate the interfacing between the host

microprocessor and the disk drive TABLE 9

shows the addresses required toaccess these

registers. Registers other than the ones shown

are not supported.

STATUS REGISTER A (SRA)

FDC I/O BASE ADDRESS + 0x00

(READ ONLY)

This register is read-only and monitors the state of the FDC Interrupt pin and several disk

interface pins in PS/2 and Model 30 modes. The SRA can be accessed at any time when in PS/2

mode. In the PC/AT mode the data bus pins D0 - D7 are held in a high impedance state for a read of

SRA.

30

Page 31

TABLE 10 - SRB - PS/2 MODEL 30 MODE

7 6 5 4 3 2 1 0

INT

PENDING

RESET

COND.

BIT 0 DIRECTION

Active high status indicating the direction of head movement. A logic "1" indicates inward direction; a

logic "0" indicates outward direction.

BIT 1 nWRITE PROTECT

Active low status of the WRITE PROTECT disk interface input. A logic "0" indicates that the disk is

write protected.

BIT 2 nINDEX

Active low status of the INDEX disk interface input.

BIT 3 HEAD SELECT

Active high status of the HDSEL disk interface input. A logic "1" selects side 1 and a logic "0" selects

side 0.

BIT 4 nTRACK 0

Active low status of the TRK0 disk interface input.

BIT 5 STEP

Active high status of the STEP output disk interface output pin.

0 N/A 0 N/A 0 N/A N/A 0

nDRV2 STEP nTRK0 HDSEL nINDX nWP DIR

BIT 6 nDRV2

Active low status of the DRV2 disk interface input pin, indicating that a second drive has been

installed.

BIT 7 INTERRUPT PENDING

Active high bit indicating the state of the Floppy Disk Interrupt output.

31

Page 32

TABLE 11 - SRA - PS/2 MODEL 30 MODE

7 6 5 4 3 2 1 0

INT

PENDING

RESET

COND.

BIT 0 nDIRECTION

Active low status indicating the direction of head movement. A logic "0" indicates inward direction; a

logic "1" indicates outward direction.

BIT 1 WRITE PROTECT

Active high status of the WRITE PROTECT disk interface input. A logic "1" indicates that the disk is

write protected.

BIT 2 INDEX

Active high status of the INDEX disk interface input.

BIT 3 nHEAD SELECT

Active low status of the HDSEL disk interface input. A logic "0" selects side 1 and a logic "1" selects

side 0.

BIT 4 TRACK 0

Active high status of the TRK0 disk interface input.

BIT 5 STEP

Active high status of the latched STEP disk interface output pin. This bit is latched with the STEP

output going active, and is cleared with a read from the DIR register, or with a hardware or software

reset.

0 0 0 N/A 1 N/A N/A 1

DRQ STEP

F/F

TRK0 NHDSELINDX WP nDIR

BIT 6 DMA REQUEST

Active high status of the FDC’s DRQ output pin.

BIT 7 INTERRUPT PENDING

Active high bit indicating the state of the Floppy Disk Interrupt output.

32

Page 33

DIGITAL OUTPUT REGISTER (DOR)

FDC I/O BASE ADDRESS + 0X02 (READ/WRITE)

The DOR controls the drive select and motor enables of the disk interface outputs. It also contains

the enable for the DMA logic and a software reset bit. The contents of the DOR are unaffected by a

software reset. The DOR can be written to at any time.

TABLE 12 - FDC DOR

7 6 5 4 3 2 1 0

MOT

EN3

RESET

COND.

BIT 0 and 1 DRIVE SELECT

These two bits are binary encoded for the two drive selects output pins nds0 and nds1, thereby

allowing only one drive to be selected at one time.

BIT 2 nreset

A logic “0” written to this bit resets the FDC. This reset will remain active until a logic “1” is written to

this bit. This software reset does not affect the DSR and CCR registers, nor does it affect the other

bits of the DOR register. The minimum reset duration required is 100ns, therefore toggling this bit by

consecutive writes to this register is a valid method of issuing a software reset.

BIT 3 DMAEN

PC/AT and Model 30 Mode: Writing this bit to logic “1” will enable the FDC’s ndack and TC inputs and

enable the FDC’s DRQ and Interrupt outputs. This bit being a logic “0” will disable the FDC’s ndack

and TC inputs, and hold the FDC’s DRQ and Interrupt outputs in a high impedance state. This bit is a

logic “0” after a reset.

PS/2 Mode: In this mode the TC and the FDC’s DRQ, ndack, and Interrupt pins are always enabled.

During a reset, the DRQ, ndack, TC, and Interrupt pins will remain enabled, but this bit will be cleared

to a logic “0”.

MOT

EN2

0 0 0 0 0 0 0 0

MOT

EN1

MOT

EN0

DMAEN nRESETDRIVE

SEL1

DRIVE

SEL0

BIT 4 MOTOR ENABLE 0

This bit controls the nmtr0 disk interface output. A logic “1” in this bit will cause the output pin to

assert.

BIT 5 MOTOR ENABLE 1

This bit controls the nmtr1 disk interface output. A logic “1” in this bit will cause the output pin to

assert.

BIT 6 MOTOR ENABLE 2

This bit controls the nmtr2 disk interface output. A logic “1” in this bit will cause the output pin to

assert.

BIT 7 MOTOR ENABLE 3

This bit controls the nmtr3 disk interface output. A logic “1” in this bit will cause the output pin to

assert.

33

Page 34

TABLE 13 – FDC SRB – PS/2 MODEL 30 MODE

7 6 5 4 3 2 1 0

RESET

nDRV2 nDS1 nDS0 WDATA

F/F

N/A 1 1 0 0 0 1 1

RDATA

F/F

WGATE

F/F

nDS3 nDS2

COND.

TABLE 14 - FDC DOR

7 6 5 4 3 2 1 0

RESET

MOT

EN3

0 0 0 0 0 0 0 0

MOT

EN2

MOT

EN1