Page 1

4-BIT NMOS MICROCONTROLLERS

.LOWCOST

.POWERFUL INSTRUCTIONSET

.2k x8 ROM, 128 x 4 RAM

.23 I/OLINES (ETL9444)

.TRUE VECTORED INTERRUPT, PLUS RES-

TART

.THREE-LEVELSUBROUTINESTACK

.16µs INSTRUCTIONTIME

.SINGLESUPPLYOPERATION(4.5-6.3V)

.LOWCURRENT DRAIN(13mA max.)

.INTERNALTIME-BASECOUNTER FORREAL-

TIMEPROCESSING

.INTERNAL BINARY COUNTER REGISTER

WITHMICROWIRE SERIALI/O CAPABILITY

.GENERALPURPOSE AND TRI-STATE

PUTS

OUT-

.LSTTL/CMOSCOMPATIBLEIN AND OUT

.DIRECTDRIVEOFLEDDIGITAND SEGMENT

LINES

.SOFTWARE/HARDWARE COMPATIBLE

WITHOTHER MEMBERSOF ET9400 FAMILY

.EXTENDED TEMPERATURE RANGE DE-

VICES

ETL9344/L9345 (– 40°Cto+85°C)

.WIDERSUPPLYRANGE (4.5 – 9.5V)

OPTIONALLY AVAILABLE

.SOIC 24/28 AND PLCC 28 PACKAGES AVAI-

LABLE

DESCRIPTION

The ETL9444/L9445 and ETL9344/L9345 SingleChip N-Channel Microcontrollers are fully compatible with the COPS family, fabricated using

N-channel,silicongateXMOStechnology. Theyare

complete microcomputers containing all system timing, internal logic,ROM, RAMand I/O necessary

to implement dedicated control functionsin avariety

of applications. Featuresinclude single supply operation,avarietyof outputconfiguration options, with

an instruction set, internal architecture and I/O

scheme designed to facilitate keyboard input, display output and BCD data manipulation. The

ETL9445isidenticalto theETL9444, exceptwith19

I/O lines instead of 23 : They are an appropriate

choicefor use innumerous humaninterface control

environments. Standard test procedures and reliable high-density fabrication techniques provide the

medium to large volume customerswith a customi-

ETL9444/ETL9445

ETL9344/ETL9345

ETL9444/ETL9344

N

(PlasticPackage)

ETL93 45/ETL9345

N

(PlasticPackage)

PIN CONNECTION

May1989

1/27

Page 2

ETL9444/9445–ETL9344/9345

zed controller oriented processor at a low end-product cost.

Figure 1 : BlockDiagram (28-pin version).

The ETL9344/L9345 are exact functional equivalents, but extended temperature range versions of

theETL9444/L9445 respectively.

2/27

Page 3

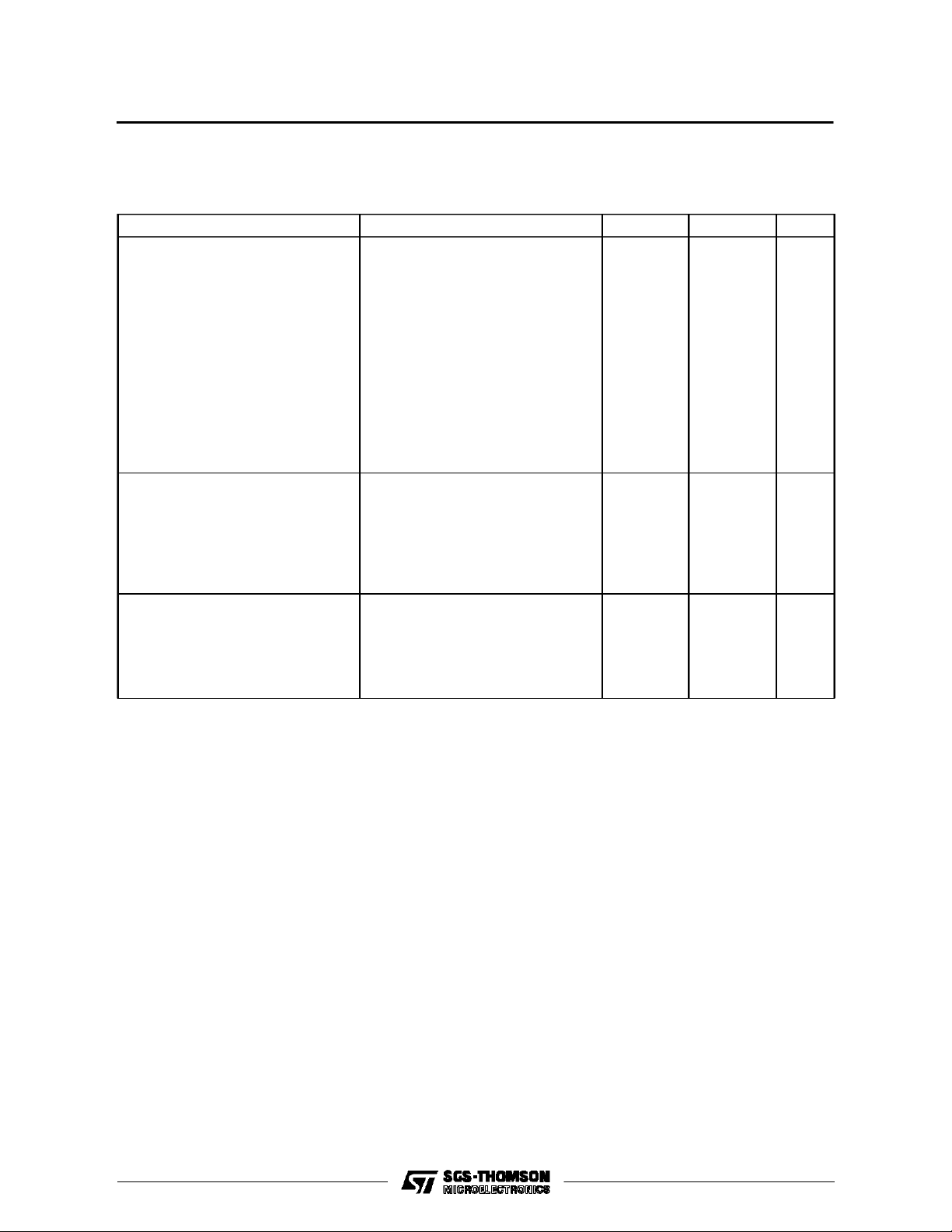

ETL9444/9445–ETL9344/9345

ETL944 4/L9445

ABSOLUTE M AXI MUM RATI NG S

Symbol Paramet e r Valu e Unit

Voltage at any Pin Relative to GND – 0.5 to + 10 V

Ambient Operating Temperature 0 to + 70 °C

Ambient Storage Temperature – 65 to + 150 °C

Lead Temperature (soldering, 10 seconds) 300 °C

Power Dissipation 0.75W at 25°C

0.4W at 70°C

Total Source Current 120 mA

Total Sink Current 120 mA

Absolute maximum ratings indicate limits beyond whichdamage to the device mayoccur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

DC ELECTRICAL CHARACTERISTICS 0°C ≤TA≤ +70°C, 4.5V ≤ VCC≤ 9.5V

(unless otherwise specified)

Parameter Test Conditions Min. Max. Unit

Standard Operating Voltage (V

Optional Operating Voltage (V

Power Supply Ripple

Operating Supply Current

Input Voltage Levels

CKI Input Levels

Crystal Input (÷ 32, ÷ 16, ÷ 8)

Logic High (V

Logic Low (V

)

IH

)

IL

Schmitt Trigger Input (÷ 4)

Logic High (VIH)

Logic Low (V

)

IL

RESET Input Levels

Logic High

Logic Low

SO Input Level (test mode)

All Other Inputs

Logic High

Logic High

Logic Low

Logic High

Logic Low

Input Capacitance

Hi-Z Input Leakage

Output Voltage Levels

LSTTL Operation

Logic High (V

OH

)

Logic Low (VOL)

CMOS Operation

Logic High

Logic Low

Note : 1. VCCvoltagechange must be less than 0.5V in a 1ms period to maintain proper operation.

CC

CC

)

Note 1

)

Peak to Peak

All Inputs and Outputs Open

Schmitt Trigger Input

V

= Max.

CC

With TTL trip level options

selected, V

CC

With high trip level options

selected.

VCC=5V±5%

IOH=–25µA

IOL= 0.36mA

I

=–10µA

OH

IOL=+10µA

=5V±5%.

4.5

4.5

2.0

– 0.3

0.7 V

CC

– 0.3

0.7 V

CC

– 0.3

2.0

3.0

2.0

– 0.3

3.6

– 0.3

–1

2.7

VCC–1

6.3

9.5

0.5

13

0.4

0.6

0.6

2.5

0.8

1.2

7

+1

0.4

0.2

V

V

V

mA

V

V

V

V

V

V

V

V

V

V

V

V

pF

µA

V

V

V

V

3/27

Page 4

ETL9444/9445–ETL9344/9345

ETL944 4/L9445

DC ELECTRICAL CHARACTERISTICS (continued)

Parameter Test Conditions Min. Max. Unit

Output Current Levels

Output Sink Current

SO and SK Outputs (I

L

Outputs and Standard

0-L7

G

0-G3,D0-D3

Outputs (IOL)

OL

)

G0-G3and D0-D3Outputs with

High Current Options (I

G

and D0-D3Outputs with

0-G3

OL

)

Very High Current Options (IOL)

CKI (single-pin RC oscillator)

CKO

Output Source Current

Standard Configuration,

All Outputs (I

OH

)

Push-pull Configuration

SO and SK Outputs (I

LED Configuration, L0-L

OH

)

7

Outputs, Low Current

Driver Option (IOH)

LED Configuration, L

0-L7

Outputs, High Current

Driver Option (IOH)

TRI-STATE Configuration,

L

Outputs, Low

0-L7

Current Driver Option (I

OH

)

TRI-STATE Configuration,

L0-L7Outputs, High

Current Driver Option (I

OH

)

Input Load Source Current

CKO Output

RAM Power Supply Option

Power Requirement V

TRI-STATE Output Leakage

Current – 2.5 + 2.5

Total Sink Current Allowed

All Outputs Combined

D, G Ports

L

7-L4

L3-L

0

All Other Pins

Total Source Current Allowed

All I/O Combined

L

7-L4

L3-L

0

Each L Pin

All Other Pins

V

= 9.5V, VOL= 0.4V

CC

VCC= 6.3V, VOL= 0.4V

V

= 4.5V, VOL= 0.4V

CC

VCC= 9.5V, VOL= 0.4V

V

= 6.3V, VOL= 0.4V

CC

VCC= 4.5V, VOL= 0.4V

VCC= 9.5V, VOL= 1.0V

V

= 6.3V, VOL= 1.0V

CC

VCC= 4.5V, VOL= 1.0V

V

= 9.5V, VOL= 1.0V

CC

VCC= 6.3V, VOL= 1.0V

VCC= 4.5V, VOL= 1.0V

V

= 4.5V, VIH= 3.5V

CC

VCC= 4.5V, VOL= 0.4V

V

= 9.5V, VOH= 2.0V

CC

VCC= 6.3V, VOH= 2.0V

V

= 4.5V, VOH= 2.0V

CC

VCC= 9.5V, VOH= 4.75V

V

= 6.3V, VOH= 2.4V

CC

VCC= 4.5V, VOH= 1.0V

V

= 9.5V, VOH= 2.0V

CC

VCC= 6.0V, VOH= 2.0V

V

= 9.5V, VOH= 2.0V

CC

VCC= 6.0V, VOH= 2.0V

V

= 9.5V, VOH= 5.5V

CC

VCC= 6.3V, VOH= 3.2V

V

= 4.5V, VOH= 1.5V

CC

VCC= 9.5V, VOH= 5.5V

VCC= 6.3V, VOH= 3.2V

V

= 4.5V, VOH= 1.5V

CC

VCC= 5.0V, VIL=0V

= 3.3V 6.0

R

1.8

1.2

0.9

0.8

0.5

0.4

15

11

7.5

30

22

15

2

0.2

–140

–75

–30

– 1.4

– 1.4

– 1.2

– 1.5

– 1.5

– 3.0

– 3.0

– 0.75

– 0.8

– 0.9

– 1.5

– 1.6

– 1.8

–10

–800

–480

–250

–140

–18

–13

–35

–25

120

120

4

4

1.5

120

60

60

30

1.5

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

µA

µA

µA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

µA

mA

µA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

4/27

Page 5

ETL9444/9445–ETL9344/9345

ETL934 4/L9345

ABSOLUTE M AXI MUM RATI NG S

Symbol Paramet e r Valu e Unit

Voltage at any Pin Relative to GND – 0.5 to + 10 V

Ambient Operating Temperature – 40 to + 85 °C

Ambient Storage Temperature – 65 to + 150 °C

Lead Temperature (soldering, 10 seconds) 300 °C

Power Dissipation 0.75W at 25°C

0.25W at 85°C

Total Source Current 120 mA

Total Sink Current 120 mA

Absolute maximum ratings indicate limits beyond whichdamage to the device mayoccur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

DC ELECTRICAL CHARACTERISTICS –40°C≤TA≤+85°C, 4.5V ≤ VCC≤ 7.5V

(unless otherwise specified)

Parameter Test Conditions Min. Max. Unit

Standard Operating Voltage (V

Optional Operating Voltage (V

Power Supply Ripple

Operating Supply Current

Input Voltage Levels

CKI Input Levels

Crystal Input

Logic High (V

Logic Low (V

)

IH

)

IL

Schmitt Trigger Input

Logic High (VIH)

Logic Low (V

)

IL

RESET Input Levels

Logic High

Logic Low

SO Input Level (test mode)

All Other Inputs

Logic High

Logic High

Logic Low

Logic High

Logic Low

Input Capacitance

Hi-Z Input Leakage

Output Voltage Levels

LSTTL Operation

Logic High (V

OH

)

Logic Low (VOL)

CMOS Operation

Logic High

Logic Low

Note : 1. VCCvoltagechange must be less than 0.5V in a 1ms period to maintain proper operation.

CC

CC

)

Note 1

)

Peak to Peak

All Inputs and Outputs Open

Schmitt Trigger Input

V

= Max.

CC

With TTL trip level options

selected, V

CC

With high trip level options

selected

VCC=5V±5%

IOH=–20µA

IOL= 0.36mA

I

=–10µA

OH

IOL=+10µA

=5V±5%

4.5

4.5

2.2

– 0.3

0.7 V

CC

– 0.3

0.7 V

CC

– 0.3

2.2

3.0

2.2

– 0.3

3.6

– 0.3

–2

2.7

VCC–1

5.5

7.5

0.5

15

0.3

0.4

0.4

2.5

0.6

1.2

7

+2

0.4

0.2

V

V

V

mA

V

V

V

V

V

V

V

V

V

V

V

V

pF

µA

V

V

V

V

5/27

Page 6

ETL9444/9445–ETL9344/9345

ETL934 4/L9345

DC ELECTRICAL CHARACTERISTICS (continued)

Parameter Test Conditions Min. Max. Unit

Output Current Levels

Output Sink Current

SO and SK Outputs (I

L

Outputs and Standard

0-L7

G

0-G3,D0-D3

G

and D0-D3Outputs with

0-G3

Outputs (IOL)

OL

)

High Current Options (IOL)

G

and D0-D3Outputs with

0-G3

Very High Current Options (IOL)

CKI (single-pin RC oscillator)

CKO

Output Source Current

Standard Configuration,

All Outputs (I

OH

)

Push-pull Configuration

SO and SK Outputs (I

LED Configuration, L

OH

0-L7

)

Outputs, Low Current

Driver Option (IOH)

LED Configuration, L

0-L7

Outputs, High Current

Driver Option (IOH)

TRI-STATE Configuration,

L

Outputs, Low

0-L7

Current Driver Option (I

OH

)

TRI-STATE Configuration,

L0-L7Outputs, High

Current Driver Option (I

OH

)

Input Load Source Current

CKO Output

RAM Power Supply Option

Power Requirement V

TRI-STATE Output Leakage

Current –5 +5

Total Sink Current Allowed

All Outputs Combined

D. G Ports

L

7-L4

L3-L

0

All Other Pins

Total Source Current Allowed

All I/O Combined

L

7-L4

L3-L

0

Each L Pin

All Other Pins

V

= 7.5V, VOL= 0.4V

CC

V

= 5.5V, VOL= 0.4V

CC

VCC= 4.5V, VOL= 0.4V

VCC= 7.5V, VOL= 0.4V

V

= 5.5V, VOL= 0.4V

CC

VCC= 4.5V, VOL= 0.4V

V

= 7.5V, VOL= 1.0V

CC

VCC= 5.5V, VOL= 1.0V

VCC= 4.5V, VOL= 1.0V

V

= 7.5V, VOL= 1.0V

CC

VCC= 5.5V, VOL= 1.0V

V

= 4.5V, VOL= 1.0V

CC

VCC= 4.5V, VIH= 3.5V

VCC= 4.5V, VOL= 0.4V

V

= 7.5V, VOH= 2.0V

CC

V

= 5.5V, VOH= 2.0V

CC

VCC= 4.5V, VOH= 2.0V

VCC= 7.5V, VOH= 3.75V

V

= 5.5V, VOH= 2.0V

CC

VCC= 4.5V, VOH= 1.0V

V

= 7.5V, VOH= 2.0V

CC

VCC= 6.0V, VOH= 2.0V

VCC= 5.5V, VOH= 2.0V

V

= 7.5V, VOH= 2.0V

CC

VCC= 6.0V, VOH= 2.0V

VCC= 5.5V, VOH= 2.0V

V

= 7.5V, VOH= 4.0V

CC

VCC= 5.5V, VOH= 2.7V

V

= 4.5V, VOH= 1.5V

CC

VCC= 7.5V, VOH= 4.0V

VCC= 5.5V, VOH= 2.7V

V

= 4.5V, VOH= 1.5V

CC

VCC= 5.0V, VIL=0V

= 3.3V 8.0

R

1.4

1.0

0.8

0.6

0.5

0.4

12

9

7

24

18

14

2

0.2

–100

–55

–28

– 0.85

– 1.1

– 1.2

– 1.4

– 1.4

– 0.7

– 2.7

– 2.7

– 1.4

– 0.7

– 0.6

– 0.9

– 1.4

– 1.2

– 1.8

–10

–900

–600

–350

–200

–27

–17

–15

–54

–34

–30

120

120

4

4

1.5

120

60

60

30

1.5

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

µA

µA

µA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

µA

mA

µA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

6/27

Page 7

ETL9444/9445–ETL9344/9345

AC ELECTRICAL CHARACTERISTICS

ETL9444/L9445 : 0°C ≤ TA≤ +70°C, 4.5V ≤ VCC≤9.5V (unless otherwise specified)

ETL9344/L9345 : –40°C≤TA≤+85°C, 4.5V ≤ VCC≤7.5V (unless otherwise specified)

Parameter Test Conditions Min. Max. Unit

Instruction Cycle Time – t

c

CKI

Input Frequency – f

I

Duty Cycle

Rise Time

Fall Time

CKI Using RC (÷ 4)

Instruction Cycle Time

CKO as SYNC Input

t

SYNC

INPUTS :

IN

-IN0,G3-G0,L7-L

3

t

SETUP

t

HOL D

0

SI

t

SETUP

t

HOL D

OUTPUT PROPAGATION DELAY

SO, SK Outputs

t

pd1,tpd0

All Other Outputs

t

pd1,tpd0

÷ 32 Mode

÷ 16 Mode

÷ 8Mode

÷4Mode

f

= 2MHz

I

R = 56kΩ ± 5%

C=100pF±10%

Test Condition :

CL= 50pF, RL= 20kΩ,V

OUT

= 1.5V

16

0.8

0.4

0.2

0.1

30

16

400

40

2.0

1.0

0.5

0.25

60

120

80

28

8.0

1.3

2.0

1.0

4.0

5.6

µs

MHz

MHz

MHz

MHz

%

ns

ns

µs

ns

µs

µs

µs

µs

µs

µs

7/27

Page 8

ETL9444/9445–ETL9344/9345

Figure 2 : Connection Diagrams.

Pin Description

L

7-L0

G

3-G0

D

3-D0

IN

-IN

3

SI Serial Input (or counter input)

SO Serial Output (or general purpose output)

SK Logic-controlled Clock (or general purpose output)

CKI System Oscillator Input

CKO System Oscillator Output (or general purpose input, RAM power supply, or SYNC input)

RESET System Reset Input

V

CC

GND Ground

8 Bidirectional I/O Ports with TRI-STATE

4 Bidirectional I/O Ports

4 General Purpose Outputs

4 General Purpose Inputs (COP444L only)

0

Power Supply

Figure 3 : Input/output Timing Diagrams (crystal divide-by-16 mode).

8/27

Page 9

Figure 3a: Synchronization Timing.

ETL9444/9445–ETL9344/9345

FUN CTI ON AL DESCRIPTI ON

A blockdiagram ofthe ETL9444is given in figure 1.

Data pathsare illustratedinsimplified formto depict

how the various logic elements communicate with

eachotherin implementing the instructionsetof the

device. Positive logic is used. Whena bit is set,it is

a logic”1”(greater than 2volts).Whena bit isreset,

it is a logic ”0” (less than 0.8volts).

Allfunctional referencesto theETL9444/L9445 also

apply tothe ETL9344/L9345.

PROGRAM MEMORY

Program Memory consists ofa 2048 byteROM. As

can be seen by an examination of the

ETL9444/L9445 instructionset,thesewordsmaybe

programinstructions, programdataorROMaddressingdata.Becauseof thespecialcharacteristics associated with the JP, JSRP, JID, and LQID

instructions,ROMmust oftenbe thoughtofas being

organized into 32 pages of 64 wordseach.

ROM addressing isaccomplishedby a11-bit PCregister. Its binaryvalueselects oneof the 2048 8-bit

words contained in ROM. A newaddress is loaded

into the PC register during each instruction cycle.

Unlesstheinstruction isa transfer of controlinstruction, thePC registeris loaded withthenext sequential 11-bit binary count value. Three levels of

subroutine nesting are implemented by the 11-bit

subroutine save registers, SA, SB, and SC ; providing a last-in, first-out (LIFO)hardware subroutine

stack.

ROM instruction words are fetched, decoded and

executed by the Instruction Decode, Control and

Skip Logiccircuitry.

DATA MEMORY

Data memoryconsistsof a 512-bit RAM,organized

as 8 data registers of 16 4-bit digits. RAM addressing is implemented by a 7-bit B register whose upper 3 bits (Br) select1 of 8 data registers andlower

4 bits (Bd) select 1 of 16 4-bit digitsin theselected

dataregister.Whilethe4-bit contentsofthe selected

RAM digit (M) is usually loaded into or from, or exchanged with, the A register (accumulator), it may

also be loaded into or fromthe Qlatches or loaded

fromthe L ports. RAM addressing may alsobe performeddirectlybythe LDDandXADinstructionsbased upon the 7-bit contents of the operand field of

these instructions. The Bd registeralso serves asa

source register for 4-bit data sent directly to the D

outputs.

INTERNALLOGIC

The 4-bit Aregister(accumulator) isthe source and

destination register for most I/O, arithmetic, logic

and datamemoryaccess operations. Itcan alsobe

usedto loadtheBr andBdportions oftheB register,

to load and input 4 bitsof the 8-bitQ latch data, to

input 4bitsof the8-bit L I/Oportdataandto perform

data exchanges with the SIO register.

A4-bitadderperforms thearithmetic andlogicfunctions,storing its results in A. It also outputs a carry

bitto the 1-bitC register, mostoftenemployed toindicate arithmetic overflow. The C register, in

conjunction with the XAS instruction and the ENregister, also serves to control the SK output. C can

be outputted directly to SK or can enableSK to be

a sync clockeach instructioncycle time. (See XAS

instruction andEN register description, below).

Four general-purpose inputs, IN3-IN0, are provided.

The D register provides 4 general-purpose outputs

and is used as the destination register for the 4-bit

contents of Bd. The D outputs can be directly

connectedtothe digitsofa multiplexed LED display.

The G register contents are outputs to 4 generalpurpose bidirectional I/O ports. G I/O ports can be

directly connected tothe digits ofa multiplexedLED

display.

The Q register is an internal, latched, 8-bit register,

usedto hold data loaded to or fromM and A,aswell

as 8-bit data from ROM. Its contentsare output to

theL I/OportswhentheLdriversareenabledunder

program control(See LEIinstruction).

9/27

Page 10

ETL9444/9445–ETL9344/9345

The 8 L drivers,when enabled, outputthe contents

of latched Q data to the L I/O ports. Also, the

contents of L may be read directly into A and M. L

I/O ports canbe directlyconnected tothe segments

of a multiplexed LED display (usingthe LED Direct

Drive output configuration option) withQdata being

outputted totheSa-Sganddecimalpointsegments

of the display.

The SIOregisterfunctionsas a 4-bit serial-in/serialout shift register or as a binary counter depending

on thecontentsof the ENregister. (See ENregister

description, below). Its contents can be exchanged

with A, allowing itto inputor output acontinuous serial data stream, SIO may also be used to provide

additional parallel I/O by connecting SO to external

serial-in/parallel-out shift registers.

The XASinstruction copiesC into the SKLlatch. In

the counter mode, SK is the output of SKL ; in the

shiftregistermode, SKoutputsSKLANDedwiththe

clock.

The EN register is an internal 4-bit register loaded

under program control by the LEI instruction. The

state of each bitof thisregister selectsor deselects

the particularfeature associated witheach bitof the

EN register (EN3-EN0).

1. The least significant bit of the enable register,

EN0,selectstheSIOregisteraseithera4-bitshift

register or a 4-bit binary counter. With EN0set,

SIO is an asynchronous binary counter,decrementing its value by one upon each low-going

pulse (”1” to ”0”)ocurring on the SI input. Each

pulse must be at least two instruction cycles

wide. SKoutputs thevalue of SKL.The SO output isequal to thevalue of EN3. WithEN0reset,

SIO is a serial shift register shifting left each instructioncycletime.The data present atSI goes

intotheleastsignificantbit of SIO.SOcan beenabled to output the most significant bit of SIO

each cycle time. (See 4 below). The SK output

becomesa logic-controlled clock.

2. With EN1set the IN1input is enabled as an interrupt input. Immediately following an interrupt,

EN1is resetto disable furtherinterrupts.

3. With EN2set,the L driversare enabledto output

the datainQto theLI/O ports.ResettingEN2disables the L drivers, placing theL I/O ports in a

high-impedance input state.

4. EN3, inconjunction withEN0, affects theSO output. With EN0set (binary counter option selected) SO will output the value loaded into EN3.

WithEN0reset(serial shiftregister option selected),settingEN3enablesSO astheoutputof the

SIO shift register, outputting serial shifted data

eachinstructiontime. ResettingEN3withthe serial shift register option selecteddisables SO as

the shift register output ; data continues to be

shiftedthrough SIOand can be exchanged with

A viaan XAS instruction butSOremains reset to

”0”. Thetable below provides asummary of the

modesassociated with EN3andEN0.

Enable Register Modes - Bits EN3and EN

EN

EN

3

0

1

0

1

0

0

0

1

1

SIO S I SO SK

Shift Register

Shift Register

Binary Counter

Binary Counter

Input to Shift Register

Input to Shift Register

Input to Binary Counter

Input to Binary Counter

0

INTERRUPT

The following features are associated with the IN1

interrupt procedure and protocolandmustbeconsidered bythe programmer when utilizing interrupts.

a. The interrupt, once acknowledged as explained

below, pushes the next sequential program

counter address (PC+1)ontothestack,pushing

in turnthe contents ofthe other subroutine-save

registers to the next lower level

(PC + 1 → SA → SB → SC). Any previous

contents of SC are lost.The program counteris

10/27

0

Serial Out

0

1

If SKL = 1, SK = Clock

If SKL = 0, SK = 0

If SKL = 1, SK = Clock

If SKL = 0, SK = 0

If SKL = 1, SK = 1

If SKL = 0, SK = 0

If SKL = 1, SK = 1

If SKL = 0, SK = 0

set tohex address 0FF (the lastword of page3)

and EN1isreset.

b. An interrupt willbe acknowledged onlyafter the

followingconditions are met :

1. EN1hasbeen set.

2. A low-going pulse (”1” to ”0”) at least two in-

structioncycles wideoccurs onthe IN1input.

3. A currently executing instruction has been

completed.

Page 11

ETL9444/9445–ETL9344/9345

4. All successive transfer of control instructions

and successive LBIs have been completed

(e.g.,if themainprogram isexecutingaJP instruction which transfers program control to

anotherJPinstruction,theinterrupt willnotbe

acknowledged untilthesecondJPinstruction

hasbeen executed.

c. Upon acknowledgement of aninterrupt, the skip

logicstatusissavedandlater restored uponpoppingof thestack.For example, ifan interrupt occurs during the execution of ASC (Add with

Carry, Skipon Carry) instructionwhichresultsin

carry,the skiplogicstatus issavedand program

control is transferred to the interrupt servicing

routineat hex address 0FF.Atthe endof the interrupt routine, a RET instruction is executed to

”pop”thestack and return programcontrolto the

instruction following the original ASC. At this

time,the skip logic is enabled and skips this instruction because of the previous ASC carry.

Subroutines andLQIDinstructionsshould not be

nested withinthe interrupt service routine, since

theirpoppingthe stackwillenable anypreviously

saved main program skips, interfering with the

orderlyexecution ofthe interrupt routine.

d. The firstinstructionof the interrupt routine athex

address 0FF must be a NOP.

e. A LEI instructioncan be put immediately before

the RETto re-enable interrupts.

INITIALIZATION

TheResetLogicwillinitialize(clear)thedeviceupon

power-up if the power supply rise time is less than

1ms and greater than 1µs. If the power supply rise

timeisgreaterthan 1ms,the useruseprovidean external RC network and diodeto the RESET pin as

shownbelow.If theRC networkis notused,theRESET pin must be pulled up to VCCeither by the internalload orbyan externalresistor (≥40kΩ)toVCC.

TheRESETpinis configured asaSchmitttriggerinput. Initialization will occur whenever a logic ”0” is

appliedto theRESETinput, providedit stays lowfor

at least three instructioncycle times.

Pow e r -up Cl ear Cir cu it.

Upon initialization, the PC register is cleared to 0

(ROM address 0) andthe A,B, C, D, EN, andG registersare cleared. The SK outputis enabled as a

SYNCoutput,providing apulse each instructioncycle time.DataMemory (RAM)is notcleared uponinitialization. The first instruction at address 0 must

be a CLRA.

OSCILLATOR

Thereare threebasic clockoscillator configurations

available as shown by figure4.

a. Crystal Controlled Oscillator. CKI and CKO

areconnected to anexternal crystal.Theinstructioncycle time equals thecrystal frequency dividedby 32(optional by 16or 8).

b. External Oscillator. CKIis an external clockin-

put signal. The external frequency is divided by

32(optionalby 16or 8) togivethe instructioncycletime. CKO isnow available tobe usedas the

RAM power supply (VR), as a general purpose

input, or as a SYNCinput.

c. RCControlled Oscillator. CKIis configured as

a single pin RC controlled Schmitt trigger oscillator.The instruction cycleequals theoscillation

frequency divided by 4. CKO is availableas the

RAMpower supply (VR) oras ageneralpurpose

input.

11/27

Page 12

ETL9444/9445–ETL9344/9345

Figure 4 : ETL9444/L9445 Oscillator.

CRYSTAL OSCILLATOR

Crystal Component Values

Value R1 (Ω) R2 (Ω) C1 (pF) C2 (pF)

455kHz

2.097MHz

4.7k

1k

1M

1M

220

30

220

6-36

CKO PIN OPTIONS

Inacrystalcontrolledoscillator system,CKOisused

as an output to the crystal network. As an option

CKO can bea SYNCinput as described above. As

anotheroptionCKO canbe ageneralpurpose input,

read intobit 2 of A(accumulator) upon executionof

an INILinstruction. As anotheroption, CKOcan be

a RAM power supply pin (VR), allowing its connection to a standby/backup power supply to maintain

the integrityof RAMdatawithminimum power drain

when themain supplyisinoperative or shutdown to

conserve power. Using either option is appropriate

in applicationswheretheETL9444/L9445 systemtiming configuration doesnot requireuse ofthe CKO

pin.

I/O OPTIONS

ETL9444/L9445 outputs havethe followingoptional

configurations, illustrated in figure5.

a. Standard - an enhancement mode device to

groundinconjunction withadepletion-mode deviceto VCC, compatible with LSTTL andCMOS

inputrequirements. Available on SO,SK,andall

D and G outputs.

RC C ONTROLLED OSCILLATO R

R (kΩ) C (pF)

51

82

Note : 200kΩ ≥ R ≥ 25kΩ

360pF≥ C ≥ 50pF

100

56

Instruction Cycle

Time (µs)

19 ± 15%

19 ± 13%

b. Open-Drain - an enhancement-mode device to

ground only, allowing external pull-up as required by the user’s application. Available on SO,

SK, andall Dand G outputs.

c. Push-Pull - An enhancement-mode device to

groundin conjunction witha depletion-mode deviceparalleled byanenhancement-mode device

to VCC. This configuration has been provided to

allowfor fast riseand falltimes whendriving capacitiveloads. Available on SO and SK outputs

only.

d. Standard L - same as a., but may be disabled.

Available on L outputsonly.

e. OpenDrainL -sameas b.,butmay bedisabled.

Available on L outputsonly.

f. LEDDirect Drive - anenhancement-mode de-

vice to ground and to VCC, meeting the typical

current sourcing requirements of the segments

of an LEDdisplay. Thesourcing device is clamped to limit currentflow. These devices maybe

turnedoffunderprogram control (See Functional

Description, EN Register),placing theoutputsin

a high-impedance stateto provide required LED

12/27

Page 13

ETL9444/9445–ETL9344/9345

segment blankingfora multiplexeddisplay. Availableon L outputsonly.

g. TRI-STATEPush-Pull - an enhancement-

mode device to ground and VCC. Theseoutputs

are TRI-STATEoutputs, allowing for connection

of these outputsto a data bus shared by other

bus drivers. Available on L outputs only.

ETL9444, L9445 inputshave thefollowingoptional configurations :

h. An on-chip depletionload device to VCC.

i. A Hi-Zinput which must bedriven toa”1” or ”0”

by external components.

The above input and output configurations share

common enhancement-mode and depletion-mode

devices. Specifically, all configurations use one or

more of six devices (numbered 1-6, respectively).

Minimum and maximum current (I

OUT

and V

OUT

curvesaregiveninfigure6foreachofthesedevices

to allow the designer to effectively use these I/O

configurationsin designing a system.

The SO,SK outputscan be configured asshownin

a., b., orc. The D and Goutputs can be configured

as shownin a. or b. Note that when inputting data

to the G ports, the G outputs should be set to ”1”.

The L outputs canbe configured asind., e.,f.org.

An important point to remember if using configuration d.orf. with the L driversis thateven when the

L driversare disabled, the depletion load devicewill

source a small amountof current(see figure 6, device 2) ; however,when the L-lines are used as inputs,the disableddepletiondevice cannotbe relied

onto sourcesufficientcurrenttopullan inputto logic

”1”.

RAMKEEP-ALIVE OPTION

Selecting CKO as the RAM power supply (VR) al-

lowsthe usertoshut offthechippowersupply(VCC)

and maintain data in the RAM.

Toinsure thatRAM dataintegrity is maintained, the

following conditions must be met :

1. RESETmust golow before VCCgoeslow during

poweroff; VCCmustgohighbefore RESETgoes

high onpower-up.

2. VRmust be within the operating range of the

chip,and equalto VCC± 1V during normal operation.

3. VRmustbe ≥ 3.3V with VCCoff.

ETL9445

If the ETL9444 ls bonded as a 24-pin device, it be-

comesthe ETL9445, illustratedinfigure2,ETL9444

Connection Diagrams.Note that theETL9445 does

notcontain thefour general purpose IN inputs (IN3IN0). Use ofthis option precludes,of course, use of

theIN options andthe interrupt feature, whichuses

IN1. Allother options are availablefor theETL9445.

13/27

Page 14

ETL9444/9445–ETL9344/9345

Figure 5 : OutputConfigurations.

14/27

Page 15

Figure 6 : ETL9444/L9445 Input/output Characteristics.

ETL9444/9445–ETL9344/9345

15/27

Page 16

ETL9444/9445–ETL9344/9345

Figure 6a: ETL9444/L9445 Input/output Characteristics.

16/27

Page 17

Figure 6b : ETL9344/L9345 Input/output Characteristics.

ETL9444/9445–ETL9344/9345

17/27

Page 18

ETL9444/9445–ETL9344/9345

ETL944 4/L9445, ETL9344/L9345 INSTR U C TION SET

Table1 isasymbol tableproviding internalarchitecture,instructionoperandand operationalsymbolsu-

Table 2provides the mnemonic, operand, machine

code,data flow,skipconditions, anddescription associated with each instruction in the

ETL9444/L9445 instructionset.

sed in the instructionsettable.

Table 1 : ETL9444/9445 ETL9344/9345 Instruction SetTable Symbols.

INTERNAL ARCHITECTURE SYMBOLS

Symbol Definition

A

4-bit Accumulator

B

7-bit RAM Address Register

Br

Upper 3 Bits of B (register address)

Bd

EN

PC

SA

SB

SC

SIO

SK

Lower 4 Bits of B (digit address)

C

1-bit Carry Register

D

4-bit Data Output Port

4-bit Enable Register

G

4-bit Register to Latch Data for G I/O Port

IL

Two 1-bit latches associatedwith the IN

or IN0inputs.

IN

4-bit Input Port

L

8-bit TRI-STATE I/O Port

M

4-bit contents of RAM memory pointed to

by B register.

11-bit ROM Address Register (program

counter)

Q

8-bit Register to Latch Data for L I/O Port

11-bit Subroutine Save Register A

11-bit Subroutine Save Register B

11-bit Subroutine Save Register C

4-bit Shift Register and Counter

Logic-controlledClock Output

3

INSTRUCTION OPERAND SYMBOLS

Symbol Definition

d

4-bit Operand Field, 0-15 Binary (RAM

digit select)

r

3-bit Operand Field, 0-7 Binary (RAM

register select)

a

11-bit Operand Field, 0-2047 Binary

(ROM address)

y

4-bit Operand Field, 0-15 Binary

(immediate data)

RAM(s)

ROM(t)

Contents of RAM location addressed by s.

Contents of ROM location addressed by t.

OPERATIONAL SYMBOLS

Symbol Definition

+

Plus

-

Minus

➞

Replaces

↔

Is exchangedwith.

=

Is equal to.

A

The one’s complementof A.

⊕

Exclusive-OR

:

Range of Values

18/27

Page 19

Table 2 : ETL9444/L9445 Instruction Set.

ARITHMETIC INSTRUCTIONS

ETL9444/9445–ETL9344/9345

Machine

Mnem Operand

Hex

Code

Language

Code

(binary)

ASC 30 |0011|0000|

ADD 31 |0011|0001|

ADT 4A |0100|1010|

AISC y 5- | 0 1 0 1 | y |

CASC 10 |0001|0000|

CLRA 00 | 0 0 0 0 | 0 0 0 0 |

COMP 40 | 0 1 0 0 | 0 0 0 0 |

NOP 44 |0100|0100|

RC 32 |0011|0010|

SC 22 |0010|0010|

XOR 02 |0000|0010|

_______________

_______________

_______________

_______________

_______________

_______________

_______________

_______________

_______________

_______________

_______________

TRANSFER OF CONTROL INSTRUCTIONS

Machine

Mnem Operand

Hex

Code

JID FF | 1 1 1 1 | 1 1 1 1 |

Language

Code

(binary)

_________________

Data Fl ow

A + C + RAM(B) → A

Carry → C

Skip

Conditions

Descriptio n

Carry Add with Car ry Skip on

Carry

A + RAM(B) → A None Add RAM to A

A+10

→ A None Add Ten to A

10

A+y→A Carry Add Immediate Skip on

Carry (y ≠ 0)

A + RAM(B) + C → A

Carry → C

Carry Complement a nd Add with

Carry, Skip on Carr y

0 → A None Clear A

A → A None Ones Complement of A to A

None None No Operation

”0” → C None Reset C

”1” → C None Set C

A ⊕ RAM(B) → A None Exclusive-OR Ram with A

Data Flow

ROM (PC

→ PC

7:0

10:8

A, M)

Skip

Conditions

Descriptio n

None Jump Indirect (n ot e 3)

JMP a 6– |0110|0| a

JP a | 1 | a

_________________

| a

_________________

_________________

|

7:0

|

6:0

10:8

(pages 2, 3 only)

or

|11| a

_________________

5:0

|

(all other pages)

JSRP a | 1 0 | a

JSR a 6– | 0 1 1 0 | 1 | a

RET 48 | 0 1 0 0 | 1 0 0 0 |

RETSK 49 | 0 1 0 0 | 1 0 0 1 |

_________________

_________________

| a

_________________

_________________

_________________

5:0

10:8

|

7:0

|

A → PC None Jump

|

A → PC

A → PC

6:0

5:0

PC+ 1 → SA→ SB → SC

00010 → PC

a→ PC

PC+ 1

|

10:6

5:0

→ SA→ SB→ SC

None Jump within Page (note 4)

None Jump to Subroutine Page

(note 5)

None Jump to Subroutine

a → PC

SC → SB → SA → PC None R eturn from Subroutine

SC → SB → SA → PC Always

Skip on

Return f rom Subroutine

then Skip

Return

19/27

Page 20

ETL9444/9445–ETL9344/9345

MEMORYREFERENCE INSTRUCTIONS

Machi n e

Mnem Operand

Hex

Code

CAMQ 333C|0011|0011|

CQMA 332C|0011|0011|

LD r –5 | 00|r|0101|

LDD r.d 23 | 0 0 1 0 | 0 0 1 1 |

LQID BF | 1 0 1 1 | 1 1 1 1 |

RMB 0

1

2

3

SMB 0

1

2

3

4C

45

42

43

4D

47

46

4B

STII y 7– | 0 1 1 1 | y |

X r –6 |00|r |0110 |

XAD r.d 23 |0010|0011|

XDS r –7 |00|r |0111 |

XIS r –4 | 0 0 | r | 0 1 0 0 |

Language

Code

(binary)

_______________

|0011|1100|

_______________

_______________

|0010|1100|

_______________

_______________

(r = 0:3)

_______________

|0 | r | d |

_______________

_______________

|0100|1100|

_______________

|0100|0101|

_______________

|0100|0010|

_______________

|0100|0011|

_______________

|0100|1101|

_______________

|0100|1101|

_______________

|0100|0110|

_______________

|0100|1011|

_______________

_______________

_______________

(r = 0:3)

_______________

|1|r |d|

_______________

_______________

(r = 0:3)

_______________

(r = 0:3)

Data Fl ow

A → Q

7:4

RAM (B) → Q

Q

→ RAM(B)

7:4

Q

→ A

3:0

RAM(B) → A

Br ⊕ r → Br

3:0

Skip

Conditions

Descriptio n

None Copy A, RAM to Q

None Copy Q to RAM A

None Load RAM into A,

Exclusive-OR Br with r

RAM(r.d) → A None Load A with RAM pointed

to directly by r.d.

ROM (PC

A.M) → Q

10:8

None Load Q Indirect (note 3)

SB → SC

0 → RAM (B)

0 → RAM (B)

0 → RAM (B)

0 → RAM (B)

1 → RAM (B)

1 → RAM (B)

1 → RAM (B)

1 → RAM (B)

y → RAM (B)

Bd + 1 → Bd

RAM (B) ↔ A

Br ⊕ r → Br

0

1

2

3

0

1

2

3

None Reset RAM Bit

None Set RAM Bit

None Store Memory Immediate

and Increment Bd

None Exchange RAM with A,

Exclusive-OR Br with r

RAM (r.d) ↔ A None Exchange A with RAM

pointed to directly by r.d.

RAM (B) ↔ A

Bd – 1 → Bd

Br ⊕ r → Br

RAM (B) ↔ A

Bd + 1 → Bd

Br ⊕ r → Br

Bd

Decrements

Past 0

Bd

Increments

Past 1 5

Exchange RAM with A and

Decrement Bd,

Exclusive-OR Br with r

Exchange RAM with A and

Increment Bd,

Exclusive-OR Br with r

20/27

Page 21

REGISTER REFERENCE INSTRUCTIONS

Machi n e

Mnem Operand

Hex

Code

Language

Code

(binary)

CAB 50 |0101|0000|

CBA 4E |0100|1110|

LBI r.d

_______________

_______________

| 0 0 | r | (d-1) |

_______________

(r = 0:3)

(d = 0.9:15)

or

33

|0011|0011|

_______________

|1| r | d |

_______________

(any r, any d)

LEI y 336–|0011|0001|

XABR 12 |0001|0010|

_______________

|0110| y |

_______________

_______________

TEST INSTRUCTIONS

ETL9444/9445–ETL9344/9345

Data Fl ow

A → Bd None Copy A to Bd

Bd → A None Copy Bd to A

r.d → B Skip until

y → EN None Load EN Immediate

A → Br (0 → A

) None Exchange A with Br

3

Skip

Conditions

not a LBI

Descriptio n

Load B Immediate with r.d

(note 6)

(note 7)

Machi n e

Mnem Operand

Hex

Code

Language

Code

(binary)

SKC 20 |0010|0000|

SKE 21 |0010|0001|

SKGZ 3321|0011|0011|

SKGBZ 33 |0011|0011|

0

1

2

3

SKMBZ 0

1

2

3

SKT 41 |0100|0001|

_______________

_______________

_______________

|0010|0001|

_______________

_______________

|0000|0001|

01

_______________

11

|0001|0001|

_______________

03

|0000|0011|

_______________

13

|0001|0011|

_______________

01

|0000|0001|

_______________

11

|0001|0001|

_______________

03

|0000|0011|

_______________

13

|0001|0011|

_______________

_______________

Data Fl ow

Skip

Conditions

Descriptio n

C = ”1” Skip if C is true.

A =RAM(B) Skip if A Equals RAM

G

= 0 Skip if G is zero (all 4 bits).

3:0

1st Byte Skip if G Bit is zero.

G

=0

0

G

=0

2nd Byte

1

G2=0

G

=0

3

RAM(B)

=0

Skip if RAM bit is zero.

0

RAM(B)1=0

RAM(B)2=0

RAM(B)

A

=0

3

Skip on Timer (note 3)

time-base

counter

carry has

occured

since last

test.

21/27

Page 22

ETL9444/9445–ETL9344/9345

INPUT/OUTPUTINSTRUCTIONS

Machi n e

Mnem Operand

ING 332A|0011|0011|

ININ 3328|0011|0011|

INIL 3329|0011|0011|

INL 332E|0011|0011|

OBD 333E|0011|0011|

OGI y 335–|0011|0011|

OMG 333A|0011|0011|

XAS 4F |0100|1111|

Notes : 1.All subscripts for alphabetical symbols indicatebitnumbers unless explicitlydefined (e.g., Br and Bd areexplicitly defined).Bitsare

numbered 0 to N where 0signifies the least significantbit (low-order,right-mostbit). For example, A3indicates the mostsignificant

(left-most) bitof the4-bit A register.

2.The ININinstruction is notavailableon the24-pin ETL9445or ETL9345 since thesedevicesdo not contain the IN inputs.

3.For additional information onthe operationof the XAS, JID, LQUID,INIL andSKT instructions, see below.

4.The JPinstruction allowsa jump,while in subroutine pages 2 or3, to anyROM locationwithinthe two-pageboundary of pages 2 or

3. The JP instruction, otherwise,permitsa jumpto aROM locationwithinthe current64-word page.JP may not jumpto the lastword

of a page.

5.A JSRPtransfers program controlto subroutine page 2 (0010 is loaded intothe upper 4 bits of P). A JSRP may notbe usedwhenin

pages 2or3, JSRP may notjump to the last word inpage2.

6.LBI isa single-byteinstruction if d= 0, 9,10, 11, 12, 13, 14 or 15.Themachine codefor the lower4 bitsequals thebinaryvalueof

the ”d” data minus1, e.g., to load thelower fourbits of B (Bd) with the value 9(10012), the lower 4 bitsofthe LBI instructionequal 8

(10002). Toload 0, the lower 4bitsofthe LBIinstruction should equal15 (11112).

7.Machinecodefor operandfieldyfor LEI instructionshould equal the binaryvalueto belatched into EN, where a ”1” or”0” ineachbit

of EN corresponds withtheselectionordeselection ofa particular functionassociated with eachbit. (See Functional Description, EN

Register).

Hex

Code

Language

Code

(binary)

_______________

|0010|1010|

_______________

_______________

|0010|1000|

_______________

_______________

|0010|1001|

_______________

_______________

|0010|1110|

_______________

_______________

|0011|1110|

_______________

_______________

|0101| y |

_______________

_______________

|0011|1010|

_______________

_______________

Data Fl ow

G → A None Input G Ports to A

IN → A None Input IN Inputs to A

IL

, CKO, ”0”, IL0→ A None Input IL Latches to A

3

L

→ RAM(B)

7:4

L

→ A

3:0

Bd → D None Output Bd to D Outputs

y → G None Output to G Ports

RAM(B) → G None Output RAM to G Ports

A ↔ SIO, C → SKL None Exchange A with SIO

Skip

Conditions

None Input L Ports to RAM, A

Descriptio n

(note 2)

(note 3)

Immediate

(note 3)

The followinginformationisprovided toassisttheuserin understandingtheoperation ofseveral unique

instructions andto provide notesuseful toprogrammers in writing ETL9444/L9445 programs.

XAS INSTRUCTION

XAS (Exchange A with SIO) exchanges the 4-bit

contents of the accumulator with the 4-bit contents

of the SIO register. The contents of SIO will contain

serial-in/serial-out shiftregisterorbinarycounterdata, depending on the value of the EN register. An

XAS instruction willalso affect the SK output. (See

Functional Description, ENRegister, above). If SIO

is selected as a shift register, an XAS instruction

must be performed once every 4 instructioncycles

to effecta continuous datastream.

22/27

JIDINSTRUCTION

JID(JumpIndirect)is anindirectaddressing instruc-

tion,transferring program control to a newROM locationpointed to indirectly byA and M. It loads the

lower 8bitsofthe ROM address register PCwiththe

contents of ROM addressed by the 11-bit word,

PC

A,M. PC10,PC9and PC8arenotaffectedby

10:8

thisinstruction.

Note that JID requires 2 instruction cycles to exe-

cute.

INIL INSTRUCTION

INIL(InputIL Latchesto A)inputs 2 latches, IL3and

IL0(see figure 7) and CKO into A. The IL3and IL

latches are set if a low-going pulse (”1” to ”0”) has

0

Page 23

ETL9444/9445–ETL9344/9345

occurredontheIN3and IN0inputssincethelastINIL

instruction, provided the input pulsestays lowfor at

least two instruction times.Execution of an INIL inputs IL3and IL0intoA3 andA0 respectively,and resets these latches to allow them to respond to

subsequent low-going pulses on the IN3and IN

lines.IfCKOis maskprogrammed asageneral purpose input, an INIL will inputthe state of CKO into

A2. If CKOhas not been so programmed, a ”1” will

be placedin A2. A ”0” is always placed in A1 upon

the executionofanINIL.Thegeneral purposeinputs

IN3-IN0areinput to Aupon executionof an ININ instruction.(seetable2, ININinstruction). INILis useful in recognizingpulses of short duration or pulses

which occur toooften to be read conveniently byan

ININ instruction.

Note : IL latchesare not cleared on reset : IL3and

IL0not input on ETL9444/L9445.

LQID INSTRUCTION

LQID(LoadQIndirect)loadsthe 8-bitQregister with

the contents of ROM pointed to by the 11-bit word

PC10,PC9,PC8, A, M. LQID can beused for table

lookup or codeconversion such as BCD to sevensegment. The LQID instruction ”pushes” the stack

(PC + 1 → SA→ SB → SC) andreplaces the least

significant 8 bits of PC as follows: A – PC

(B) → PC

, leaving PC10,PC9and PC8unchan-

3:0

7:4

, RAM

ged. The ROMdata pointed to by thenewaddress

is fetched and loaded into the Q latches. Next, the

stackis”popped” (SC→ SB→ SA→ PC),restoring

the saved valueof PC to continue sequential programexecution. SinceLQID pushesSB → SC, the

previous contents of SCare lost.Also, whenLQID

pops the stack, the previously pushed contents of

SB areleftin SC.The net resultis thatthe contents

of SB areplaced in SC (SB → SC). Note thatLQID

takes twoinstruction cycletimes to execute.

Figure 7 : INIL Hardware Implementation.

SKT INSTRUCTION

The SKT(Skip OnTimer) instructiontests the state

ofan internal 10-bit time-basecounter.This counter

divides the instruction cycle clock, frequency by

1024and provides a latchedindication ofcounter o-

0

verflow.The SKT instruction teststhis latch, executing the next program instruction if the latch is not

set.If thelatchhas beenset since theprevious test,

thenextprogram instructionisskipped andthelatch

is reset. The features associated with this instruction, therefore, allow the ETL9344/L9345 to generate its own time-base for real-time processing

ratherthan relying on an externalinput signal.

Forexample, usinga2.097MHz crystal asthetimebase to the clock generator, the instruction cycle

clock frequency will be 65kHz (crystal frequency ÷

32) and the binary counter output pulse frequency

willbe 64Hz.For time-of-dayorsimilar real-timeprocessing,the SKTinstructioncancalla routine which

increments a ”seconds”counter every64 ticks.

INSTRUCTIONSET NOTES

a. The first word of a ETL9444/L9445 program

(ROM address0) must be a CLRA (Clear A) instruction.

b. Althoughskipped instructionsare not executed,

one instruction cycletime is devotedto skipping

eachbyte oftheskippedinstruction.Thusallprogram pathsexcept JIDand LQID take thesame

number of cycle times whether instructions are

skippedor executed. JID and LQID instructions

take 2 cycles if executedand 1 cycle if skipped.

c. TheROMisorganized into32pagesof64words

each. The Program Counter is an 11-bit binary

counter,and willcountthroughpageboundaries.

If a JP, JSRP, JID or LQID instruction islocated

in the last word of a page, the instruction operates asif it were in the nextpage. For example

: aJP located inthe lastwork of apage willjump

toalocationin thenextpage.Also,aLQID orJID

located in the last word of page 3, 7,11, 15,19,

23 or27will accessdatainthe next groupof four

pages.

23/27

Page 24

ETL9444/9445–ETL9344/9345

OPTI ON LI ST

The ETL9444/L9445 mask programmable options

are assigned numbers which correspond with the

ETL9444pins.

The following is a list of ETL9444 options. When

specifyingETL9445 chip, Options 9, 10, 19, and 20

mustallbesettozero.Theoptions areprogrammed

at the sametime asthe ROM pattern toprovide the

user with the hardware flexibility to interface to various I/O components using little or no external circuitry.

Option1 = 0 : GroundPin - nooptions available

Option2 : CKO Output

= 0 : clock generator output tocrystal/resonator

(0 not allowable value if option 3 = 3)

= 1 : pin isRAM power supply (VR) input

= 2 : generalpurpose input. load device toV

CC

= 3 : generalpurpose input, Hi-Z

Option3 : CKIInput

= 0 : oscillatorinputdivided by 32 (2MHzmax.)

= 1 : oscillatorinputdivided by 16 (1MHzmax.)

= 2 : oscillatorinputdivided by 8 (500kHz max.)

= 3 : single-pinRC controlled oscillator divided

by 4

= 4 : oscillatorinputdivided by 4 (Schmitt)

Option4 : RESET Input

= 0 : load device toV

CC

= 1 : Hi-Z input

Option5 : L

7

Driver

= 0 : Standard output

= 1 : Open-drain output

= 2 : High current LED direct segment drive

output

= 3 : High current TRI-STATE push-pull

output

= 4 : Low-current LED direct segment drive

output

= 5 : Low-current TRI-STATEpush-pull

output

Option6 : L6Driver

same asOption 5

Option7 : L5Driver

same asOption 5

Option8 : L4Driver

same asOption 5

Option9 : IN1Input

= 0 : load device toV

CC

= 1 : Hi-Z input

Option10 :IN2Input

same asOption 9

Option11 : VCCpin

= 0 : 4.5V to 6.3Voperation

= 1 : 4.5V to 9.5Voperation

Option12 : L3Driver

sameas Option5

Option14 : L2Driver

sameas Option5

Option14 : L1Driver

sameas Option5

Option15 : L0Driver

sameas Option5

Option16 : SIInput

sameas Option9

Option17 : SODriver

= 0 : standard output

= 1 : open-drain output

= 2 : push-pull output

Option18 : SKDriver

sameas Option17

Option19 : IN0Input

sameas Option9

Option20 : IN3Input

sameas Option9

Option21 : G0I/OPort

= 0 : very-highcurrent standardoutput

= 1 : very-highcurrent open-drain output

= 2 : high current standardoutput

= 3 : high current open-drain output

= 4 : standard LSTTL output (fanout = 1)

= 5 : open-drain LSTTLoutput (fanout = 1)

Option22 : G1I/OPort

sameas Option21

Option23 : G2I/OPort

sameas Option21

Option24 : G3I/OPort

sameas Option21

Option25 : D3Output

sameas Option21

Option26 : D2Output

sameas Option21

Option27 : D1Output

sameas Option21

Option28 : D0Output

sameas Option21

Option29 : L InputLevels

= 0 : standard TTL input levels

(”0”= 0.8V, ”1” = 2.0V)

24/27

Page 25

ETL9444/9445–ETL9344/9345

= 1 : higher voltage input levels

(”0”= 1.2V,”1” = 3.6V)

Option30 :IN InputLevels

same asOption 29

Option31 :G InputLevels

same asOption 29

Option32 :SI Input Levels

same asOption 29

Option33 :RESET Input

= 0 : Schmitttrigger input

TEST MODE (Non-Standard Ope ratio n)

The SO output has been configured to providefor

standard test procedures for the custom-programmed ETL9444. WithSO forced to logic ”1”,two test

modes are provided, depending upon the value of

SI :

a. RAMand Internal LogicTest Mode (SI = 1)

b. ROMTest Mode (SI = 0)

These special test modesshould not be employed

by the user ; they are intended for manufacturing

test only.

APPLICATION EXAMPLE :

ETL9444General Controller

Figure 8 shows and interconnect diagram for a

ETL9444used asa general controller. Operation of

the systemis as follows :

1. The L7-L0outputsare configuredas LED Direct

Drive outputs, allowing direct connection to the

segments of thedisplay.

= 1 : standard TTL input levels

= 2 : higher voltage input levels

Option34 : CKO InputLevels (CKO = input Option

2 = 2.3)

sameas Option29

Option35 COP Bonding

= 0 : ETL9444 (28-pin device)

= 1 : ETL9445 (24-pin device)

= 2 : both 28 and 24 pin versions

2. The D3-D0outputs drive the digits of the multiplexed display directly and scanthe columns of

the 4 x 4 keyboardmatrix.

3. The IN3-IN0inputs are used to input the 4 rows

of the keyboard matrix. Reading the IN lines in

conjunction with the current value of the D outputs allows detection, debouncing, and decoding ofany one ofthe 16 keyswitches.

4. CKI is configured as a single-pin oscillator input

allowing system timing to be controlled by asingle-pinRC network. CKO is therefore available

for useasa general-purpose input.

5. SI is selected asthe input to a binary counterinput. WithSIO used asa binary counter, SOand

SK can be usedas general purpose outputs.

6. The 4 bidirectional G I/Oports (G3-G-0) are available for use as required by the user’s application.

7. Normal reset operation is selected.

Figure 8 : ETL9444 Keyboard/display Interface.

25/27

Page 26

ETL9444/9445–ETL9344/9345

PHYSIC AL DIME NSIO NS

28–PINS– PLASTIC PACKAGE

24–PINS– PLASTIC PACKAGE

26/27

Page 27

ETL9444/9445–ETL9344/9345

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no

responsability for the consequences of use of such information nor for any infringement of patents or other rights of

third parties which may result from its use. No license is grantedby implication or otherwiseunder any patent or patent

rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without

notice. This publicationsupersedes and replaces all informationpreviously supplied.

SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or

systems without the express written approval of SGS-THOMSON Microelectronics.

1994 SGS-THOMSON Microelectronics - All rights reserved.

Purchase of I2C Components by SGS-THOMSON Microelectronicsconveys a license under the Philips I2C Patent. Rights to use these

components in an I2C system isgranted provided that the system conforms to the I2C StandardSpecification as defined by Philips.

SGS-THOMSON Microelectronics Group of Companies

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco The Netherlands - Singapore - Spain

Sweden - Switzerland- Taiwan - Thailand- UnitedKingdom -U.S.A.

27/27

Loading...

Loading...