Page 1

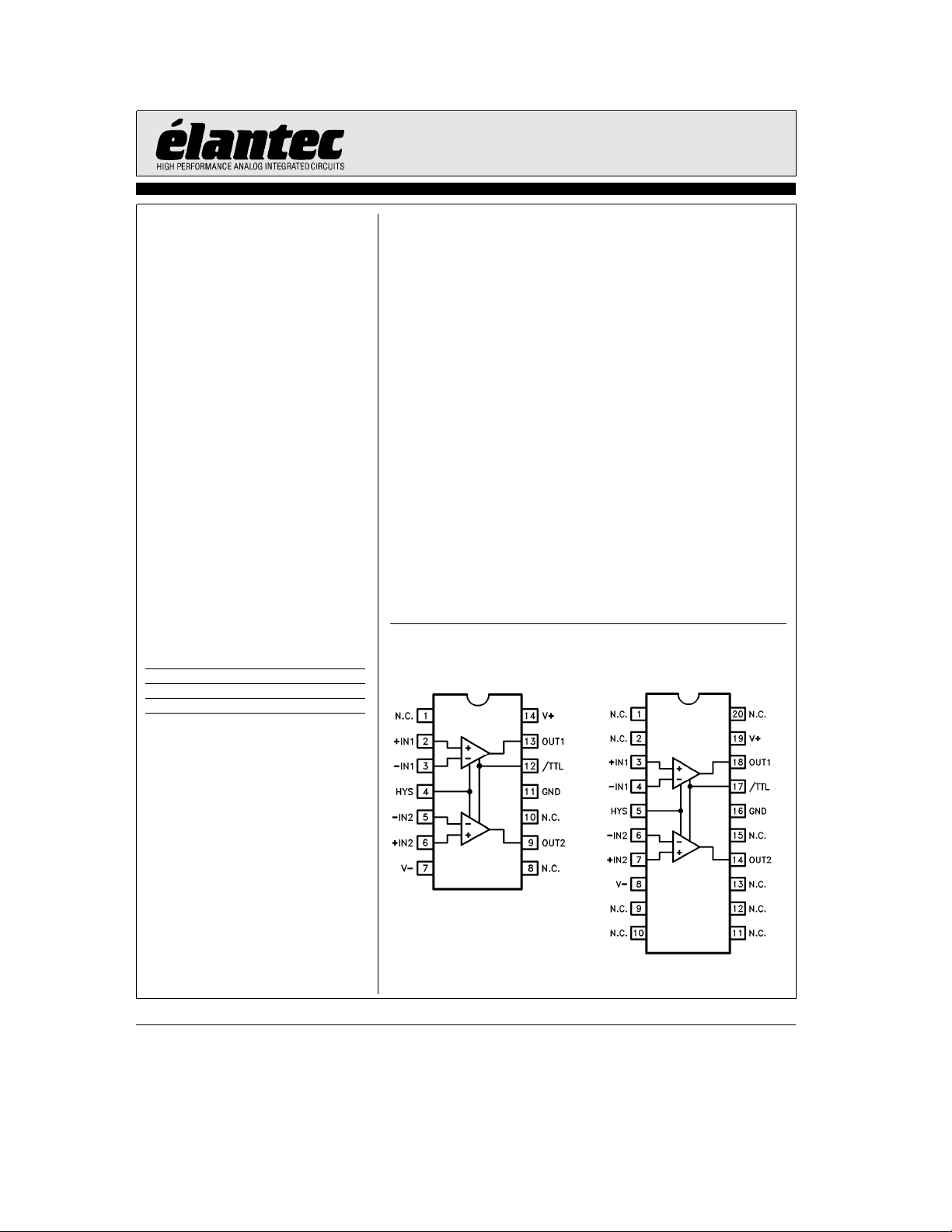

EL2252C

Dual 50 MHz Comparator/Pin Receiver

EL2252C December 1995 Rev E

Features

# Fast responseÐ7 ns

# Inputs tolerate large overdrives

with no speed nor bias current

penalties

# Propagation delay is relatively

constant with variations of input

Slew Rate, overdrive,

temperature, and supply voltage

# Output provides proper CMOS or

TTL logic levels

# Hysteresis is available on-chip

# Large voltage gainÐ8000 V/V

# Not oscillation-prone

# Can detect 4 ns glitches

# MIL-STD-883 Rev. C compliant

Applications

# Pin receiver for automatic test

equipment

# Data communications line

receiver

# Frequency counter input

# Pulse squarer

Ordering Information

Part No. Temp. Range Package Outline

EL2252CN 0§Ctoa75§C 14-Pin P-DIP MDP0031

EL2252CM 0§Ctoa75§C 20-Lead SOL MDP0027

General Description

The EL2252 dual comparator replaces the traditional input

a

buffer

attenuatoraECL comparatoraECL to TTL translator circuit blocks used in digital equipment. The EL2252 provides a quick 7 ns propagation delay while complying with

g

10V inputs. Input accuracy and propagation delay is maintained even with input signal Slew Rates as great as 4000 V/ms.

The EL2252 can run on supplies as low as

b

5.2V anda9V and

comply with ECL and CMOS inputs, or use supplies as great as

g

18V for much greater input range.

The EL2252 has a /TTL pin which, when grounded, restricts

the output V

When left open, the output V

to a TTL swing to minimize propagation delay.

OH

increases to a valid CMOS

OH

level.

The comparators are well behaved and have little tendency to

oscillate over a variety of input and output source and load

impedances. They do not oscillate even when the inputs are

held in the linear range of the device. To improve output stability in the presence of input noise, an internal 60 mV of hysteresis is available by connecting the HYS pin to V

b

.

Elantec’s products and facilities comply with MIL-I-45208A,

and other applicable quality specifications. For information on

Elantec’s processing, see Elantec document, QRA-1; ‘‘Elantec’s

Processing, Monolithic Integrated Circuits’’.

Connection Diagrams

Ý

14-Pin DIP 20-Pin SOL

Top View

Note: All information contained in this data sheet has been carefully checked and is believed to be accurate as of the date of publication; however, this data sheet cannot be a ‘‘controlled document’’. Current revisions, if any, to these

specifications are maintained at the factory and are available upon your request. We recommend checking the revision level before finalization of your design documentation. Patent pending.

©

1995 Elantec, Inc.

2252– 1

2252– 2

Top View

Page 2

EL2252C

Dual 50 MHz Comparator/Pin Receiver

Absolute Maximum Ratings

a

Voltage between V

Voltage at V

Voltage between

a

b

Output Current 12 mA

Current into

a

IN,bIN, HYS

b

and V

IN andaIN pins 36V

e

(T

25§C)

A

Internal Power Dissipation See Curves

36V

Operating Ambient Temperature Range

18V

Operating Junction Temperature 150

Storage Temperature Range

b

25§Ctoa85§C

b

65§toa150C

C

§

or /TTL 5 mA

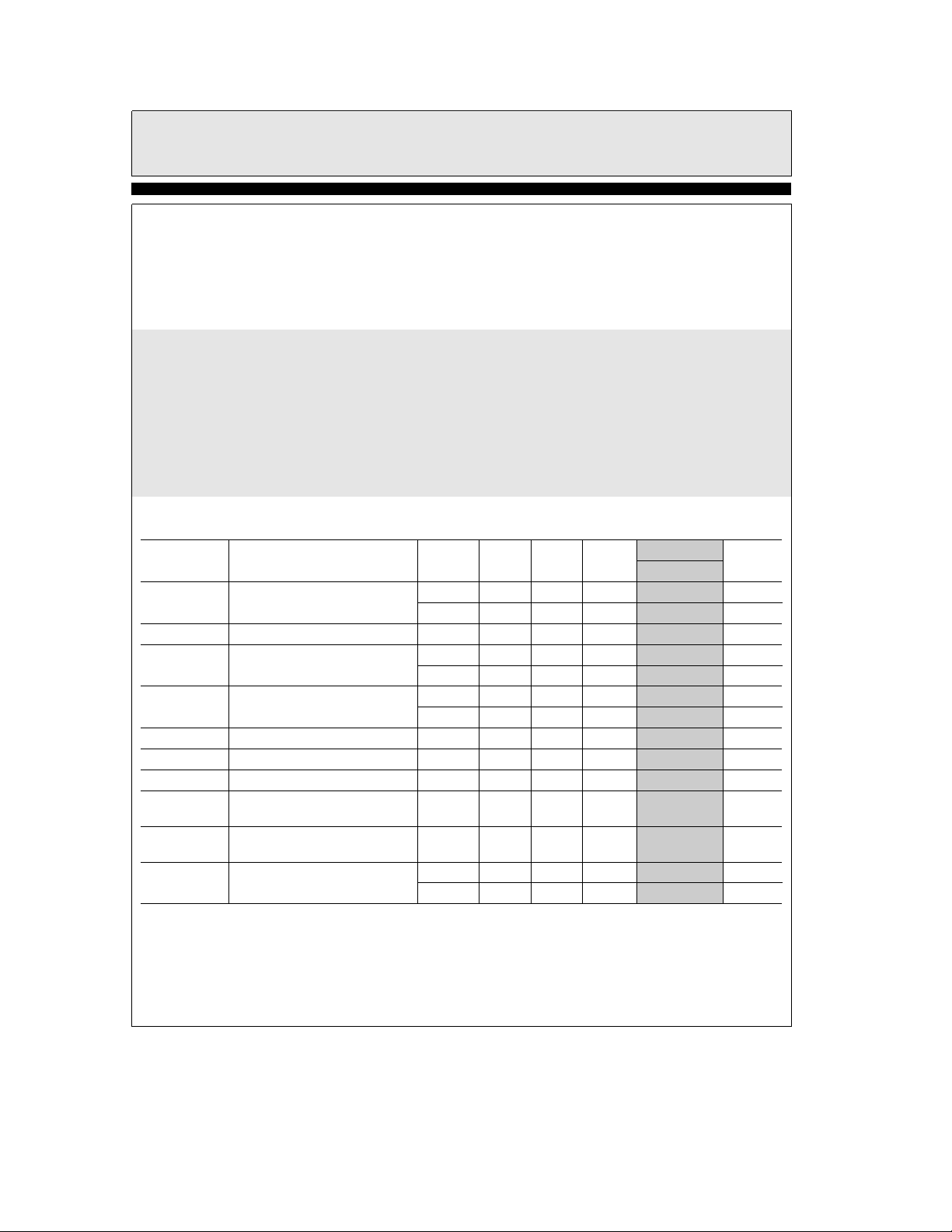

Important Note:

All parameters having Min/Max specifications are guaranteed. The Test Level column indicates the specific device testing actually

performed during production and Quality inspection. Elantec performs most electrical tests using modern high-speed automatic test

equipment, specifically the LTX77 Series system. Unless otherwise noted, all tests are pulsed tests, therefore T

Test Level Test Procedure

I 100% production tested and QA sample tested per QA test plan QCX0002.

II 100% production tested at T

III QA sample tested per QA test plan QCX0002.

IV Parameter is guaranteed (but not tested) by Design and Characterization Data.

V Parameter is typical value at T

T

MAX

and T

per QA test plan QCX0002.

MIN

DC Electrical Characteristics

e

25§C and QA sample tested at T

A

e

25§C for information purposes only.

A

e

g

V

15V; HYS and /TTL grounded; T

S

e

25§C,

A

e

25§C unless otherwise specified

A

Parameter Description Temp Min Typ Max

e

T

J

Test Level

e

TA.

C

Units

EL2252C

V

OS

Input Offset Voltage 25§C19ImV

Full 13 III mV

TCV

I

B

OS

Average Offset Voltage Drift Full 7 V mV/C

Input Bias Current at Null 25§C 6 16 I mA

Full 21 III mA

I

OS

Input Offset Current 25§C 0.2 1 I mA

Full 2 III mA

RIN, diff Input Differential Resistance 25§C30 VkX

R

, comm Input Common-Mode Resistance 25§C10 VMX

IN

CINInput Capacitance 25§C2 VpF

a

V

CM

b

V

CM

A

VOL

Positive Common-Mode

Input Range

Negative Common-Mode

Input Range

Full 10 13 II V

Full

b

b

9

12 II V

Large Signal Voltage Gain 25§C 4000 8000 I V/V

e

V

0.8V to 2.0V

O

Full 3000 III V/V

TDis 3.3in

2

Page 3

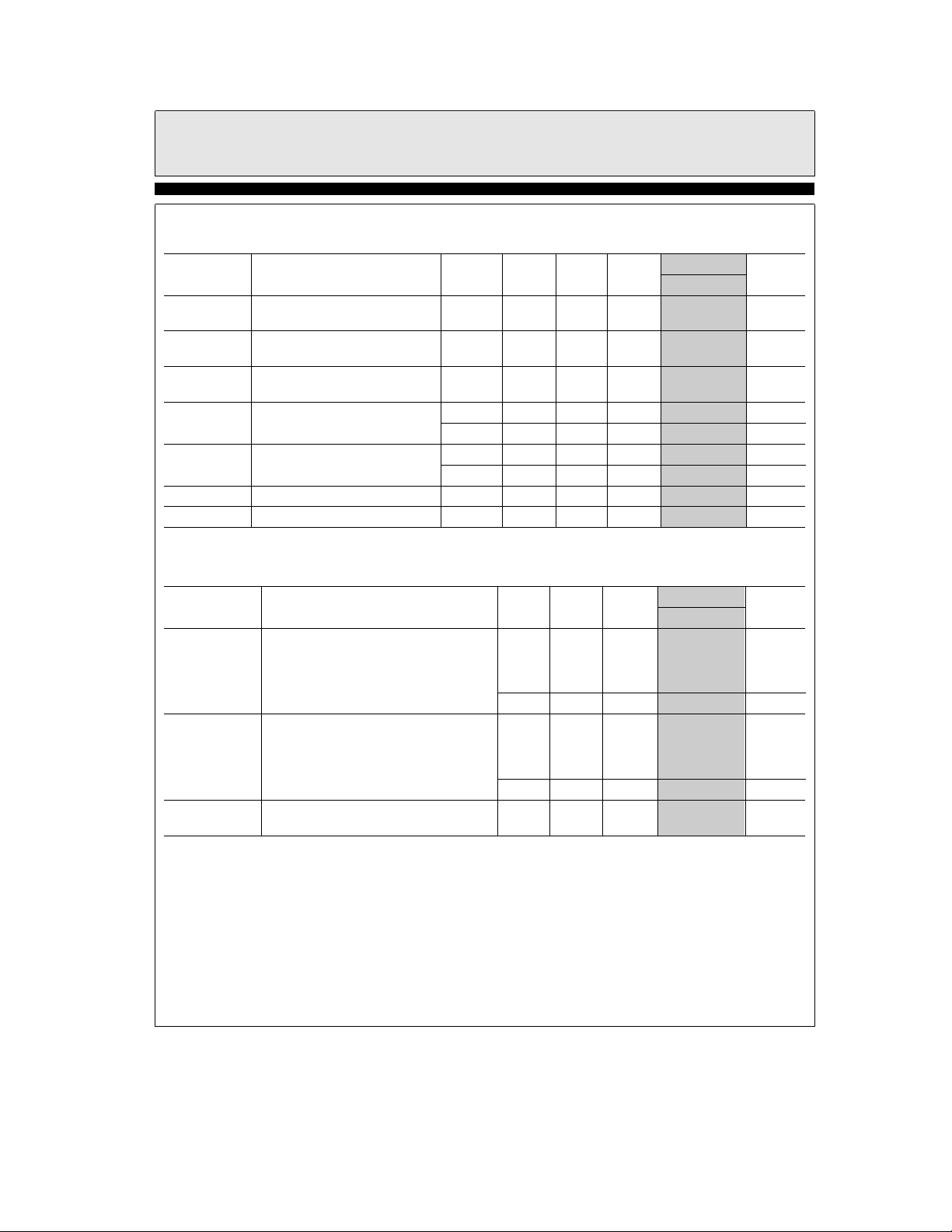

Dual 50 MHz Comparator/Pin Receiver

DC Electrical Characteristics

e

g

V

15V; HYS and /TTL grounded; T

S

Parameter Description Temp Min Typ Max

CMRR Common-Mode Rejection Ratio

(Note 1)

PSRR Power-Supply Rejection Ratio

(Note 2)

V

V

V

I

I

HYS

OH

OL

a

S

b

S

Peak-to-Peak Input Hysteresis

with HYS connected to V

High Level Output, CMOS Mode Full 4.0 4.6 5.1 II V

Low Level Output, I1e0 Full

Positive Supply Current Full 16 19 II mA

Negative Supply Current Full 17 20 II mA

AC Electrical Characteristics

e

g

V

S

Parameter Description Min Typ Max

T

PD

T

PD

T

PDSYM

Note 1: Two tests are performed with V

Note 2: Two tests are performed with V

15V; C

,T

a

,T

a

PD

PD

L

b

e

10 pF; T

e

25§C; TTL output threshold is 1.4V, CMOS output threshold is 2.5V; unless otherwise specified

A

Input to Output Propagation Delay,

k

0

V

IN

2000 V/ms Input Slew Rate

TTL Output Swing

CMOS Output Swing 8 V ns

Input to Output Propagation Delay,

b

b

2VkV

2 ns Input Rise Time

TTL Output Swing

CMOS Output Swing 9 V ns

Propagation Delay Change between

Positive and Negative Input Slopes

e

25§C unless otherwise specified Ð Contd.

A

Full 70 95 II dB

Full 70 90 II dB

25

C60 VmV

b

§

TTL Mode Full 2.4 2.7 3.2 II V

b

0.2 0.2 0.8 II V

I1e5 mA Full

k

5V, 500 mV Overdrive,

k

b

1V, 500 mV Overdrive,

IN

b

0.2 0.4 0.8 II V

6 9 III ns

5 9 III ns

1.25 V ns

e

0V tob9V and V

CM

ae

15V, Vbchanged fromb10V tob15V;

beb

15V, Vachanged from 10V to 15V.

V

CM

e

0V to 10V.

EL2252C

Test Level

EL2252C

Test Level

EL2252C

Units

Units

TDis 2.5inTDis 2.2in

3

Page 4

EL2252C

Dual 50 MHz Comparator/Pin Receiver

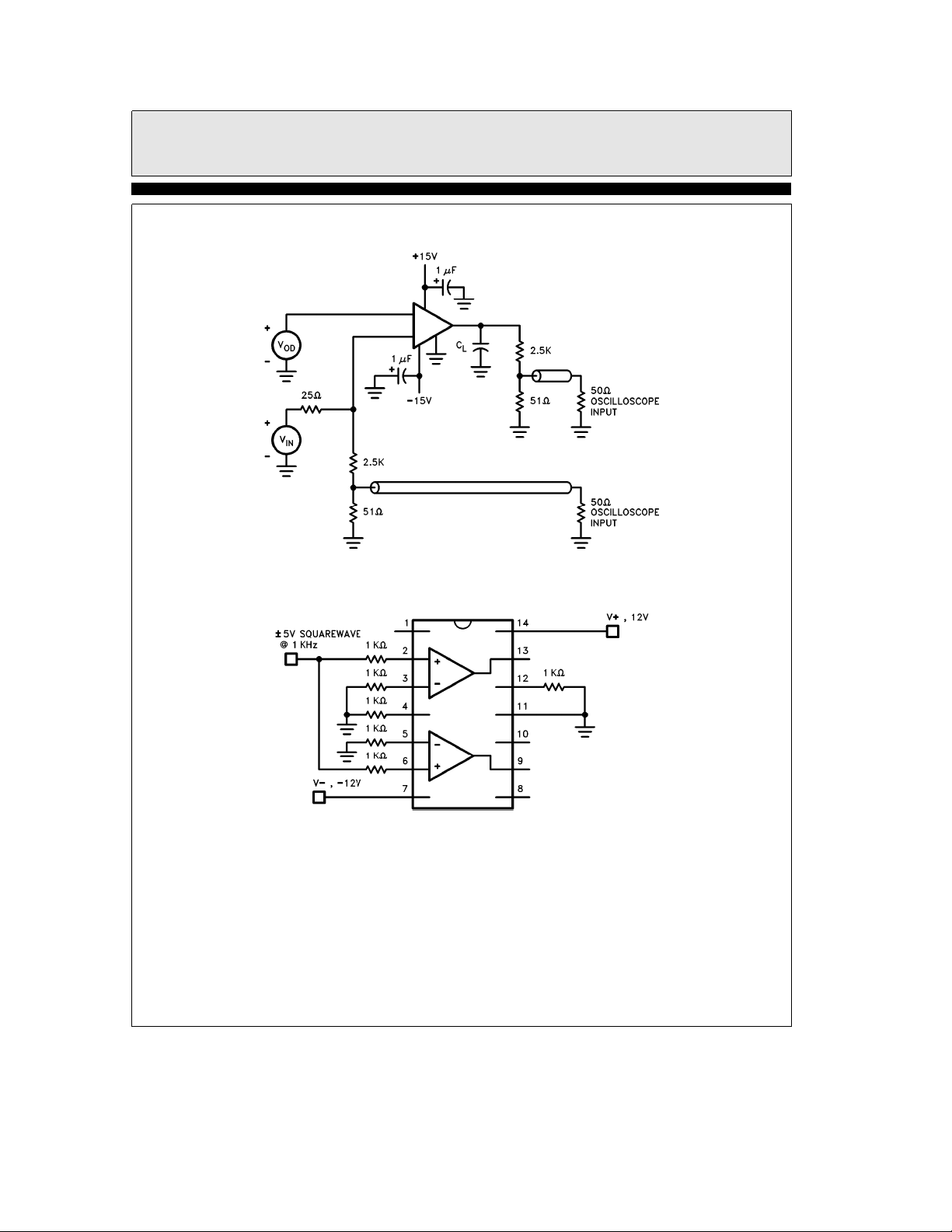

AC Test Circuit

Burn-In Circuit

2252– 3

2252– 4

4

Page 5

Typical Performance Curves

EL2252C

Dual 50 MHz Comparator/Pin Receiver

Input Bias Current

vs Small Overdrives

Bias Current vs

TemperatureÐInputs Balanced

Input Bias Current

vs Large Overdrives

Input Hysteresis Voltage

vs Temperature

Input/Output Transfer

FunctionÐHYS Open

2252– 6

2252– 5

Input/Output Transfer

FunctionÐHYS Connected to V

2252– 7

5

Page 6

EL2252C

Dual 50 MHz Comparator/Pin Receiver

Typical Performance Curves

Supply Current vs Supply Current vs Temperature

Supply Voltage

Output DelayÐ0.5V Overdrive

Ð Contd.

e

g

(V

15V)

S

Output DelayÐ0.5V Overdrive

2252– 8

Output with 50 MHz CMOS Input

2252– 9

2252– 11

2252– 10

Output with 50 MHz ECL Input

2252– 12

6

Page 7

EL2252C

Dual 50 MHz Comparator/Pin Receiver

Typical Performance Curves

Gain vs Frequency

Ð Contd.

4 ns TTL Glitch Detection

Propagation Delay vs

Temperature, CMOS Input

2252– 13

Propagation Delay vs

Temperature, ECL Input

Propagation Delay vs

Overdrive, CMOS Input

Propagation Delay vs

Input Slew Rate, CMOS Input

2252– 14

7

Page 8

EL2252C

Dual 50 MHz Comparator/Pin Receiver

Typical Performance Curves

Propagation Delay vs Propagation Delay vs

Power Supply Voltage

14-Lead Plastic DIP

Maximum Power Dissipation

vs Ambient Temperature

Ð Contd.

Load Capacitance

20-Lead SOL

Maximum Power Dissipation

vs Ambient Temperature

2252– 15

2252– 16

2252– 18

8

Page 9

EL2252C

Dual 50 MHz Comparator/Pin Receiver

Simplified Schematic

One Comparator

2252– 19

Applications Information

The EL2252 is very easy to use and is relatively

oscillation-free, but a few items must be attended. The first is that both supplies should be bypassed closely. 1 mF tantalums are very good and

no additional smaller capacitors are necessary.

The EL2252 requires V

serve AC performance. V

for a TTL output swing, 8V for CMOS outputs.

The input voltage range will be referred to the

more positive of the two inputs. That is, bringing

an input as negative as V

lems; it’s the other input’s level that must be considered. The typical input range is

b

to be at least 5V to pre-

a

must be at least 6V

b

will not cause prob-

a

13/b12V

g

when the supplies are

ishes over temperature and varies with processing; it is wise to set power supplies such that V

is 5V more positive than the most positive input

signal and V

most negative input.

encompass all CMOS and ECL logic inputs. If

the input exceeds the device’s common-mode input capability, the EL2252 propagation delay

and input bias current will increase. Fault currents will occur with inputs a diode below V

above V

even when fault currents within the absolute

maximum ratings.

9

b

more negative than 6V below the

a

. No damage nor VOSshift will occur

15V. This range dimin-

g

12V supplies will easily

b

a

or

Page 10

EL2252C

Dual 50 MHz Comparator/Pin Receiver

Applications Information

One of the few ways in which oscillations can be

induced is by connecting a high-Q reactive source

impedance to the EL2252 inputs. Such sources

are long wires and unterminated coaxial lines.

The source impedance should be de-Q’ed. One

method is to connect a series resistor to the

EL2252 input of around 100X value. More resistance will calm the system more effectively, but at

the expense of comparator response time. Another method is to install a ‘‘snubber’’ network from

comparator input to ground. A snubber is a resistor in series with a small capacitor, around 100X

and 33 pF. Each physical and electrical environment will require different treatments, although

many need none.

The major use of the HYS pin is to suppress

noise superimposed on the input signal. By

shorting the HYS pin to V

sis is placed around the V

input. Leaving the pin open, or more appropriately, grounding the HYS pin removes all hysteresis. Connecting a resistor between HYS and

b

V

allows an adjustment of the peak-to-peak

hysteresis level. Unfortunately, an external resistor cannot track the internal devices properly, so

temperature and unit-to-unit variations of hys-

b

ag30 mV hystere-

OS

Ð Contd.

of the comparator

teresis are increased. The relationship between

the resistor and resulting hysteresis level is not

linear, but a 1.5k resistor will approximately

halve the nominal value.

The time delay of the EL2252 will increase by

about 0.7 ns when using full hysteresis.

The EL2252 is specifically designed to be tolerent

of large inputs. It will exhibit very much increased delay times for input overdrives below

100 mV. If very small overdrives must be sensed,

the EL2018 or EL2019 comparators would be

good choices, although they lose accuracies with

signal input Slew Rates above 400 V/ms. The

EL2252 keeps its timing accuracy with input

Slew Rates between 100 V/ms and 4000 V/msof

input Slew Rate.

The output stage drives tens of pF load capacitances without increased overshoot, but propagation delay increases about 1 ns per 10 pF. The

output circuit is not a traditional TTL stage, and

using an external pullup resistor will not change

the V

TTL (by grounding the /TTL pin) will optimize

overall propagation delay and

try.

. In general setting the output swing to

OH

g

swing symme-

10

Page 11

EL2252C Macromodel

EL2252C

Dual 50 MHz Comparator/Pin Receiver

* Connections:

*

*

*

*

*

*

*

.subckt M2252 2 3 14 7 4 5 13

*

* Application Hints:

*

* Connect pin 4 to ground through 1000 MX resistor to inhibit

* Hysteresis; to invoke Hysteresis, connect pin 4 to V

*

* Connect pin 5 to ground to invoke TTL V

* for CMOS V

*

* To facilitate .OP, set itl1

* and node 30 to

*

*Input Stage

*

i1 22 7 1.7mA

r1 14 20 300

r2 14 21 300

q1 20 2 22 qn

q2 21 3 22 qn

q3 20 26 23 qn

q4 21 25 23 qn

q13 25 27 20 qp

q14 26 27 21 qp

v1 14 27 1.2V

r3 23 24 1.4k

d1 24 4 ds

r4 25 33 700

r5 26 33 700

q16 33 33 34 qn

q17 34 34 37 qn

v4 37 7 1.2V

*

* 2nd Stage

*

i2 30 7 3mA

i3 14 28 1.5mA

q703528qp

v2 44 0 1.2V

s1 44 35 5 0 swa

s2 45 35 5 0 swb

rsw 14 5 10k

a

input

b

input

l

ll

lll

llll

lllll

llllll

a

V

b

V

HYS

TTL

output

lllllll

b

.

; pin 5 may left open

OH

.

e

b

200, itl2e200, set node 27 to 13.8V,

12V.

OH

TDis 6.7in

11

Page 12

EL2252C

Dual 50 MHz Comparator/Pin Receiver

EL2252CDecember 1995 Rev E

EL2252C Macromodel

v3 45 0 2.5V

q502630qn

q6 28 25 30 qn

d3028ds

*

*Output Stage

*

i4 14 38 1mA

q8 38 38 39 qn

q9 32 32 39 qp

q1072832qp

q11 14 38 40 qn 2

q1272813qp2

r6 40 13 50

c1 28 0 3pF

*

* Models

*

.model qn npn (is

.model qp pnp (is

.model ds d(is

.model swa vswitch (von

.model swb vswitch (von

.ends

e2eb

15 bfe120 tfe0.2nS cjee0.2pF cjce0.2pF ccse0.2pF)

e

0.6eb15 bfe60 tfe0.2nS cjee0.5pF cjce0.3pF ccse0.2pF)

e3eb

12 tte0.05nS ege0.72V vje0.58)

e

0v voffe2.5V)

e

2.5 voffe0V)

Ð Contd.

TDis 3.1in

General Disclaimer

Specifications contained in this data sheet are in effect as of the publication date shown. Elantec, Inc. reserves the right to make changes

in the circuitry or specifications contained herein at any time without notice. Elantec, Inc. assumes no responsibility for the use of any

circuits described herein and makes no representations that they are free from patent infringement.

WARNING Ð Life Support Policy

Elantec, Inc. products are not authorized for and should not be

used within Life Support Systems without the specific written

consent of Elantec, Inc. Life Support systems are equipment in-

Elantec, Inc.

1996 Tarob Court

Milpitas, CA 95035

Telephone: (408) 945-1323

(800) 333-6314

Fax: (408) 945-9305

European Office: 44-71-482-4596

tended to support or sustain life and whose failure to perform

when properly used in accordance with instructions provided can

be reasonably expected to result in significant personal injury or

death. Users contemplating application of Elantec, Inc. products

in Life Support Systems are requested to contact Elantec, Inc.

factory headquarters to establish suitable terms & conditions for

these applications. Elantec, Inc.’s warranty is limited to replacement of defective components and does not cover injury to persons or property or other consequential damages.

Printed in U.S.A.12

Loading...

Loading...